#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 28-SPDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24k40-i-sp |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| REGISIE    | toning                            | uration word                     |                | siij. Superv               | 1501            |                 |               |

|------------|-----------------------------------|----------------------------------|----------------|----------------------------|-----------------|-----------------|---------------|

| R/W-1      | U-1                               | R/W-1                            | R/W-1          | R/W-1                      | R/W-1           | R/W-1           | R/W-1         |

| XINST      | _                                 | DEBUG                            | STVREN         | PPS1WAY                    | ZCD             | BORV            | /<1:0>        |

| bit 7      |                                   |                                  |                |                            |                 |                 | bit (         |

|            |                                   |                                  |                |                            |                 |                 |               |

| Legend:    |                                   |                                  |                |                            |                 |                 |               |

| R = Reada  |                                   | W = Writable                     |                | -                          | mented bit, rea |                 |               |

| -n = value | for blank device                  | '1' = Bit is set                 | [              | '0' = Bit is cle           | eared           | x = Bit is unkı | nown          |

| bit 7      | XINST: Exten                      | ded Instruction                  | Set Enable bi  | it                         |                 |                 |               |

|            |                                   | ed Instruction Se                |                |                            |                 | (Legacy mode)   |               |

|            |                                   | ed Instruction Se                |                | d Addressing r             | node enabled    |                 |               |

| bit 6      |                                   | ted: Read as '1                  |                |                            |                 |                 |               |

| bit 5      |                                   | ugger Enable b<br>ound debugger  |                |                            |                 |                 |               |

|            | •                                 | ound debugger                    |                |                            |                 |                 |               |

| bit 4      | •                                 | ck Overflow/Ur                   |                | t Enable bit               |                 |                 |               |

|            |                                   | verflow or Unde                  |                |                            |                 |                 |               |

|            |                                   | verflow or Unde                  |                |                            | t               |                 |               |

| bit 3      |                                   | PSLOCKED bit<br>SLOCKED bit      |                |                            | an unlocking s  | sequence is ex  | ecuted: once  |

|            |                                   | CK is set, all fut               |                |                            |                 |                 |               |

|            | 0 = The PPS                       | SLOCKED bit o                    |                |                            |                 |                 | g sequence is |

|            | execute                           | ,                                |                |                            |                 |                 |               |

| bit 2      | <b>ZCD:</b> ZCD Di<br>1 = ZCD dis | sable bit<br>abled. ZCD car      | n ha anahlad l | hy setting the 3           | 7CDSEN bit of   |                 |               |

|            |                                   | ays enabled, Z                   |                |                            |                 | ZODOON          |               |

| bit 1-0    | BORV<1:0>:                        | Brown-out Res                    | et Voltage Se  | lection bit <sup>(1)</sup> |                 |                 |               |

|            | PIC18F2xK40                       |                                  |                |                            |                 |                 |               |

|            |                                   | wn-out Reset \<br>wn-out Reset \ | • •            | ,                          |                 |                 |               |

|            |                                   | wn-out Reset V                   |                |                            |                 |                 |               |

|            |                                   | wn-out Reset V                   |                |                            |                 |                 |               |

|            | PIC18LF2xK4                       | 0 device:                        |                |                            |                 |                 |               |

|            |                                   | wn-out Reset V                   | • •            | ,                          |                 |                 |               |

|            |                                   | wn-out Reset V                   |                |                            |                 |                 |               |

|            |                                   | wn-out Reset \<br>wn-out Reset \ |                |                            |                 |                 |               |

|            |                                   |                                  |                |                            |                 |                 |               |

| Note 1 Th  | he higher voltage si              | ettina is recomr                 | nended for on  | eration at or a            | hove 16 MHz     |                 |               |

#### REGISTER 3-4: Configuration Word 2H (30 0003h): Supervisor

**Note 1:** The higher voltage setting is recommended for operation at or above 16 MHz.

#### 4.3.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a precision digitally-controlled internal clock source that produces a stable clock up to 64 MHz. The HFINTOSC can be enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits in Configuration Word 1 to '110' (Fosc = 1 MHz) or '000' (Fosc = 64 MHz) to set the oscillator upon device Power-up or Reset.

- Write to the NOSC<2:0> bits of the OSCCON1 register during run-time. See Section 4.4 "Clock Switching" for more information.

The HFINTOSC frequency can be selected by setting the HFFRQ<3:0> bits of the OSCFRQ register.

The NDIV<3:0> bits of the OSCCON1 register allow for division of the HFINTOSC output from a range between 1:1 and 1:512.

#### 4.3.2.2 MFINTOSC

The module provides two (500 kHz and 31.25 kHz) constant clock outputs. These clocks are digital divisors of the HFINTOSC clock. Dynamic divider logic is used to provide constant MFINTOSC clock rates for all settings of HFINTOSC.

The MFINTOSC cannot be used to drive the system but it is used to clock certain modules such as the Timers and WWDT.

#### 4.3.2.3 Internal Oscillator Frequency Adjustment

The internal oscillator is factory-calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 4-3).

The default value of the OSCTUNE register is 00h. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE **does not affect** the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), WWDT, Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

### 4.3.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a factory-calibrated 31 kHz internal clock source.

The LFINTOSC is the frequency for the Power-up Timer (PWRT), Windowed Watchdog Timer (WWDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits of Configuration Word 1 to enable LFINTOSC.

- Write to the NOSC<2:0> bits of the OSCCON1 register during run-time. See Section 4.4, Clock Switching for more information.

#### 4.3.2.5 ADCRC

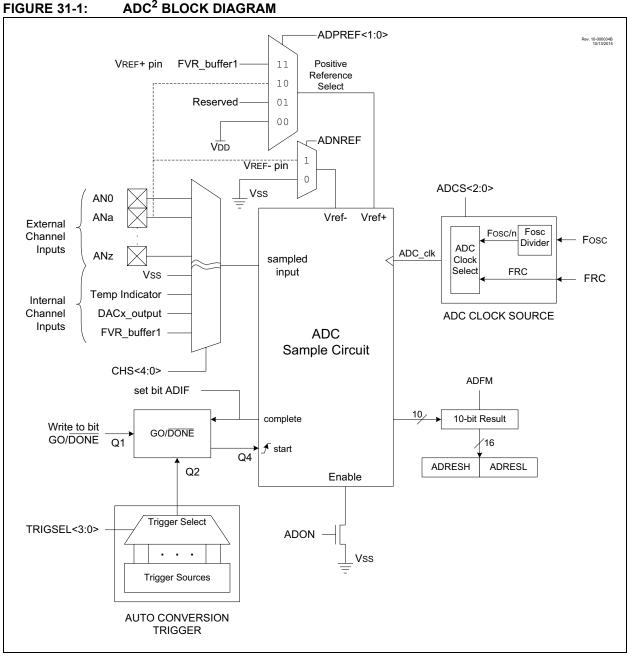

The ADCRC is an oscillator dedicated to the  $ADC^2$  module. The ADCRC oscillator can be manually enabled using the ADOEN bit of the OSCEN register. The ADCRC runs at a fixed frequency of 600 kHz. ADCRC is automatically enabled if it is selected as the clock source for the  $ADC^2$  module.

## 7.5 Register Definitions: Peripheral Module Disable

| REGISTER        | 7-1: PMD                           | U: PMD CON                                                           | RUL REGIS                       |                    |                  |                  |              |

|-----------------|------------------------------------|----------------------------------------------------------------------|---------------------------------|--------------------|------------------|------------------|--------------|

| R/W-0/0         | R/W-0/0                            | R/W-0/0                                                              | R/W-0/0                         | R/W-0/0            | R/W-0/0          | R/W-0/0          | R/W-0/0      |

| SYSCMD          | FVRMD                              | HLVDMD                                                               | CRCMD                           | SCANMD             | NVMMD            | CLKRMD           | IOCMD        |

| 7               |                                    |                                                                      |                                 |                    |                  |                  | (            |

| Legend:         |                                    |                                                                      |                                 |                    |                  |                  |              |

| R = Readabl     | le bit                             | W = Writable                                                         | bit                             | U = Unimplerr      | nented bit, read | d as '0'         |              |

| u = Bit is und  | changed                            | x = Bit is unkr                                                      | iown                            | -n/n = Value a     | t POR and BO     | R/Value at all o | ther Resets  |

| '1' = Bit is se | et                                 | '0' = Bit is clea                                                    | ared                            | q = Value dep      | ends on condit   | tion             |              |

| bit 7           | See descript<br>1 = System         | isable Peripheration in <b>Section 7</b><br>clock network di         | 7.4 "System C<br>isabled (Fosc) | lock Disable".     |                  |                  |              |

| bit 6           | FVRMD: Dis                         | clock network e<br>able Fixed Volta<br>dule disabled<br>dule enabled |                                 | bit                |                  |                  |              |

| bit 5           | 1 = HLVD n                         | isable Low-Volta<br>nodule disabled<br>nodule enabled                | age Detect bit                  |                    |                  |                  |              |

| bit 4           | 1 = CRC mo                         | able CRC Engir<br>odule disabled<br>odule enabled                    | ne bit                          |                    |                  |                  |              |

| bit 3           | 1 = NVM M                          | isable NVM Me<br>emory Scan mo<br>emory Scan mo                      | dule disabled                   | bit <sup>(2)</sup> |                  |                  |              |

| bit 2           | 1 = All Mem                        | /M Module Disal<br>ory reading and<br>odule enabled                  |                                 | bled; NVMCON       | registers canr   | not be written   |              |

| bit 1           | 1 = CLKR m                         | isable Clock Re<br>nodule disabled<br>nodule enabled                 | ference bit                     |                    |                  |                  |              |

| bit 0           | 1 = IOC mo                         | able Interrupt-on<br>dule(s) disabled<br>dule(s) enabled             | -Change bit, A                  | All Ports          |                  |                  |              |

|                 | learing the SYS<br>y Fosc/4 are no | SCMD bit disablet of affected.                                       | es the system                   | clock (Fosc) to    | peripherals, h   | owever periphe   | rals clocked |

## REGISTER 7-1: PMD0: PMD CONTROL REGISTER 0

- 2: Subject to SCANE bit in CONFIG4H.

- **3:** When enabling NVM, a delay of up to 1 µs may be required before accessing data.

#### 10.4.2 ACCESS BANK

While the use of the BSR with an embedded 8-bit address allows users to address the entire range of data memory, it also means that the user must always ensure that the correct bank is selected. Otherwise, data may be read from or written to the wrong location. This can be disastrous if a GPR is the intended target of an operation, but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 96 bytes of memory (00h<sup>-</sup>5Fh) in Bank 0 and the last 160 bytes of memory (60h<sup>-</sup>FFh) in Block 15. The lower half is known as the "Access RAM" and is composed of GPRs. This upper half is also where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figure 10-4).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0', however, the instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle, without updating the BSR first. For 8-bit addresses of 60h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 60h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 10.7.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

#### 10.4.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM, which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

#### 10.4.4 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (FFFh) and extend downward to occupy the top portion of Bank 15 (F38h to FFFh). A list of these registers is given in Table 10-3 and Table 10-4.

The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the peripheral functions. The Reset and Interrupt registers are described in their respective chapters, while the ALU's STATUS register is described later in this section. Registers related to the operation of a peripheral feature are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's.

| Address | Name                   | Bit 7   | Bit 6   | Bit 5     | Bit 4      | Bit 3  | Bit 2       | Bit 1  | Bit 0    | <u>Value on</u><br>POR, BOR |

|---------|------------------------|---------|---------|-----------|------------|--------|-------------|--------|----------|-----------------------------|

| EF2h    | RB3PPS                 | _       | —       | _         |            | •      | RB3PPS<4:0> | •      | •        | 00000                       |

| EF1h    | RB2PPS                 | _       | —       | _         |            |        | RB2PPS<4:0> |        |          | 00000                       |

| EF0h    | RB1PPS                 | _       | —       | _         |            |        | RB1PPS<4:0> |        |          | 00000                       |

| EEFh    | RB0PPS                 | _       | —       | _         |            |        | RB0PPS<4:0> |        |          | 00000                       |

| EEEh    | RA7PPS                 | _       | —       | _         |            |        | RA7PPS<4:0> |        |          | 00000                       |

| EEDh    | RA6PPS                 | _       | —       | _         |            |        | RA6PPS<4:0> |        |          | 00000                       |

| EECh    | RA5PPS                 | _       | —       | _         |            |        | RA5PPS<4:0> |        |          | 00000                       |

| EEBh    | RA4PPS                 | _       | —       | _         |            |        | RA4PPS<4:0> |        |          | 00000                       |

| EEAh    | RA3PPS                 | _       | —       | _         |            |        | RA3PPS<4:0> |        |          | 00000                       |

| EE9h    | RA2PPS                 | _       | —       | _         |            |        | RA2PPS<4:0> |        |          | 00000                       |

| EE8h    | RA1PPS                 | _       | —       | _         |            |        | RA1PPS<4:0> |        |          | 00000                       |

| EE7h    | RA0PPS                 | _       | —       | _         |            |        | RA0PPS<4:0> |        |          | 00000                       |

| EE6h    | PMD5                   | _       | —       | _         | —          | —      | —           | —      | DSMMD    | 0                           |

| EE5h    | PMD4                   | _       | UART1MD | _         | MSSP1MD    | —      | —           | —      | CWG1MD   | -0-00                       |

| EE4h    | PMD3                   | _       | —       | _         | —          | PWM4MD | PWM3MD      | CCP2MD | CCP1MD   | 0000                        |

| EE3h    | PMD2                   | _       | DACMD   | ADCMD     | —          | —      | CMP2MD      | CMP1MD | ZCDMD    | -00000                      |

| EE2h    | PMD1                   | _       | TMR6MD  | TMR5MD    | TMR4MD     | TMR3MD | TMR2MD      | TMR1MD | TMR0MD   | -0000000                    |

| EE1h    | PMD0                   | SYSCMD  | FVRMD   | HLVDMD    | CRCMD      | SCANMD | NVMMD       | CLKRMD | IOCMD    | 00x00000                    |

| EE0h    | BORCON                 | SBOREN  | —       | _         | —          | —      | —           | —      | BORRDY   | 1q                          |

| EDFh    | VREGCON <sup>(1)</sup> | _       | —       | _         | —          | —      | —           | VREGPM | Reserved | 01                          |

| EDEh    | OSCFRQ                 | _       | —       | _         | —          |        | HFFR        | Q<3:0> |          | 1111                        |

| EDDh    | OSCTUNE                | _       | —       |           | HFTUN<5:0> |        |             |        |          | 100000                      |

| EDCh    | OSCEN                  | EXTOEN  | HFOEN   | MFOEN     | LFOEN      | SOSCEN | ADOEN       | —      | —        | 000000                      |

| EDBh    | OSCSTAT                | EXTOR   | HFOR    | MFOR      | LFOR       | SOR    | ADOR        | —      | PLLR     | ddddd-d                     |

| EDAh    | OSCCON3                | CSWHOLD | SOSCPWR | —         | ORDY       | NOSCR  | —           | —      | —        | 00-00                       |

| ED9h    | OSCCON2                | _       |         | COSC<2:0> |            |        | CDIV        | <3:0>  |          | -ddddddd                    |

## TABLE 10-5: REGISTER FILE SUMMARY FOR PIC18(L)F24/25K40 DEVICES (CONTINUED)

$\label{eq:Legend: Legend: Legend: a generative state of the state of$

Note 1: Not available on LF devices.

| R/W-0            | R/W-0 | R/W-0               | R/W-0 | R/W-0            | R/W-0            | R/W-0    | R/W-0 |

|------------------|-------|---------------------|-------|------------------|------------------|----------|-------|

|                  |       |                     | NVMCC | DN2<7:0>         |                  |          |       |

| bit 7            |       |                     |       |                  |                  |          | bit 0 |

|                  |       |                     |       |                  |                  |          |       |

| Legend:          |       |                     |       |                  |                  |          |       |

| R = Readable b   | bit   | W = Writable bit    |       | U = Unimpler     | nented bit, read | d as '0' |       |

| x = Bit is unkno | wn    | '0' = Bit is cleare | ed    | '1' = Bit is set | :                |          |       |

| -n = Value at P  | OR    |                     |       |                  |                  |          |       |

#### REGISTER 11-2: NVMCON2: NONVOLATILE MEMORY CONTROL 2 REGISTER

#### bit 7-0 NVMCON2<7:0>:

Refer to Section 11.1.4 "NVM Unlock Sequence".

**Note 1:** This register always reads zeros, regardless of data written.

#### Register 11-3: NVMADRL: Data EEPROM Memory Address Low

|             |         |         |         | 3       |         |         |         |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| R/W-x/0     | R/W-x/0 | R/W-x/0 | R/W-x/0 | R/W-x/0 | R/W-x/0 | R/W-x/0 | R/W-x/0 |

| NVMADR<7:0> |         |         |         |         |         |         |         |

| bit 7       |         |         |         |         |         |         | bit 0   |

|             |         |         |         |         |         |         |         |

| Legend:            |                      |                                    |  |

|--------------------|----------------------|------------------------------------|--|

| R = Readable bit   | W = Writable bit     | U = Unimplemented bit, read as '0' |  |

| x = Bit is unknown | '0' = Bit is cleared | '1' = Bit is set                   |  |

| -n = Value at POR  |                      |                                    |  |

#### bit 7-0 NVMADR<7:0>: EEPROM Read Address bits

### REGISTER 11-4: NVMADRH: DATA EEPROM MEMORY ADDRESS HIGH<sup>(1)</sup>

| U-0      | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-x/u     | R/W-x/u |

|----------|-----|-----|-----|-----|-----|-------------|---------|

| —        | _   | —   | —   | _   | —   | NVMADR<9:8> |         |

| bit 7 bi |     |     |     |     |     | bit 0       |         |

| Legend:            |                      |                                    |  |

|--------------------|----------------------|------------------------------------|--|

| R = Readable bit   | W = Writable bit     | U = Unimplemented bit, read as '0' |  |

| x = Bit is unknown | '0' = Bit is cleared | '1' = Bit is set                   |  |

| -n = Value at POR  |                      |                                    |  |

bit 7-2 Unimplemented: Read as '0'

bit 1-0 NVMADR<9:8>: EEPROM Read Address bits

**Note 1:** The NVMADRH register is not implemented on PIC18(L)F24/25K40.

## 14.8 Register Definitions: Interrupt Control

| R/W-0/0               | R/W-0/0                                                                                              | R/W-0/0                                                                                           | U-0                                                 | U-0                                      | R/W-1/1          | R/W-1/1           | R/W-1/1       |

|-----------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------|------------------|-------------------|---------------|

| GIE/GIEH              | PEIE/GIEL                                                                                            | IPEN                                                                                              | _                                                   | -                                        | INT2EDG          | INT1EDG           | INT0EDG       |

| bit 7                 |                                                                                                      |                                                                                                   |                                                     | <b>I</b>                                 |                  | I                 | bit (         |

|                       |                                                                                                      |                                                                                                   |                                                     |                                          |                  |                   |               |

| Legend:               |                                                                                                      |                                                                                                   |                                                     |                                          |                  |                   |               |

| R = Readable          | e bit                                                                                                | W = Writable                                                                                      | bit                                                 | U = Unimple                              | mented bit, read | 1 as '0'          |               |

| -n = Value at         | POR                                                                                                  | '1' = Bit is set                                                                                  |                                                     | '0' = Bit is cle                         | eared            | x = Bit is unki   | nown          |

| bit 7                 | <u>If IPEN = 1</u> :<br>1 = En<br>0 = Dis                                                            | lobal Interrupt I<br>ables all unma<br>sables all interr                                          | sked interrup                                       | ts and cleared                           | by hardware for  | high-priority in  | terrupts only |

|                       |                                                                                                      | ables all unmas<br>ables all interru                                                              |                                                     | ts and cleared                           | by hardware for  | all interrupts    |               |

| bit 6                 | <u>If IPEN = 1</u> :<br>1 = En<br>0 = Dis<br><u>If IPEN = 0</u> :<br>1 = En                          | Peripheral Intern<br>ables all low-pr<br>sables all low-p<br>ables all unmas<br>sables all peripl | iority interrup<br>riority interrup<br>sked periphe | ots and cleared<br>ots<br>ral interrupts | by hardware fo   | r low-priority in | terrupts only |

| bit 5                 | 1 = Enable                                                                                           | pt Priority Enab<br>priority levels o<br>priority levels o                                        | n interrupts                                        |                                          |                  |                   |               |

| bit 4-3               | Unimplemen                                                                                           | ted: Read as 'd                                                                                   | )'                                                  |                                          |                  |                   |               |

| bit 2                 | 1 = Interrup                                                                                         | tternal Interrup<br>t on rising edge<br>t on falling edge                                         | e of INT2 pin                                       | ect bit                                  |                  |                   |               |

| bit 1                 | 1 = Interrup                                                                                         | tternal Interrupt<br>t on rising edge<br>t on falling edge                                        | e of INT1 pin                                       |                                          |                  |                   |               |

| bit 0                 | 1 = Interrup                                                                                         | tternal Interrupi<br>t on rising edge<br>t on falling edge                                        | e of INT0 pin                                       |                                          |                  |                   |               |

| cc<br>its<br>er<br>th | terrupt flag bits a<br>ondition occurs, r<br>corresponding<br>nable bit. User s<br>e appropriate int | egardless of the<br>enable bit or the<br>software should<br>errupt flag bits                      | e state of<br>ne global<br>d ensure<br>are clear    |                                          |                  |                   |               |

prior to enabling an interrupt. This feature

allows for software polling.

#### 21.5.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for standard PWM operation:

- Use the desired output pin RxyPPS control to select CCPx as the source and disable the CCPx pin output driver by setting the associated TRIS bit.

- 2. Load the PR2 register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- 4. Load the CCPRxL register, and the CCPRxH register with the PWM duty cycle value and configure the FMT bit of the CCPxCON register to set the proper register alignment.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR4 register. See Note below.

- Select the timer clock source to be as FOSC/4 using the TxCLKCON register. This is required for correct operation of the PWM module.

- Configure the T2CKPS bits of the T2CON register with the Timer prescale value.

- Enable the Timer by setting the ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until the Timer overflows and the TMR2IF bit of the PIR4 register is set. See Note below.

- Enable the CCPx pin output driver by clearing the associated TRIS bit.

**Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

#### 21.5.3 TIMER2 TIMER RESOURCE

The PWM standard mode makes use of the 8-bit Timer2 timer resources to specify the PWM period.

### 21.5.4 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 21-1.

#### EQUATION 21-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)

Note 1: Tosc = 1/Fosc

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is transferred from the CCPRxL/H register pair into a 10-bit buffer.

Note: The Timer postscaler (see Section 20.4 "Timer2 Interrupt") is not used in the determination of the PWM frequency.

PIC18(L)F24/25K40

#### 26.10.8 ACKNOWLEDGE SEQUENCE TIMING

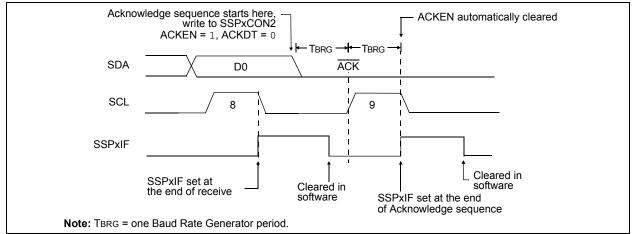

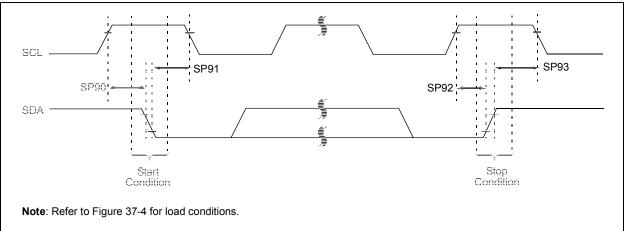

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPxCON2 register. When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 26-30).

#### 26.10.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

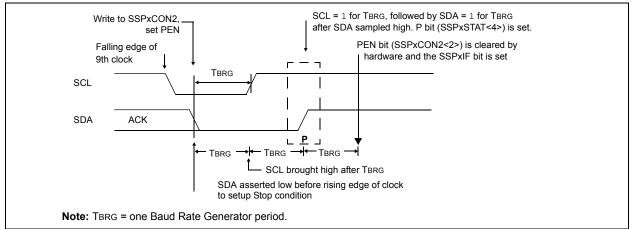

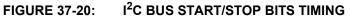

#### 26.10.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPxCON2 register. At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit of the SSPxSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 26-31).

#### 26.10.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

### FIGURE 26-30: ACKNOWLEDGE SEQUENCE WAVEFORM

#### FIGURE 26-31: STOP CONDITION RECEIVE OR TRANSMIT MODE

#### 27.2.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCxSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCxREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCxSTA register which resets the EUSART. Clearing the CREN bit of the RCxSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive   |

|-------|--------------------------------------------|

|       | FIFO have framing errors, repeated reads   |

|       | of the RCxREG will not clear the FERR bit. |

#### 27.2.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCxSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCxSTA register or by resetting the EUSART by clearing the SPEN bit of the RCxSTA register.

#### 27.2.2.6 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCxSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCxSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCxREG.

#### 27.2.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCxSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCxIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

ADC<sup>2</sup> BLOCK DIAGRAM

## TABLE 31-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES<sup>(1,4)</sup>

| ADC C               | lock Period (TAD)   |                         |                         | Device                | Frequency (I          | Fosc)                  |                        |                         |

|---------------------|---------------------|-------------------------|-------------------------|-----------------------|-----------------------|------------------------|------------------------|-------------------------|

| ADC<br>Clock Source | ADCS<5:0>           | 64 MHz                  | 32 MHz                  | 20 MHz                | 16 MHz                | 8 MHz                  | 4 MHz                  | 1 MHz                   |

| Fosc/2              | 000000              | 31.25 ns <sup>(2)</sup> | 62.5 ns <sup>(2)</sup>  | 100 ns <sup>(2)</sup> | 125 ns <sup>(2)</sup> | 250 ns <sup>(2)</sup>  | 500 ns <sup>(2)</sup>  | 2.0 μs                  |

| Fosc/4              | 000001              | 62.5 ns <sup>(2)</sup>  | 125 ns <sup>(2)</sup>   | 200 ns <sup>(2)</sup> | 250 ns <sup>(2)</sup> | 500 ns <sup>(2)</sup>  | 1.0 μs                 | 4.0 μs                  |

| Fosc/6              | 000010              | 125 ns <sup>(2)</sup>   | 187.5 ns <sup>(2)</sup> | 300 ns <sup>(2)</sup> | 375 ns <sup>(2)</sup> | 750 ns <sup>(2)</sup>  | 1.5 μs                 | 6.0 μs                  |

| Fosc/8              | 000011              | 187.5 ns <sup>(2)</sup> | 250 ns <sup>(2)</sup>   | 400 ns <sup>(2)</sup> | 500 ns <sup>(2)</sup> | 1.0 μs                 | 2.0 μs                 | 8.0 μs <sup>(3)</sup>   |

|                     |                     |                         |                         |                       |                       |                        |                        |                         |

| Fosc/16             | 000100              | 250 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 800 ns <sup>(2)</sup> | 1.0 μs                | 2.0 μs                 | 4.0 μs                 | 16.0 μs <sup>(3)</sup>  |

|                     |                     |                         |                         |                       |                       |                        |                        |                         |

| Fosc/128            | 111111              | 2.0 μs                  | 4.0 μs                  | 6.4 μs                | 8.0 μs                | 16.0 μs <sup>(3)</sup> | 32.0 μs <sup>(2)</sup> | 128.0 μs <sup>(2)</sup> |

| FRC                 | ADCS(ADCON0<4>) = 1 | 1.0-6.0 μs              | 1.0-6.0 μs              | 1.0-6.0 μs            | 1.0-6.0 μs            | 1.0-6.0 μs             | 1.0-6.0 μs             | 1.0-6.0 μs              |

Legend: Shaded cells are outside of recommended range.

Note 1: See TAD parameter for FRC source typical TAD value.

2: These values violate the required TAD time.

- **3:** Outside the recommended TAD time.

- 4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the FRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

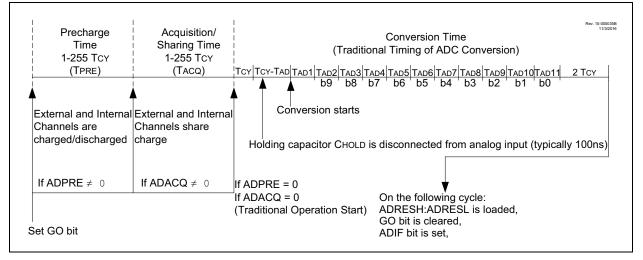

### FIGURE 31-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

#### 31.2.6 ADC CONVERSION PROCEDURE (BASIC MODE)

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- · Disable pin output driver (Refer to the TRISx register)

- · Configure pin as analog (Refer to the ANSELx register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- · Configure voltage reference

- Select ADC input channel (precharge+acquisition)

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- · Clear ADC interrupt flag

- · Enable ADC interrupt

- Enable peripheral interrupt (PEIE bit)

- Enable global interrupt (GIE bit)<sup>(1)</sup>

- 4. If ADACQ = 0, software must wait the required acquisition time<sup>(2)</sup>.

- Start conversion by setting the ADGO bit. 5.

- Wait for ADC conversion to complete by one of 6. the following:

- · Polling the ADGO bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

The global interrupt can be disabled if the Note 1: user is attempting to wake-up from Sleep and resume in-line code execution.

> 2: Refer to Section 31.3 "ADC Acquisition Requirements".

#### EXAMPLE 31-1:

ADC CONVERSION ;This code block configures the ADC ; for polling, VDD and Vss references, FRC ;oscillator and ANO input. ;Conversion start & polling for completion ;are included. BANKSEL ADCON1 ; B'11110000' ;Right justify, MOVLW ;FRC oscillator MOVWF ADCON1 ;Vdd and Vss Vref BANKSEL TRISA ; BSF TRISA,0 ;Set RA0 to input BANKSEL ANSEL ; BSF ANSEL,0 ;Set RA0 to analog BANKSEL ADCON0 B'00000001' ;Select channel AN0 MOVLW MOVWF ADCON0 ;Turn ADC On SampleTime ; Acquisiton delay CALL ADCON0, ADGO ; Start conversion BSF BTFSC ADCON0, ADGO ; Is conversion done? GOTO \$-1 ;No, test again ; BANKSEL ADRESH ADRESH,W ;Read upper 2 bits MOVF MOVWF RESULTHI ;store in GPR space BANKSEL ADRESL ; MOVF ADRESL,W ;Read lower 8 bits MOVWF RESULTIO ;Store in GPR space

-n/n = Value at POR and BOR/Value at all other Resets

#### REGISTER 31-27: ADERRL: ADC SETPOINT ERROR LOW BYTE REGISTER

x = Bit is unknown

| R-x              | R-x | R-x              | R-x  | R-x          | R-x              | R-x    | R-x   |

|------------------|-----|------------------|------|--------------|------------------|--------|-------|

|                  |     |                  | ADER | R<7:0>       |                  |        |       |

| bit 7            |     |                  |      |              |                  |        | bit 0 |

|                  |     |                  |      |              |                  |        |       |

| Legend:          |     |                  |      |              |                  |        |       |

| R = Readable bit |     | W = Writable bit |      | U = Unimpler | nented bit, reac | as '0' |       |

| '1' = Bit is set | '0' = Bit is cleared                                                                          |

|------------------|-----------------------------------------------------------------------------------------------|

|                  |                                                                                               |

| bit 7-0          | ADERR<7:0>: ADC Setpoint Error LSB Lower byte of ADC Setpoint Error calculation is determined |

bit 7-0 **ADERR<7:0>**: ADC Setpoint Error LSB. Lower byte of ADC Setpoint Error calculation is determined by ADCALC bits of ADCON3, see Register 23-1 for more details.

#### REGISTER 31-28: ADLTHH: ADC LOWER THRESHOLD HIGH BYTE REGISTER

| R/W-x/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ADLTH   | <15:8>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADLTH<15:8>**: ADC Lower Threshold MSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

#### REGISTER 31-29: ADLTHL: ADC LOWER THRESHOLD LOW BYTE REGISTER

| R/W-x/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ADLTH   | 1<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADLTH<7:0>**: ADC Lower Threshold LSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

© 2016-2017 Microchip Technology Inc.

u = Bit is unchanged

|                  | R/W-x/x |                   | R/W-x/x |                | R/W-x/x          |                |              |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

| R/W-x/x          | R/W-X/X | R/W-x/x           | R/W-X/X | R/W-x/x        | R/W-X/X          | R/W-x/x        | R/W-x/x      |

|                  |         |                   | ADUTH   | H<15:8>        |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable b    | bit     | U = Unimpler   | nented bit, read | 1 as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | own     | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ired    |                |                  |                |              |

#### REGISTER 31-30: ADUTHH: ADC UPPER THRESHOLD HIGH BYTE REGISTER

bit 7-0 **ADUTH<15:8>**: ADC Upper Threshold MSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

#### REGISTER 31-31: ADUTHL: ADC UPPER THRESHOLD LOW BYTE REGISTER

| R/W-x/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ADUTH   | 1<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADUTH<7:0>**: ADC Upper Threshold LSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

# PIC18(L)F24/25K40

| ΒZ          |                                                    | Branch if                                                                 | Zero                                                                                                                      |                                                    |

|-------------|----------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Synta       | ax:                                                | BZ n                                                                      |                                                                                                                           |                                                    |

| Oper        | ands:                                              | -128 ≤ n ≤ 1                                                              | 127                                                                                                                       |                                                    |

| Oper        | ation:                                             | if ZERO bit<br>(PC) + 2 + 2                                               |                                                                                                                           |                                                    |

| Statu       | is Affected:                                       | None                                                                      |                                                                                                                           |                                                    |

| Enco        | oding:                                             | 1110                                                                      | 0000 nnr                                                                                                                  | in nnnn                                            |

| Desc        | ription:                                           | will branch.<br>The 2's con<br>added to th<br>have incren<br>instruction, | ) bit is '1', then<br>nplement numl<br>e PC. Since th<br>nented to fetch<br>the new addre<br>n. This instruct<br>ruction. | ber '2n' is<br>e PC will<br>the next<br>ss will be |

| Word        | ds:                                                | 1                                                                         |                                                                                                                           |                                                    |

| Cycle       | es:                                                | 1(2)                                                                      |                                                                                                                           |                                                    |

|             | ycle Activity:<br>imp:                             |                                                                           |                                                                                                                           |                                                    |

|             | Q1                                                 | Q2                                                                        | Q3                                                                                                                        | Q4                                                 |

|             | Decode                                             | Read literal<br>'n'                                                       | Process<br>Data                                                                                                           | Write to PC                                        |

|             | No<br>operation                                    | No<br>operation                                                           | No<br>operation                                                                                                           | No<br>operation                                    |

| lf No       | o Jump:                                            |                                                                           |                                                                                                                           |                                                    |

|             | Q1                                                 | Q2                                                                        | Q3                                                                                                                        | Q4                                                 |

|             | Decode                                             | Read literal<br>'n'                                                       | Process<br>Data                                                                                                           | No<br>operation                                    |

| <u>Exan</u> | Before Instruc<br>PC                               | = ad                                                                      | BZ Jump<br>dress (HERE)                                                                                                   |                                                    |

|             | After Instructio<br>If ZERO<br>PC<br>If ZERO<br>PC | = 1;<br>= ad<br>= 0;                                                      | dress (Jump)<br>dress (HERE                                                                                               |                                                    |

| CALL                                                | Subroutin                                                                                                                                                             |                                                                                                                              |                                                                                         |                                                                                                                                  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                             | CALL k {,                                                                                                                                                             | s}                                                                                                                           |                                                                                         |                                                                                                                                  |

| Operands:                                           | $\begin{array}{l} 0 \leq k \leq 104 \\ s \in [0,1] \end{array}$                                                                                                       | 8575                                                                                                                         |                                                                                         |                                                                                                                                  |

| Operation:                                          | $\begin{array}{l} (PC) + 4 \rightarrow \\ k \rightarrow PC < 20 \\ \text{if } s = 1 \\ (W) \rightarrow WS \\ (Status) \rightarrow \\ (BSR) \rightarrow B \end{array}$ | ):1>,<br>,<br>STATUS                                                                                                         | S,                                                                                      |                                                                                                                                  |

| Status Affected:                                    | None                                                                                                                                                                  |                                                                                                                              |                                                                                         |                                                                                                                                  |

| Encoding:<br>1st word (k<7:0>)<br>2nd word(k<19:8>) | 1110<br>1111                                                                                                                                                          | 110s<br>k <sub>19</sub> kkk                                                                                                  | k <sub>7</sub> kk<br>kkkł                                                               |                                                                                                                                  |

|                                                     | memory rai<br>(PC + 4) is                                                                                                                                             |                                                                                                                              |                                                                                         |                                                                                                                                  |

|                                                     | stack. If 's'<br>registers ar<br>respective<br>STATUSS a<br>update occ<br>20-bit value<br>CALL is a                                                                   | = 1, the '<br>re also pu<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                                                 | W, State<br>ushed in<br>register<br>S. If 's'<br>out). Th<br>ided inte                  | us and BS<br>nto their<br>rs, WS,<br>= 0, no<br>nen, the<br>to PC<20:                                                            |

| Words:                                              | registers ar<br>respective<br>STATUSS a<br>update occ<br>20-bit value                                                                                                 | = 1, the '<br>re also pu<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                                                 | W, State<br>ushed in<br>register<br>S. If 's'<br>out). Th<br>ided inte                  | us and BS<br>nto their<br>rs, WS,<br>= 0, no<br>nen, the<br>to PC<20:                                                            |

| Words:<br>Cycles:                                   | registers ar<br>respective<br>STATUSS a<br>update occ<br>20-bit value<br>CALL is a                                                                                    | = 1, the '<br>re also pu<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                                                 | W, State<br>ushed in<br>register<br>S. If 's'<br>out). Th<br>ided inte                  | us and BS<br>nto their<br>rs, WS,<br>= 0, no<br>nen, the<br>to PC<20:                                                            |

|                                                     | registers ar<br>respective<br>STATUSS a<br>update occ<br>20-bit value<br>CALL is a<br>2                                                                               | = 1, the '<br>re also pu<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                                                 | W, State<br>ushed in<br>register<br>S. If 's'<br>out). Th<br>ided inte                  | us and BS<br>nto their<br>rs, WS,<br>= 0, no<br>nen, the<br>to PC<20:                                                            |

| Cycles:                                             | registers ar<br>respective<br>STATUSS a<br>update occ<br>20-bit value<br>CALL is a<br>2                                                                               | = 1, the '<br>re also pu<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa                                                 | W, Statu<br>ushed in<br>register<br>S. If 's'<br>ult). Th<br>ded intu<br>nstructio      | us and BS<br>nto their<br>rs, WS,<br>= 0, no<br>nen, the<br>to PC<20:                                                            |

| Cycles:<br>Q Cycle Activity:                        | registers ar<br>respective<br>STATUSS a<br>update occ<br>20-bit value<br>CALL is a<br>2<br>2<br>2                                                                     | = 1, the '<br>re also pu<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa<br>2-cycle ir                                   | W, Statu<br>register<br>S. If 's'<br>ult). Th<br>ded intr<br>astructions<br>PC to<br>sk | us and BS<br>nto their<br>rs, WS,<br>= 0, no<br>nen, the<br>o PC<20:<br>on.                                                      |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>No  | registers ar<br>respective<br>STATUSS a<br>update occ<br>20-bit value<br>CALL is a<br>2<br>2<br>2<br>Q2<br>Read literal<br>'k'<7:0>,                                  | = 1, the <sup>1</sup><br>re also pu<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa<br>2-cycle ir<br>Q3<br>PUSHF<br>stac | W, Statu<br>register<br>S. If 's'<br>ult). Th<br>ded into<br>astructions<br>PC to<br>ck | us and BS<br>nto their<br>'s, WS,<br>= 0, no<br>nen, the<br>o PC<20:<br>on.<br>Q4<br>Read liter<br>'k'<19:82<br>Write to F<br>No |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode        | registers ar<br>respective<br>STATUSS a<br>update occ<br>20-bit value<br>CALL is a<br>2<br>2<br>2<br>Q2<br>Read literal<br>'k'<7:0>,                                  | = 1, the <sup>1</sup><br>re also pu<br>shadow r<br>and BSR<br>urs (defa<br>e 'k' is loa<br>2-cycle ir<br>Q3<br>PUSHF<br>stac | W, Statu<br>register<br>S. If 's'<br>ult). Th<br>ded into<br>astructions<br>PC to<br>ck | us and BS<br>nto their<br>'s, WS,<br>= 0, no<br>hen, the<br>o PC<20:<br>on.<br>Q4<br>Read liter<br>'k'<19:82<br>Write to F       |

|    |             | (,                                     |                                                        |

|----|-------------|----------------------------------------|--------------------------------------------------------|

| on |             |                                        |                                                        |

| =  |             |                                        |                                                        |

| =  | address     | (HERE +                                | 4)                                                     |

| =  | W           |                                        |                                                        |

| =  | BSR         |                                        |                                                        |

| S= | Status      |                                        |                                                        |

|    | =<br>=<br>= | = address<br>= address<br>= W<br>= BSR | = address (THERE)<br>= address (HERE +<br>= W<br>= BSR |

# PIC18(L)F24/25K40

| MULLW Multiply literal with                                                                                                                                                                                                                                                                                                                                                |                                                                    |                     |                   |                                                                          |                                      |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------|-------------------|--------------------------------------------------------------------------|--------------------------------------|--|--|--|--|

| Synt                                                                                                                                                                                                                                                                                                                                                                       | ax:                                                                | MULLW               | MULLW k           |                                                                          |                                      |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                                       | ands:                                                              | $0 \le k \le 2$     | $0 \le k \le 255$ |                                                                          |                                      |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                                       | ration:                                                            | (W) x k –           | → PRODH           | :PRODL                                                                   |                                      |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                                                                                                                      | is Affected:                                                       | None                |                   |                                                                          |                                      |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                                                                                                                       | oding:                                                             | 0000                | 1101              | kkkk                                                                     | kkkk                                 |  |  |  |  |

| Description: An unsigned multiplication is carr<br>out between the contents of W ar<br>8-bit literal 'k'. The 16-bit result is<br>placed in the PRODH:PRODL rep<br>pair. PRODH contains the high by<br>W is unchanged.<br>None of the Status flags are affect<br>Note that neither overflow nor car<br>possible in this operation. A zero<br>is possible but not detected. |                                                                    |                     |                   | W and the<br>ult is<br>L register<br>gh byte.<br>affected.<br>r carry is |                                      |  |  |  |  |

| Word                                                                                                                                                                                                                                                                                                                                                                       | ds:                                                                | 1                   |                   |                                                                          |                                      |  |  |  |  |

| Cycle                                                                                                                                                                                                                                                                                                                                                                      | es:                                                                | 1                   | 1                 |                                                                          |                                      |  |  |  |  |