Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25k40-e-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

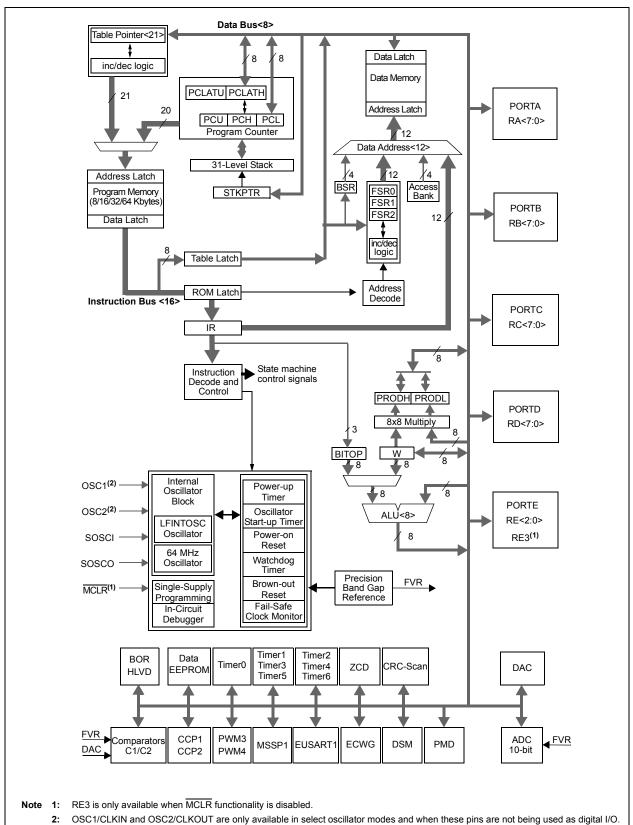

### FIGURE 1-1: PIC18(L)F24/25K40 FAMILY BLOCK DIAGRAM

2: OSC1/CLKIN and OSC2/CLKOUT are only available in select oscillator modes and when these pins are not being used as digital I/O. Refer to Section 4.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional information.

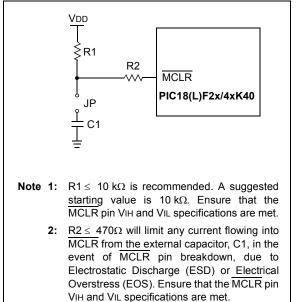

# 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: Device Reset, and Device Programming and Debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the MCLR pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

# 2.4 ICSP<sup>™</sup> Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 36.0 "Development Support"**.

| ······································                               |             |                  |                                           |       |       |                |       |  |  |

|----------------------------------------------------------------------|-------------|------------------|-------------------------------------------|-------|-------|----------------|-------|--|--|

| U-1                                                                  | U-1         | U-1              | U-1                                       | R/W-1 | R/W-1 | R/W-1          | R/W-1 |  |  |

| _                                                                    | _           | _                | _                                         | WRT3  | WRT2  | WRT1           | WRT0  |  |  |

| bit 7                                                                |             |                  |                                           |       | •     |                | bit 0 |  |  |

|                                                                      |             |                  |                                           |       |       |                |       |  |  |

| Legend:                                                              |             |                  |                                           |       |       |                |       |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '1' |             |                  |                                           |       |       |                |       |  |  |

| -n = Value for bl                                                    | lank device | '1' = Bit is set | = Bit is set '0' = Bit is cleared x = Bit |       |       | x = Bit is unk | nown  |  |  |

|                                                                      |             |                  |                                           |       |       |                |       |  |  |

### Register 3-7: Configuration Word 4L (30 0006h): Memory Write Protection

| bit 7-4 Unimplemented: Read as '1' |  |

|------------------------------------|--|

|------------------------------------|--|

bit 3-0 WRT<3:0>: User NVM Self-Write Protection bits<sup>(1)</sup>

1 = Corresponding Memory Block NOT write-protected

0 = Corresponding Memory Block write-protected

Note 1: Refer to Table 10-2 for details on implementation of the individual WRT bits.

### Register 3-8: Configuration Word 4H (30 0007h): Memory Write Protection

| U-1   | U-1 | R/W-1 | R/W-1 | U-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-----|-------|-------|-------|

| _     | -   | LVP   | SCANE | _   | WRTD  | WRTB  | WRTC  |

| bit 7 |     |       |       |     |       |       | bit 0 |

| Legend:                     |                  |                            |                    |  |

|-----------------------------|------------------|----------------------------|--------------------|--|

| R = Readable bit            | W = Writable bit | U = Unimplemented bit, rea | id as '1'          |  |

| -n = Value for blank device | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |  |

| bit 7-6 | Unimplemented: Read as '1'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | <ul> <li>LVP: Low-Voltage Programming Enable bit</li> <li>1 = Low-voltage programming enabled. MCLR/VPP pin function is MCLR. MCLRE Configuration bit is ignored.<br/>The LVP bit cannot be written (to zero) while operating from the LVP programming interface. The purpose of this rule is to prevent the user from dropping out of LVP mode while programming from LVP mode, or accidentally eliminating LVP mode from the Configuration state.</li> <li>0 = HV on MCLR/VPP must be used for programming</li> </ul> |

| bit 4   | <ul> <li>SCANE: Scanner Enable bit</li> <li>1 = Scanner module is available for use, SCANMD bit enables the module</li> <li>0 = Scanner module is NOT available for use, SCANMD bit is ignored</li> </ul>                                                                                                                                                                                                                                                                                                               |

| bit 3   | Unimplemented: Read as '1'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 2   | <ul> <li>WRTD: Data EEPROM Write Protection bit</li> <li>1 = Data EEPROM NOT write-protected</li> <li>0 = Data EEPROM write-protected</li> </ul>                                                                                                                                                                                                                                                                                                                                                                        |

| bit 1   | <ul> <li>WRTB: Boot Block Write Protection bit</li> <li>1 = Boot Block NOT write-protected</li> <li>0 = Boot Block write-protected</li> </ul>                                                                                                                                                                                                                                                                                                                                                                           |

| bit 0   | <ul> <li>WRTC: Configuration Register Write Protection bit</li> <li>1 = Configuration Register NOT write-protected</li> <li>0 = Configuration Register write-protected</li> </ul>                                                                                                                                                                                                                                                                                                                                       |

#### 5.5 **Register Definitions: Reference Clock**

Long bit name prefixes for the Reference Clock peripherals are shown in Table 5-1. Refer to Section 1.4.2.2 "Long Bit Names" for more information. TABLE 5-1:

#### Porinheral Dif Norm

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| CLKR       | CLKR            |

#### **REGISTER 5-1: CLKRCON: REFERENCE CLOCK CONTROL REGISTER**

| R/W-0/0 | U-0 | U-0 | R/W-1/1 | R/W-0/0 | R/W-0/0  | R/W-0/0 R/W-0/0 |       |

|---------|-----|-----|---------|---------|----------|-----------------|-------|

| EN      | _   |     | DC<1:0> |         | DIV<2:0> |                 |       |

| bit 7   |     |     |         |         |          |                 | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: Reference Clock Module Enable bit                                                                  |

|---------|--------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Reference clock module enabled</li> <li>0 = Reference clock module is disabled</li> </ul> |

| bit 6-5 | Unimplemented: Read as '0'                                                                             |

|         | •                                                                                                      |

| bit 4-3 | DC<1:0>: Reference Clock Duty Cycle bits <sup>(1)</sup>                                                |

|         | 11 = Clock outputs duty cycle of 75%                                                                   |

|         | 10 = Clock outputs duty cycle of 50%                                                                   |

|         | 01 = Clock outputs duty cycle of 25%                                                                   |

|         | 00 = Clock outputs duty cycle of 0%                                                                    |

|         |                                                                                                        |

| bit 2-0 | DIV<2:0>: Reference Clock Divider bits                                                                 |

|         | 111 = Base clock value divided by 128                                                                  |

|         | 110 = Base clock value divided by 64                                                                   |

|         | 101 = Base clock value divided by 32                                                                   |

|         | 100 = Base clock value divided by 16                                                                   |

|         | 011 = Base clock value divided by 8                                                                    |

|         | 010 = Base clock value divided by 4                                                                    |

|         | 001 = Base clock value divided by 2                                                                    |

|         | 000 = Base clock value                                                                                 |

|         |                                                                                                        |

Note 1: Bits are valid for reference clock divider values of two or larger, the base clock cannot be further divided.

### REGISTER 11-5: NVMDAT: DATA EEPROM MEMORY DATA

| R/W-0/0         | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0          | R/W-0/0          | R/W-0/0  | R/W-0/0 |

|-----------------|---------|-------------------|---------|------------------|------------------|----------|---------|

|                 |         |                   | NVMD    | AT<7:0>          |                  |          |         |

| bit 7           |         |                   |         |                  |                  |          | bit 0   |

|                 |         |                   |         |                  |                  |          |         |

| Legend:         |         |                   |         |                  |                  |          |         |

| R = Readable    | bit     | W = Writable I    | bit     | U = Unimpler     | nented bit, read | d as '0' |         |

| x = Bit is unkn | own     | '0' = Bit is clea | ared    | '1' = Bit is set |                  |          |         |

| -n = Value at F | POR     |                   |         |                  |                  |          |         |

bit 7-0 **NVMDAT<7:0>:** The value of the data memory word returned from NVMADR after a Read command, or the data written by a Write command.

### TABLE 11-5: SUMMARY OF REGISTERS ASSOCIATED WITH DATA EEPROM MEMORY

| Name                   | Bit 7                                        | Bit 6          | Bit 5 | Bit 4 | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|------------------------|----------------------------------------------|----------------|-------|-------|---------|---------|---------|---------|---------------------|

| NVMCON1                | NVMRE                                        | G<1:0>         | —     | FREE  | WRERR   | WREN    | WR      | RD      | 141                 |

| NVMCON2                |                                              | Unlock Pattern |       |       |         |         |         |         |                     |

| NVMADRL                |                                              |                |       | NVMA  | DR<7:0> |         |         |         | 142                 |

| NVMADRH <sup>(1)</sup> | — — — — — NVMADR<9:8>                        |                |       |       |         |         |         |         | 142                 |

| NVMDAT                 | NVMDAT<7:0>                                  |                |       |       |         |         |         |         | 143                 |

| TBLPTRU                | Program Memory Table Pointer (TBLPTR<21:16>) |                |       |       |         |         |         |         | 123*                |

| TBLPTRH                | Program Memory Table Pointer (TBLPTR<15:8>)  |                |       |       |         |         |         |         | 123*                |

| TBLPTRL                | Program Memory Table Pointer (TBLPTR<7:0>)   |                |       |       |         |         |         |         | 123*                |

| TABLAT                 | TABLAT                                       |                |       |       |         |         |         | 122*    |                     |

| INTCON                 | GIE/GIEH                                     | PEIE/GIEL      | IPEN  | —     | —       | INT2EDG | INT1EDG | INT0EDG | 166                 |

| PIE7                   | SCANIE                                       | CRCIE          | NVMIE | —     | —       | —       | —       | CWG1IE  | 182                 |

| PIR7                   | SCANIF                                       | CRCIF          | NVMIF | _     | _       | _       | _       | CWG1IF  | 174                 |

| IPR7                   | SCANIP                                       | CRCIP          | NVMIP | —     | —       | _       | —       | CWG1IP  | 190                 |

Legend: — = unimplemented, read as '0'. Shaded bits are not used during EEPROM access.

\*Page provides register information.

Note 1: The NVMADRH register is not implemented on PIC18(L)F24/25K40.

# 16.0 INTERRUPT-ON-CHANGE

PORTA, PORTB, PORTC and pin RE3 of PORTE can be configured to operate as Interrupt-on-Change (IOC) pins on PIC18(L)F2x/4xK40 family devices. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual port pin, or combination of port pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 16-1 is a block diagram of the IOC module.

## 16.1 Enabling the Module

To allow individual port pins to generate an interrupt, the IOCIE bit of the PIE0 register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

## 16.2 Individual Pin Configuration

For each port pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both associated bits of the IOCxP and IOCxN registers, respectively.

# 16.3 Interrupt Flags

The IOCAFx, IOCBFx, IOCCFx and IOCEF3 bits located in the IOCAF, IOCBF, IOCCF and IOCEF registers respectively, are status flags that correspond to the interrupt-on-change pins of the associated port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the PIRO register reflects the status of all IOCAFx, IOCBFx, IOCCFx and IOCEF3 bits.

# 16.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx, IOCBFx, IOCCFx and IOCEF3 bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

### EXAMPLE 16-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

| MOVLW | 0xff   |              |

|-------|--------|--------------|

| XORWF | IOCAF, | W            |

| ANDWF | IOCAF, | F            |

|       |        |              |

|       | XORWF  | XORWF IOCAF, |

# 16.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCxF register will be updated prior to the first instruction executed out of Sleep.

### 16.6 Register Definitions: Interrupt-on-Change Control

| R/W-0/0           | R/W-0/0                               | R/W-0/0            | R/W-0/0 | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|-------------------|---------------------------------------|--------------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|

| IOCxP7            | IOCxP6                                | IOCxP5             | IOCxP4  | IOCxP3                                                | IOCxP2  | IOCxP1  | IOCxP0  |  |  |

| bit 7             |                                       |                    |         |                                                       |         |         | bit 0   |  |  |

|                   |                                       |                    |         |                                                       |         |         |         |  |  |

| Legend:           |                                       |                    |         |                                                       |         |         |         |  |  |

| R = Readable bi   | t                                     | W = Writable bi    | t       | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is unchan | = Bit is unchanged x = Bit is unknown |                    | wn      | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

| '1' = Bit is set  |                                       | '0' = Bit is clear | ed      |                                                       |         |         |         |  |  |

### **REGISTER 16-1:** IOCxP: INTERRUPT-ON-CHANGE POSITIVE EDGE REGISTER EXAMPLE

bit 7-0

IOCxP<7:0>: Interrupt-on-Change Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the IOCx pin for a positive-going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

### REGISTER 16-2: IOCxN: INTERRUPT-ON-CHANGE NEGATIVE EDGE REGISTER EXAMPLE

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCxN7  | IOCxN6  | IOCxN5  | IOCxN4  | IOCxN3  | IOCxN2  | IOCxN1  | IOCxN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

IOCxN<7:0>: Interrupt-on-Change Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the IOCx pin for a negative-going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin

### REGISTER 16-3: IOCxF: INTERRUPT-ON-CHANGE FLAG REGISTER EXAMPLE

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCxF7     | IOCxF6     | IOCxF5     | IOCxF4     | IOCxF3     | IOCxF2     | IOCxF1     | IOCxF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

IOCxF<7:0>: Interrupt-on-Change Flag bits

1 = A enabled change was detected on the associated pin. Set when IOCP[n] = 1 and a positive edge was detected on the IOCn pin, or when IOCN[n] = 1 and a negative edge was detected on the IOCn pin

0 = No change was detected, or the user cleared the detected change

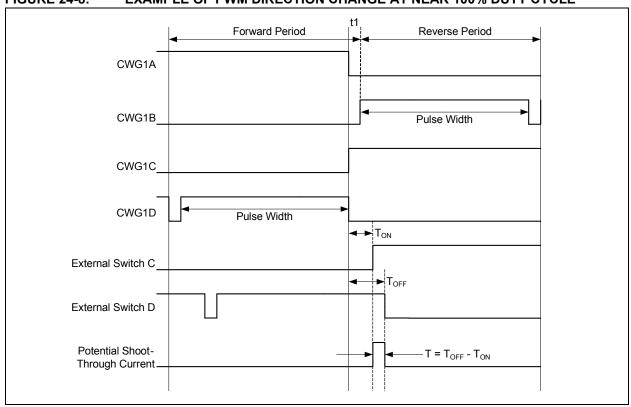

# 24.2.3.1 Direction Change in Full-Bridge Mode

In Full-Bridge mode, changing MODE<2:0> controls the forward/reverse direction. Changes to MODE<2:0> change to the new direction on the next rising edge of the modulated input.

A direction change is initiated in software by changing the MODE<2:0> bits of the CWG1CON0 register. The sequence is illustrated in Figure 24-8.

- The associated active output CWG1A and the inactive output CWG1C are switched to drive in the opposite direction.

- The previously modulated output CWG1D is switched to the inactive state, and the previously inactive output CWG1B begins to modulate.

- CWG modulation resumes after the directionswitch dead band has elapsed.

# 24.2.3.2 Dead-Band Delay in Full-Bridge Mode

Dead-band delay is important when either of the following conditions is true:

- The direction of the CWG output changes when the duty cycle of the data input is at or near 100%, or

- 2. The turn-off time of the power switch, including the power device and driver circuit, is greater than the turn-on time.

The dead-band delay is inserted only when changing directions, and only the modulated output is affected. The statically-configured outputs (CWG1A and CWG1C) are not afforded dead band, and switch essentially simultaneously.

Figure 24-8 shows an example of the CWG outputs changing directions from forward to reverse, at near 100% duty cycle. In this example, at time t1, the output of CWG1A and CWG1D become inactive, while output CWG1C becomes active. Since the turn-off time of the power devices is longer than the turn-on time, a shootthrough current will flow through power devices QC and QD for the duration of 't'. The same phenomenon will occur to power devices QA and QB for the CWG direction change from reverse to forward.

When changing the CWG direction at high duty cycle is required for an application, two possible solutions for eliminating the shoot-through current are:

- 1. Reduce the CWG duty cycle for one period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

# FIGURE 24-8: EXAMPLE OF PWM DIRECTION CHANGE AT NEAR 100% DUTY CYCLE

© 2016-2017 Microchip Technology Inc.

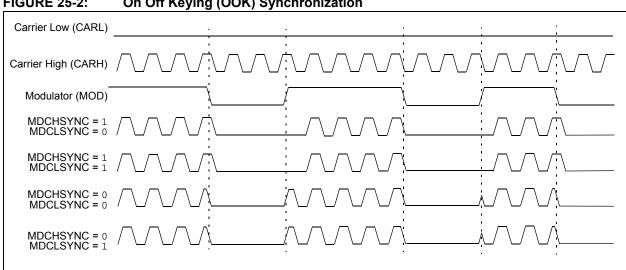

#### **FIGURE 25-2: On Off Keying (OOK) Synchronization**

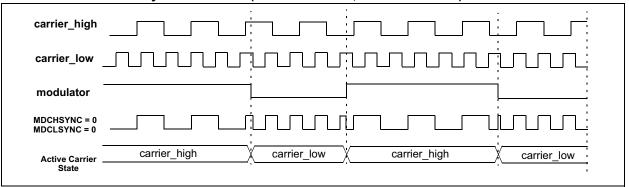

FIGURE 25-4: Carrier High Synchronization (MDSHSYNC = 1, MDCLSYNC = 0)

| carrier_high                 |                                                                     |

|------------------------------|---------------------------------------------------------------------|

| carrier_low                  |                                                                     |

| modulator                    |                                                                     |

| MDCHSYNC = 1<br>MDCLSYNC = 0 |                                                                     |

| Active Carrier<br>State      | carrier_high / both carrier_low / carrier_high / both \ carrier_low |

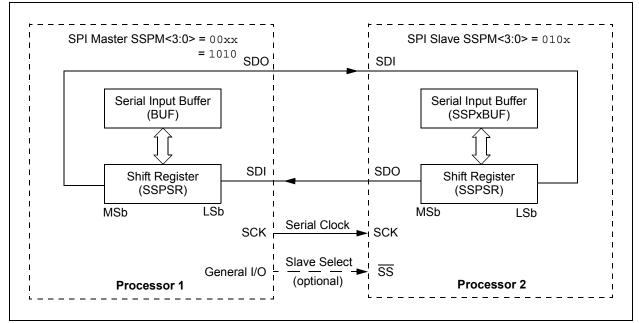

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF of the SSPxSTAT register, indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPxBUF register. Additionally, the SSPxSTAT register indicates the various Status conditions.

### FIGURE 26-3: SPI MASTER/SLAVE CONNECTION

### 26.10.3 WCOL STATUS FLAG

If the user writes the SSPxBUF when a Start, Restart, Stop, Receive or Transmit sequence is in progress, the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur). Any time the WCOL bit is set it indicates that an action on SSPxBUF was attempted while the module was not idle.

| Note: | Because queuing of events is not allowed,  |

|-------|--------------------------------------------|

|       | writing to the lower five bits of SSPxCON2 |

|       | is disabled until the Start condition is   |

|       | complete.                                  |

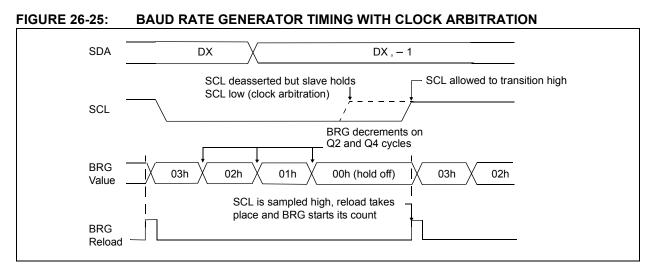

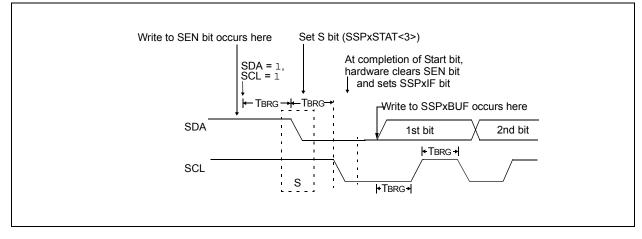

### 26.10.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition (Figure 26-26), the user sets the Start Enable bit, SEN bit of the SSPxCON2 register. If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is

FIGURE 26-26: FIRST START BIT TIMING

the Start condition and causes the S bit of the SSPxSTAT1 register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPxCON2 register will be automatically cleared by hardware; the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

- Note 1: If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLxIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

- **2:** The Philips I<sup>2</sup>C specification states that a bus collision cannot occur on a Start.

© 2016-2017 Microchip Technology Inc.

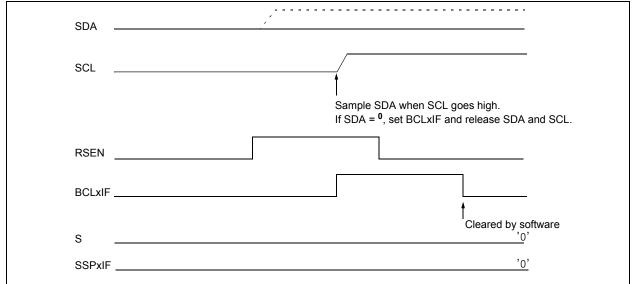

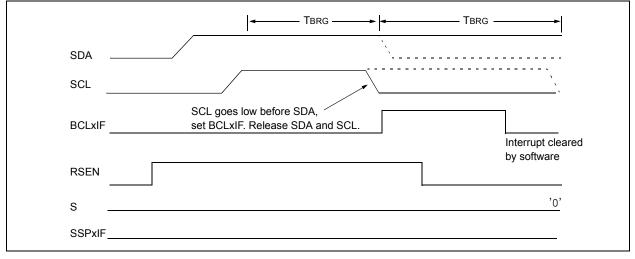

# 26.10.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level (Case 1).

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1' (Case 2).

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPxADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 26-36). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 26-37.

If, at the end of the BRG time out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

FIGURE 26-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

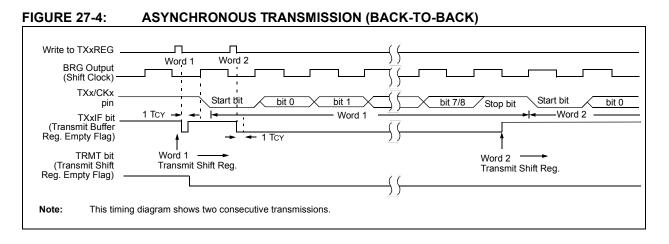

### TABLE 27-1: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name     | Bit 7    | Bit 6     | Bit 5   | Bit 4      | Bit 3         | Bit 2      | Bit 1   | Bit 0   | Register<br>on Page |

|----------|----------|-----------|---------|------------|---------------|------------|---------|---------|---------------------|

| BAUDxCON | ABDOVF   | RCIDL     | —       | SCKP       | BRG16         |            | WUE     | ABDEN   | 389                 |

| INTCON   | GIE/GIEH | PEIE/GIEL | IPEN    |            | _             | INT2EDG    | INT1EDG | INT0EDG | 166                 |

| PIE3     | —        | _         | RC1IE   | TX1IE      | _             |            | BCL1IE  | SSP1IE  | 178                 |

| PIR3     | —        | _         | RC1IF   | TX1IF      | _             |            | BCL1IF  | SSP1IF  | 170                 |

| IPR3     | —        | —         | RC1IP   | TX1IP      | _             | -          | BCL1IP  | SSP1IP  | 186                 |

| RCxSTA   | SPEN     | RX9       | SREN    | CREN       | ADDEN         | FERR       | OERR    | RX9D    | 388                 |

| RxyPPS   | —        | —         | _       |            |               | RxyPPS<4:0 | >       |         | 213                 |

| TXxPPS   | —        | —         | _       |            |               | TXPPS<4:0  | >       |         | 211                 |

| SPxBRGH  |          |           | EUSARTx | Baud Rate  | Generator, H  | ligh Byte  |         |         | 398*                |

| SPxBRGL  |          |           | EUSARTx | Baud Rate  | Generator, I  | ow Byte    |         |         | 398*                |

| TXxREG   |          |           | EU      | SARTx Tran | ismit Registe | er         |         |         | 390*                |

| TXxSTA   | CSRC     | TX9       | TXEN    | SYNC       | SENDB         | BRGH       | TRMT    | TX9D    | 387                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for asynchronous transmission. \* Page provides register information.

### FIGURE 27-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

| :<br>              |                       | :<br>:<br>:::::::::::::::::::::::::::::::::: | :<br>//////////////////////////////////// | :<br>//////////////////////////////////// | Ciparati<br>IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII | ora (n' Spire Farm.<br>111111111111111111111111111111111111 | n en      | :::::::::::::::::::::::::::::::::::::: |  |

|--------------------|-----------------------|----------------------------------------------|-------------------------------------------|-------------------------------------------|--------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------|----------------------------------------|--|

| 1.302<br>          | :<br>:<br>            | :<br>:<br>                                   | : 444774<br>: 4                           |                                           | <br>·····                                        | ·····                                                       | с ,<br>, ,<br>, , , , , , , , , , , , , , , , | ·····                                  |  |

| - 280 (390 99)<br> |                       |                                              |                                           |                                           | -                                                |                                                             | r .<br>Geografia                              | · · · · · · · · · · · · · · · · · · ·  |  |

| 1 1255-0           | aat ary doodae i mini | ананананананананананананананананананан       |                                           |                                           | <br>                                             | andara.                                                     | ,                                             | - Auto-Meored                          |  |

© 2016-2017 Microchip Technology Inc.

| FIGURE 27-12:                                       | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                               |

|-----------------------------------------------------|-------------------------------------------------------------------------|

| RXx/DTx<br>pin<br>TXx/CKx pin<br>(SCKP = 0)         | X     bit 0     bit 2     bit 3     bit 4     bit 5     bit 6     bit 7 |

| TXx/CKx pin<br>(SCKP = 1)<br>Write to<br>bit SREN   |                                                                         |

| SREN bit                                            | ·0,                                                                     |

| RCxIF bit<br>(Interrupt) ———<br>Read<br>RCxREG ———— |                                                                         |

|                                                     | gram demonstrates Sync Master mode with bit SREN = 1 and bit BRGH = 0.  |

# TABLE 27-8:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>RECEPTION

| Name     | Bit 7    | Bit 6     | Bit 5   | Bit 4       | Bit 3         | Bit 2       | Bit 1   | Bit 0   | Register<br>on Page |

|----------|----------|-----------|---------|-------------|---------------|-------------|---------|---------|---------------------|

| ANSELB   | ANSELB7  | ANSELB6   | ANSELB5 | ANSELB4     | ANSELB3       | ANSELB2     | ANSELB1 | ANSELB0 | 199                 |

| ANSELC   | ANSELC7  | ANSELC6   | ANSELC5 | ANSELC4     | ANSELC3       | ANSELC2     | ANSELC1 | ANSELC0 | 199                 |

| BAUDxCON | ABDOVF   | RCIDL     | _       | SCKP        | BRG16         | —           | WUE     | ABDEN   | 389                 |

| INTCON   | GIE/GIEH | PEIE/GIEL | IPEN    | —           | _             | INT2EDG     | INT1EDG | INT0EDG | 166                 |

| PIE3     | _        | _         | RC1IE   | TX1IE       | —             | —           | BCL1IE  | SSP1IE  | 178                 |

| PIR3     |          | —         | RC1IF   | TX1IF       | —             | —           | BCL1IF  | SSP1IF  | 170                 |

| IPR3     | _        | —         | RC1IP   | TX1IP       | —             | _           | BCL1IP  | SSP1IP  | 186                 |

| RCxREG   |          |           | EUS     | ARTx Receiv | e Data Regis  | ter         |         |         | 393*                |

| RCxSTA   | SPEN     | RX9       | SREN    | CREN        | ADDEN         | FERR        | OERR    | RX9D    | 388                 |

| RxyPPS   | _        | _         | _       |             | F             | RxyPPS<4:0> |         |         | 213                 |

| RXxPPS   | _        | —         | _       |             |               | RXPPS<4:0>  |         |         | 211                 |

| SPxBRGH  |          |           | EUSART  | Baud Rate   | Generator, Hi | gh Byte     |         |         | 398*                |

| SPxBRGL  |          |           | EUSART  | x Baud Rate | Generator, Lo | ow Byte     |         |         | 398*                |

| TXxSTA   | CSRC     | TX9       | TXEN    | SYNC        | SENDB         | BRGH        | TRMT    | TX9D    | 387                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master reception.

\* Page provides register information.

### 32.2 Register Definitions: Comparator Control

Long bit name prefixes for the Comparators are shown in Table 32-1. Refer to **Section 1.4.2.2 "Long Bit Names"** for more information.

### TABLE 32-1:

| Peripheral | Bit Name Prefix |  |  |  |

|------------|-----------------|--|--|--|

| C1         | C1              |  |  |  |

| C2         | C2              |  |  |  |

### REGISTER 32-1: CMxCON0: COMPARATOR x CONTROL REGISTER 0

| R/W-0/0   | R-0/0 | U-0 | R/W-0/0 | U-0 | U-1 | R/W-0/0 | R/W-0/0 |  |

|-----------|-------|-----|---------|-----|-----|---------|---------|--|

| EN        | OUT   | —   | POL     | —   | —   | HYS     | SYNC    |  |

| bit 7 bit |       |     |         |     |     |         |         |  |

| Legend:           |                                                               |                      |                    |  |  |

|-------------------|---------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | dable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                              | '0' = Bit is cleared | x = Bit is unknown |  |  |

| bit 7 | EN: Comparator Enable bit                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | <ul> <li>1 = Comparator is enabled</li> <li>0 = Comparator is disabled and consumes no active power</li> </ul>                                                                                                                                                    |  |  |  |  |  |  |

| bit 6 | OUT: Comparator Output bit                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|       | $\frac{\text{If POL} = 0 \text{ (non-inverted polarity)}}{1 = CxVP > CxVN}$ $0 = CxVP < CxVN$ $\frac{\text{If POL} = 1 \text{ (inverted polarity)}}{1 = CxVP < CxVN}$                                                                                             |  |  |  |  |  |  |

|       | 0 = CxVP > CxVN                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| bit 5 | Unimplemented: Read as '0'                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| bit 4 | POL: Comparator Output Polarity Select bit                                                                                                                                                                                                                        |  |  |  |  |  |  |

|       | <ul> <li>1 = Comparator output is inverted</li> <li>0 = Comparator output is not inverted</li> </ul>                                                                                                                                                              |  |  |  |  |  |  |

| bit 3 | Unimplemented: Read as '0'                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| bit 2 | Unimplemented: Read as '1'                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| bit 1 | HYS: Comparator Hysteresis Enable bit                                                                                                                                                                                                                             |  |  |  |  |  |  |

|       | <ul> <li>1 = Comparator hysteresis enabled</li> <li>0 = Comparator hysteresis disabled</li> </ul>                                                                                                                                                                 |  |  |  |  |  |  |

| bit 0 | SYNC: Comparator Output Synchronous Mode bit                                                                                                                                                                                                                      |  |  |  |  |  |  |

|       | <ul> <li>1 = Comparator output to Timer1/3/5 and I/O pin is synchronous to changes on Timer1 clock source.</li> <li>0 = Comparator output to Timer1/3/5 and I/O pin is asynchronous<br/>Output updated on the falling edge of Timer1/3/5 clock source.</li> </ul> |  |  |  |  |  |  |

# 32.4 Comparator Hysteresis

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See Comparator Specifications in Table 37-15 for more information.

# 32.5 Timer1/3/5 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1/3/5. See **Section 19.8 "Timer1/3/5 Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

### 32.5.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from a comparator can be synchronized with Timer1 by setting the SYNC bit of the CMxCON0 register.

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 32-2) and the Timer1 Block Diagram (Figure 19-1) for more information.

## 32.6 Comparator Interrupt

An interrupt can be generated upon a change in the output value of the comparator for each comparator, a rising edge detector and a falling edge detector are present.

When either edge detector is triggered and its associated enable bit is set (CxINTP and/or CxINTN bits of the CMxCON1 register), the Corresponding Interrupt Flag bit (CxIF bit of the PIR2 register) will be set.

To enable the interrupt, you must set the following bits:

- EN and POL bits of the CMxCON0 register

- CxIE bit of the PIE2 register

- INTP bit of the CMxCON1 register (for a rising edge detection)

- INTN bit of the CMxCON1 register (for a falling edge detection)

- PEIE and GIE bits of the INTCON register

The associated interrupt flag bit, CxIF bit of the PIR2 register, must be cleared in software. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

**Note:** Although a comparator is disabled, an interrupt can be generated by changing the output polarity with the CxPOL bit of the CMxCON0 register, or by switching the comparator on or off with the CxEN bit of the CMxCON0 register.

# 32.7 Comparator Positive Input Selection

Configuring the PCH<2:0> bits of the CMxPCH register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- CxIN0+, CxIN1+ analog pin

- DAC output

- FVR (Fixed Voltage Reference)

- AVss (Ground)

See Section 28.0 "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 30.0 "5-Bit Digital-to-Analog Converter (DAC) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxEN = 0), all comparator inputs are disabled.

## 32.8 Comparator Negative Input Selection

The NCH<2:0> bits of the CMxNCH register direct an analog input pin and internal reference voltage or analog ground to the inverting input of the comparator:

- · CxIN0-, CxIN1-, CxIN2-, CxIN3- analog pin

- FVR (Fixed Voltage Reference)

- Analog Ground

Note: To use CxINy+ and CxINy- pins as analog input, the appropriate bits must be set in the ANSEL register and the corresponding TRIS bits must also be set to disable the output drivers.

# PIC18(L)F24/25K40

| DEC         | FSZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SZ Decrement f, skip if 0                                                          |                | DCF               | SNZ                                                                                                                                                                                                                                                                                             | Decrement f, skip if not 0                                                                                                                                                                                                                                                                                                                         |                                                       |                                                                                             |                 |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------|--|--|

| Synta       | ax:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DECFSZ f {,d {,a}}                                                                 |                | Synta             | ix:                                                                                                                                                                                                                                                                                             | DCFSNZ f {,d {,a}}                                                                                                                                                                                                                                                                                                                                 |                                                       |                                                                                             |                 |  |  |

| Oper        | ands:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$ |                | Opera             | ands:                                                                                                                                                                                                                                                                                           | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                 |                                                       |                                                                                             |                 |  |  |

| Oper        | ation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $(f) - 1 \rightarrow dest,$<br>skip if result = 0                                  |                | Opera             | ation:                                                                                                                                                                                                                                                                                          | (f) – 1 $\rightarrow$ de skip if resul                                                                                                                                                                                                                                                                                                             |                                                       |                                                                                             |                 |  |  |

| Statu       | is Affected:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | None                                                                               |                |                   | Status                                                                                                                                                                                                                                                                                          | s Affected:                                                                                                                                                                                                                                                                                                                                        | None                                                  |                                                                                             |                 |  |  |

| Enco        | oding:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0010                                                                               | 11da ffi       | ff ffff           | Enco                                                                                                                                                                                                                                                                                            | Encoding:                                                                                                                                                                                                                                                                                                                                          |                                                       | 11da fff                                                                                    | ff ffff         |  |  |

| Desc        | ription:<br>The contents of register 'f' are<br>decremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If the result is '0', the next instruction,<br>which is already fetched, is discarded<br>and a NOP is executed instead, making<br>it a 2-cycle instruction.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 35.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit-<br>eral Offset Mode" for details. |                                                                                    | Desc           | ription:          | decremente<br>placed in W<br>placed back<br>if the result<br>instruction,<br>discarded a<br>instead, ma<br>instruction.<br>If 'a' is '0', tt<br>If 'a' is '0', tt<br>If 'a' is '0', tt<br>GPR bank.<br>If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode wher<br>tion 35.2.3<br>Oriented Ir | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the GPR bank.<br>If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever $f \le 95$ (5Fh). See Section 35.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Lit- |                                                       |                                                                                             |                 |  |  |

| Word        | ds:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                  |                |                   |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                    |                                                       | Mode" for de                                                                                | tails.          |  |  |

| Cycle       | es:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1(2)                                                                               |                |                   | Word                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                    | 1                                                     |                                                                                             |                 |  |  |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>Note:</b> 3 cycles if skip and followed by a 2-word instruction.                |                |                   | Cycle                                                                                                                                                                                                                                                                                           | Cycles:                                                                                                                                                                                                                                                                                                                                            |                                                       | <ul><li>1(2)</li><li>Note: 3 cycles if skip and followed by a 2-word instruction.</li></ul> |                 |  |  |

| QC          | ycle Activity:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 00                                                                                 | 00             | 04                | 0.0                                                                                                                                                                                                                                                                                             | cle Activity:                                                                                                                                                                                                                                                                                                                                      | Uy                                                    |                                                                                             |                 |  |  |

|             | Q1<br>Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Q2<br>Read                                                                         | Q3<br>Process  | Q4<br>Write to    |                                                                                                                                                                                                                                                                                                 | Q1                                                                                                                                                                                                                                                                                                                                                 | Q2                                                    | Q3                                                                                          | Q4              |  |  |

|             | Decoue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | register 'f'                                                                       | Data           | destination       |                                                                                                                                                                                                                                                                                                 | Decode                                                                                                                                                                                                                                                                                                                                             | Read                                                  | Process                                                                                     | Write to        |  |  |

| lf sk       | ip:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                    |                |                   |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                    | register 'f'                                          | Data                                                                                        | destination     |  |  |