#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 28-SPDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25k40-i-sp |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

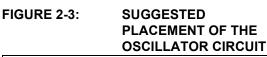

# 2.5 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to Section 4.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-3. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate website (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

# 2.6 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

|                                         |       |                   |              | •                | ,                |              |         |

|-----------------------------------------|-------|-------------------|--------------|------------------|------------------|--------------|---------|

| R-0/0                                   | R-0/0 | R-0/0             | R-0/0        | R-0/0            | R-0/0            | R-0/0        | R-0/0   |

|                                         |       | WDTTMR<4:0>       |              |                  | STATE            | PSCNT        | <17:16> |

| bit 7                                   |       |                   |              |                  | ·                |              | bit 0   |

|                                         |       |                   |              |                  |                  |              |         |

| Legend:                                 |       |                   |              |                  |                  |              |         |

| R = Readable bit W = Writable bit       |       |                   | U = Unimpler | mented bit, read | l as '0'         |              |         |

| u = Bit is unchanged x = Bit is unknown |       |                   | -n/n = Value | at POR and BO    | R/Value at all o | other Resets |         |

| '1' = Bit is set                        |       | '0' = Bit is clea | ared         |                  |                  |              |         |

### REGISTER 9-5: WDTTMR: WDT TIMER REGISTER (READ-ONLY)

bit 7-3 WDTTMR<4:0>: Watchdog Window Value bits

|        | WDT Win     | Onen Dersent |              |

|--------|-------------|--------------|--------------|

| WINDOW | Closed      | Open         | Open Percent |

| 111    | N/A         | 00000-11111  | 100          |

| 110    | 00000-00011 | 00100-11111  | 87.5         |

| 101    | 00000-00111 | 01000-11111  | 75           |

| 100    | 00000-01011 | 01100-11111  | 62.5         |

| 011    | 00000-01111 | 10000-11111  | 50           |

| 010    | 00000-10011 | 10100-11111  | 37.5         |

| 001    | 00000-10111 | 11000-11111  | 25           |

| 000    | 00000-11011 | 11100-11111  | 12.5         |

bit 2 STATE: WDT Armed Status bit

1 = WDT is armed

0 = WDT is not armed

# bit 1-0 **PSCNT<17:16>:** Prescale Select Upper Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

# 9.7 Operation During Sleep

When the device enters Sleep, the WWDT is cleared. If the WWDT is enabled during Sleep, the WWDT resumes counting. When the device exits Sleep, the WWDT is cleared again.

The WWDT remains clear until the Oscillator Start-up Timer (OST) completes, if enabled. See **Section 4.3.1.3 "Oscillator Start-up Timer (OST)**" for more information on the OST.

When a WWDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. The RWDT bit in the PCON0 register can also be used. See **Section 10.0 "Memory Organization"** for more information.

## TABLE 9-2: WWDT CLEARING CONDITIONS

| Conditions                                              | WWDT                         |

|---------------------------------------------------------|------------------------------|

| WDTE<1:0> = 00                                          |                              |

| WDTE<1:0> = 01 and SEN = 0                              |                              |

| WDTE<1:0> = 10 and enter Sleep                          | Cleared                      |

| CLRWDT Command                                          | Cleared                      |

| Oscillator Fail Detected                                |                              |

| Exit Sleep + System Clock = SOSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                  | Cleared until the end of OST |

| Change INTOSC divider (IRCF bits)                       | Unaffected                   |

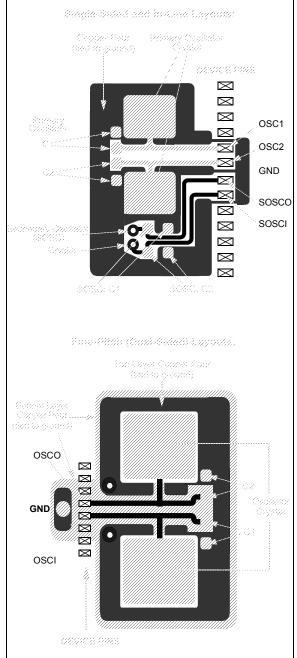

# FIGURE 9-2: WINDOW PERIOD AND DELAY

© 2016-2017 Microchip Technology Inc.

## 10.4.5 STATUS REGISTER

The STATUS register, shown in Register 10-2, contains the arithmetic status of the ALU. As with any other SFR, it can be the operand for any instruction.

If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, the results of the instruction are not written; instead, the STATUS register is updated according to the instruction performed. Therefore, the result of an instruction with the STATUS register as its destination may be different than intended. As an example, CLRF STATUS will set the Z bit and leave the remaining Status bits unchanged ('000u u1uu').

It is recommended that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register.

For other instructions that do not affect Status bits, see the instruction set summaries in **Section 35.0 "Instruction Set Summary"** and Table 35-3.

Note: The C and DC bits operate as the borrow and digit borrow bits, respectively, in subtraction.

| EXAMPLE 11-4: | WRITING TO PROGRAM FLASH MEMORY |

|---------------|---------------------------------|

|               |                                 |

|              | MOVLW          | D'64′                     | ; number of bytes in erase block                 |

|--------------|----------------|---------------------------|--------------------------------------------------|

|              | MOVWF          | COUNTER                   |                                                  |

|              | MOVLW          | BUFFER_ADDR_HIGH          | ; point to buffer                                |

|              | MOVWF          | FSROH                     |                                                  |

|              | MOVLW          | BUFFER_ADDR_LOW           |                                                  |

|              | MOVWF          | FSROL                     |                                                  |

|              | MOVLW          | CODE_ADDR_UPPER           | ; Load TBLPTR with the base                      |

|              | MOVWF          | TBLPTRU                   | ; address of the memory block                    |

|              | MOVLW          | CODE_ADDR_HIGH            |                                                  |

|              | MOVWF          | TBLPTRH                   |                                                  |

|              | MOVLW          | CODE_ADDR_LOW             |                                                  |

|              | MOVWF          | TBLPTRL                   |                                                  |

| READ_BLOCK   |                |                           |                                                  |

|              | TBLRD*+        |                           | ; read into TABLAT, and inc                      |

|              | MOVE           | TABLAT, W                 | ; get data                                       |

|              | MOVWF          | POSTINCO                  | ; store data                                     |

|              | DECFSZ<br>BRA  | COUNTER<br>READ_BLOCK     | ; done?                                          |

| MODIFY_WORD  | BRA            | READ_BLOCK                | ; repeat                                         |

| MODIFI_WORD  | MOVLW          | BUFFER_ADDR_HIGH          | ; point to buffer                                |

|              | MOVLW          | FSROH                     | , point to barrer                                |

|              | MOVLW          | BUFFER_ADDR_LOW           |                                                  |

|              | MOVWF          | FSROL                     |                                                  |

|              | MOVLW          | NEW_DATA_LOW              | ; update buffer word                             |

|              | MOVWF          | POSTINCO                  |                                                  |

|              | MOVLW          | NEW_DATA_HIGH             |                                                  |

|              | MOVWF          | INDF0                     |                                                  |

| ERASE_BLOCK  |                |                           |                                                  |

|              | MOVLW          | CODE_ADDR_UPPER           | ; load TBLPTR with the base                      |

|              | MOVWF          | TBLPTRU                   | ; address of the memory block                    |

|              | MOVLW          | CODE_ADDR_HIGH            |                                                  |

|              | MOVWF          | TBLPTRH                   |                                                  |

|              | MOVLW          | CODE_ADDR_LOW             |                                                  |

|              | MOVWF          | TBLPTRL                   |                                                  |

|              | BCF            | NVMCON1, NVMREG0          | ; point to Program Flash Memory                  |

|              | BSF            | NVMCON1, NVMREG1          | ; point to Program Flash Memory                  |

|              | BSF            | NVMCON1, WREN             | ; enable write to memory                         |

|              | BSF            | NVMCON1, FREE             | ; enable Erase operation                         |

|              | BCF            | INTCON, GIE               | ; disable interrupts                             |

|              | MOVLW          | 55h                       |                                                  |

| Required     | MOVWF          | NVMCON2                   | ; write 55h                                      |

| Sequence     | MOVLW          | AAh<br>Mumaon2            | · write 077b                                     |

|              | MOVWF          | NVMCON2                   | ; write OAAh                                     |

|              | BSF            | NVMCON1, WR               | ; start erase (CPU stall)                        |

|              | BSF<br>TBLRD*- | INTCON, GIE               | ; re-enable interrupts<br>; dummy read decrement |

|              | MOVLW          | BUFFFF ADDD UTCU          | ; point to buffer                                |

|              | MOVLW<br>MOVWF | BUFFER_ADDR_HIGH<br>FSR0H | , Potne co parter                                |

|              | MOVWF          | BUFFER_ADDR_LOW           |                                                  |

|              | MOVLW          | FSROL                     |                                                  |

| WRITE_BUFFER |                | 1 511015                  |                                                  |

|              | MOVLW          | BlockSize                 | ; number of bytes in holding register            |

|              | MOVWF          | COUNTER                   |                                                  |

|              | MOVLW          | D'64'/BlockSize           | ; number of write blocks in 64 bytes             |

|              | MOVWF          | COUNTER2                  |                                                  |

|              |                |                           |                                                  |

|              |                |                           |                                                  |

| R/W-0/0                     | R/W-0/0 | R/W-0/0                                             | R/W-0/0 | R/W-0/0                                             | R/W-0/0 | R/W-0/0 | R/W-0/0     |  |  |

|-----------------------------|---------|-----------------------------------------------------|---------|-----------------------------------------------------|---------|---------|-------------|--|--|

| LADR<7:0> <sup>(1, 2)</sup> |         |                                                     |         |                                                     |         |         |             |  |  |

| bit 7                       |         |                                                     |         |                                                     |         |         | bit 0       |  |  |

|                             |         |                                                     |         |                                                     |         |         |             |  |  |

| Legend:                     |         |                                                     |         |                                                     |         |         |             |  |  |

| R = Readable                | bit     | W = Writable bit U = Unimplemented bit, read as '0' |         |                                                     |         |         |             |  |  |

| u = Bit is uncha            | anged   | x = Bit is unkn                                     | iown    | n -n/n = Value at POR and BOR/Value at all other Re |         |         | ther Resets |  |  |

| '1' = Bit is set            |         | '0' = Bit is clea                                   | ared    |                                                     |         |         |             |  |  |

#### REGISTER 13-14: SCANLADRL: SCAN LOW ADDRESS LOW BYTE REGISTER

# bit 7-0 LADR<7:0>: Scan Start/Current Address bits<sup>(1, 2)</sup> Least Significant bits of the current address to be fetched from, value increments on each fetch of memory

- **Note 1:** Registers SCANLADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

- 2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

#### REGISTER 13-15: SCANHADRU: SCAN HIGH ADDRESS UPPER BYTE REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | —   |         |         | HADR    | <21:16> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| Dit 7-6 Unimplemented: Read as U | bit 7-6 | Unimplemented: Read as '0' |

|----------------------------------|---------|----------------------------|

|----------------------------------|---------|----------------------------|

bit 5-0 **HADR<21:16>:** Scan End Address bits<sup>(1, 2)</sup> Upper bits of the address at the end of the designated scan

- **Note 1:** Registers SCANHADRU/H/L form a 22-bit value but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

- 2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

| bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7       OSCFIF: Oscillator Fail Interrupt Flag bit         1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by softwore)         0 = Device clock operating         bit 6       CSWIF: Clock-Switch Interrupt Flag bit( <sup>1)</sup> 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt Has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                               | R/W-0/0                                                              | ) R/W-0/0            | U-0                   | U-0           | U-0              | U-0            | R/W-0/0          | R/W-0/0         |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------|-----------------------|---------------|------------------|----------------|------------------|-----------------|--|

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7       OSCFIF: Oscillator Fail Interrupt Flag bit       1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by softwore)         bit 6       CSWIF: Clock-Switch Interrupt Flag bit <sup>(1)</sup> 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold interrupt Flag bit         1 = ADC Threshold interrupt Has occurred (must be cleared by software)         0 = ADC Threshold interrupt Flag bit         1 = ADC Threshold interrupt Has occurred (must be cleared by software)         0 = ADC Threshold interrupt Flag bit         1 = ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)   | OSCFIF                                                               | CSWIF <sup>(1)</sup> | —                     | _             | _                | _              | ADTIF            | ADIF            |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7       OSCFIF: Oscillator Fail Interrupt Flag bit       1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by softwore)         bit 6       CSWIF: Clock-Switch Interrupt Flag bit <sup>(1)</sup> 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold interrupt Flag bit         1 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software) | bit 7                                                                | ·                    |                       |               |                  |                |                  | bit 0           |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7       OSCFIF: Oscillator Fail Interrupt Flag bit       1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by softwore)         bit 6       CSWIF: Clock-Switch Interrupt Flag bit <sup>(1)</sup> 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold interrupt Flag bit         1 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software) |                                                                      |                      |                       |               |                  |                |                  |                 |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7       OSCFIF: Oscillator Fail Interrupt Flag bit       1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by softwork)         bit 6       CSWIF: Clock-Switch Interrupt Flag bit <sup>(1)</sup> 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                           | Legend:                                                              |                      |                       |               |                  |                |                  |                 |  |

| bit 7       OSCFIF: Oscillator Fail Interrupt Flag bit         1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by softwork)         0 = Device clock operating         bit 6       CSWIF: Clock-Switch Interrupt Flag bit <sup>(1)</sup> 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                           | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                       |               |                  |                |                  |                 |  |

| <ul> <li>1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by softwore) = Device clock operating</li> <li>bit 6</li> <li>CSWIF: Clock-Switch Interrupt Flag bit<sup>(1)</sup></li> <li>1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started</li> <li>bit 5-2</li> <li>Unimplemented: Read as '0'</li> <li>bit 1</li> <li>ADTIF: ADC Threshold Interrupt Flag bit</li> <li>1 = ADC Threshold interrupt has occurred (must be cleared by software)</li> <li>0 = ADC Threshold event is not complete or has not been started</li> <li>bit 0</li> <li>ADIF: ADC Interrupt Flag bit</li> <li>1 = An A/D conversion completed (must be cleared by software)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                     | -n = Value                                                           | at POR               | '1' = Bit is set      |               | '0' = Bit is cle | ared           | x = Bit is unkr  | nown            |  |

| <ul> <li>1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by softwore) = Device clock operating</li> <li>bit 6</li> <li>CSWIF: Clock-Switch Interrupt Flag bit<sup>(1)</sup></li> <li>1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started</li> <li>bit 5-2</li> <li>Unimplemented: Read as '0'</li> <li>bit 1</li> <li>ADTIF: ADC Threshold Interrupt Flag bit</li> <li>1 = ADC Threshold interrupt has occurred (must be cleared by software)</li> <li>0 = ADC Threshold event is not complete or has not been started</li> <li>bit 0</li> <li>ADIF: ADC Interrupt Flag bit</li> <li>1 = An A/D conversion completed (must be cleared by software)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |                      |                       |               |                  |                |                  |                 |  |

| 0 = Device clock operating         bit 6       CSWIF: Clock-Switch Interrupt Flag bit <sup>(1)</sup> 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 7                                                                | OSCFIF: Osc          | cillator Fail Interro | upt Flag bit  |                  |                |                  |                 |  |

| bit 6       CSWIF: Clock-Switch Interrupt Flag bit <sup>(1)</sup> 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold Interrupt Has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      | 1 = Device o         | scillator failed, c   | lock input ha | s changed to I   | HFINTOSC (mu   | ist be cleared b | y software)     |  |

| 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold Interrupt has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                      |                       |               |                  |                |                  |                 |  |

| 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 6                                                                |                      | -                     | -             |                  |                |                  |                 |  |

| bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                      |                      |                       |               |                  |                | e Figure 4-6 ar  | nd Figure 4-7)  |  |

| bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |                      |                       | •             | or has not bee   | n started      |                  |                 |  |

| 1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit 5-2                                                              | Unimplemen           | ited: Read as '0'     |               |                  |                |                  |                 |  |

| 0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 1                                                                |                      |                       |               |                  |                |                  |                 |  |

| bit 0 ADIF: ADC Interrupt Flag bit<br>1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                      |                      |                       |               | •                | •              | e)               |                 |  |

| 1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                      |                       | not complete  | or has not bee   | en started     |                  |                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 0                                                                |                      |                       |               |                  |                |                  |                 |  |

| 0 = 1  ne A/D conversion is not complete or has not been started                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                      |                      |                       |               |                  |                |                  |                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      | 0 = 1  ne A/D        | conversion is not     | complete or   | r nas not been   | started        |                  |                 |  |

| Note 1: The CSWIF interrupt will not wake the system from Sleep. The system will sleep until another i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Note 1:                                                              | The CSWIF inter      | rupt will not wak     | e the systen  | n from Sleep.    | The system wil | I sleep until an | other interrupt |  |

# REGISTER 14-3: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

**Note 1:** The CSWIF interrupt will not wake the system from Sleep. The system will sleep until another interrupt causes the wake-up.

| U-0                                                                  | U-0                                                                           | U-0              | U-0            | U-0              | R/W-0/0 | R/W-0/0         | R/W-0/0 |  |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------|----------------|------------------|---------|-----------------|---------|--|

| —                                                                    | —                                                                             | —                | _              | —                | TMR5GIE | TMR3GIE         | TMR1GIE |  |

| bit 7                                                                |                                                                               |                  |                |                  |         |                 | bit 0   |  |

|                                                                      |                                                                               |                  |                |                  |         |                 |         |  |

| Legend:                                                              |                                                                               |                  |                |                  |         |                 |         |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                               |                  |                |                  |         |                 |         |  |

| -n = Value at F                                                      | POR                                                                           | '1' = Bit is set |                | '0' = Bit is cle | ared    | x = Bit is unkr | iown    |  |

|                                                                      |                                                                               |                  |                |                  |         |                 |         |  |

| bit 7-3                                                              | Unimplemen                                                                    | ted: Read as '   | )'             |                  |         |                 |         |  |

| bit 2                                                                | <b>TMR5GIE:</b> TMR5 Gate Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled |                  |                |                  |         |                 |         |  |

| bit 1                                                                | TMR3GIE: TM<br>1 = Enabled<br>0 = Disabled                                    | /IR3 Gate Inter  | rupt Enable bi | t                |         |                 |         |  |

| bit 0                                                                | <b>TMR1GIE:</b> TM<br>1 = Enabled<br>0 = Disabled                             | /IR1 Gate Inter  | rupt Enable bi | t                |         |                 |         |  |

# REGISTER 14-15: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

# 18.3 **Programmable Prescaler**

A software programmable prescaler is available for exclusive use with Timer0. There are 16 prescaler options for Timer0 ranging in powers of two from 1:1 to 1:32768. The prescaler values are selected using the T0CKPS<3:0> bits of the T0CON1 register.

The prescaler is not directly readable or writable. Clearing the prescaler register can be done by writing to the TMR0L register or the T0CON0, T0CON1 registers or by any Reset.

# 18.4 **Programmable Postscaler**

A software programmable postscaler (output divider) is available for exclusive use with Timer0. There are 16 postscaler options for Timer0 ranging from 1:1 to 1:16. The postscaler values are selected using the TOOUTPS<3:0> bits of the TOCON0 register.

The postscaler is not directly readable or writable. Clearing the postscaler register can be done by writing to the TMR0L register or the T0CON0, T0CON1 registers or by any Reset.

## 18.5 **Operation During Sleep**

When operating synchronously, Timer0 will halt. When operating asynchronously, Timer0 will continue to increment and wake the device from Sleep (if Timer0 interrupts are enabled) provided that the input clock source is active.

# 18.6 Timer0 Interrupts

The Timer0 interrupt flag bit (TMR0IF) is set when either of the following conditions occur:

- 8-bit TMR0L matches the TMR0H value

- 16-bit TMR0 rolls over from 'FFFFh'

When the postscaler bits (T0OUTPS<3:0>) are set to 1:1 operation (no division), the T0IF flag bit will be set with every TMR0 match or rollover. In general, the TMR0IF flag bit will be set every T0OUTPS +1 matches or rollovers.

If Timer0 interrupts are enabled (TMR0IE bit of the PIE0 register = '1'), the CPU will be interrupted and the device may wake from Sleep (see **Section 18.2 "Clock Source Selection"** for more details).

## 18.7 Timer0 Output

The Timer0 output can be routed to any I/O pin via the RxyPPS output selection register (see **Section 17.0 "Peripheral Pin Select (PPS) Module**" for additional information). The Timer0 output can also be used by other peripherals, such as the auto-conversion trigger of the Analog-to-Digital Converter. Finally, the Timer0 output can be monitored through software via the Timer0 output bit (TOOUT) of the TOCON0 register (Register 18-1).

TMR0\_out will be a pulse of one postscaled clock period when a match occurs between TMR0L and PR0 (Period register for TMR0) in 8-bit mode, or when TMR0 rolls over in 16-bit mode. The Timer0 output is a 50% duty cycle that toggles on each TMR0\_out rising clock edge.

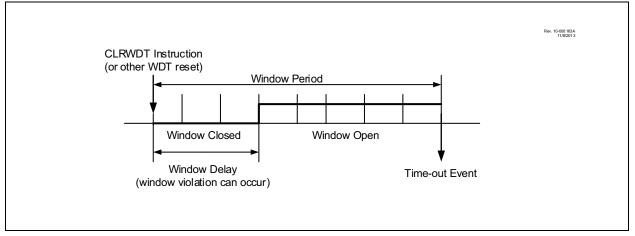

#### 20.5.5 SOFTWARE START ONE-SHOT MODE

In One-Shot mode the timer resets and the ON bit is cleared when the timer value matches the PRx period value. The ON bit must be set by software to start another timer cycle. Setting MODE<4:0> = 01000 selects One-Shot mode which is illustrated in Figure 20-8. In the example, ON is controlled by BSF and BCF instructions. In the first case, a BSF instruction sets ON and the counter runs to completion and clears ON. In the second case, a BSF instruction starts the cycle, BCF/BSF instructions turn the counter off and on during the cycle, and then it runs to completion.

When One-Shot mode is used in conjunction with the CCP PWM operation the PWM pulse drive starts concurrent with setting the ON bit. Clearing the ON bit while the PWM drive is active will extend the PWM drive. The PWM drive will terminate when the timer value matches the CCPRx pulse width value. The PWM drive will remain off until software sets the ON bit to start another cycle. If software clears the ON bit after the CCPRx match but before the PRx match then the PWM drive will be extended by the length of time the ON bit remains cleared. Another timing cycle can only be initiated by setting the ON bit after it has been cleared by a PRx period count match.

FIGURE 20-8: SOFTWARE START ONE-SHOT MODE TIMING DIAGRAM (MODE = 01000)

## 20.5.10 LEVEL-TRIGGERED HARDWARE LIMIT ONE-SHOT MODES

The Level-Triggered Hardware Limit One-Shot modes hold the timer in Reset on an external Reset level and start counting when both the ON bit is set and the external signal is not at the Reset level. If one of either the external signal is not in Reset or the ON bit is set then the other signal being set/made active will start the timer. Reset levels are selected as follows:

- Low Reset level (MODE<4:0> = 10110)

- High Reset level (MODE<4:0> = 10111)

When the timer count matches the PRx period count, the timer is reset and the ON bit is cleared. When the ON bit is cleared by either a PRx match or by software control the timer will stay in Reset until both the ON bit is set and the external signal is not at the Reset level.

When Level-Triggered Hardware Limit One-Shot modes are used in conjunction with the CCP PWM operation the PWM drive goes active with either the external signal edge or the setting of the ON bit, whichever of the two starts the timer.

| R/W/HC-0/0       | R/W-0/0                      | R/W-0/0            | R/W-0/0         | R/W-0/0         | R/W-0/0         | R/W-0/0        | R/W-0/0      |

|------------------|------------------------------|--------------------|-----------------|-----------------|-----------------|----------------|--------------|

| TxON             |                              | CKPS<2:0>          |                 |                 | OUTP            | S<3:0>         |              |

| bit 7            |                              |                    |                 |                 |                 |                | bit          |

|                  |                              |                    |                 |                 |                 |                |              |

| Legend:          |                              |                    |                 |                 |                 |                |              |

| R = Readable     | bit                          | W = Writable I     | bit             | U = Unimplen    | nented bit, rea | d as '0'       |              |

| u = Bit is unch  | nanged                       | x = Bit is unkn    | iown            | -n/n = Value a  | at POR and BC   | R/Value at all | other Resets |

| '1' = Bit is set |                              | '0' = Bit is clea  | ared            | HC = Bit is cle | eared by hardv  | vare           |              |

| bit 7            | ON: Timerx                   | On hit(1)          |                 |                 |                 |                |              |

|                  | 1 = Timerx i                 |                    |                 |                 |                 |                |              |

|                  |                              | s off: all counter | s and state m   | achines are res | et              |                |              |

| bit 6-4          |                              | : Timerx-type Cl   |                 |                 |                 |                |              |

|                  | 111 = 1:128                  | • •                |                 |                 |                 |                |              |

|                  | 110 = 1:64                   |                    |                 |                 |                 |                |              |

|                  | 101 = <b>1:32</b>            |                    |                 |                 |                 |                |              |

|                  | 100 = 1:16 Prescaler         |                    |                 |                 |                 |                |              |

|                  | 011 = 1:8 P                  | rescaler           |                 |                 |                 |                |              |

|                  | 010 = 1:4 P                  |                    |                 |                 |                 |                |              |

|                  | 001 = 1:2 P                  |                    |                 |                 |                 |                |              |

|                  | 000 = 1:1 P                  |                    |                 |                 |                 |                |              |

| bit 3-0          | 1111 = 1:16                  | >: Timerx Outpu    | It Postscaler : | Select Dits     |                 |                |              |

|                  | 1110 = 1.10                  |                    |                 |                 |                 |                |              |

|                  | 1101 = 1:14                  |                    |                 |                 |                 |                |              |

|                  | 1100 = 1:13                  |                    |                 |                 |                 |                |              |

|                  | 1011 = <b>1</b> : <b>1</b> 2 | 2 Postscaler       |                 |                 |                 |                |              |

|                  | 1010 = <b>1</b> : <b>11</b>  | Postscaler         |                 |                 |                 |                |              |

|                  | 1001 = 1:10                  | ) Postscaler       |                 |                 |                 |                |              |

|                  | 1000 = <b>1</b> :9           |                    |                 |                 |                 |                |              |

|                  | 0111 = 1:8                   |                    |                 |                 |                 |                |              |

|                  | 0110 = 1:7 Postscaler        |                    |                 |                 |                 |                |              |

|                  | 0101 = <b>1</b> :6           |                    |                 |                 |                 |                |              |

|                  | 0100 = 1:5<br>0011 = 1:4     |                    |                 |                 |                 |                |              |

|                  | 0011 - 1.4<br>0010 = 1:3     |                    |                 |                 |                 |                |              |

|                  |                              |                    |                 |                 |                 |                |              |

|                  | 0001 = <b>1</b> :2           | Postscaler         |                 |                 |                 |                |              |

# REGISTER 20-1: TxCON: TIMERx CONTROL REGISTER

Note 1: In certain modes, the TxON bit will be auto-cleared by hardware. See Section 20.5 "Operation Examples".

| R/W-0/0       | R/W-1/1                                                                                                                                                                                                                                                                                                              | R/W-0/0                          | R/W-1/1                          | R/W-0/0                                              | R/W-1/1          | R/W-0/0         | R/W-1/1 |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------|------------------------------------------------------|------------------|-----------------|---------|

| P4TSE         | EL<1:0>                                                                                                                                                                                                                                                                                                              | P3TSE                            | L<1:0>                           | C2TSE                                                | EL<1:0>          | C1TSE           | L<1:0>  |

| bit 7         |                                                                                                                                                                                                                                                                                                                      |                                  |                                  |                                                      |                  |                 | bit 0   |

| <b></b>       |                                                                                                                                                                                                                                                                                                                      |                                  |                                  |                                                      |                  |                 |         |

| Legend:       |                                                                                                                                                                                                                                                                                                                      |                                  |                                  |                                                      |                  |                 |         |

| R = Readable  | bit                                                                                                                                                                                                                                                                                                                  | W = Writable                     | bit                              | U = Unimplen                                         | nented bit, read | l as '0'        |         |

| -n = Value at | POR                                                                                                                                                                                                                                                                                                                  | '1' = Bit is set                 |                                  | '0' = Bit is clea                                    | ared             | x = Bit is unkr | nown    |

| bit 7-6       | P4TSEL<1:0>: PWM4 Timer Selection bits<br>11 = PWM4 based on TMR6<br>10 = PWM4 based on TMR4<br>01 = PWM4 based on TMR2<br>00 = Reserved                                                                                                                                                                             |                                  |                                  |                                                      |                  |                 |         |

| bit 5-4       | P3TSEL<1:0>: PWM3 Timer Selection bits<br>11 = PWM3 based on TMR6<br>10 = PWM3 based on TMR4<br>01 = PWM3 based on TMR2<br>00 = Reserved                                                                                                                                                                             |                                  |                                  |                                                      |                  |                 |         |

| bit 3-2       | 11 = CCP2 is<br>10 = CCP2 is                                                                                                                                                                                                                                                                                         | based off Time<br>based off Time | er5 in Capture<br>er3 in Capture | s<br>e/Compare mod<br>e/Compare mod<br>e/Compare mod | le and Timer4 i  | n PWM mode      |         |

| bit 1-0       | <b>C1TSEL&lt;1:0&gt;:</b> CCP1 Timer Selection bits<br>11 = CCP1 is based off Timer5 in Capture/Compare mode and Timer6 in PWM mode<br>10 = CCP1 is based off Timer3 in Capture/Compare mode and Timer4 in PWM mode<br>01 = CCP1 is based off Timer1 in Capture/Compare mode and Timer2 in PWM mode<br>00 = Reserved |                                  |                                  |                                                      |                  |                 |         |

# REGISTER 22-2: CCPTMRS: CCP TIMERS CONTROL REGISTER

| Name   | Bit 7  | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1   | Bit 0   | Register<br>on page |

|--------|--------|-------|--------|--------|-------|--------|---------|---------|---------------------|

| PIE2   | HLVDIE | ZCDIE | _      | _      | _     | —      | C2IE    | C1IE    | 177                 |

| PIR2   | HLVDIF | ZCDIF | _      | _      | _     | _      | C2IF    | C1IF    | 169                 |

| IPR2   | HLVDIP | ZCDIP | _      | _      | _     | _      | C2IP    | C1IP    | 185                 |

| ZCDCON | ZCDSEN | _     | ZCDOUT | ZCDPOL | _     | _      | ZCDINTP | ZCDINTN | 288                 |

| PMD2   | _      | DACMD | ADCMD  |        | _     | CMP2MD | CMP1MD  | ZCDMD   | 66                  |

# TABLE 23-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE ZCD MODULE

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the ZCD module.

# TABLE 23-2: SUMMARY OF CONFIGURATION WORD WITH THE ZCD MODULE

| Name    | Bits | Bit 15/7 | Bit 14/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|----------|----------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG2 | 15:8 | XINST    | _        | DEBUG    | STVREN   | PPS1WAY  | ZCD      | BORV1   | BORV0   | 20                  |

|         | 7:0  | BOREN1   | BOREN0   | LPBOREN  | _        | _        | _        | PWRTE   | MCLRE   |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the ZCD module.

## 26.9.3 SLAVE TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCL pin is held low (see **Section 26.9.6** "**Clock Stretching**" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPSR register. Then the SCL pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. This ACK value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, the SCL pin must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

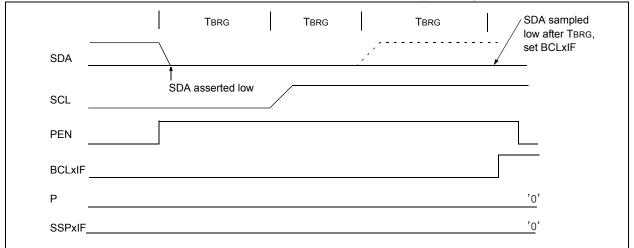

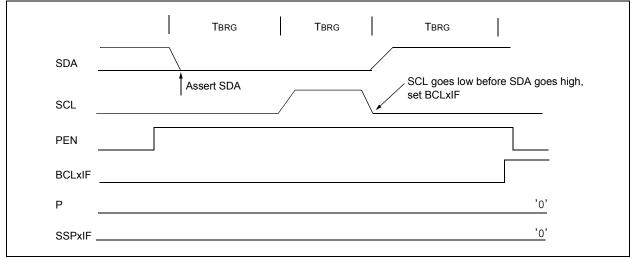

#### 26.9.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDA line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCLxIF bit of the PIR register is set. Once a bus collision is detected, the slave goes idle and waits to be addressed again. User software can use the BCLxIF bit to handle a slave bus collision.

#### 26.9.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 26-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDA and SCL.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with R/W bit set is received by the Slave setting SSPxIF bit.

- 4. Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.