#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

÷ХГ

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-UQFN (4x4)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25k40t-i-mv |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| U-1                         | U-1 | U-1              | U-1 | R/W-1                                   | R/W-1           | R/W-1     | R/W-1 |  |  |

|-----------------------------|-----|------------------|-----|-----------------------------------------|-----------------|-----------|-------|--|--|

| _                           | _   | _                | _   | WRT3                                    | WRT2            | WRT1      | WRT0  |  |  |

| bit 7                       |     |                  |     |                                         | •               |           | bit 0 |  |  |

|                             |     |                  |     |                                         |                 |           |       |  |  |

| Legend:                     |     |                  |     |                                         |                 |           |       |  |  |

| R = Readable b              | it  | W = Writable     | bit | U = Unimple                             | mented bit, rea | ld as '1' |       |  |  |

| -n = Value for blank device |     | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |                 |           | nown  |  |  |

|                             |     |                  |     |                                         |                 |           |       |  |  |

#### Register 3-7: Configuration Word 4L (30 0006h): Memory Write Protection

| bit 7-4 Unimplemented: Read as '1' |  |

|------------------------------------|--|

|------------------------------------|--|

bit 3-0 WRT<3:0>: User NVM Self-Write Protection bits<sup>(1)</sup>

1 = Corresponding Memory Block NOT write-protected

0 = Corresponding Memory Block write-protected

Note 1: Refer to Table 10-2 for details on implementation of the individual WRT bits.

#### Register 3-8: Configuration Word 4H (30 0007h): Memory Write Protection

| U-1   | U-1 | R/W-1 | R/W-1 | U-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-----|-------|-------|-------|

| _     | -   | LVP   | SCANE | _   | WRTD  | WRTB  | WRTC  |

| bit 7 |     |       |       |     |       |       | bit 0 |

| Legend:                                                              |                  |                      |                    |  |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|--|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '1' |                  |                      |                    |  |

| -n = Value for blank device                                          | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 7-6 | Unimplemented: Read as '1'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | <ul> <li>LVP: Low-Voltage Programming Enable bit</li> <li>1 = Low-voltage programming enabled. MCLR/VPP pin function is MCLR. MCLRE Configuration bit is ignored.<br/>The LVP bit cannot be written (to zero) while operating from the LVP programming interface. The purpose of this rule is to prevent the user from dropping out of LVP mode while programming from LVP mode, or accidentally eliminating LVP mode from the Configuration state.</li> <li>0 = HV on MCLR/VPP must be used for programming</li> </ul> |

| bit 4   | <ul> <li>SCANE: Scanner Enable bit</li> <li>1 = Scanner module is available for use, SCANMD bit enables the module</li> <li>0 = Scanner module is NOT available for use, SCANMD bit is ignored</li> </ul>                                                                                                                                                                                                                                                                                                               |

| bit 3   | Unimplemented: Read as '1'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 2   | <ul> <li>WRTD: Data EEPROM Write Protection bit</li> <li>1 = Data EEPROM NOT write-protected</li> <li>0 = Data EEPROM write-protected</li> </ul>                                                                                                                                                                                                                                                                                                                                                                        |

| bit 1   | <ul> <li>WRTB: Boot Block Write Protection bit</li> <li>1 = Boot Block NOT write-protected</li> <li>0 = Boot Block write-protected</li> </ul>                                                                                                                                                                                                                                                                                                                                                                           |

| bit 0   | <ul> <li>WRTC: Configuration Register Write Protection bit</li> <li>1 = Configuration Register NOT write-protected</li> <li>0 = Configuration Register write-protected</li> </ul>                                                                                                                                                                                                                                                                                                                                       |

#### 4.3.2.6 Oscillator Status and Manual Enable

The Ready status of each oscillator (including the ADCRC oscillator) is displayed in OSCSTAT (Register 4-4). The oscillators (but not the PLL) may be explicitly enabled through OSCEN (Register 4-7).

#### 4.3.2.7 HFOR and MFOR Bits

The HFOR and MFOR bits indicate that the HFINTOSC and MFINTOSC is ready. These clocks are always valid for use at all times, but only accurate after they are ready.

When a new value is loaded into the OSCFRQ register, the HFOR and MFOR bits will clear, and set again when the oscillator is ready. During pending OSCFRQ changes the MFINTOSC clock will stall at a high or a low state, until the HFINTOSC resumes operation.

# 4.4 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the New Oscillator Source (NOSC) bits of the OSCCON1 register. The following clock sources can be selected using the following:

- External oscillator

- Internal Oscillator Block (INTOSC)

| Note: | The Clock Switch Enable bit in          |

|-------|-----------------------------------------|

|       | Configuration Word 1 can be used to     |

|       | enable or disable the clock switching   |

|       | capability. When cleared, the NOSC and  |

|       | NDIV bits cannot be changed by user     |

|       | software. When set, writing to NOSC and |

|       | NDIV is allowed and would switch the    |

|       | clock frequency.                        |

#### 4.4.1 NEW OSCILLATOR SOURCE (NOSC) AND NEW DIVIDER SELECTION REQUEST (NDIV) BITS

The New Oscillator Source (NOSC) and New Divider Selection Request (NDIV) bits of the OSCCON1 register select the system clock source and frequency that are used for the CPU and peripherals.

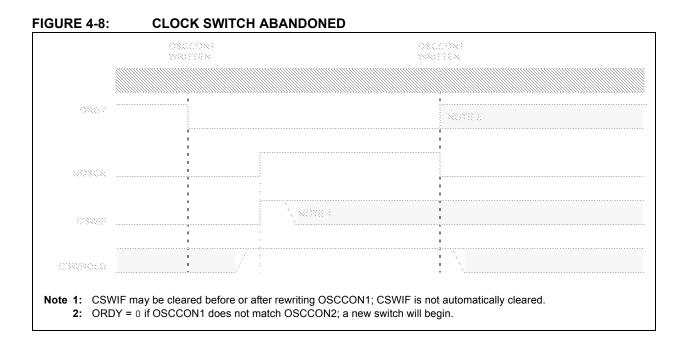

When new values of NOSC and NDIV are written to OSCCON1, the current oscillator selection will continue to operate while waiting for the new clock source to indicate that it is stable and ready. In some cases, the newly requested source may already be in use, and is ready immediately. In the case of a divider-only change, the new and old sources are the same, so the old source will be ready immediately. The device may enter Sleep while waiting for the switch as described in **Section 4.4.2 "Clock Switch and Sleep"**. When the new oscillator is ready, the New Oscillator Ready (NOSCR) bit of OSCCON3 is set and also the Clock Switch Interrupt Flag (CSWIF) bit of PIR1 sets. If Clock Switch Interrupts are enabled (CSWIE = 1), an interrupt will be generated at that time. The Oscillator Ready (ORDY) bit of OSCCON3 can also be polled to determine when the oscillator is ready in lieu of an interrupt.

| Note: | The CSWIF interrupt will not wake the |

|-------|---------------------------------------|

|       | system from Sleep.                    |

If the Clock Switch Hold (CSWHOLD) bit of OSCCON3 is clear, the oscillator switch will occur when the New Oscillator is Ready bit (NOSCR) is set, and the interrupt (if enabled) will be serviced at the new oscillator setting.

If CSWHOLD is set, the oscillator switch is suspended, while execution continues using the current (old) clock source. When the NOSCR bit is set, software should:

- Set CSWHOLD = 0 so the switch can complete, or

- Copy COSC into NOSC to abandon the switch.

If DOZE is in effect, the switch occurs on the next clock cycle, whether or not the CPU is operating during that cycle.

Changing the clock post-divider without changing the clock source (i.e., changing Fosc from 1 MHz to 2 MHz) is handled in the same manner as a clock source change, as described previously. The clock source will already be active, so the switch is relatively quick. CSWHOLD must be clear (CSWHOLD = 0) for the switch to complete.

The current COSC and CDIV are indicated in the OSCCON2 register up to the moment when the switch actually occurs, at which time OSCCON2 is updated and ORDY is set. NOSCR is cleared by hardware to indicate that the switch is complete.

# 8.2 Register Definitions: Power Control

| R/W/HS-0/q       | R/W/HS-0/q                                                                                                                                       | R/W/HC-1/q                                          | R/W/HC-1/q       |                 | R/W/HC-1/q                               | R/W/HC-0/u       | R/W/HC-q/u    |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------|-----------------|------------------------------------------|------------------|---------------|--|--|

| STKOVF           | STKUNF                                                                                                                                           |                                                     | RWDT             | RMCLR           | RI                                       | POR              | BOR           |  |  |

| bit 7            |                                                                                                                                                  | I                                                   |                  |                 |                                          |                  | bit (         |  |  |

| Legend:          |                                                                                                                                                  |                                                     |                  |                 |                                          |                  |               |  |  |

| HC = Bit is clea | ared by hardwa                                                                                                                                   | are                                                 |                  | HS = Bit is se  | t by hardware                            |                  |               |  |  |

| R = Readable     | bit                                                                                                                                              | W = Writable                                        | bit              | U = Unimplen    | nented bit, read                         | <b>as</b> '0'    |               |  |  |

| u = Bit is uncha | anged                                                                                                                                            | x = Bit is unkr                                     | iown             | -m/n = Value    | at POR and BO                            | R/Value at all o | other Resets  |  |  |

| '1' = Bit is set |                                                                                                                                                  | '0' = Bit is clea                                   | ared             | q = Value dep   | ends on condit                           | ion              |               |  |  |

| bit 7            | STKOVF: Sta                                                                                                                                      | ack Overflow Fl                                     | ag bit           |                 |                                          |                  |               |  |  |

|                  |                                                                                                                                                  | Overflow occur<br>Overflow has r                    |                  |                 |                                          |                  |               |  |  |

| bit 6            | STKUNF: Sta                                                                                                                                      | ack Underflow F                                     | lag bit          |                 |                                          |                  |               |  |  |

|                  |                                                                                                                                                  | Cunderflow occ                                      | •                |                 | ,                                        |                  |               |  |  |

| bit 5            | WDTWV: Watchdog Window Violation bit                                                                                                             |                                                     |                  |                 |                                          |                  |               |  |  |

|                  | 0 = ACLRWI                                                                                                                                       | window violatic<br>or instruction w<br>WDT window v | as issued whe    | n the WDT Re    | '1' by firmware<br>set window was        | closed (set to ' | 0' in hardwar |  |  |

| bit 4            | <b>RWDT</b> : WDT Reset Flag bit                                                                                                                 |                                                     |                  |                 |                                          |                  |               |  |  |

|                  |                                                                                                                                                  |                                                     |                  |                 | r set to '1' by fir<br>o '0' in hardware |                  | Reset occurs  |  |  |

| bit 3            | RMCLR: MCI                                                                                                                                       | Reset Flag                                          | bit              |                 |                                          |                  |               |  |  |

|                  | 1 = A MCLF                                                                                                                                       | Reset has not                                       | occurred or s    |                 |                                          |                  |               |  |  |

|                  |                                                                                                                                                  |                                                     |                  | 0' in hardware  | when a MCLR                              | Reset occurs)    |               |  |  |

| bit 2            | <b>RI:</b> RESET Instruction Flag bit<br>1 = A RESET instruction has not been executed or set to '1' by firmware                                 |                                                     |                  |                 |                                          |                  |               |  |  |

|                  |                                                                                                                                                  | T instruction h                                     |                  |                 | o '1' by firmware<br>'0' in hardware     |                  | ting a rese   |  |  |

| bit 1            | POR: Power-on Reset Status bit                                                                                                                   |                                                     |                  |                 |                                          |                  |               |  |  |

|                  | 1 = No Power-on Reset occurred or set to '1' by firmware                                                                                         |                                                     |                  |                 |                                          |                  |               |  |  |

|                  |                                                                                                                                                  | - an Deast ass                                      | irred (set to '0 | ' in hardware y | when a Power-o                           | on Reset occur   | e)            |  |  |

|                  | <ul> <li>0 = A Power-on Reset occurred (set to '0' in hardware when a Power-on Reset occurs)</li> <li>BOR: Brown-out Reset Status bit</li> </ul> |                                                     |                  |                 |                                          |                  |               |  |  |

| bit 0            |                                                                                                                                                  |                                                     |                  | in naranaro i   |                                          |                  | 5)            |  |  |

# REGISTER 8-2: PCON0: POWER CONTROL REGISTER 0

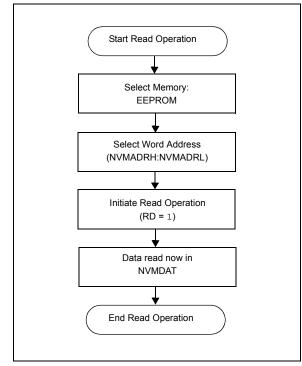

#### 11.3.3 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the NVMADRL and NVMADRH register pair, clear NVMREG<1:0> control bit in NVMCON1 register to access Data EEPROM locations and then set control bit, RD. The data is available on the very next instruction cycle; therefore, the NVMDAT register can be read by the next instruction. NVMDAT will hold this value until another read operation, or until it is written to by the user (during a write operation).

The basic process is shown in Example 11-5.

#### FIGURE 11-11: DATA EEPROM READ FLOWCHART

# 11.3.4 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the address must first be written to the NVMADRL and NVMADRH register pair and the data written to the NVMDAT register. The sequence in Example 11-6 must be followed to initiate the write cycle.

The write will not begin if NVM Unlock sequence, described in **Section 11.1.4 "NVM Unlock Sequence"**, is not exactly followed for each byte. It is strongly recommended that interrupts be disabled during this code segment.

Additionally, the WREN bit in NVMCON1 must be set to enable writes. This mechanism prevents accidental writes to data EEPROM due to unexpected code execution (i.e., runaway programs). The WREN bit should be kept clear at all times, except when updating the EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, NVMCON1, NVMADRL, NVMADRH and NVMDAT cannot be modified. The WR bit will be inhibited from being set unless the WREN bit is set. Both WR and WREN cannot be set with the same instruction.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. A single Data EEPROM word is written and the operation includes an implicit erase cycle for that word (it is not necessary to set FREE). CPU execution continues in parallel and at the completion of the write cycle, the WR bit is cleared in hardware and the NVM Interrupt Flag bit (NVMIF) is set. The user can either enable this interrupt or poll this bit. NVMIF must be cleared by software.

# 19.9 Timer1/3/5 Interrupt

The Timer1/3/5 register pair (TMRxH:TMRxL) increments to FFFFh and rolls over to 0000h. When Timer1/3/5 rolls over, the Timer1/3/5 interrupt flag bit of the PIR4 register is set. To enable the interrupt-on-rollover, you must set these bits:

- TMRxON bit of the TxCON register

- TMRxIE bits of the PIE4 register

- PEIE/GIEL bit of the INTCON register

- · GIE/GIEH bit of the INTCON register

The interrupt is cleared by clearing the TMRxIF bit in the Interrupt Service Routine.

For more information on selecting high or low priority status for the Timer1/3/5 Overflow Interrupt, see **Section 14.0 "Interrupts"**.

Note: The TMRxH:TMRxL register pair and the TMRxIF bit should be cleared before enabling interrupts.

# 19.10 Timer1/3/5 Operation During Sleep

Timer1/3/5 can only operate during Sleep when set up in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMRxON bit of the TxCON register must be set

- TMRxIE bit of the PIE4 register must be set

- PEIE/GIEL bit of the INTCON register must be set

- TxSYNC bit of the TxCON register must be set

- Configure the TMRxCLK register for using secondary oscillator as the clock source

- Enable the SOSCEN bit of the OSCEN register (Register 4-7)

The device will wake-up on an overflow and execute the next instruction. If the GIE/GIEH bit of the INTCON register is set, the device will call the Interrupt Service Routine.

The secondary oscillator will continue to operate in Sleep regardless of the  $\overline{\text{TxSYNC}}$  bit setting.

## 19.11 CCP Capture/Compare Time Base

The CCP modules use the TMRxH:TMRxL register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMRxH:TMRxL register pair is copied into the CCPRxH:CCPRxL register pair on a configured event.

In Compare mode, an event is triggered when the value in the CCPRxH:CCPRxL register pair matches the value in the TMRxH:TMRxL register pair. This event can be a Special Event Trigger.

For more information, see Section 21.0 "Capture/Compare/PWM Module".

# 19.12 CCP Special Event Trigger

When any of the CCP's are configured to trigger a special event, the trigger will clear the TMRxH:TMRxL register pair. This special event does not cause a Timer1/3/5 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPRxH:CCPRxL register pair becomes the period register for Timer1/3/5.

Timer1/3/5 should be synchronized and FOSC/4 should be selected as the clock source in order to utilize the Special Event Trigger. Asynchronous operation of Timer1/3/5 can cause a Special Event Trigger to be missed.

In the event that a write to TMRxH or TMRxL coincides with a Special Event Trigger from the CCP, the write will take precedence.

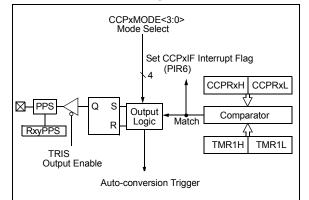

# 21.0 CAPTURE/COMPARE/PWM MODULE

The Capture/Compare/PWM module is a peripheral that allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

This family of devices contains two standard Capture/Compare/PWM modules (CCP1 and CCP2). Each individual CCP module can select the timer source that controls the module. Each module has an independent timer selection which can be accessed using the CxTSEL bits in the CCPTMRS register (Register 21-2). The default timer selection is TMR1 when using Capture/Compare mode and TMR2 when using PWM mode in the CCPx module.

Please note that the Capture/Compare mode operation is described with respect to TMR1 and the PWM mode operation is described with respect to TMR2 in the following sections.

The Capture and Compare functions are identical for all CCP modules.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to CCPx module. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

# 21.1 CCP Module Configuration

Each Capture/Compare/PWM module is associated with a control register (CCPxCON), a capture input selection register (CCPxCAP) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte).

#### 21.1.1 CCP MODULES AND TIMER RESOURCES

The CCP modules utilize Timers 1 through 6 that vary with the selected mode. Various timers are available to the CCP modules in Capture, Compare or PWM modes, as shown in Table 21-1.

#### TABLE 21-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource           |  |  |  |

|----------|--------------------------|--|--|--|

| Capture  |                          |  |  |  |

| Compare  | Timer1, Timer3 or Timer5 |  |  |  |

| PWM      | Timer2, Timer4 or Timer6 |  |  |  |

The assignment of a particular timer to a module is determined by the timer to CCP enable bits in the CCPTMRS register (see Register 21-2) All of the modules may be active at once and may share the same timer resource if they are configured to operate in the same mode (Capture/Compare or PWM) at the same time.

## 21.1.2 OPEN-DRAIN OUTPUT OPTION

When operating in Output mode (the Compare or PWM modes), the drivers for the CCPx pins can be optionally configured as open-drain outputs. This feature allows the voltage level on the pin to be pulled to a higher level through an external pull-up resistor and allows the output to communicate with external circuits without the need for additional level shifters.

## 21.3.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE Interrupt Priority bit of the PIE6 register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIR6 register following any change in Operating mode.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Capture mode. In order for Capture mode to recognize the trigger event on the CCPx pin, Timer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

## 21.3.4 CCP PRESCALER

There are four prescaler settings specified by the MODE<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 21-1 demonstrates the code to perform this function.

#### EXAMPLE 21-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEI | L CCPxCON   | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCPxCON             |

| CLRF    | CCPxCON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ;the new prescaler      |

|         |             | ;move value and CCP ON  |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this |

|         |             | ;value                  |

|         |             |                         |

# 21.3.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

# 21.4 Compare Mode

The Compare mode function described in this section is available and identical for all CCP modules.

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMRxH:TMRxL register pair. When a match occurs, one of the following events can occur:

- Toggle the CCPx output, clear TMRx

- · Toggle the CCPx output

- · Set the CCPx output

- · Clear the CCPx output

- Pulse output

- Pulse output, clear TMRx

The action on the pin is based on the value of the MODE<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set, and an ADC conversion can be triggered, if selected.

All Compare modes can generate an interrupt and trigger an ADC conversion. When MODE =  $4 \cdot b0001$  or  $4 \cdot b1011$ , the CCP resets the TMR register pair.

Figure 21-2 shows a simplified diagram of the compare operation.

# FIGURE 21-2:

#### COMPARE MODE OPERATION BLOCK DIAGRAM

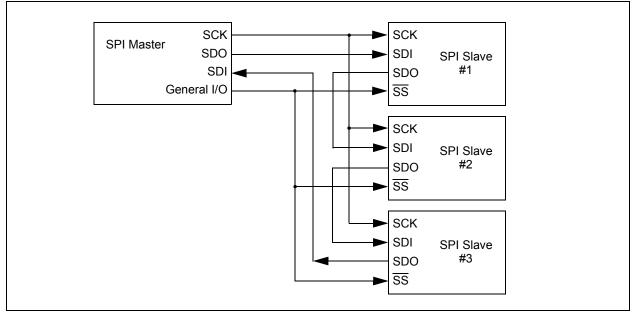

### 26.5.4 SLAVE SELECT SYNCHRONIZATION

The Slave Select can also be used to synchronize communication. The Slave Select line is held high until the master device is ready to communicate. When the Slave Select line is pulled low, the slave knows that a new transmission is starting.

If the slave fails to receive the communication properly, it will be reset at the end of the transmission, when the Slave Select line returns to a high state. The slave is then ready to receive a new transmission when the Slave Select line is pulled low again. If the Slave Select line is not used, there is a risk that the slave will eventually become out of sync with the master. If the slave misses a bit, it will always be one bit off in future transmissions. Use of the Slave Select line allows the slave and master to align themselves at the beginning of each transmission.

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPxCON1<3:0> = 0100).

FIGURE 26-5: SPI DAISY-CHAIN CONNECTION

When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven.

When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

- Note 1: When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPxCON1<3:0> = 0100), the SPI module will reset if the  $\overline{SS}$ pin is set to VDD.

- 2: When the SPI is used in Slave mode with CKE set; the user must enable SS pin control.

- While operated in SPI Slave mode the SMP bit of the SSPxSTAT register must remain clear.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

# 27.1 Register Definitions: EUSART Control

| R/W-/0         | R/W-0/0                                              | R/W-0/0                                                    | R/W-0/0         | R/W-0/0         | R/W-0/0          | R-1/1            | R/W-0/0      |

|----------------|------------------------------------------------------|------------------------------------------------------------|-----------------|-----------------|------------------|------------------|--------------|

| CSRC           | TX9                                                  | TXEN <sup>(1)</sup>                                        | SYNC            | SENDB           | BRGH             | TRMT             | TX9D         |

| bit 7          |                                                      |                                                            |                 |                 |                  |                  | bit          |

| Legend:        |                                                      |                                                            |                 |                 |                  |                  |              |

| R = Reada      | ble bit                                              | W = Writable                                               | bit             | U = Unimpler    | mented bit, read | as '0'           |              |

| u = Bit is ur  | nchanged                                             | x = Bit is unki                                            | nown            | -n/n = Value a  | at POR and BOF   | R/Value at all o | other Resets |

| '1' = Bit is s | set                                                  | '0' = Bit is cle                                           | ared            |                 |                  |                  |              |

| bit 7          | Asynchrono<br>Don't care<br>Synchronou<br>1 = Master |                                                            | nerated intern  |                 | )                |                  |              |

| bit 6          | <b>TX9:</b> 9-bit T<br>1 = Selects                   | ransmit Enable I<br>s 9-bit transmiss<br>s 8-bit transmiss | oit<br>ion      | ,               |                  |                  |              |

| bit 5          | <b>TXEN:</b> Tran<br>1 = Transm<br>0 = Transm        |                                                            | 1)              |                 |                  |                  |              |

| bit 4          | 1 = Synchr                                           | SART Mode Sele<br>onous mode<br>ronous mode                | ect bit         |                 |                  |                  |              |

| bit 3          | Asynchrono<br>1 = Send S                             | ync Break on ne<br>reak transmissio                        | ext transmissio |                 | nardware upon o  | completion)      |              |

| bit 2          | BRGH: Higl<br>Asynchrono                             | beed, if BRG16 =<br>eed<br><u>is mode:</u>                 |                 | is baudclk/4; e | lse baudclk/16   |                  |              |

| bit 1          |                                                      | smit Shift Regist<br>npty                                  | ter Status bit  |                 |                  |                  |              |

| bit 0          |                                                      | n bit of Transmit                                          |                 |                 |                  |                  |              |

# REGISTER 27-1: TXxSTA: TRANSMIT STATUS AND CONTROL REGISTER

## 27.5.1.5 Synchronous Master Reception

Data is received at the RXx/DTx pin. The RXx/DTx pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCxSTA register) or the Continuous Receive Enable bit (CREN of the RCxSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

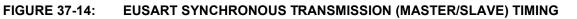

To initiate reception, set either SREN or CREN. Data is sampled at the RXx/DTx pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCxIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCxREG. The RCxIF bit remains set as long as there are unread characters in the receive FIFO.

| Note: | If the RX/DT function is on an analog pin, |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

|       | the corresponding ANSEL bit must be        |  |  |  |  |  |

|       | cleared for the receiver to function.      |  |  |  |  |  |

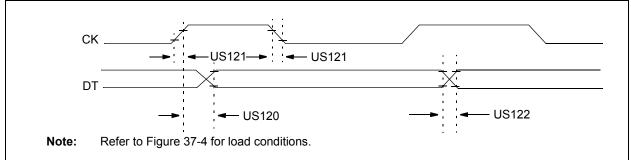

## 27.5.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TXx/CKx pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

**Note:** If the device is configured as a slave and the TX/CK function is on an analog pin, the corresponding ANSEL bit must be cleared.

#### 27.5.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCxREG is read to access the FIFO. When this happens the OERR bit of the RCxSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCxREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

#### 27.5.1.8 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCxSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCxSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCxREG.

# 27.5.1.9 Synchronous Master Reception Setup:

- 1. Initialize the SPxBRGH:SPxBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RXx pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- Interrupt flag bit RCxIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCxIE was set.

- 9. Read the RCxSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCxREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

| R/W-x/u          | R/W-x/u                                                        | R/W-x/u            | R/W-x/u | R/W-x/u        | R/W-x/u       | R/W-x/u          | R/W-x/u      |

|------------------|----------------------------------------------------------------|--------------------|---------|----------------|---------------|------------------|--------------|

|                  |                                                                |                    | ADSTF   | PT<15:8>       |               |                  |              |

| bit 7            |                                                                |                    |         |                |               |                  | bit 0        |

|                  |                                                                |                    |         |                |               |                  |              |

| Legend:          |                                                                |                    |         |                |               |                  |              |

| R = Readable     | adable bit W = Writable bit U = Unimplemented bit, read as '0' |                    |         |                |               |                  |              |

| u = Bit is unch  | anged                                                          | x = Bit is unknown |         | -n/n = Value a | at POR and BC | R/Value at all o | other Resets |

| '1' = Bit is set |                                                                | '0' = Bit is clea  | ared    |                |               |                  |              |

## REGISTER 31-24: ADSTPTH: ADC THRESHOLD SETPOINT REGISTER HIGH

bit 7-0 **ADSTPT<15:8>**: ADC Threshold Setpoint MSB. Upper byte of ADC threshold setpoint, depending on ADCALC, may be used to determine ADERR, see Register 23-1 for more details.

#### REGISTER 31-25: ADSTPTL: ADC THRESHOLD SETPOINT REGISTER LOW

| R/W-x/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ADSTP   | T<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADSTPT<7:0>**: ADC Threshold Setpoint LSB. Lower byte of ADC threshold setpoint, depending on ADCALC, may be used to determine ADERR, see Register 23-1 for more details.

#### REGISTER 31-26: ADERRH: ADC SETPOINT ERROR REGISTER HIGH

| R-x        | R-x         | R-x | R-x | R-x | R-x | R-x | R-x |

|------------|-------------|-----|-----|-----|-----|-----|-----|

| ADERR<7:0> |             |     |     |     |     |     |     |

| bit 7      | bit 7 bit 0 |     |     |     |     |     |     |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADERR<7:0>**: ADC Setpoint Error MSB. Upper byte of ADC Setpoint Error. Setpoint Error calculation is determined by ADCALC bits of ADCON3, see Register 23-1 for more details.

© 2016-2017 Microchip Technology Inc.

-n/n = Value at POR and BOR/Value at all other Resets

#### REGISTER 31-27: ADERRL: ADC SETPOINT ERROR LOW BYTE REGISTER

x = Bit is unknown

| R-x              | R-x | R-x              | R-x  | R-x          | R-x              | R-x    | R-x   |

|------------------|-----|------------------|------|--------------|------------------|--------|-------|

|                  |     |                  | ADER | R<7:0>       |                  |        |       |

| bit 7            |     |                  |      |              |                  |        | bit 0 |

|                  |     |                  |      |              |                  |        |       |

| Legend:          |     |                  |      |              |                  |        |       |

| R = Readable bit |     | W = Writable bit |      | U = Unimpler | nented bit, reac | as '0' |       |

| '1' = Bit is set | '0' = Bit is cleared                                                                          |

|------------------|-----------------------------------------------------------------------------------------------|

|                  |                                                                                               |

| bit 7-0          | ADERR<7:0>: ADC Setpoint Error LSB Lower byte of ADC Setpoint Error calculation is determined |

bit 7-0 **ADERR<7:0>**: ADC Setpoint Error LSB. Lower byte of ADC Setpoint Error calculation is determined by ADCALC bits of ADCON3, see Register 23-1 for more details.

#### REGISTER 31-28: ADLTHH: ADC LOWER THRESHOLD HIGH BYTE REGISTER

| R/W-x/x     | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| ADLTH<15:8> |         |         |         |         |         |         |         |

| bit 7 bit 0 |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADLTH<15:8>**: ADC Lower Threshold MSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

#### REGISTER 31-29: ADLTHL: ADC LOWER THRESHOLD LOW BYTE REGISTER

| R/W-x/x     | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| ADLTH<7:0>  |         |         |         |         |         |         |         |

| bit 7 bit 0 |         |         |         |         |         |         |         |

|             |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADLTH<7:0>**: ADC Lower Threshold LSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

© 2016-2017 Microchip Technology Inc.

u = Bit is unchanged

| R/W-0/0         | U-0                                     | R-x                                | R-x                 | U-0                             | U-0              | R/W-0/0         | R/W-0/0 |  |  |  |

|-----------------|-----------------------------------------|------------------------------------|---------------------|---------------------------------|------------------|-----------------|---------|--|--|--|

| EN              | -                                       | OUT                                | RDY                 | —                               | —                | INTH            | INTL    |  |  |  |

| bit 7           |                                         |                                    |                     |                                 |                  |                 | bit C   |  |  |  |

| Legend:         |                                         |                                    |                     |                                 |                  |                 |         |  |  |  |

| R = Readable    | bit                                     | W = Writable                       | bit                 | U = Unimplei                    | mented bit, read | d as '0'        |         |  |  |  |

| -n = Value at F | POR                                     | '1' = Bit is set                   |                     | '0' = Bit is cle                |                  | x = Bit is unki | nown    |  |  |  |

|                 |                                         |                                    |                     |                                 |                  |                 |         |  |  |  |

| bit 7           | EN: High/Low                            | -voltage Detec                     | t Power Enal        | ole bit                         |                  |                 |         |  |  |  |

|                 |                                         |                                    |                     | cuit and suppo<br>and supportin | rting reference  | circuitry       |         |  |  |  |

| bit 6           | Unimplemen                              | ted: Read as '(                    | D'                  |                                 |                  |                 |         |  |  |  |

| bit 5           | OUT: HLVD C                             | omparator Out                      | put bit             |                                 |                  |                 |         |  |  |  |

|                 | 0                                       | ≤ selected dete                    | ,                   | ,                               |                  |                 |         |  |  |  |

|                 | •                                       | ≥ selected dete                    |                     | ,                               |                  |                 |         |  |  |  |

| bit 4           |                                         | •                                  | •                   | le Status Flag                  |                  |                 |         |  |  |  |

|                 |                                         |                                    |                     |                                 |                  |                 |         |  |  |  |

| bit 3-2         |                                         |                                    | ,                   |                                 |                  |                 |         |  |  |  |

|                 | •                                       | ted: Read as '                     |                     |                                 |                  |                 |         |  |  |  |

| bit 1           |                                         |                                    |                     | ) Interrupt Enal                |                  |                 |         |  |  |  |

|                 |                                         | will be set whe<br>will not be set | en voltage $\geq$ s |                                 | on limit (HLVDS  | 5EL<3:0>)       |         |  |  |  |

| bit 0           | • • • • • • • • • • • • • • • • • • • • |                                    | (Low Voltage        | e) Interrupt Ena                | ble              |                 |         |  |  |  |

|                 | 1 = HLVDIF                              |                                    |                     | , ,                             | ion limit (HLVD  | SEL<3:0>)       |         |  |  |  |

## REGISTER 33-2: HLVDCON0: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER 0

| TABLE 33-2: F | REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE |

|---------------|----------------------------------------------------------|

|---------------|----------------------------------------------------------|

| Name     | Bit 7    | Bit 6     | Bit 5  | Bit 4 | Bit 3    | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|----------|----------|-----------|--------|-------|----------|---------|---------|---------|---------------------|

| HLVDCON0 | EN       | -         | OUT    | RDY   | -        | -       | INTH    | INTL    | 476                 |

| HLVDCON1 | -        | -         | -      | -     | SEL<3:0> |         |         |         | 475                 |

| INTCON   | GIE/GIEH | PEIE/GIEL | IPEN   | -     | -        | INT2EDG | INT1EDG | INT0EDG | 166                 |

| PIR2     | HLVDIF   | ZCDIF     | -      | -     | -        | -       | C2IF    | C1IF    | 169                 |

| PIE2     | HLVDIE   | ZCDIE     | -      | -     | -        | -       | C2IE    | C1IE    | 177                 |

| IPR2     | HLVDIP   | ZCDIP     | -      | -     | -        | -       | C2IP    | C1IP    | 185                 |

| PMD0     | SYSCMD   | FVRMD     | HLVDMD | CRCMD | SCANMD   | NVMMD   | CLKRMD  | IOCMD   | 64                  |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

**Note 1:** PORTA<7:6> and their direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

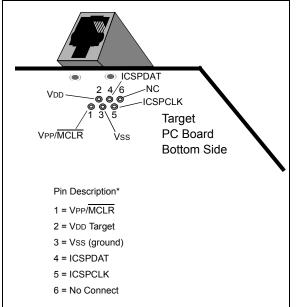

# 34.0 IN-CIRCUIT SERIAL PROGRAMMING™ (ICSP™)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process, allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP<sup>TM</sup> refer to the "PIC18(L)F2X/4XK40 Memory Programming Specification" (DS40001772).

# 34.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

# 34.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the MCLR Reset function is automatically enabled and cannot be disabled. See **Section 8.6** "**MCLR**" for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

# 34.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 34-1.

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 34-2.

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 34-3 for more information.

# PIC18(L)F24/25K40

| ADDWFC                                                                            | oit to f                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| Syntax:                                                                           | ADDWFC                                                                                                                                                                       | f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      |  |  |  |

| Operands:                                                                         | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                           | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |  |  |  |

| Operation:                                                                        | (W) + (f) +                                                                                                                                                                  | $(C) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |  |  |  |

| Status Affected:                                                                  | N,OV, C, D                                                                                                                                                                   | C, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |  |  |  |

| Encoding:                                                                         | 0010                                                                                                                                                                         | 00da ffi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | f ffff               |  |  |  |

| Description:                                                                      | ory location<br>placed in W<br>placed in d<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank.<br>If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode wher<br>tion 35.2.3 | Add W, the CARRY flag and data mem-<br>ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 35.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit- |                      |  |  |  |

| Words:                                                                            | 1                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| Cycles:                                                                           | 1                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| Q Cycle Activity:                                                                 |                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| Q1                                                                                | Q2                                                                                                                                                                           | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Q4                   |  |  |  |

| Decode                                                                            | Read<br>register 'f'                                                                                                                                                         | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Write to destination |  |  |  |

| Example:                                                                          | ADDWFC                                                                                                                                                                       | REG, 0,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                    |  |  |  |

| Before Instruct<br>CARRY &<br>REG<br>W<br>After Instructio<br>CARRY &<br>REG<br>W | bit = 1<br>= 02h<br>= 4Dh                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

|                                                                                               | DLW               | AND lite            | ral with          | w    |           |

|-----------------------------------------------------------------------------------------------|-------------------|---------------------|-------------------|------|-----------|

| Synt                                                                                          | ax:               | ANDLW               | k                 |      |           |

| Oper                                                                                          | ands:             | $0 \le k \le 25$    | 5                 |      |           |

| Oper                                                                                          | ration:           | (W) .AND            | $k \rightarrow W$ |      |           |

| Statu                                                                                         | is Affected:      | N, Z                |                   |      |           |

| Enco                                                                                          | oding:            | 0000                | 1011              | kkkk | kkkk      |

| Description: The contents of W are AND'ed with the 8-bit literal 'k'. The result is placed in |                   |                     |                   |      |           |

| Word                                                                                          | ds:               | 1                   |                   |      |           |

| Cycle                                                                                         | es:               | 1                   |                   |      |           |

| QC                                                                                            | ycle Activity:    |                     |                   |      |           |

|                                                                                               | Q1                | Q2                  | Q3                | 3    | Q4        |

|                                                                                               | Decode            | Read literal<br>'k' | l Proce<br>Dat    |      | rite to W |

| Example:                                                                                      |                   | ANDLW               | 05Fh              |      |           |