Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25k40t-i-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data memory are controlled independently. Internal access to the program memory is unaffected by any code protection setting.

#### 3.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Self-writing the program memory is dependent upon the write protection setting. See **Section 3.4 "Write Protection"** for more information.

## 3.3.2 DATA MEMORY PROTECTION

The entire Data EEPROM Memory space is protected from external reads and writes by the CPD bit in the Configuration Words. When  $\overline{CPD} = 0$ , external reads and writes of Data EEPROM Memory are inhibited and a read will return all '0's. The CPU can continue to read Data EEPROM Memory regardless of the protection bit settings.

## 3.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

## 3.5 User ID

Eight words in the memory space (200000h-200000Fh) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See Section 11.2 "User ID, Device ID and Configuration Word Access" for more information on accessing these memory locations. For more information on checksum calculation, see the "PIC18(L)F2X/4XK40 Memory Programming Specification" (DS40001772).

| U-0              | R-q/q | R-q/q             | R-q/q | R-q/q                                               | R-q/q     | R-q/q | R-q/q        |  |

|------------------|-------|-------------------|-------|-----------------------------------------------------|-----------|-------|--------------|--|

| —                |       | COSC<2:0>         |       |                                                     | CDIV<3:0> |       |              |  |

| bit 7            |       |                   |       |                                                     |           |       | bit 0        |  |

|                  |       |                   |       |                                                     |           |       |              |  |

| Legend:          |       |                   |       |                                                     |           |       |              |  |

| R = Readable I   | bit   | W = Writable b    | bit   | U = Unimplemented bit, read as '0'                  |           |       |              |  |

| u = Bit is uncha | anged | x = Bit is unkn   | own   | -n/n = Value at POR and BOR/Value at all other Rese |           |       | other Resets |  |

| '1' = Bit is set |       | '0' = Bit is clea | ired  | q = Reset value is determined by hardware           |           |       | 9            |  |

|                  |       |                   |       |                                                     |           |       |              |  |

| bit 6-4 | COSC<2:0>: Current Oscillator Source Select bits (read-only) <sup>(1,2)</sup> |

|---------|-------------------------------------------------------------------------------|

|         | Indicates the current source oscillator and PLL combination per Table 4-2.    |

|         |                                                                               |

bit 3-0 **CDIV<3:0>:** Current Divider Select bits (read-only)<sup>(1,2)</sup> Indicates the current postscaler division ratio per Table 4-2.

**2**: The Reset value (q/q) is the same as the NOSC/NDIV bits.

## TABLE 4-2: NOSC/COSC AND NDIV/CDIV BIT SETTINGS

| NOSC<2:0><br>COSC<2:0> | Clock Source                   |  |  |  |

|------------------------|--------------------------------|--|--|--|

| 111                    | EXTOSC <sup>(1)</sup>          |  |  |  |

| 110                    | HFINTOSC <sup>(2)</sup>        |  |  |  |

| 101                    | LFINTOSC                       |  |  |  |

| 100                    | SOSC                           |  |  |  |

| 011                    | Reserved                       |  |  |  |

| 010                    | EXTOSC + 4x PLL <sup>(3)</sup> |  |  |  |

| 001                    | Reserved                       |  |  |  |

| 000                    | Reserved                       |  |  |  |

| NDIV<3:0><br>CDIV<3:0> | Clock Divider |

|------------------------|---------------|

| 1111-1010              | Reserved      |

| 1001                   | 512           |

| 1000                   | 256           |

| 0111                   | 128           |

| 0110                   | 64            |

| 0101                   | 32            |

| 0100                   | 16            |

| 0011                   | 8             |

| 0010                   | 4             |

| 0001                   | 2             |

| 0000                   | 1             |

|                        |               |

Note 1: EXTOSC configured by the FEXTOSC bits of Configuration Word 1 (Register 3-1).

2: HFINTOSC frequency is set with the HFFRQ bits of the OSCFRQ register (Register 4-5).

3: EXTOSC must meet the PLL specifications (Table 37-9).

**Note 1:** The POR value is the value present when user code execution begins.

## 5.1 Clock Source

The input to the reference clock output can be selected using the CLKRCLK register.

## 5.1.1 CLOCK SYNCHRONIZATION

Once the reference clock enable (EN) is set, the module is ensured to be glitch-free at start-up.

When the reference clock output is disabled, the output signal will be disabled immediately.

Clock dividers and clock duty cycles can be changed while the module is enabled, but glitches may occur on the output. To avoid possible glitches, clock dividers and clock duty cycles should be changed only when the CLKREN is clear.

## 5.2 Programmable Clock Divider

The module takes the clock input and divides it based on the value of the DIV<2:0> bits of the CLKRCON register (Register 5-1).

The following configurations can be made based on the DIV<2:0> bits:

- · Base Fosc value

- Fosc divided by 2

- Fosc divided by 4

- Fosc divided by 8

- Fosc divided by 16

- · Fosc divided by 32

- Fosc divided by 64

- Fosc divided by 128

The clock divider values can be changed while the module is enabled; however, in order to prevent glitches on the output, the DIV<2:0> bits should only be changed when the module is disabled (EN = 0).

## 5.3 Selectable Duty Cycle

The DC<1:0> bits of the CLKRCON register can be used to modify the duty cycle of the output clock. A duty cycle of 25%, 50%, or 75% can be selected for all clock rates, with the exception of the undivided base Fosc value.

The duty cycle can be changed while the module is enabled; however, in order to prevent glitches on the output, the DC<1:0> bits should only be changed when the module is disabled (EN = 0).

Note: The DC1 bit is reset to '1'. This makes the default duty cycle 50% and not 0%.

## 5.4 Operation in Sleep Mode

The reference clock output module clock is based on the system clock. When the device goes to Sleep, the module outputs will remain in their current state. This will have a direct effect on peripherals using the reference clock output as an input signal. No change should occur in the module from entering or exiting from Sleep.

| U-0            | R/W-0/0                        | R/W-0/0                      | R/W-0/0 | R/W-0/0       | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |

|----------------|--------------------------------|------------------------------|---------|---------------|------------------|------------------|--------------|--|

| _              | TMR6MD                         | TMR5MD                       | TMR4MD  | TMR3MD        | TMR2MD           | TMR1MD           | TMR0MD       |  |

| oit 7          |                                | •                            |         |               | •                | •                | bit          |  |

|                |                                |                              |         |               |                  |                  |              |  |

| Legend:        |                                |                              |         |               |                  |                  |              |  |

| R = Reada      |                                | W = Writable                 |         | •             | nented bit, read |                  |              |  |

| u = Bit is u   | 0                              | x = Bit is unkr              |         |               |                  | R/Value at all c | other Resets |  |

| '1' = Bit is s | set                            | '0' = Bit is clea            | ared    | q = Value dep | ends on condit   | ion              |              |  |

| bit 7          | Unimplemen                     | ted: Read as '               | )'      |               |                  |                  |              |  |

| bit 6          | TMR6MD: Di                     | sable Timer TM               | IR6 bit |               |                  |                  |              |  |

|                | 1 = TMR6 m                     | odule disabled               |         |               |                  |                  |              |  |

|                | 0 = TMR6 m                     | odule enabled                |         |               |                  |                  |              |  |

| bit 5          | TMR5MD: Disable Timer TMR5 bit |                              |         |               |                  |                  |              |  |

|                | 1 = TMR5 m                     | odule disabled               |         |               |                  |                  |              |  |

|                | 0 = TMR5 m                     | odule enabled                |         |               |                  |                  |              |  |

| bit 4          | TMR4MD: Di                     | sable Timer TM               | IR4 bit |               |                  |                  |              |  |

|                | 1 = TMR4 m                     | odule disabled               |         |               |                  |                  |              |  |

|                | 0 = TMR4 m                     | odule enabled                |         |               |                  |                  |              |  |

| bit 3          |                                | sable Timer TM               | IR3 bit |               |                  |                  |              |  |

|                | -                              | odule disabled               |         |               |                  |                  |              |  |

|                |                                | odule enabled                |         |               |                  |                  |              |  |

| bit 2          |                                | sable Timer TM               | IR2 bit |               |                  |                  |              |  |

|                |                                | odule disabled odule enabled |         |               |                  |                  |              |  |

| bit 1          | TMR1MD: Di                     | sable Timer TM               | IR1 bit |               |                  |                  |              |  |

|                | 1 = TMR1 m                     | 1 = TMR1 module disabled     |         |               |                  |                  |              |  |

|                | 0 = TMR1 m                     | odule enabled                |         |               |                  |                  |              |  |

| bit 0          | TMR0MD: Di                     | sable Timer TM               | IR0 bit |               |                  |                  |              |  |

|                |                                | odule disabled               |         |               |                  |                  |              |  |

|                | 0 = TMR0 m                     | odule enabled                |         |               |                  |                  |              |  |

#### REGISTER 7-2: PMD1: PMD CONTROL REGISTER 1

| U-0                                                   | U-0               | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| —                                                     | —                 | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PWM4MD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PWM3MD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CCP2MD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CCP1MD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                       |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                       |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                       |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| e bit                                                 | W = Writable      | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | U = Unimplem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nented bit, read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | l as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| hanged                                                | x = Bit is unkn   | own                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -n/n = Value a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | t POR and BO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/Value at all o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ther Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| t                                                     | '0' = Bit is clea | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | q = Value dep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ends on condit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                       |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Unimplement                                           | ed: Read as '0'   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                       |                   | th Modulator PV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | VM4 bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                       |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                       |                   | th Madulatar DV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1/1/2 hit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                       |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0 = PWM3 m                                            | odule enabled     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

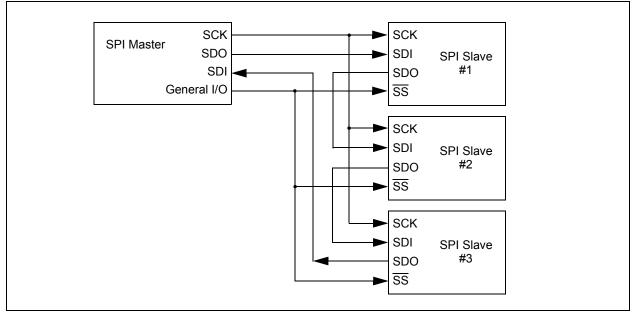

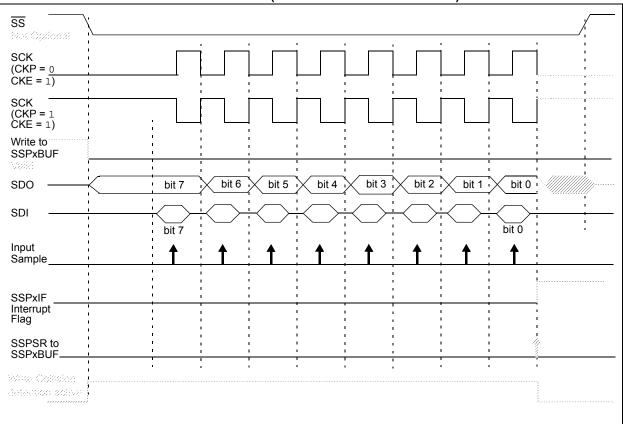

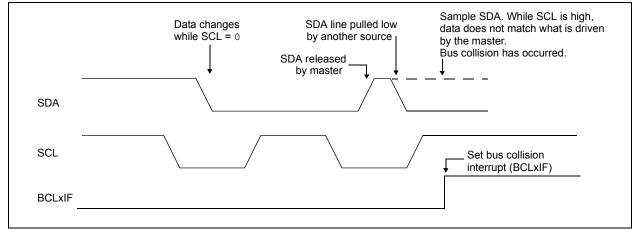

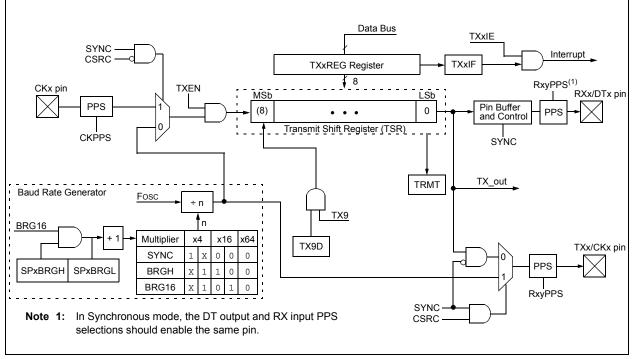

| t 1 CCP2MD: Disable Pulse-Width Modulator CCP2 bit    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |