#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1516-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.4.5 CORE FUNCTION REGISTERS SUMMARY

The Core Function registers listed in Table 3-7 can be addressed from any Bank.

| Addr            | Name   | Bit 7                                                    | Bit 6                                       | Bit 5         | Bit 4        | Bit 3        | Bit 2         | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on all other Resets |

|-----------------|--------|----------------------------------------------------------|---------------------------------------------|---------------|--------------|--------------|---------------|--------|-----------|----------------------|---------------------------|

| Bank 0-31       |        |                                                          |                                             |               |              |              |               |        |           |                      |                           |

| x00h or<br>x80h | INDF0  |                                                          | this location<br>ical register)             |               | nts of FSR0H | /FSR0L to ad | ddress data r | memory |           | xxxx xxxx            | uuuu uuuu                 |

| x01h or<br>x81h | INDF1  |                                                          | this location<br>ical register)             |               | nts of FSR1H | /FSR1L to ad | ddress data r | memory |           | xxxx xxxx            | uuuu uuuu                 |

| x02h or<br>x82h | PCL    | Program Co                                               | ounter (PC) I                               | Least Signifi | cant Byte    |              |               |        |           | 0000 0000            | 0000 0000                 |

| x03h or<br>x83h | STATUS |                                                          | _                                           | _             | TO           | PD           | Z             | DC     | С         | 1 1000               | q quuu                    |

| x04h or<br>x84h | FSR0L  | Indirect Dat                                             | Indirect Data Memory Address 0 Low Pointer  |               |              |              |               |        |           | 0000 0000            | uuuu uuuu                 |

| x05h or<br>x85h | FSR0H  | Indirect Dat                                             | Indirect Data Memory Address 0 High Pointer |               |              |              |               |        |           | 0000 0000            | 0000 0000                 |

| x06h or<br>x86h | FSR1L  | Indirect Dat                                             | ta Memory A                                 | ddress 1 Lo   | w Pointer    |              |               |        |           | 0000 0000            | uuuu uuuu                 |

| x07h or<br>x87h | FSR1H  | Indirect Dat                                             | ta Memory A                                 | ddress 1 Hig  | gh Pointer   |              |               |        |           | 0000 0000            | 0000 0000                 |

| x08h or<br>x88h | BSR    | -                                                        | -                                           | -             | BSR4         | BSR3         | BSR2          | BSR1   | BSR0      | 0 0000               | 0 0000                    |

| x09h or<br>x89h | WREG   | Working Register                                         |                                             |               |              |              |               |        | 0000 0000 | uuuu uuuu            |                           |

| x0Ahor<br>x8Ah  | PCLATH | Write Buffer for the upper 7 bits of the Program Counter |                                             |               |              |              |               |        |           | -000 0000            | -000 0000                 |

| x0Bhor<br>x8Bh  | INTCON | GIE                                                      | PEIE                                        | TMR0IE        | INTE         | IOCIE        | TMR0IF        | INTF   | IOCIF     | 0000 0000            | 0000 0000                 |

TABLE 3-7: CORE FUNCTION REGISTERS SUMMARY

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

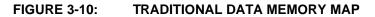

### 3.7.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

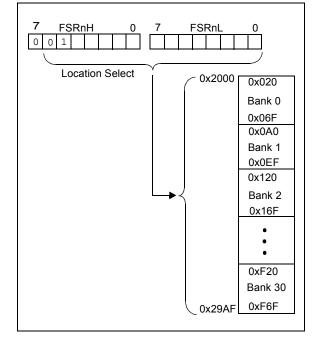

## 3.7.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address 0x2000 to FSR address 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 3-11: LINEAR DATA MEMORY MAP

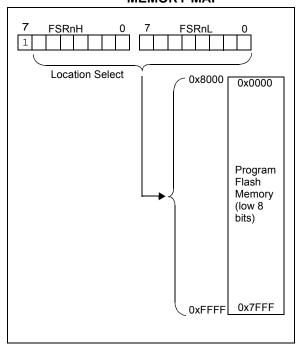

### 3.7.3 PROGRAM FLASH MEMORY

To make constant data access easier, the entire program Flash memory is mapped to the upper half of the FSR address space. When the MSB of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower eight bits of each memory location is accessible via INDF. Writing to the program Flash memory cannot be accomplished via the FSR/INDF interface. All instructions that access program Flash memory via the FSR/INDF interface will require one additional instruction cycle to complete.

FIGURE 3-12: PROGRAM FLASH MEMORY MAP

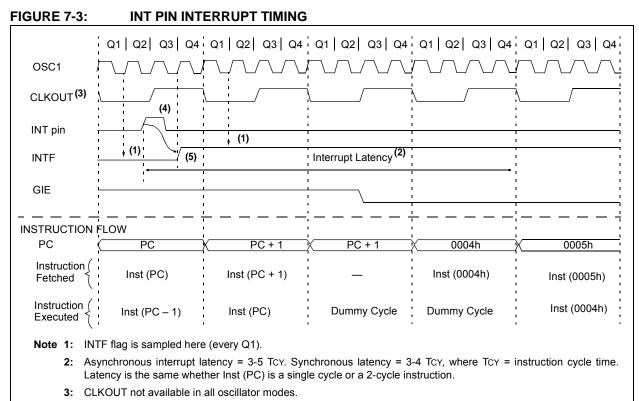

4: For minimum width of INT pulse, refer to AC specifications in Section 25.0 "Electrical Specifications".

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

### EXAMPLE 11-2: ERASING ONE ROW OF PROGRAM MEMORY

- ; This row erase routine assumes the following:

- ; 1. A valid address within the erase row is loaded in ADDRH:ADDRL

; 2. ADDRH and ADDRL are located in shared data memory  $0\,\mathrm{x}70$  -  $0\,\mathrm{x}7F$  (common RAM)

| BCF<br>BANKSEL<br>MOVF<br>MOVWF<br>MOVF<br>BCF<br>BSF<br>BSF      | INTCON,GIE<br>PMADRL<br>ADDRL,W<br>PMADRL<br>ADDRH,W<br>PMADRH<br>PMCON1,CFGS<br>PMCON1,FREE<br>PMCON1,WREN | <pre>; Disable ints so required sequences will execute properly ; Load lower 8 bits of erase address boundary ; Load upper 6 bits of erase address boundary ; Not configuration space ; Specify an erase operation ; Enable writes</pre>                                                                                                                                    |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BSF<br>MOVLW<br>MOVWF<br>MOVWF<br>BSF<br>NOP<br>NOP<br>BCF<br>BSF | PMCON1, WREN<br>55h<br>PMCON2<br>0AAh<br>PMCON2<br>PMCON1, WR<br>PMCON1, WREN<br>INTCON, GIE                | <pre>; Enable writes ; Start of required sequence to initiate erase ; Write 55h ; ; Write AAh ; Set WR bit to begin erase ; NOP instructions are forced as processor starts ; row erase of program memory. ; ; ; The processor stalls until the erase process is complete ; after erase processor continues with 3rd instruction ; Disable writes ; Enable interrupts</pre> |

#### 12.2 **PORTA Registers**

#### 12.2.1 DATA REGISTER

PORTA is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 12-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTA register (Register 12-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

#### 12.2.2 DIRECTION CONTROL

The TRISA register (Register 12-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 12.2.3 ANALOG CONTROL

The ANSELA register (Register 12-5) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

The ANSELA bits default to the Analog Note: mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

#### EXAMPLE 12-1: **INITIALIZING PORTA**

| ; | This code example illustrates         |

|---|---------------------------------------|

| ; | initializing the PORTA register. The  |

| ; | other ports are initialized in the sa |

| ; | manner.                               |

same

| BANKSEL | PORTA       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

| BANKSEL | LATA        | ;Data Latch            |

| CLRF    | LATA        | ;                      |

| BANKSEL | ANSELA      | ;                      |

| CLRF    | ANSELA      | ;digital I/O           |

| BANKSEL | TRISA       | ;                      |

| MOVLW   | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF   | TRISA       | ;and set RA<2:0> as    |

|         |             | ;outputs               |

#### 12.2.4 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-2.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown in the priority list.

| TABLE 12-2: | PORTA OUTPUT PRIORITY |

|-------------|-----------------------|

|-------------|-----------------------|

| Pin Name | Function Priority <sup>(1)</sup>    |

|----------|-------------------------------------|

| RA0      | RA0                                 |

| RA1      | RA1                                 |

| RA2      | RA2                                 |

| RA3      | RA3                                 |

| RA4      | RA4                                 |

| RA5      | VCAP (PIC16F1516/7/8/9 only)<br>RA5 |

| RA6      | CLKOUT<br>OSC2<br>RA6               |

| RA7      | RA7                                 |

**Note 1:** Priority listed from highest to lowest.

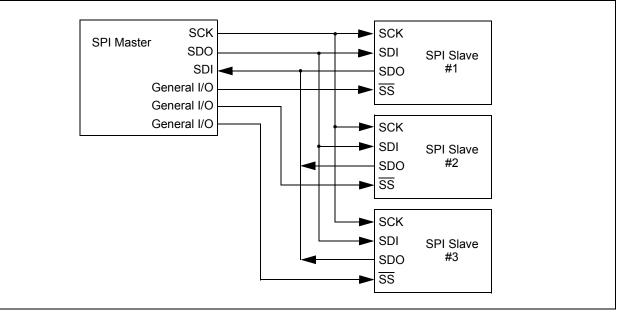

During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on its SDO pin) and the slave device is reading this bit and saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDO pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After eight bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data.

- Master sends useful data and slave sends useful data.

- Master sends dummy data and slave sends useful data.

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

## FIGURE 21-4: SPI MASTER AND MULTIPLE SLAVE CONNECTION

## 21.2.1 SPI MODE REGISTERS

The MSSP module has five registers for SPI mode operation. These are:

- MSSP STATUS register (SSPSTAT)

- MSSP Control register 1 (SSPCON1)

- MSSP Control register 3 (SSPCON3)

- MSSP Data Buffer register (SSPBUF)

- MSSP Address register (SSPADD)

- MSSP Shift register (SSPSR) (Not directly accessible)

SSPCON1 and SSPSTAT are the control and STA-TUS registers in SPI mode operation. The SSPCON1 register is readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write. In one SPI master mode, SSPADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section 21.7 "Baud Rate Generator"**.

SSPSR is the shift register used for shifting data in and out. SSPBUF provides indirect access to the SSPSR register. SSPBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPSR and SSPBUF together create a buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not buffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

# 21.3 I<sup>2</sup>C MODE OVERVIEW

The Inter-Integrated Circuit Bus (I<sup>2</sup>C) is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A Slave device is controlled through addressing.

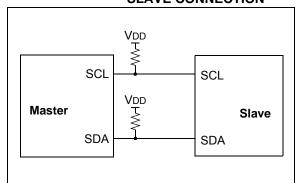

The I<sup>2</sup>C bus specifies two signal connections:

- Serial Clock (SCL)

- Serial Data (SDA)

Figure 21-1 shows the block diagram of the MSSP module when operating in  $I^2C$  mode.

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 21-11 shows a typical connection between two processors configured as master and slave devices.

The I<sup>2</sup>C bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode (master is transmitting data to a slave)

- Master Receive mode (master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDA line while the SCL line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

## FIGURE 21-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDA line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of a data bit is always performed while the SCL line is held low. Transitions that occur while the SCL line is held high are used to indicate Start and Stop bits.

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an  $\overrightarrow{ACK}$  bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an ACK bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDA line while the SCL line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last ACK bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

| TABLE 21-1: I-C BUS TERMS |                                                                                                                                                                                                      |  |  |  |  |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Term                      | Description                                                                                                                                                                                          |  |  |  |  |  |

| Transmitter               | The device which shifts data out onto the bus.                                                                                                                                                       |  |  |  |  |  |

| Receiver                  | The device which shifts data in from the bus.                                                                                                                                                        |  |  |  |  |  |

| Master                    | The device that initiates a transfer, generates clock signals and termi-<br>nates a transfer.                                                                                                        |  |  |  |  |  |

| Slave                     | The device addressed by the mas-<br>ter.                                                                                                                                                             |  |  |  |  |  |

| Multi-master              | A bus with more than one device that can initiate data transfers.                                                                                                                                    |  |  |  |  |  |

| Arbitration               | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                                  |  |  |  |  |  |

| Synchronization           | Procedure to synchronize the<br>clocks of two or more devices on<br>the bus.                                                                                                                         |  |  |  |  |  |

| Idle                      | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                                         |  |  |  |  |  |

| Active                    | Any time one or more master devices are controlling the bus.                                                                                                                                         |  |  |  |  |  |

| Addressed<br>Slave        | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                         |  |  |  |  |  |

| Matching<br>Address       | Address byte that is clocked into a slave that matches the value stored in SSPADD.                                                                                                                   |  |  |  |  |  |

| Write Request             | Slave receives a matching address with $R/\overline{W}$ bit clear, and is ready to clock in data.                                                                                                    |  |  |  |  |  |

| Read Request              | Master sends an address byte with<br>the $R/W$ bit set, indicating that it<br>wishes to clock data out of the<br>Slave. This data is the next and all<br>following bytes until a Restart or<br>Stop. |  |  |  |  |  |

| Clock Stretching          | When a device on the bus hold SCL low to stall communication.                                                                                                                                        |  |  |  |  |  |

| Bus Collision             | Any time the SDA line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                                           |  |  |  |  |  |

## TABLE 21-1: I<sup>2</sup>C BUS TERMS

### 21.4.5 START CONDITION

The  $I^2C$  specification defines a Start condition as a transition of SDA from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 21-12 shows wave forms for Start and Stop conditions.

A bus collision can occur on a Start condition if the module samples the SDA line low before asserting it low. This does not conform to the  $I^2C$  Specification that states no bus collision can occur on a Start.

## 21.4.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

| Note: | At least one SCL low time must appear         |

|-------|-----------------------------------------------|

|       | before a Stop is valid, therefore, if the SDA |

|       | line goes low then high again while the SCL   |

|       | line stays high, only the Start condition is  |

|       | detected.                                     |

## 21.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 21-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the  $R/\overline{W}$  bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with  $R/\overline{W}$  clear in 10-bit mode, a prior match flag is set and maintained. Until a Stop condition, a high address with  $R/\overline{W}$  clear, or high address match fails.

### 21.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

© 2010-2016 Microchip Technology Inc.

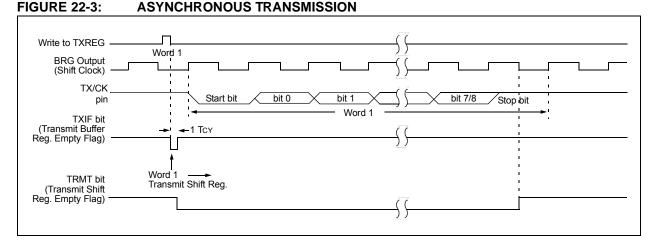

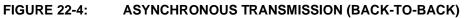

### 22.1.1.5 TSR Status

The TRMT bit of the TXSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

### 22.1.1.6 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXSTA register is set, the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXSTA register is the 9th, and Most Significant, data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 22.1.2.7** "Address **Detection**" for more information on the address mode.

### 22.1.1.7 Asynchronous Transmission Setup:

- 1. Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 22.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set 9th data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Set SCKP bit if inverted transmit is desired.

- Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 7. If 9-bit transmission is selected, the 9th bit should be loaded into the TX9D data bit.

- 8. Load 8-bit data into the TXREG register. This will start the transmission.

| Mnemonic, |      | Description                   | Cycles     | 14-Bit Opcode |      |      |      | Status   | Notes |

|-----------|------|-------------------------------|------------|---------------|------|------|------|----------|-------|

| Oper      | ands | Description                   |            | MSb           |      |      | LSb  | Affected | Notes |

|           |      | BYTE-ORIENTED FILE REG        | ISTER OPE  | RATIC         | NS   |      |      |          |       |

| ADDWF     | f, d | Add W and f                   | 1          | 00            | 0111 | dfff | ffff | C, DC, Z | 2     |

| ADDWFC    | f, d | Add with Carry W and f        | 1          | 11            | 1101 | dfff | ffff | C, DC, Z | 2     |

| ANDWF     | f, d | AND W with f                  | 1          | 00            | 0101 | dfff | ffff | Z        | 2     |

| ASRF      | f, d | Arithmetic Right Shift        | 1          | 11            | 0111 | dfff | ffff | C, Z     | 2     |

| LSLF      | f, d | Logical Left Shift            | 1          | 11            | 0101 | dfff | ffff | C, Z     | 2     |

| LSRF      | f, d | Logical Right Shift           | 1          | 11            | 0110 | dfff | ffff | C, Z     | 2     |

| CLRF      | f    | Clear f                       | 1          | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW      | -    | Clear W                       | 1          | 00            | 0001 | 0000 | 00xx | Z        |       |

| COMF      | f, d | Complement f                  | 1          | 00            | 1001 | dfff | ffff | Z        | 2     |

| DECF      | f, d | Decrement f                   | 1          | 00            | 0011 | dfff |      | Z        | 2     |

| INCF      | f, d | Increment f                   | 1          | 00            | 1010 | dfff | ffff | Z        | 2     |

| IORWF     | f, d | Inclusive OR W with f         | 1          | 00            | 0100 | dfff | ffff | Z        | 2     |

| MOVF      | f, d | Move f                        | 1          | 00            | 1000 | dfff | ffff | Z        | 2     |

| MOVWF     | f    | Move W to f                   | 1          | 00            | 0000 | lff  | ffff |          | 2     |

| RLF       | f, d | Rotate Left f through Carry   | 1          | 00            | 1101 | dfff | ffff | С        | 2     |

| RRF       | f, d | Rotate Right f through Carry  | 1          | 00            | 1100 | dfff | ffff | С        | 2     |

| SUBWF     | f, d | Subtract W from f             | 1          | 00            | 0010 | dfff | ffff | C, DC, Z | 2     |

| SUBWFB    | f, d | Subtract with Borrow W from f | 1          | 11            | 1011 | dfff | ffff | C, DC, Z | 2     |

| SWAPF     | f, d | Swap nibbles in f             | 1          | 00            | 1110 | dfff | ffff |          | 2     |

| XORWF     | f, d | Exclusive OR W with f         | 1          | 00            | 0110 | dfff | ffff | Z        | 2     |

|           |      | BYTE-ORIENTED SKI             | P OPERATIO | ONS           |      |      |      |          |       |

| DECFSZ    | f, d | Decrement f, Skip if 0        | 1(2)       | 00            | 1011 | dfff | ffff |          | 1, 2  |

| INCFSZ    | f, d | Increment f, Skip if 0        | 1(2)       | 00            | 1111 | dfff | ffff |          | 1, 2  |

|           |      | BIT-ORIENTED FILE REGI        | STER OPER  | RATION        | NS   |      |      | 1        |       |

| BCF       | f, b | Bit Clear f                   | 1          | 01            | 00bb | bfff | ffff |          | 2     |

| BSF       | f, b | Bit Set f                     | 1          | 01            | 01bb | bfff | ffff |          | 2     |

|           |      | BIT-ORIENTED SKIP             | OPERATIO   | NS            |      |      |      |          |       |

| BTFSC     | f, b | Bit Test f, Skip if Clear     | 1 (2)      | 01            | 10bb | bfff | ffff |          | 1, 2  |

| BTFSS     | f, b | Bit Test f, Skip if Set       | 1 (2)      | 01            | 11bb | bfff | ffff |          | 1, 2  |

| LITERAL   |      |                               |            |               |      |      |      | 1        |       |

| ADDLW     | k    | Add literal and W             | 1          | 11            | 1110 | kkkk |      | C, DC, Z |       |

| ANDLW     | k    | AND literal with W            | 1          | 11            | 1001 | kkkk | kkkk | Z        |       |

| IORLW     | k    | Inclusive OR literal with W   | 1          | 11            | 1000 | kkkk |      | Z        |       |

| MOVLB     | k    | Move literal to BSR           | 1          | 00            | 0000 | 001k |      |          |       |

| MOVLP     | k    | Move literal to PCLATH        | 1          | 11            | 0001 | 1kkk | kkkk |          |       |

| MOVLW     | k    | Move literal to W             | 1          | 11            |      | kkkk |      |          |       |

| SUBLW     | k    | Subtract W from literal       | 1          | 11            | 1100 |      |      | C, DC, Z |       |

| XORLW     | k    | Exclusive OR literal with W   | 1          | 11            | 1010 | kkkk | kkkk | Z        |       |

## TABLE 24-3: INSTRUCTION SET

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

### TABLE 24-3: INSTRUCTION SET (CONTINUED)

| Mnemonic, |      | Description                                   |        |     | 14-Bit | Opcode | 9    | Status   | Netes |

|-----------|------|-----------------------------------------------|--------|-----|--------|--------|------|----------|-------|

| Oper      | ands | Description                                   | Cycles | MSb |        |        | LSb  | Affected | Notes |

|           |      | CONTROL OPERA                                 | TIONS  |     |        |        |      |          |       |

| BRA       | k    | Relative Branch                               | 2      | 11  | 001k   | kkkk   | kkkk |          |       |

| BRW       | -    | Relative Branch with W                        | 2      | 00  | 0000   | 0000   | 1011 |          |       |

| CALL      | k    | Call Subroutine                               | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CALLW     | -    | Call Subroutine with W                        | 2      | 00  | 0000   | 0000   | 1010 |          |       |

| GOTO      | k    | Go to address                                 | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| RETFIE    | k    | Return from interrupt                         | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW     | k    | Return with literal in W                      | 2      | 11  | 0100   | kkkk   | kkkk |          |       |

| RETURN    | _    | Return from Subroutine                        | 2      | 00  | 0000   | 0000   | 1000 |          |       |

|           |      | INHERENT OPERA                                | TIONS  |     |        |        |      |          |       |

| CLRWDT    | _    | Clear Watchdog Timer                          | 1      | 00  | 0000   | 0110   | 0100 | TO, PD   |       |

| NOP       | -    | No Operation                                  | 1      | 00  | 0000   | 0000   | 0000 |          |       |

| OPTION    | -    | Load OPTION_REG register with W               | 1      | 00  | 0000   | 0110   | 0010 |          |       |

| RESET     | -    | Software device Reset                         | 1      | 00  | 0000   | 0000   | 0001 |          |       |

| SLEEP     | -    | Go into Standby mode                          | 1      | 00  | 0000   | 0110   | 0011 | TO, PD   |       |

| TRIS      | f    | Load TRIS register with W                     | 1      | 00  | 0000   | 0110   | Offf |          |       |

|           |      | C-COMPILER OPT                                | IMIZED |     |        |        |      | •        |       |

| ADDFSR    | n, k | Add Literal k to FSRn                         | 1      | 11  | 0001   | 0nkk   | kkkk |          |       |

| MOVIW     | n mm | Move Indirect FSRn to W with pre/post inc/dec | 1      | 00  | 0000   | 0001   | 0nmm | Z        | 2, 3  |

|           |      | modifier, mm                                  |        |     |        |        |      |          |       |

|           | k[n] | Move INDFn to W, Indexed Indirect.            | 1      | 11  | 1111   | 0nkk   | kkkk | Z        | 2     |

| MOVWI     | n mm | Move W to Indirect FSRn with pre/post inc/dec | 1      | 00  | 0000   | 0001   | 1nmm |          | 2, 3  |

|           |      | modifier, mm                                  |        |     |        |        |      |          |       |

|           | k[n] | Move W to INDFn, Indexed Indirect.            | 1      | 11  | 1111   | 1nkk   | kkkk |          | 2     |

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

3: See Table in the MOVIW and MOVWI instruction descriptions.

| RRF              | Rotate Right f through Carry                                                                                                                                                                                       |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                           |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                 |  |

| Operation:       | See description below                                                                                                                                                                                              |  |

| Status Affected: | С                                                                                                                                                                                                                  |  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |  |

|                  | C Register f                                                                                                                                                                                                       |  |

| SUBLW            | Subtract W from literal                                                                                                               |                 |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| Syntax:          | [label] Sl                                                                                                                            | JBLW k          |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                   |                 |  |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                             |                 |  |

| Status Affected: | C, DC, Z                                                                                                                              |                 |  |

| Description:     | The W register is subtracted (2's com-<br>plement method) from the 8-bit literal<br>'k'. The result is placed in the W regis-<br>ter. |                 |  |

|                  | <b>C</b> = 0                                                                                                                          | W > k           |  |

|                  | <b>C =</b> 1                                                                                                                          | $W \le k$       |  |

|                  | DC = 0                                                                                                                                | W<3:0> > k<3:0> |  |

|                  | DC = 1                                                                                                                                | W<3:0> ≤ k<3:0> |  |

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |

| Operands:        | None                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT}, \\ 0 \rightarrow \text{WDT prescaler}, \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$                                                |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |

| Description:     | The power-down Status bit, $\overline{\text{PD}}$ is cleared. Time-out Status bit, $\overline{\text{TO}}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into Sleep mode with the oscillator stopped. |

| SUBWF            | Subtract W from f                                                                                                                                                                          |                 |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| Syntax:          | [label] SU                                                                                                                                                                                 | JBWF f,d        |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                          |                 |  |

| Operation:       | (f) - $(W)$ → $(c)$                                                                                                                                                                        | lestination)    |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                   |                 |  |

| Description:     | Subtract (2's complement method) W<br>register from register 'f'. If 'd' is '0', the<br>result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f. |                 |  |

|                  | <b>C =</b> 0                                                                                                                                                                               | W > f           |  |

|                  | C = 1                                                                                                                                                                                      | $W \leq f$      |  |

|                  | DC = 0                                                                                                                                                                                     | W<3:0> > f<3:0> |  |

$W<3:0> \le f<3:0>$

| SUBWFB           | Subtract W from f with Borrow                                                                                                                                                                       |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | SUBWFB f {,d}                                                                                                                                                                                       |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                  |  |  |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                       |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                            |  |  |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's comple-<br>ment method). If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |

DC = 1

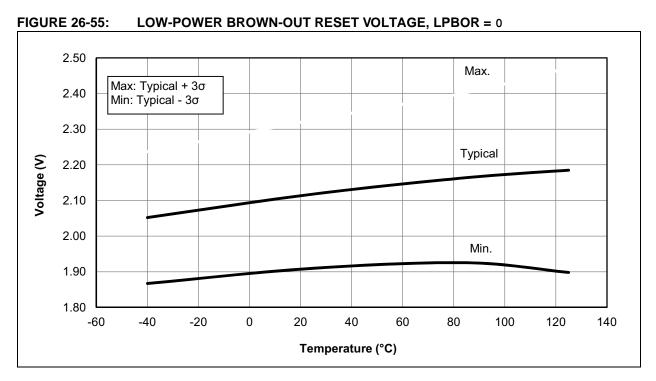

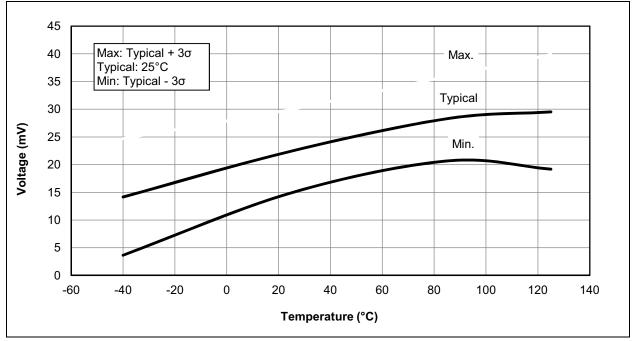

FIGURE 26-56: LOW-POWER BROWN-OUT RESET HYSTERESIS, LPBOR = 0

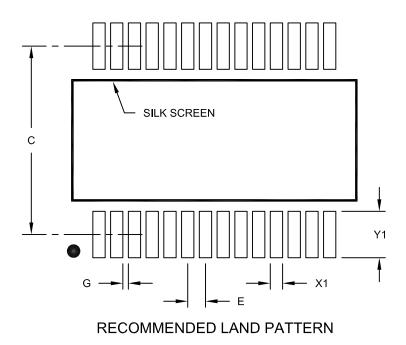

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |    | MILLIMETERS |          |      |

|--------------------------|----|-------------|----------|------|

| Dimension Limits         |    | MIN         | NOM      | MAX  |

| Contact Pitch            | E  |             | 0.65 BSC |      |

| Contact Pad Spacing      | С  |             | 7.20     |      |

| Contact Pad Width (X28)  | X1 |             |          | 0.45 |

| Contact Pad Length (X28) | Y1 |             |          | 1.75 |

| Distance Between Pads    | G  | 0.20        |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | [X] <sup>(1)</sup> - <u>X</u> /XX                                                                                                                                                   | XXX<br>Pattern | Examples:<br>a) PIC16F1516T - I/MV 301<br>Tape and Reel,<br>Industrial temperature,<br>UQFN package,                                                                                                                                                                                                                                                                                                                               |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                  | PIC16F1516, PIC16LF1516<br>PIC16F1517, PIC16LF1517<br>PIC16F1518, PIC16LF1518<br>PIC16F1519, PIC16LF1519                                                                            |                | QTP pattern #301<br>b) PIC16F1519 - I/P<br>Industrial temperature<br>PDIP package<br>c) PIC16F1518 - E/SS<br>Extended temperature,                                                                                                                                                                                                                                                                                                 |

| Tape and Reel<br>Option: | Blank = Standard packaging (tube or tray)<br>T = Tape and Reel <sup>(1)</sup>                                                                                                       |                | SSOP package                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Temperature<br>Range:    | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended)                                                                           |                |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Package: <sup>(2)</sup>  | ML = Thin Quad Flat, no lead (QFN)<br>MV = Ultra Thin Quad Flat, no lead (UQFN)<br>P = Plastic DIP (PDIP)<br>PT = TQFP<br>SO = SOIC<br>SP = Skinny Plastic DIP (SPDIP)<br>SS = SSOP |                | <ul> <li>Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and Reel option.</li> <li>2: For other small form-factor package availability and marking information, please visit www.microchip.com/packaging or</li> </ul> |

| Pattern:                 | QTP, SQTP, Code or Special Requirements (blank otherwise)                                                                                                                           |                | contact your local sales office.                                                                                                                                                                                                                                                                                                                                                                                                   |