Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1516-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

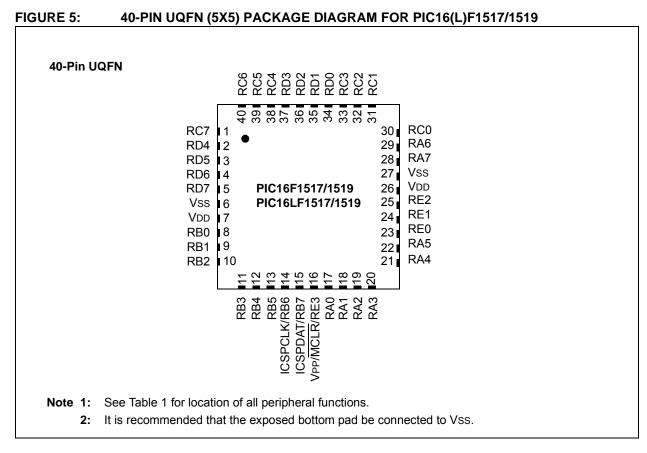

## PIC16(L)F1516/7/8/9

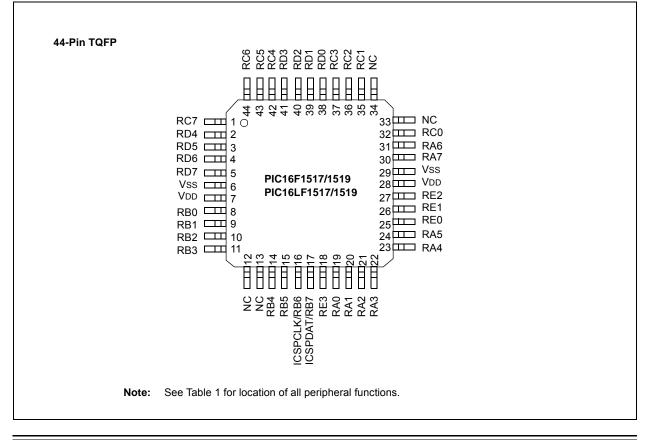

#### FIGURE 6: 44-PIN TQFP PACKAGE DIAGRAM FOR PIC16(L)F1517/1519

#### TABLE 1-2: PINOUT DESCRIPTION

| Name                            | Function | Input<br>Type | Output<br>Type | Description                                                    |  |  |  |

|---------------------------------|----------|---------------|----------------|----------------------------------------------------------------|--|--|--|

| RA0/AN0/SS <sup>(2)</sup>       | RA0      | TTL           | CMOS           | General purpose I/O.                                           |  |  |  |

|                                 | AN0      | AN            | _              | ADC Channel 0 input.                                           |  |  |  |

|                                 | SS       | ST            | _              | Slave Select input.                                            |  |  |  |

| RA1/AN1                         | RA1      | TTL           | CMOS           | General purpose I/O.                                           |  |  |  |

|                                 | AN1      | AN            | —              | ADC Channel 1 input.                                           |  |  |  |

| RA2/AN2                         | RA2      | TTL           | CMOS           | General purpose I/O.                                           |  |  |  |

|                                 | AN2      | AN            | _              | ADC Channel 2 input.                                           |  |  |  |

| RA3/AN3/VREF+                   | RA3      | TTL           | CMOS           | General purpose I/O.                                           |  |  |  |

|                                 | AN3      | AN            | _              | ADC Channel 3 input.                                           |  |  |  |

|                                 | VREF+    | AN            | _              | ADC Positive Voltage Reference input.                          |  |  |  |

| RA4/T0CKI                       | RA4      | TTL           | CMOS           | General purpose I/O.                                           |  |  |  |

|                                 | TOCKI    | ST            | _              | Timer0 clock input.                                            |  |  |  |

| RA5/AN4/SS <sup>(1)</sup> /VCAP | RA5      | TTL           | CMOS           | General purpose I/O.                                           |  |  |  |

|                                 | AN4      | AN            | —              | ADC Channel 4 input.                                           |  |  |  |

|                                 | SS       | ST            | _              | Slave Select input.                                            |  |  |  |

|                                 | VCAP     | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F1516/7/8/9 only) |  |  |  |

| RA6/OSC2/CLKOUT                 | RA6      | TTL           | CMOS           | General purpose I/O.                                           |  |  |  |

|                                 | OSC2     | —             | XTAL           | Crystal/Resonator (LP, XT, HS modes).                          |  |  |  |

|                                 | CLKOUT   | _             | CMOS           | Fosc/4 output.                                                 |  |  |  |

| RA7/OSC1/CLKIN                  | RA7      | TTL           | CMOS           | General purpose I/O.                                           |  |  |  |

|                                 | OSC1     | XTAL          | _              | Crystal/Resonator (LP, XT, HS modes).                          |  |  |  |

|                                 | CLKIN    | ST            | —              | External clock input (EC mode).                                |  |  |  |

| RB0/AN12/INT                    | RB0      | TTL           | CMOS           | General purpose I/O with IOC and WPU.                          |  |  |  |

|                                 | AN12     | AN            | _              | ADC Channel 12 input.                                          |  |  |  |

|                                 | INT      | ST            | —              | External interrupt.                                            |  |  |  |

| RB1/AN10                        | RB1      | TTL           | CMOS           | General purpose I/O with IOC and WPU.                          |  |  |  |

|                                 | AN10     | AN            | _              | ADC Channel 10 input.                                          |  |  |  |

| RB2/AN8                         | RB2      | TTL           | CMOS           | General purpose I/O with IOC and WPU.                          |  |  |  |

|                                 | AN8      | AN            | —              | ADC Channel 8 input.                                           |  |  |  |

| RB3/AN9/CCP2 <sup>(2)</sup>     | RB3      | TTL           | CMOS           | General purpose I/O with IOC and WPU.                          |  |  |  |

|                                 | AN9      | AN            | _              | ADC Channel 9 input.                                           |  |  |  |

|                                 | CCP2     | ST            | CMOS           | Capture/Compare/PWM 2.                                         |  |  |  |

| RB4/AN11                        | RB4      | TTL           | CMOS           |                                                                |  |  |  |

|                                 | AN11     | AN            | _              | ADC Channel 11 input.                                          |  |  |  |

| RB5/AN13/T1G                    | RB5      | TTL           | CMOS           | General purpose I/O with IOC and WPU.                          |  |  |  |

|                                 | AN13     | AN            | —              | ADC Channel 13 input.                                          |  |  |  |

|                                 | T1G      | ST            | _              | Timer1 Gate input.                                             |  |  |  |

| RB6/ICSPCLK                     | RB6      | TTL           | CMOS           | General purpose I/O with IOC and WPU.                          |  |  |  |

|                                 | ICSPCLK  | ST            | CMOS           | In-Circuit Data I/O.                                           |  |  |  |

| RB7/ICSPDAT                     | RB7      | TTL           | CMOS           | General purpose I/O with IOC and WPU.                          |  |  |  |

|                                 | ICSPDAT  | ST            | CMOS           | ICSP™ Data I/O.                                                |  |  |  |

AN = Analog input or output CMOS = CMOS compatible input or output OD = Open-Drain TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$

levels

Note 1: Peripheral pin location selected using APFCON register (Register 12-1). Default location.

XTAL = Crystal

2: Peripheral pin location selected using APFCON register (Register 12-1). Alternate location.

3: PORTD and RE<2:0> available on PIC16(L)F1517/9 only.

HV = High Voltage

|                     |                                                                                                                                                                                                                              | LVP                                                                                                                                          | DEBUG                                                                                                                                         | LPBOR                                                                                                                           | BORV                                                                       | STVREN                          | _     |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------|-------|

|                     |                                                                                                                                                                                                                              | bit 13                                                                                                                                       | ł                                                                                                                                             |                                                                                                                                 | L                                                                          |                                 | bit 8 |

|                     |                                                                                                                                                                                                                              |                                                                                                                                              |                                                                                                                                               |                                                                                                                                 |                                                                            |                                 |       |

| U-1                 | U-1                                                                                                                                                                                                                          | U-1                                                                                                                                          | R/P-1                                                                                                                                         | U-1                                                                                                                             | U-1                                                                        | R/P-1                           | R/P-1 |

| -                   | —                                                                                                                                                                                                                            | -                                                                                                                                            | VCAPEN <sup>(1)</sup>                                                                                                                         | _                                                                                                                               | —                                                                          | WRT<                            | :1:0> |

| bit 7               |                                                                                                                                                                                                                              |                                                                                                                                              |                                                                                                                                               |                                                                                                                                 |                                                                            |                                 | bit C |

|                     |                                                                                                                                                                                                                              |                                                                                                                                              |                                                                                                                                               |                                                                                                                                 |                                                                            |                                 |       |

| Legend:             |                                                                                                                                                                                                                              |                                                                                                                                              |                                                                                                                                               |                                                                                                                                 |                                                                            |                                 |       |

| R = Readable bit    |                                                                                                                                                                                                                              | P = Programma                                                                                                                                | ble bit                                                                                                                                       | U = Unimplemente                                                                                                                |                                                                            |                                 |       |

| 0' = Bit is cleared |                                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                             |                                                                                                                                               | -n = Value when b                                                                                                               | lank or after Bulk                                                         | Erase                           |       |

| bit 13              | 1 = Low-voltage                                                                                                                                                                                                              | ge Programming Ei<br>e prog <u>ramm</u> ing enal<br>e on MCLR must be                                                                        | bled                                                                                                                                          | ning                                                                                                                            |                                                                            |                                 |       |

| bit 12              | 1 = In-Circuit De                                                                                                                                                                                                            |                                                                                                                                              | CSPCLK and ICSPI                                                                                                                              | DAT are general pur<br>DAT are dedicated to                                                                                     |                                                                            |                                 |       |

| bit 11              |                                                                                                                                                                                                                              | ower BOR<br>BOR is disabled<br>BOR is enabled                                                                                                |                                                                                                                                               |                                                                                                                                 |                                                                            |                                 |       |

| bit 10              | 1 = Brown-out F                                                                                                                                                                                                              | out Reset Voltage S<br>Reset voltage (Vbor<br>Reset voltage (Vbor                                                                            | ), low trip point sele                                                                                                                        |                                                                                                                                 |                                                                            |                                 |       |

| bit 9               | 1 = Stack Overf                                                                                                                                                                                                              | < Overflow/Underflo<br>low or Underflow wi<br>low or Underflow wi                                                                            | Il cause a Reset                                                                                                                              |                                                                                                                                 |                                                                            |                                 |       |

| bit 8-5             | Unimplemente                                                                                                                                                                                                                 | d: Read as '1'                                                                                                                               |                                                                                                                                               |                                                                                                                                 |                                                                            |                                 |       |

| bit 4               | <u>If PIC16LF1516</u><br>These bits<br><u>If PIC16F1516/</u><br>0 = VCA                                                                                                                                                      | ge Regulator Capa<br>///8/9 (regulator dis<br>s are ignored. All Vo<br>7/8/9 (regulator ena<br>P functionality is en<br>/CAP pin functions a | <u>abled)</u> :<br>CAP pin functions are<br><u>bled)</u> :<br>abled on RA5                                                                    | e disabled.                                                                                                                     |                                                                            |                                 |       |

| bit 3-2             | Unimplemente                                                                                                                                                                                                                 | d: Read as '1'                                                                                                                               |                                                                                                                                               |                                                                                                                                 |                                                                            |                                 |       |

| bit 1-0             | 8 kW Flash mer           11 =         W           10 =         00           01 =         00           10 =         00           10 =         00           11 =         W           10 =         00           01 =         00 | 00h to FFFh write-p<br>00h to 1FFFh write-<br><u>emory (PIC16(L)F1</u><br>rite protection off<br>00h to 1FFh write-p<br>00h to 1FFh write-p  | 16/7 only):<br>otected, 200h to 1F<br>otected, 1000h to 1<br>protected, no addre<br>518/9 only):<br>otected, 200h to 3F<br>protected, 200h to | FFh may be modifie<br>FFFh may be modif<br>sses may be modifie<br>FFh may be modifie<br>3FFFh may be mod<br>sses may be modifie | ied by PMCON co<br>ed by PMCON con<br>ed by PMCON con<br>ified by PMCON co | ntrol<br>trol<br>trol<br>ontrol |       |

## $\ensuremath{\textcircled{}^{\odot}}$ 2010-2016 Microchip Technology Inc.

## 5.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

#### 5.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 5-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be supplied from one of two internal oscillators, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Two-Speed Start-up mode, which minimizes latency between external oscillator start-up and code execution.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, EC or RC modes) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability

of crystal oscillator sources

- Fast start-up oscillator allows internal circuits to power up and stabilize before switching to the 16 MHz HFINTOSC

The oscillator module can be configured in one of eight clock modes.

- 1. ECL External Clock Low-Power mode (0 MHz to 0.5 MHz)

- 2. ECM External Clock Medium-Power mode (0.5 MHz to 4 MHz)

- 3. ECH External Clock High-Power mode (4 MHz to 20 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (up to 4 MHz)

- HS High Gain Crystal or Ceramic Resonator mode (4 MHz to 20 MHz)

- 7. RC External Resistor-Capacitor (RC)

- 8. INTOSC Internal oscillator (31 kHz to 16 MHz)

Clock Source modes are selected by the FOSC<2:0> bits in the Configuration Words. The FOSC bits determine the type of oscillator that will be used when the device is first powered.

The EC clock mode relies on an external logic level signal as the device clock source. The LP, XT, and HS clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The RC clock mode requires an external resistor and capacitor to set the oscillator frequency.

The INTOSC internal oscillator block produces a low and high-frequency clock source, designated LFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 5-1). A wide selection of device clock frequencies may be derived from these two clock sources.

## 5.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Words. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, EC, RC and secondary oscillator).

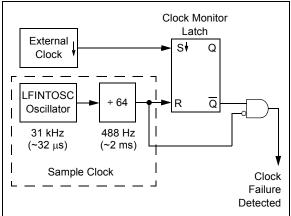

FIGURE 5-9: FSCM BLOCK DIAGRAM

## 5.5.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64 (see Figure 5-9). Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

#### 5.5.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<3:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

### 5.5.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the SCS bits of the OSCCON register. When the SCS bits are changed, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared after successfully switching to the external clock source. The OSFIF bit should be cleared prior to switching to the external clock source. If the Fail-Safe condition still exists, the OSFIF flag will again become set by hardware.

### 5.5.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

| Note: | Due to the wide range of oscillator start-up<br>times, the Fail-Safe circuit is not active<br>during oscillator start-up (i.e., after exiting<br>Reset or Sleep). After an appropriate |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | amount of time, the user should check the<br>Status bits in the OSCSTAT register to<br>verify the oscillator start-up and that the                                                     |

|       | system clock switchover has successfully<br>completed.                                                                                                                                 |

| R/W-0/       |                   | U-0                                          | U-0          | R/W-0/0         |                  | L-0            | R/W-0/0      |  |  |  |  |

|--------------|-------------------|----------------------------------------------|--------------|-----------------|------------------|----------------|--------------|--|--|--|--|

| OSFIF        |                   |                                              | _            | BCLIF           | _                | _              | CCP2IF       |  |  |  |  |

| bit 7        |                   |                                              |              | 201             |                  |                | bit          |  |  |  |  |

| Legend:      |                   |                                              |              |                 |                  |                |              |  |  |  |  |

| R = Read     | able bit          | W = Writable                                 | hit          | II – I Inimpler | mented bit, read | l as '0'       |              |  |  |  |  |

|              |                   | x = Bit is unki                              |              | •               | at POR and BO    |                | other Depote |  |  |  |  |

|              | unchanged         |                                              |              |                 | al POR and BO    | R/Value at all | other Resets |  |  |  |  |

| '1' = Bit is | set               | '0' = Bit is cle                             | ared         |                 |                  |                |              |  |  |  |  |

| bit 7        |                   | scillator Fail Interr                        | unt Flag hit |                 |                  |                |              |  |  |  |  |

|              | 1 = Interru       |                                              |              |                 |                  |                |              |  |  |  |  |

|              |                   | ipt is not pending                           |              |                 |                  |                |              |  |  |  |  |

| bit 6-4      |                   | nented: Read as '                            | 0'           |                 |                  |                |              |  |  |  |  |

| bit 3        | -                 | BCLIF: MSSP Bus Collision Interrupt Flag bit |              |                 |                  |                |              |  |  |  |  |

|              |                   | ipt is pending                               |              | 0               |                  |                |              |  |  |  |  |

|              | 0 = Interru       | ipt is not pending                           |              |                 |                  |                |              |  |  |  |  |

| bit 2-1      | Unimplen          | nented: Read as '                            | 0'           |                 |                  |                |              |  |  |  |  |

| bit 0        | CCP2IF: (         | CCP2 Interrupt Fla                           | ig bit       |                 |                  |                |              |  |  |  |  |

|              | 1 = Interru       | ipt is pending                               |              |                 |                  |                |              |  |  |  |  |

|              | 0 = Interru       | pt is not pending                            |              |                 |                  |                |              |  |  |  |  |

|              |                   |                                              |              |                 |                  |                |              |  |  |  |  |

| Note:        | Interrupt flag bi | ts are set when an                           | interrupt    |                 |                  |                |              |  |  |  |  |

|              |                   | s, regardless of the                         |              |                 |                  |                |              |  |  |  |  |

|              | •                 | ng enable bit or th                          |              |                 |                  |                |              |  |  |  |  |

|              |                   | E, of the INTCON                             | •            |                 |                  |                |              |  |  |  |  |

|              |                   | e should ensu                                | ure the      |                 |                  |                |              |  |  |  |  |

#### REGISTER 7-5: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

#### TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

appropriate interrupt flag bits are clear prior

to enabling an interrupt.

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2   | Bit 1  | Bit 0  | Register<br>on Page |

|------------|---------|--------|--------|--------|-------|---------|--------|--------|---------------------|

| INTCON     | GIE     | PEIE   | TMR0IE | INTE   | IOCIE | TMR0IF  | INTF   | IOCIF  | 74                  |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA   | PS<2:0> |        |        | 146                 |

| PIE1       | TMR1GIE | ADIE   | RCIE   | TXIE   | SSPIE | CCP1IE  | TMR2IE | TMR1IE | 75                  |

| PIE2       | OSFIE   | _      | —      | _      | BCLIE | -       | -      | CCP2IE | 76                  |

| PIR1       | TMR1GIF | ADIF   | RCIF   | TXIF   | SSPIF | CCP1IF  | TMR2IF | TMR1IF | 77                  |

| PIR2       | OSFIF   |        | —      | —      | BCLIF | _       | _      | CCP2IF | 78                  |

Legend: — = unimplemented locations read as '0'. Shaded cells are not used by Interrupts.

## 9.0 LOW DROPOUT (LDO) VOLTAGE REGULATOR

The PIC16F1516/7/8/9 has an internal Low Dropout Regulator (LDO) which provides operation above 3.6V. The LDO regulates a voltage for the internal device logic while permitting the VDD and I/O pins to operate at a higher voltage. There is no user enable/disable control available for the LDO, it is always active. The PIC16LF1516/7/8/9 operates at a maximum VDD of 3.6V and does not incorporate an LDO.

A device I/O pin may be configured as the LDO voltage output, identified as the VCAP pin. Although not required, an external low-ESR capacitor may be connected to the VCAP pin for additional regulator stability.

The  $\overline{\text{VCAPEN}}$  bit of Configuration Words enables or disables the VCAP pin. Refer to Table 9-1.

#### TABLE 9-1: VCAPEN SELECT BIT

| VCAPEN | Pin |

|--------|-----|

| 0      | RA5 |

On power-up, the external capacitor will load the LDO voltage regulator. To prevent erroneous operation, the device is held in Reset while a constant current source charges the external capacitor. After the cap is fully charged, the device is released from Reset. For more information on the constant current rate, refer to the LDO Regulator Characteristics Table in **Section 25.0** "Electrical Specifications".

#### TABLE 9-2: SUMMARY OF CONFIGURATION WORD WITH LDO

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

|         | 13:8 |         |         | LVP      | DEBUG    | LPBOR    | BORV     | STVREN  | —       | 40                  |

| CONFIG2 | 7:0  | -       |         | —        | VCAPEN   | -        |          | WRT     | <1:0>   | 43                  |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used by LDO.

Note 1: PIC16F1516/7/8/9 only.

| R/W-x/x                                 | R/W-x/x | R/W-x/x           | R/W-x/x | R/W-x/x                                               | R/W-x/x | R/W-x/x | R/W-x/x |  |

|-----------------------------------------|---------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|

| RA7                                     | RA6     | RA5               | RA4     | RA3                                                   | RA2     | RA1     | RA0     |  |

| bit 7                                   |         |                   |         |                                                       |         |         | bit 0   |  |

|                                         |         |                   |         |                                                       |         |         |         |  |

| Legend:                                 |         |                   |         |                                                       |         |         |         |  |

| R = Readable                            | bit     | W = Writable      | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |         |                   | iown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared    |                                                       |         |         |         |  |

|                                         |         |                   |         |                                                       |         |         |         |  |

#### REGISTER 12-2: PORTA: PORTA REGISTER

bit 7-0 RA<7:0>: PORTA I/O Value bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

#### REGISTER 12-3: TRISA: PORTA TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **TRISA<7:0>:** PORTA Tri-State Control bits

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is the return of actual I/O pin values.

## 13.0 INTERRUPT-ON-CHANGE

The PORTB pins can be configured to operate as Interrupt-On-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual PORTB pin, or combination of PORTB pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt on Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 13-1 is a block diagram of the IOC module.

## 13.1 Enabling the Module

To allow individual PORTB pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

## 13.2 Individual Pin Configuration

For each PORTB pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated IOCBPx bit of the IOCBP register is set. To enable a pin to detect a falling edge, the associated IOCBNx bit of the IOCBN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both the IOCBPx bit and the IOCBNx bit of the IOCBP and IOCBN registers, respectively.

## 13.3 Interrupt Flags

The IOCBFx bits located in the IOCBF register are status flags that correspond to the interrupt-on-change pins of PORTB. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCBFx bits.

## 13.4 Clearing Interrupt Flags

The individual status flags, (IOCBFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 13-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

## 13.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCBF register will be updated prior to the first instruction executed out of Sleep.

## 13.6 Register Definitions: Interrupt-on-change Control

| R/W-0/0         R/W-0/0 <t< th=""><th>OR/Value at all oth</th><th>ner Resets</th></t<> | OR/Value at all oth                | ner Resets |  |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------|--|--|--|--|--|--|--|--|--|

| IOCBP7 IOCBP6 IOCBP5 IOCBP4 IOCBP3 IOCBP2<br>bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | U = Unimplemented bit, read as '0' |            |  |  |  |  |  |  |  |  |  |

| IOCBP7 IOCBP6 IOCBP5 IOCBP4 IOCBP3 IOCBP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Legend:                            |            |  |  |  |  |  |  |  |  |  |

| IOCBP7 IOCBP6 IOCBP5 IOCBP4 IOCBP3 IOCBP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                    |            |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    | bit 0      |  |  |  |  |  |  |  |  |  |

| R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IOCBP1                             | IOCBP0     |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0/0                            | R/W-0/0    |  |  |  |  |  |  |  |  |  |

#### REGISTER 13-1: IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER

bit 7-0

1' = Bit is set

IOCBP<7:0>: Interrupt-on-Change PORTB Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

'0' = Bit is cleared

#### REGISTER 13-2: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | IOCBN3  | IOCBN2  | IOCBN1  | IOCBN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

**IOCBN<7:0>:** Interrupt-on-Change PORTB Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-3: IOCBF: INTERRUPT-ON-CHANGE PORTB FLAG REGISTER

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | IOCBF3     | IOCBF2     | IOCBF1     | IOCBF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

IOCBF7:0>: Interrupt-on-Change PORTB Flag bits

1 = An enabled change was detected on the associated pin.

- Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was detected on RBx.

- 0 = No change was detected, or the user cleared the detected change.

#### 17.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A software programmable prescaler is available for exclusive use with Timer0. The prescaler is enabled by clearing the PSA bit of the OPTION\_REG register.

| Note: | The Watchdog Timer (WDT) uses its own |

|-------|---------------------------------------|

|       | independent prescaler.                |

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION\_REG register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be disabled by setting the PSA bit of the OPTION\_REG register.

The prescaler is not readable or writable. All instructions writing to the TMR0 register will clear the prescaler.

### 17.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The TMR0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The TMR0IF bit can only be cleared in software. The Timer0 interrupt enable is the TMR0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |

|-------|-----------------------------------------|

|       | processor from Sleep since the timer is |

|       | frozen during Sleep.                    |

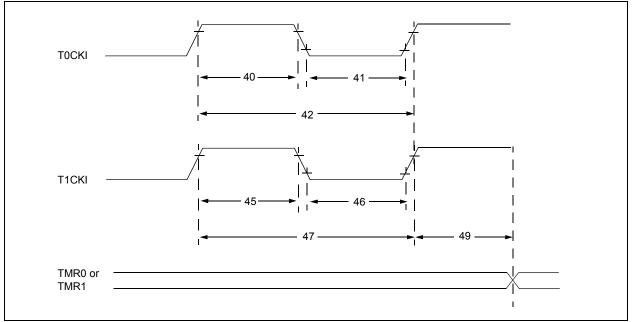

#### 17.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 25.0 "Electrical Specifications"**.

## 17.1.6 OPERATION DURING SLEEP

Timer0 cannot operate while the processor is in Sleep mode. The contents of the TMR0 register will remain unchanged while the processor is in Sleep mode.

## 19.5 Register Definitions: Timer2 Control

| U-0            | R/W-0/0                                        | R/W-0/0                                        | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |  |  |

|----------------|------------------------------------------------|------------------------------------------------|----------------|----------------|------------------|----------------|--------------|--|--|

| _              |                                                | T2OUT                                          | PS<3:0>        |                | TMR2ON           | T2CKF          | 'S<1:0>      |  |  |

| bit 7          |                                                |                                                |                |                |                  |                | bit          |  |  |

|                |                                                |                                                |                |                |                  |                |              |  |  |

| Legend:        |                                                |                                                |                |                |                  |                |              |  |  |

| R = Readal     |                                                | W = Writable                                   |                | -              | mented bit, read |                |              |  |  |

| u = Bit is ur  | -                                              | x = Bit is unkr                                | iown           | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |  |  |

| '1' = Bit is s | et                                             | '0' = Bit is clea                              | ared           |                |                  |                |              |  |  |

| bit 7          | Unimpleme                                      | ented: Read as '                               | 0'             |                |                  |                |              |  |  |

| bit 6-3        | T2OUTPS<                                       | 3:0>: Timer2 Ou                                | tput Postscale | er Select bits |                  |                |              |  |  |

|                | 1111 <b>= 1:16</b>                             | 1111 = 1:16 Postscaler                         |                |                |                  |                |              |  |  |

|                | 1110 <b>= 1:15</b>                             | 1110 = 1:15 Postscaler                         |                |                |                  |                |              |  |  |

|                | 1101 = 1:14 Postscaler                         |                                                |                |                |                  |                |              |  |  |

|                | 1100 = 1:13 Postscaler                         |                                                |                |                |                  |                |              |  |  |

|                | 1011 = 1:12 Postscaler                         |                                                |                |                |                  |                |              |  |  |

|                | 1010 = 1:11 Postscaler                         |                                                |                |                |                  |                |              |  |  |

|                | 1001 = 1:10 Postscaler                         |                                                |                |                |                  |                |              |  |  |

|                |                                                | 1000 = 1:9 Postscaler                          |                |                |                  |                |              |  |  |

|                | 0111 = 1:8 Postscaler<br>0110 = 1:7 Postscaler |                                                |                |                |                  |                |              |  |  |

|                | 0110 = 1.7 Postscaler<br>0101 = 1.6 Postscaler |                                                |                |                |                  |                |              |  |  |

|                |                                                | 0101 - 1.6 Postscaler                          |                |                |                  |                |              |  |  |

|                | 0011 = 1:4 Postscaler                          |                                                |                |                |                  |                |              |  |  |

|                | 0010 = 1:3 Postscaler                          |                                                |                |                |                  |                |              |  |  |

|                | 0001 = 1:2                                     | 0001 = 1:2 Postscaler                          |                |                |                  |                |              |  |  |

|                | 0000 = 1:1                                     | Postscaler                                     |                |                |                  |                |              |  |  |

| bit 2          | TMR2ON: T                                      | ïmer2 On bit                                   |                |                |                  |                |              |  |  |

|                | 1 = Timer2                                     | 1 = Timer2 is ON                               |                |                |                  |                |              |  |  |

|                | 0 = Timer2 is OFF                              |                                                |                |                |                  |                |              |  |  |

| bit 1-0        | T2CKPS<1:                                      | T2CKPS<1:0>: Timer2 Clock Prescale Select bits |                |                |                  |                |              |  |  |

|                | 11 = Prescaler is 64                           |                                                |                |                |                  |                |              |  |  |

|                | 10 = Presca                                    |                                                |                |                |                  |                |              |  |  |

|                | 01 = Presca                                    |                                                |                |                |                  |                |              |  |  |

|                | 00 = Presca                                    |                                                |                |                |                  |                |              |  |  |

## REGISTER 19-1: T2CON: TIMER2 CONTROL REGISTER

#### 21.2 SPI Mode Overview

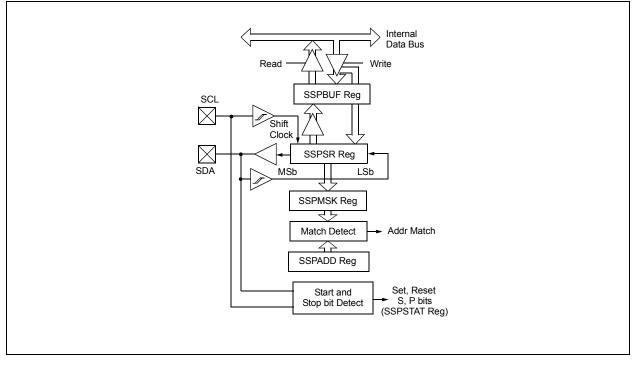

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select.

The SPI bus specifies four signal connections:

- Serial Clock (SCK)

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Slave Select (SS)

Figure 21-1 shows the block diagram of the MSSP module when operating in SPI mode.

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 21-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected. Transmissions involve two shift registers, eight bits in size, one in the master and one in the slave. With either the master or the slave device, data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 21-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.

The master device transmits information out on its SDO output pin which is connected to, and received by, the slave's SDI input pin. The slave device transmits information out on its SDO output pin, which is connected to, and received by, the master's SDI input pin.

To begin communication, the master device first sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

The master device starts a transmission by sending out the MSb from its shift register. The slave device reads this bit from that same line and saves it into the LSb position of its shift register.

## PIC16(L)F1516/7/8/9

During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on its SDO pin) and the slave device is reading this bit and saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDO pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After eight bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data.

- Master sends useful data and slave sends useful data.

- Master sends dummy data and slave sends useful data.

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

## FIGURE 21-4: SPI MASTER AND MULTIPLE SLAVE CONNECTION

## 21.2.1 SPI MODE REGISTERS

The MSSP module has five registers for SPI mode operation. These are:

- MSSP STATUS register (SSPSTAT)

- MSSP Control register 1 (SSPCON1)

- MSSP Control register 3 (SSPCON3)

- MSSP Data Buffer register (SSPBUF)

- MSSP Address register (SSPADD)

- MSSP Shift register (SSPSR) (Not directly accessible)

SSPCON1 and SSPSTAT are the control and STA-TUS registers in SPI mode operation. The SSPCON1 register is readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write. In one SPI master mode, SSPADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section 21.7 "Baud Rate Generator"**.

SSPSR is the shift register used for shifting data in and out. SSPBUF provides indirect access to the SSPSR register. SSPBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPSR and SSPBUF together create a buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not buffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

When one device is transmitting a logical one, or letting the line float, and a second device is transmitting a logical zero, or holding the line low, the first device can detect that the line is not a logical one. This detection, when used on the SCL line, is called clock stretching. Clock stretching gives slave devices a mechanism to control the flow of data. When this detection is used on the SDA line, it is called arbitration. Arbitration ensures that there is only one master device communicating at any single time.

## 21.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of clock stretching. An addressed slave device may hold the SCL clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCL line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCL connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

#### 21.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDA data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDA line.

For example, if one transmitter holds the SDA line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDA line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDA line. If this transmitter is also a master device, it also must stop driving the SCL line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDA line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message. Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

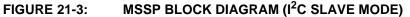

## 21.4 I<sup>2</sup>C MODE OPERATION

All MSSP I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

#### 21.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the 8th falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

## 21.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips  $I^2C$  specification.

#### 21.4.3 SDA AND SCL PINS

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

**Note:** Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

#### 21.4.4 SDA HOLD TIME