#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

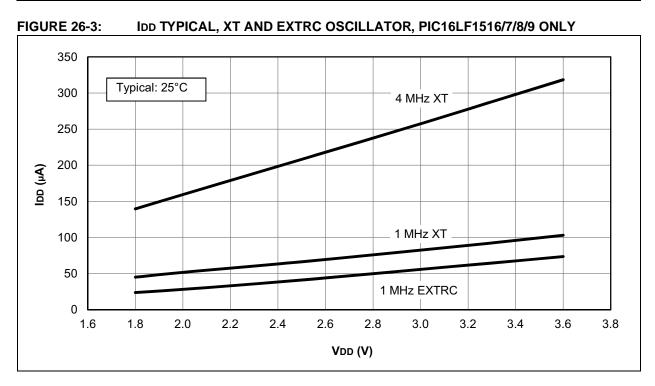

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1516-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.3.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{TO}$  and  $\overline{PD}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

#### 3.4 **Register Definitions: Status**

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 24.0 "Instruction Set Summary").

Note 1: The C and DC bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction.

#### **REGISTER 3-1:** STATUS: STATUS REGISTER

|       | • • • • • • |     |       |       |         |                   |                  |

|-------|-------------|-----|-------|-------|---------|-------------------|------------------|

| U-0   | U-0         | U-0 | R-1/q | R-1/q | R/W-0/u | R/W-0/u           | R/W-0/u          |

| —     | _           |     | TO    | PD    | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7 |             |     |       |       |         |                   | bit 0            |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-out bit                                                                                                                                                        |

|         | <ul> <li>1 = After power-up, CLRWDT instruction or SLEEP instruction</li> <li>0 = A WDT time-out occurred</li> </ul>                                                    |

| bit 3   | PD: Power-down bit                                                                                                                                                      |

|         | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                                                  |

| bit 2   | Z: Zero bit                                                                                                                                                             |

|         | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                  |

| bit 1   | DC: Digit Carry/Digit Borrow bit <sup>(1)</sup>                                                                                                                         |

|         | <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul>                |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup>                                                                                                                                      |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement                                                                          |

nt of the second operand.

# 4.2 Register Definitions: Configuration Words

### REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1

|                      |                                                                                                                                                                                                                           | R/P-1                                                                                                                                    | R/P-1                                                                                                                                        | R/P-1                                                                                                                                                            | R/P-1                                                               | R/P-1             | U-1   |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------|-------|

|                      |                                                                                                                                                                                                                           | FCMEN                                                                                                                                    | IESO                                                                                                                                         | CLKOUTEN                                                                                                                                                         | BORE                                                                | EN<1:0>           | _     |

|                      |                                                                                                                                                                                                                           | bit 13                                                                                                                                   |                                                                                                                                              |                                                                                                                                                                  |                                                                     |                   | bit 8 |

|                      |                                                                                                                                                                                                                           |                                                                                                                                          |                                                                                                                                              |                                                                                                                                                                  |                                                                     |                   |       |

| R/P-1                | R/P-1                                                                                                                                                                                                                     | R/P-1                                                                                                                                    | R/P-1                                                                                                                                        | R/P-1                                                                                                                                                            | R/P-1                                                               | R/P-1             | R/P-1 |

| CP                   | MCLRE                                                                                                                                                                                                                     | PWRTE                                                                                                                                    | WD.                                                                                                                                          | FE<1:0>                                                                                                                                                          |                                                                     | FOSC<2:0>         |       |

| bit 7                |                                                                                                                                                                                                                           |                                                                                                                                          |                                                                                                                                              |                                                                                                                                                                  |                                                                     |                   | bit ( |

| Legend:              |                                                                                                                                                                                                                           |                                                                                                                                          |                                                                                                                                              |                                                                                                                                                                  |                                                                     |                   |       |

| R = Readable bit     |                                                                                                                                                                                                                           | P = Programmab                                                                                                                           | e bit                                                                                                                                        | U = Unimplemente                                                                                                                                                 | d bit, read as '1'                                                  |                   |       |

| '0' = Bit is cleared |                                                                                                                                                                                                                           | '1' = Bit is set                                                                                                                         |                                                                                                                                              | -n = Value when bl                                                                                                                                               | ank or after Bulk                                                   | Erase             |       |

|                      |                                                                                                                                                                                                                           |                                                                                                                                          |                                                                                                                                              |                                                                                                                                                                  |                                                                     |                   |       |

| bit 13               | 1 = Fail-Safe Cloo                                                                                                                                                                                                        | e Clock Monitor En<br>ck Monitor is enable<br>ck Monitor is disabl                                                                       | ed                                                                                                                                           |                                                                                                                                                                  |                                                                     |                   |       |

| bit 12               | 1 = Internal/Exter                                                                                                                                                                                                        | ternal Switchover b<br>nal Switchover mo<br>nal Switchover mo                                                                            | de is enabled                                                                                                                                |                                                                                                                                                                  |                                                                     |                   |       |

| bit 11               | This bit is igr<br>All other FOSC m<br>1 = CLKOU                                                                                                                                                                          | ation bits are set to<br>nored, CLKOUT fur<br>nodes:                                                                                     | nction is disabled.                                                                                                                          | Oscillator function on on the CLKOUT pin.                                                                                                                        | the CLKOUT pir                                                      | ı.                |       |

| bit 10-9             | 11 = BOR enable<br>10 = BOR enable                                                                                                                                                                                        | d during operation                                                                                                                       | and disabled in S                                                                                                                            |                                                                                                                                                                  |                                                                     |                   |       |

| bit 8                | Unimplemented:                                                                                                                                                                                                            | Read as '1'                                                                                                                              |                                                                                                                                              |                                                                                                                                                                  |                                                                     |                   |       |

| bit 7                |                                                                                                                                                                                                                           | tion bit<br>nory code protectio<br>nory code protectio                                                                                   |                                                                                                                                              |                                                                                                                                                                  |                                                                     |                   |       |

| bit 6                | $\frac{\text{If LVP bit = 1:}}{\text{This bit is igr}}$ $\frac{\text{If LVP bit = 0:}}{1 = MCLR}$                                                                                                                         | /PP pin function is<br>/PP pin function is di                                                                                            | CLR; Wea <u>k pull-u</u>                                                                                                                     | o enabled.<br>nternally disabled; We                                                                                                                             | ak pull-up under c                                                  | ontrol of         |       |

| bit 5                | <b>PWRTE:</b> Power-u<br>1 = PWRT disal<br>0 = PWRT enab                                                                                                                                                                  |                                                                                                                                          |                                                                                                                                              |                                                                                                                                                                  |                                                                     |                   |       |

| bit 4-3              | 11 = WDT enabl<br>10 = WDT enabl                                                                                                                                                                                          | led while running a<br>olled by the SWDT                                                                                                 | nd disabled in Sle                                                                                                                           |                                                                                                                                                                  |                                                                     |                   |       |

| bit 2-0              | 111 =         ECH: Ex           110 =         ECM: Ex           101 =         ECL: Ext           100 =         INTOSC           011 =         EXTRC 0           010 =         HS oscill           001 =         XT oscill | ternal Clock, Media<br>ternal Clock, Low-F<br>oscillator: I/O func<br>oscillator: External<br>ator: High-speed c<br>ator: Crystal/resona | Power mode (4-2)<br>um-Power mode (<br>ower mode (0-0.<br>tion on CLKIN pin<br>RC circuit connec<br>rystal/resonator co<br>ator connected be | 0 MHz): device clock s<br>0.5-4 MHz): device clo<br>5 MHz): device clock s<br>ted to CLKIN pin<br>onnected between OS<br>tween OSC1 and OS<br>etween OSC1 and OS | ock supplied to C<br>supplied to CLKIN<br>C1 and OSC2 pi<br>C2 pins | LKIN pin<br>I pin |       |

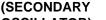

#### 5.2.1.4 Secondary Oscillator

The secondary oscillator is a separate crystal oscillator that is associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the SOSCO and SOSCI device pins.

The secondary oscillator can be used as an alternate system clock source and can be selected during run time using clock switching. Refer to **Section 5.3 "Clock Switching"** for more information.

#### FIGURE 5-5:

OPERATION

QUARTZ CRYSTAL

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices (DS00826)

- AN849, Basic PIC<sup>®</sup> Oscillator Design (DS00849)

- AN943, Practical PIC<sup>®</sup> Oscillator Analysis and Design (DS00943)

- AN949, Making Your Oscillator Work (DS00949)

- TB097, Interfacing a Micro Crystal MS1V-T1K 32.768 kHz Tuning Fork Crystal to a PIC16F690/SS (DS91097)

- AN1288, Design Practices for Low-Power External Oscillators (DS01288)

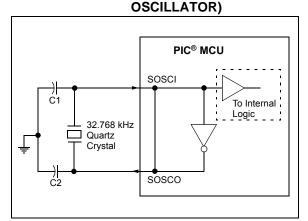

### 5.2.1.5 External RC Mode

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required.

The RC circuit connects to OSC1. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

Figure 5-6 shows the external RC mode connections.

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- · threshold voltage variation

- component tolerances

- packaging variations in capacitance

The user also needs to take into account variation due to tolerance of the external RC components used.

#### 8.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared

- If the interrupt occurs **during or after** the execution of a SLEEP instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

| OSC1 <sup>(1)</sup><br>CLKOUT <sup>(2)</sup> | 1                                                                                           | Q1 Q2 Q3  Q4                             | <u></u>               | Tost <sup>(3)</sup> |                 | Q1 Q2 Q3 Q4<br>/~_/~_/ | Q1 Q2 Q3 Q4<br>//////////////////////////////////// | Q1 Q2 Q3 Q4<br>     |

|----------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------|-----------------------|---------------------|-----------------|------------------------|-----------------------------------------------------|---------------------|

| Interrupt flag                               | 1<br>H                                                                                      | 1<br>+                                   | ·                     |                     | Interrupt Laten | cy <sup>(4)</sup>      | · · ·                                               |                     |

| GIE bit<br>(INTCON reg.)                     | '                                                                                           | I<br>I<br>I<br>I<br>I<br>I               | Processor in<br>Sleep |                     |                 | ·                      |                                                     |                     |

| Instruction Flow                             | ,<br>,<br>,                                                                                 | 1<br>1<br>1                              | 1                     | 1<br>1              | ·<br>·          | 1<br>1<br>1            | , , , , , , , , , , , , , , , , , , ,               | 1                   |

| PC                                           | X PC                                                                                        | X PC + 1                                 | X PC                  | + 2                 | X PC + 2        | X PC + 2               | <u>χ 0004h</u>                                      | X 0005h             |

| Instruction {<br>Fetched                     | Inst(PC) = Sleep                                                                            | Inst(PC + 1)                             |                       |                     | Inst(PC + 2)    | י<br>ו<br>ו            | Inst(0004h)                                         | Inst(0005h)         |

| Instruction {<br>Executed {                  | Inst(PC - 1)                                                                                | Sleep                                    | 1<br>1<br>1           |                     | Inst(PC + 1)    | Forced NOP             | Forced NOP                                          | Inst(0004h)         |

| 2: (<br>3:                                   | XT, HS or LP Oscil<br>CLKOUT is not ava<br>Tost=1024 Tosc. <sup>-</sup><br>Speed Clock Star | ailable in XT, HS,<br>This delay does no | or LP Oscillato       |                     | ·               | 0                      |                                                     | e Section 5.4 "Two- |

4: GIE = 1 assumed. In this case after wake-up, the processor calls the ISR at 0004h. If GIE = 0, execution will continue in-line.

#### FIGURE 8-1: WAKE-UP FROM SLEEP THROUGH INTERRUPT

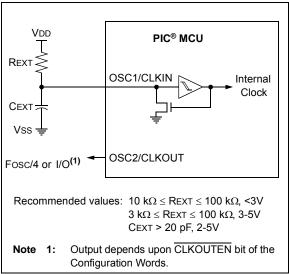

# 10.0 WATCHDOG TIMER (WDT)

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- · Independent clock source

- · Multiple operating modes

- WDT is always ON

- WDT is OFF when in Sleep

- WDT is controlled by software

- WDT is always OFF

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Multiple Reset conditions

- Operation during Sleep

## 11.5 Write Verify

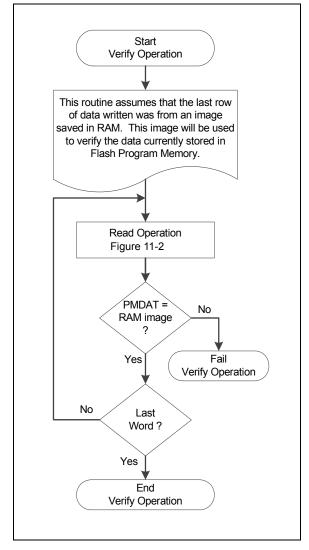

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full page then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

FIGURE 11-8: FLASH PROGRAM MEMORY VERIFY FLOWCHART

| U-0                                                                                  | U-0        | U-0               | U-0          | R/W-1/1                                               | U-0    | U-0 | U-0   |  |  |

|--------------------------------------------------------------------------------------|------------|-------------------|--------------|-------------------------------------------------------|--------|-----|-------|--|--|

| —                                                                                    | _          |                   |              | WPUE3                                                 | _      | —   | —     |  |  |

| bit 7                                                                                | 7          |                   |              |                                                       |        |     | bit 0 |  |  |

|                                                                                      |            |                   |              |                                                       |        |     |       |  |  |

| Legend:                                                                              |            |                   |              |                                                       |        |     |       |  |  |

| R = Readab                                                                           | le bit     | bit               | U = Unimpler | mented bit, read                                      | as '0' |     |       |  |  |

| u = Bit is un                                                                        | changed    | x = Bit is unkn   | iown         | -n/n = Value at POR and BOR/Value at all other Resets |        |     |       |  |  |

| '1' = Bit is se                                                                      | et         | '0' = Bit is clea | ared         |                                                       |        |     |       |  |  |

| bit 7-4                                                                              | Unimplomon | ted: Dood op '    | <u>,</u>     |                                                       |        |     |       |  |  |

|                                                                                      | -          | ted: Read as '    |              |                                                       |        |     |       |  |  |

| bit 3 WPUE: Weak Pull-up Register bit<br>1 = Pull-up enabled<br>0 = Pull-up disabled |            |                   |              |                                                       |        |     |       |  |  |

# REGISTER 12-23: WPUE: WEAK PULL-UP PORTE REGISTER<sup>(1,2)</sup>

bit 2-0 Unimplemented: Read as '0'

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

| Name                  | Bit 7 | Bit 6       | Bit 5 | Bit 4    | Bit 3 | Bit 2                | Bit 1                 | Bit 0                | Register<br>on Page |

|-----------------------|-------|-------------|-------|----------|-------|----------------------|-----------------------|----------------------|---------------------|

| ADCON0                |       |             |       | CHS<4:0> |       |                      | GO/DONE               | ADON                 | 137                 |

| ANSELE <sup>(1)</sup> | _     | —           | _     | _        | _     | ANSE2                | ANSE1                 | ANSE0                | 121                 |

| CCPxCON               | —     | — DCxB<1:0> |       |          |       | CCPx                 |                       | 168                  |                     |

| LATE                  | —     | —           | _     | _        | —     | LATE2 <sup>(1)</sup> | LATE1 <sup>(1)</sup>  | LATE0 <sup>(1)</sup> | 121                 |

| PORTE                 | _     | _           | _     | _        | RE3   | RE2 <sup>(1)</sup>   | RE1 <sup>(1)</sup>    | RE0 <sup>(1)</sup>   | 120                 |

| TRISE                 | —     | —           | —     | _        | (2)   | TRISE2(1)            | TRISE1 <sup>(1)</sup> | TRISE0(1)            | 120                 |

| WPUE                  | _     | _           | _     | —        | WPUE3 | _                    | _                     | _                    | 122                 |

#### TABLE 12-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTE.

Note 1: These bits are not implemented on the PIC16(L)F1516/8 devices, read as '0'.

2: Unimplemented, read as '1'.

#### TABLE 12-11: SUMMARY OF CONFIGURATION WORD WITH PORTE

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2 | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|----------|-----------|---------|---------------------|

|         | 13:8 |         |         | FCMEN    | IESO      | CLKOUTEN | BOREI    | N<1:0>    | —       | 40                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          |          | FOSC<2:0> |         | 42                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTE.

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELB |        |        | ANSB5  | ANSB4  | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 112                 |

| INTCON | GIE    | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 74                  |

| IOCBF  | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3 | IOCBP2 | IOCBP1 | IOCBP0 | 125                 |

| IOCBN  | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3 | IOCBN2 | IOCBN1 | IOCBN0 | 125                 |

| IOCBP  | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3 | IOCBF2 | IOCBF1 | IOCBF0 | 125                 |

| TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 111                 |

### TABLE 13-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Interrupt-on-Change.

# **16.4 ADC Acquisition Requirements**

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 16-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 16-4. **The maximum recommended impedance for analog sources is 10 k** $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 16-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

### EQUATION 16-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature = 50°C and external impedance of 10k

$$\Omega$$

5.0V VDD

$$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient

= TAMP + TC + TCOFF

= 2µs + TC + [(Temperature - 25°C)(0.05µs/°C)]

The value for TC can be approximated with the following equations:

$$VAPPLIED\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = VCHOLD \qquad :[1] VCHOLD charged to within 1/2 lsb

VAPPLIED\left(1 - e^{\frac{-TC}{RC}}\right) = VCHOLD \qquad :[2] VCHOLD charge response to VAPPLIED

$$VAPPLIED\left(1 - e^{\frac{-TC}{RC}}\right) = VCHOLD \qquad :[2] VCHOLD charge response to VAPPLIED

VAPPLIED\left(1 - e^{\frac{-TC}{RC}}\right) = VAPPLIED\left(1 - \frac{1}{(2^{n+1}) - 1}\right) \qquad :combining [1] and [2]

Note: Where n = number of bits of the ADC.

Solving for TC:

$$TC = -CHOLD(RIC + RSS + RS) \ln(1/2047) = -13.5pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885) = 1.20µs$$$$$$$$

Therefore:

$$TACQ = 2\mu s + 1.20\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.45\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

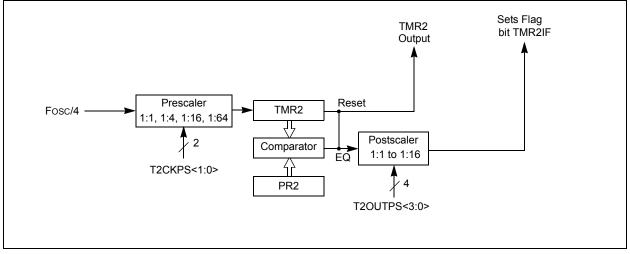

# 19.0 TIMER2 MODULE

The Timer2 module incorporates the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match with PR2, respectively

- Optional use as the shift clock for the MSSP modules

See Figure 19-1 for a block diagram of Timer2.

| TABLE 21-1:         | I-C BUS TERMS                                                                                                                                                                                        |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Term                | Description                                                                                                                                                                                          |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                                       |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                                        |

| Master              | The device that initiates a transfer,<br>generates clock signals and termi-<br>nates a transfer.                                                                                                     |

| Slave               | The device addressed by the mas-<br>ter.                                                                                                                                                             |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                                    |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                                  |

| Synchronization     | Procedure to synchronize the<br>clocks of two or more devices on<br>the bus.                                                                                                                         |

| Idle                | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                                         |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                                         |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                         |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPADD.                                                                                                                   |

| Write Request       | Slave receives a matching address with $R/\overline{W}$ bit clear, and is ready to clock in data.                                                                                                    |

| Read Request        | Master sends an address byte with<br>the $R/W$ bit set, indicating that it<br>wishes to clock data out of the<br>Slave. This data is the next and all<br>following bytes until a Restart or<br>Stop. |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                                        |

| Bus Collision       | Any time the SDA line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                                           |

## TABLE 21-1: I<sup>2</sup>C BUS TERMS

#### 21.4.5 START CONDITION

The  $I^2C$  specification defines a Start condition as a transition of SDA from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 21-12 shows wave forms for Start and Stop conditions.

A bus collision can occur on a Start condition if the module samples the SDA line low before asserting it low. This does not conform to the  $I^2C$  Specification that states no bus collision can occur on a Start.

### 21.4.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

| Note: | At least one SCL low time must appear         |

|-------|-----------------------------------------------|

|       | before a Stop is valid, therefore, if the SDA |

|       | line goes low then high again while the SCL   |

|       | line stays high, only the Start condition is  |

|       | detected.                                     |

# 21.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 21-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the  $R/\overline{W}$  bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with  $R/\overline{W}$  clear in 10-bit mode, a prior match flag is set and maintained. Until a Stop condition, a high address with  $R/\overline{W}$  clear, or high address match fails.

#### 21.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

#### 21.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPCON3 register enables additional clock stretching and interrupt generation after the 8th falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSPIF interrupt is set.

Figure 21-19 displays a standard waveform of a 7-bit Address Slave Transmission with AHEN enabled.

- 1. Bus starts Idle.

- Master sends Start condition; the S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the 8th falling edge of the SCL line the CKP bit is cleared and SSPIF interrupt is generated.

- 4. Slave software clears SSPIF.

- 5. Slave software reads ACKTIM bit of SSPCON3 register, and R/W and D/A of the SSPSTAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSPBUF register clearing the BF bit.

- Slave software decides from this information if it wishes to ACK or not ACK and sets the ACKDT bit of the SSPCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCL.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSPIF after the ACK if the R/W bit is set.

- 11. Slave software clears SSPIF.

- 12. Slave loads value to transmit to the master into SSPBUF setting the BF bit.

Note: <u>SSPBUF</u> cannot be loaded until after the <u>ACK</u>.

13. Slave sets the CKP bit, releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the 9th SCL pulse.

- 15. Slave hardware copies the ACK value into the ACKSTAT bit of the SSPCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not ACK the slave releases the bus allowing the master to send a Stop and end the communication.

**Note:** Master must send a not ACK on the last byte to ensure that the slave releases the SCL line to receive a Stop.

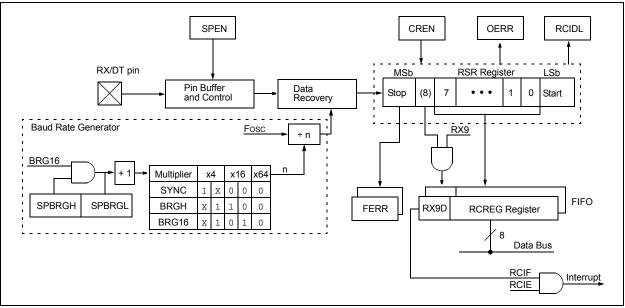

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 22-1, Register 22-2 and Register 22-3, respectively.

When the receiver or transmitter section is not enabled then the corresponding RX or TX pin may be used for general purpose input and output.

## FIGURE 22-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

#### FIGURE 22-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

01 The SUSARY remains in hits white House is and

### 22.5.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 22.5.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 22.5.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 22.5.2.2 Synchronous Slave Transmission Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant 8 bits to the TXREG register.

#### TABLE 22-7: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Name    | Bit 7                         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                        | RCIDL  | —      | SCKP   | BRG16  | —      | WUE    | ABDEN  | 232                 |

| INTCON  | GIE                           | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 74                  |

| PIE1    | TMR1GIE                       | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 75                  |

| PIR1    | TMR1GIF                       | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 77                  |

| RCSTA   | SPEN                          | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 231                 |

| TRISC   | TRISC7                        | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 114                 |

| TXREG   | EUSART Transmit Data Register |        |        |        |        |        |        |        | 222*                |

| TXSTA   | CSRC                          | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 230                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

\* Page provides register information.

### 25.6 DC Characteristics: I/O Ports

| DC CHARACTERISTICS |      |                                      | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature -40°C } \le TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array}$ |      |          |       |                                                                            |  |  |  |

|--------------------|------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|----------------------------------------------------------------------------|--|--|--|

| Param<br>No.       | Sym. | Characteristic                       | Min.                                                                                                                                                                                                                                              | Тур† | Max.     | Units | Conditions                                                                 |  |  |  |

|                    | VIL  | Input Low Voltage                    |                                                                                                                                                                                                                                                   |      |          |       |                                                                            |  |  |  |

|                    |      | I/O PORT:                            |                                                                                                                                                                                                                                                   |      |          |       |                                                                            |  |  |  |

| D030               |      | with TTL buffer                      | —                                                                                                                                                                                                                                                 | _    | 0.8      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                           |  |  |  |

| D030A              |      |                                      | —                                                                                                                                                                                                                                                 | _    | 0.15 VDD | V     | $1.8V \leq V\text{DD} \leq 4.5V$                                           |  |  |  |

| D031               |      | with Schmitt Trigger buffer          | —                                                                                                                                                                                                                                                 | _    | 0.2 VDD  | V     | $2.0V \leq V\text{DD} \leq 5.5V$                                           |  |  |  |

|                    |      | with I <sup>2</sup> C levels         | _                                                                                                                                                                                                                                                 | _    | 0.3 Vdd  | V     |                                                                            |  |  |  |

|                    |      | with SMBus levels                    | _                                                                                                                                                                                                                                                 |      | 0.8      | V     | $2.7V \leq V\text{DD} \leq 5.5V$                                           |  |  |  |

| D032               |      | MCLR, OSC1 (RC mode) <sup>(1)</sup>  | _                                                                                                                                                                                                                                                 | _    | 0.2 VDD  | V     | (Note 1)                                                                   |  |  |  |

| D033               |      | OSC1 (HS mode)                       | _                                                                                                                                                                                                                                                 | _    | 0.3 Vdd  | V     |                                                                            |  |  |  |

|                    | Vih  | Input High Voltage                   |                                                                                                                                                                                                                                                   |      |          |       |                                                                            |  |  |  |

|                    |      | I/O ports:                           |                                                                                                                                                                                                                                                   | _    | —        |       |                                                                            |  |  |  |

| D040               |      | with TTL buffer                      | 2.0                                                                                                                                                                                                                                               | _    | —        | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                           |  |  |  |

| D040A              |      |                                      | 0.25 VDD +<br>0.8                                                                                                                                                                                                                                 | —    | —        | V     | $1.8V \leq V\text{DD} \leq 4.5V$                                           |  |  |  |

| D041               |      | with Schmitt Trigger buffer          | 0.8 VDD                                                                                                                                                                                                                                           | _    | _        | V     | $2.0V \leq V\text{DD} \leq 5.5V$                                           |  |  |  |

|                    |      | with I <sup>2</sup> C levels         | 0.7 Vdd                                                                                                                                                                                                                                           | _    | _        | V     |                                                                            |  |  |  |

|                    |      | with SMBus levels                    | 2.1                                                                                                                                                                                                                                               | _    | _        | V     | $2.7V \le V\text{DD} \le 5.5V$                                             |  |  |  |

| D042               |      | MCLR                                 | 0.8 VDD                                                                                                                                                                                                                                           | _    | _        | V     |                                                                            |  |  |  |

| D043A              |      | OSC1 (HS mode)                       | 0.7 Vdd                                                                                                                                                                                                                                           |      | _        | V     |                                                                            |  |  |  |

| D043B              |      | OSC1 (RC mode)                       | 0.9 VDD                                                                                                                                                                                                                                           | _    | _        | V     | VDD > 2.0V (Note 1)                                                        |  |  |  |

|                    | lı∟  | Input Leakage Current <sup>(2)</sup> |                                                                                                                                                                                                                                                   |      |          |       |                                                                            |  |  |  |

| D060               |      | I/O ports                            | _                                                                                                                                                                                                                                                 | ± 5  | ± 125    | nA    | $Vss \leq VPIN \leq VDD, Pin at high-impedance at 85^{\circ}C$             |  |  |  |

|                    |      |                                      |                                                                                                                                                                                                                                                   | ± 5  | ± 1000   | nA    | 125°C                                                                      |  |  |  |

| D061               |      | MCLR <sup>(3)</sup>                  | —                                                                                                                                                                                                                                                 | ± 50 | ± 200    | nA    | $Vss \leq V \text{PIN} \leq V \text{DD} \text{ at } 85^\circ C$            |  |  |  |

|                    | Ipur | Weak Pull-up Current                 |                                                                                                                                                                                                                                                   |      |          |       |                                                                            |  |  |  |

| D070*              |      |                                      | 25                                                                                                                                                                                                                                                | 100  | 200      | μA    | VDD = 3.3V, $VPIN = VSS$                                                   |  |  |  |

|                    | Vol  | Output Low Voltage <sup>(4)</sup>    | 25                                                                                                                                                                                                                                                | 140  | 300      | μA    | VDD = 5.0V, VPIN = VSS                                                     |  |  |  |

| D080               |      | I/O ports                            | _                                                                                                                                                                                                                                                 | _    | 0.6      | v     | IOL = 8 mA, VDD = 5V<br>IOL = 6 mA, VDD = 3.3V<br>IOL = 1.8 mA, VDD = 1.8V |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: Including OSC2 in CLKOUT mode.

DS40001452F-page 328