#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

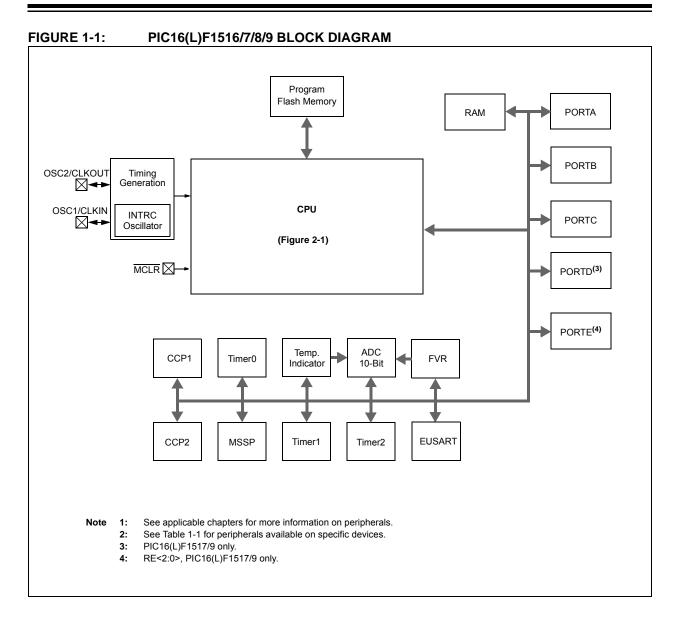

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1516t-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

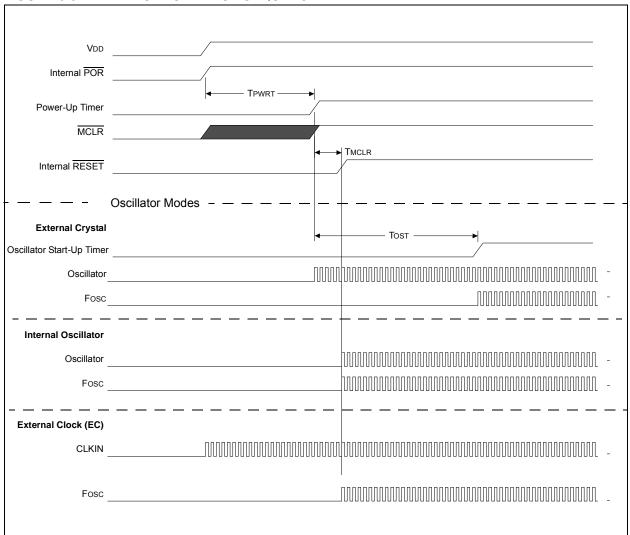

#### FIGURE 6-3: RESET START-UP SEQUENCE

| U-1          | R/W-0/0             | R/W-0/0                                   | R/W/HC-0/0         | R/W/HC-x/q <sup>(2)</sup> | R/W-0/0            | R/S/HC-0/0           | R/S/HC-0/0      |

|--------------|---------------------|-------------------------------------------|--------------------|---------------------------|--------------------|----------------------|-----------------|

| _(1)         | CFGS                | LWLO                                      | FREE               | WRERR                     | WREN               | WR                   | RD              |

| bit 7        |                     |                                           |                    |                           |                    |                      | bit             |

| Legend:      |                     |                                           |                    |                           |                    |                      |                 |

| R = Reada    | able bit            | W = Writable b                            | it                 | U = Unimpleme             | ented bit, read as | s 'O'                |                 |

| S = Bit car  | n only be set       | x = Bit is unkno                          | own                |                           | -                  | √alue at all other I | Resets          |

| '1' = Bit is | 5                   | '0' = Bit is clea                         | red                | HC = Bit is clea          | ared by hardware   | 9                    |                 |

| =            |                     |                                           |                    |                           |                    |                      |                 |

| bit 7        | -                   | ted: Read as '1'                          |                    |                           |                    |                      |                 |

| bit 6        |                     | uration Select bit                        |                    |                           |                    |                      |                 |

|              |                     | Configuration, Use                        |                    | ID Registers              |                    |                      |                 |

| bit 5        |                     | Write Latches On                          |                    |                           |                    |                      |                 |

|              |                     |                                           | ,                  | e latch is loaded         | updated on the i   | next WR comman       | d               |

|              |                     |                                           |                    |                           |                    | all program mem      |                 |

|              | will be in          | itiated on the nex                        | t WR command       |                           |                    |                      |                 |

| bit 4        | •                   | m Flash Erase E                           |                    |                           |                    |                      |                 |

|              |                     | an erase operati<br>an write operatio     |                    |                           | ardware cleared    | upon completion)     |                 |

| bit 3        |                     | gram/Erase Error                          |                    | IX command                |                    |                      |                 |

| DIT D        |                     |                                           | -                  | or erase sequer           | ice attempt or te  | rmination (bit is s  | et automaticall |

|              |                     | et attempt (write '                       |                    |                           |                    |                      | 01 00100000     |

|              | 0 = The prog        | ram or erase ope                          | ration complete    | d normally.               |                    |                      |                 |

| bit 2        | WREN: Progr         | am/Erase Enable                           | bit                |                           |                    |                      |                 |

|              |                     | ogram/erase cyc                           |                    | -1                        |                    |                      |                 |

| L 11 A       |                     | rogramming/eras                           | ing of program F   | lash                      |                    |                      |                 |

| bit 1        | WR: Write Co        | ntroi bit<br>a program Flash p            | rogram/oraso o     | noration                  |                    |                      |                 |

|              |                     | ation is self-timed                       |                    |                           | are once operation | on is complete.      |                 |

|              | •                   | bit can only be se                        |                    | •                         |                    | ·                    |                 |

|              | 0 = Program         | erase operation f                         | to the Flash is co | omplete and inac          | ctive.             |                      |                 |

| bit 0        | RD: Read Co         |                                           |                    |                           |                    |                      |                 |

|              |                     |                                           | ead. Read takes    | s one cycle. RD i         | s cleared in hard  | lware. The RD bit    | can only be se  |

|              | •                   | red) in software.<br>i initiate a prograr | n Flash read       |                           |                    |                      |                 |

| Note 1:      | Unimplemented bit,  |                                           |                    |                           |                    |                      |                 |

| 2:           | The WRERR bit is a  |                                           | y hardware whe     | en a program me           | mory write or era  | se operation is st   | arted (WR = 1)  |

| 3:           | The LWLO bit is ign | ,                                         |                    |                           |                    |                      | 、,              |

### REGISTER 11-6: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

3: The LWLO bit is ignored during a program memory erase operation (FREE = 1).

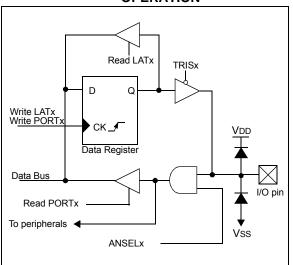

# 12.0 I/O PORTS

Each port has three standard registers for its operation. These registers are:

- TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- ANSELx (analog select)

- WPUx (weak pull-up)

In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

### TABLE 12-1: PORT AVAILABILITY PER DEVICE

| Device          | PORTA | РОКТВ | PORTC | PORTD | PORTE |

|-----------------|-------|-------|-------|-------|-------|

| PIC16(L)F1516/8 | •     | •     | •     |       | ٠     |

| PIC16(L)F1517/9 | •     | •     | •     | •     | •     |

The Data Latch (LATx register) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 12-1.

#### FIGURE 12-1: GENERIC I/O PORT OPERATION

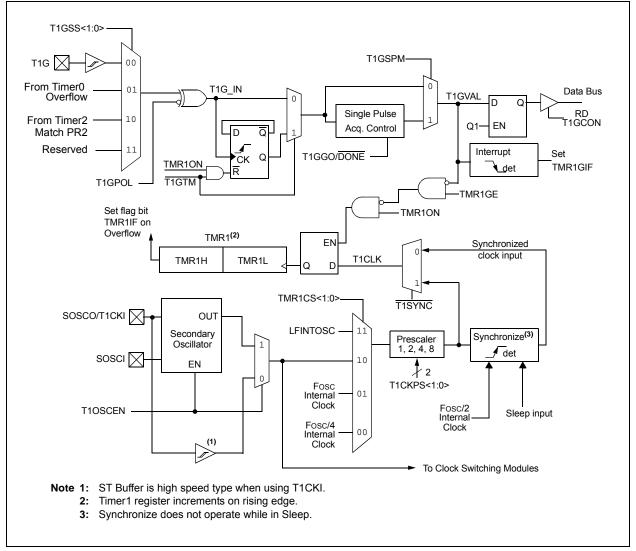

# 18.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- · 2-bit prescaler

- · 32 kHz secondary oscillator circuit

- · Optionally synchronized comparator out

- Multiple Timer1 gate (count enable) sources

- · Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function

- Special Event Trigger (with CCP)

- Selectable Gate Source Polarity

- Gate Toggle mode

- Gate Single-pulse mode

- Gate Value Status

- Gate Event Interrupt

- Figure 18-1 is a block diagram of the Timer1 module.

# FIGURE 18-1: TIMER1 BLOCK DIAGRAM

| Name    | Bit 7      | Bit 6          | Bit 5      | Bit 4         | Bit 3          | Bit 2     | Bit 1  | Bit 0  | Register<br>on Page |

|---------|------------|----------------|------------|---------------|----------------|-----------|--------|--------|---------------------|

| ANSELB  | —          | —              | ANSB5      | ANSB4         | ANSB3          | ANSB2     | ANSB1  | ANSB0  | 112                 |

| CCP1CON | —          | —              | DC1B       | <1:0>         |                | CCP1N     | /<3:0> |        | 168                 |

| CCP2CON | —          | —              | DC2B       | <1:0>         |                | CCP2N     | /<3:0> |        | 168                 |

| INTCON  | GIE        | PEIE           | TMR0IE     | INTE          | IOCIE          | TMR0IF    | INTF   | IOCIF  | 74                  |

| PIE1    | TMR1GIE    | ADIE           | RCIE       | TXIE          | SSPIE          | CCP1IE    | TMR2IE | TMR1IE | 75                  |

| PIR1    | TMR1GIF    | ADIF           | RCIF       | TXIF          | SSPIF          | CCP1IF    | TMR2IF | TMR1IF | 77                  |

| TMR1H   | Holding Re | gister for the | Most Signi | ficant Byte o | of the 16-bit  | TMR1 Cour | nt     |        | 151*                |

| TMR1L   | Holding Re | gister for the | Least Sign | ificant Byte  | of the 16-bit  | TMR1 Cou  | nt     |        | 151*                |

| TRISB   | TRISB7     | TRISB6         | TRISB5     | TRISB4        | TRISB3         | TRISB2    | TRISB1 | TRISB0 | 112                 |

| TRISC   | TRISC7     | TRISC6         | TRISC5     | TRISC4        | TRISC3         | TRISC2    | TRISC1 | TRISC0 | 115                 |

| T1CON   | TMR1C      | S<1:0>         | T1CKP      | S<1:0>        | T1OSCEN        | T1SYNC    | —      | TMR10N | 155                 |

| T1GCON  | TMR1GE     | T1GPOL         | T1GTM      | T1GSPM        | T1GGO/<br>DONE | T1GVAL    | T1GS   | S<1:0> | 156                 |

### TABLE 18-5: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

\* Page provides register information.

### 20.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 20-1 demonstrates the code to perform this function.

#### EXAMPLE 20-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCPxCON     | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCPxCON             |

| CLRF    | CCPxCON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ;the new prescaler      |

|         |             | ;move value and CCP ON  |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this |

|         |             | ;value                  |

|         |             |                         |

# 20.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (Fosc/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

### 20.1.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function**" for more information.

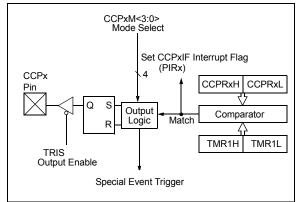

# 20.2 Compare Mode

The Compare mode function described in this section is available and identical for CCP modules CCP1 and CCP2.

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMR1H:TMR1L register pair. When a match occurs, one of the following events can occur:

- · Toggle the CCPx output

- Set the CCPx output

- Clear the CCPx output

- Generate a Special Event Trigger

- Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set.

All Compare modes can generate an interrupt.

Figure 20-2 shows a simplified diagram of the Compare operation.

#### FIGURE 20-2: COMPARE MODE OPERATION BLOCK DIAGRAM

# 20.2.1 CCPX PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

The CCP2 pin function can be moved to alternate pins using the APFCON register (Register 12-1). Refer to **Section 12.1 "Alternate Pin Function"** for more details.

### 20.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section 18.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TImer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

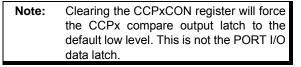

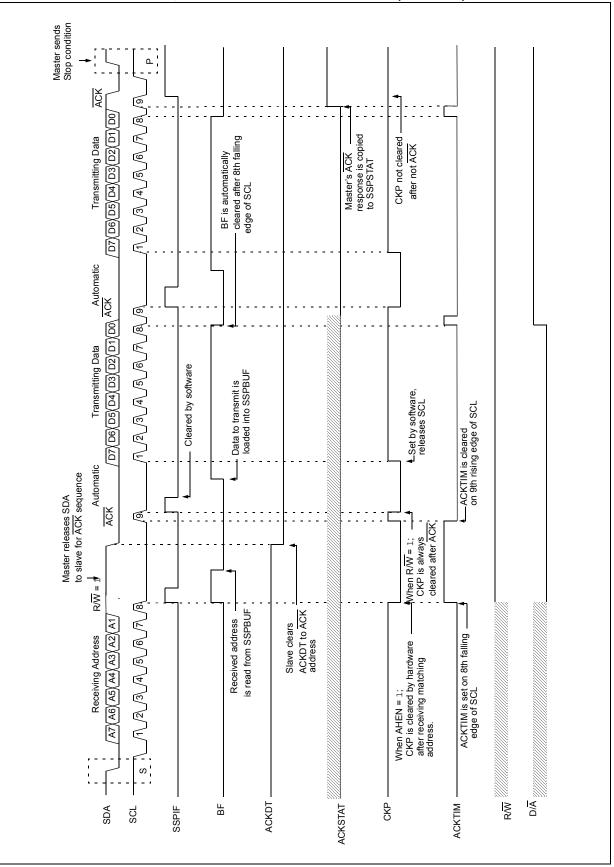

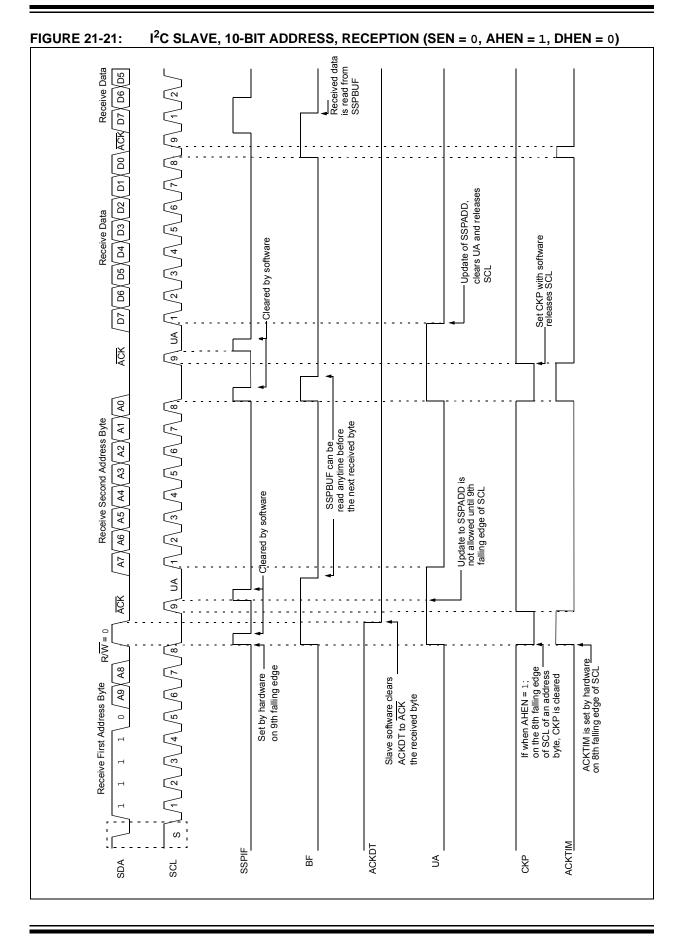

The I<sup>2</sup>C interface supports the following modes and features:

- · Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited Multi-master support

- 7-bit and 10-bit addressing

- · Start and Stop interrupts

- Interrupt masking

- Clock stretching

- · Bus collision detection

- · General call address matching

- Address masking

- · Address Hold and Data Hold modes

- Selectable SDA hold times

Figure 21-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 21-3 is a diagram of the  $I^2C$  interface module in Slave mode.

# FIGURE 21-2: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

# 21.3 I<sup>2</sup>C MODE OVERVIEW

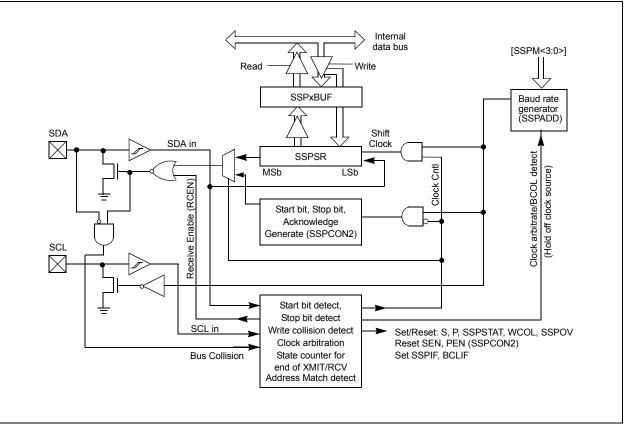

The Inter-Integrated Circuit Bus (I<sup>2</sup>C) is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A Slave device is controlled through addressing.

The I<sup>2</sup>C bus specifies two signal connections:

- Serial Clock (SCL)

- Serial Data (SDA)

Figure 21-1 shows the block diagram of the MSSP module when operating in I<sup>2</sup>C mode.

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 21-11 shows a typical connection between two processors configured as master and slave devices.

The I<sup>2</sup>C bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode (master is transmitting data to a slave)

- Master Receive mode

(master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDA line while the SCL line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

# FIGURE 21-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDA line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of a data bit is always performed while the SCL line is held low. Transitions that occur while the SCL line is held high are used to indicate Start and Stop bits.

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an  $\overrightarrow{ACK}$  bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an ACK bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDA line while the SCL line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last ACK bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

### 22.4.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCON register starts the auto-baud calibration sequence (Figure 22-6). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Table . The fifth rising edge will occur on the RX pin at the end of the 8th bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRGL register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRGL register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table . During ABD, both the SPBRGH and SPBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH and SPBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 22.4.3 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRGL register pair.

| <b>TABLE 22-5:</b> | <b>BRG COUNTER CLOCK RATES</b> |

|--------------------|--------------------------------|

|                    |                                |

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

**Note:** During the ABD sequence, SPBRGL and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

#### XXXXh 0000h 001Ch **BRG** Value Edge #1 Edge #2 Edge #3 Edge #4 Edge #5 RX pin Start bit 0 bit 1 bit 2 bit 3 bit 4 bit 5 bit 6 bit 7 Stop bit Auto-Cleared Set by User ABDEN bit RCIDL RCIF bit (Interrupt) Read RCREG SPBRGL XXh 1Ch SPBRGH 00h XXh Note 1: The ABD sequence requires the EUSART module to be configured in Asynchronous mode.

#### FIGURE 22-6: AUTOMATIC BAUD RATE CALIBRATION

# 22.4.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDxCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPxBRGH:SPxBRGL register pair. The overflow condition will set the RCIF flag. The counter continues to count until the fifth rising edge is detected on the RX pin. The RCIDL bit will remain false ('0') until the fifth rising edge at which time the RCIDL bit will be set. If the RCREG is read after the overflow occurs but before the fifth rising edge then the fifth rising edge will set the RCIF again.

Terminating the auto-baud process early to clear an overflow condition will prevent proper detection of the sync character fifth rising edge. If any falling edges of the sync character have not yet occurred when the ABDEN bit is cleared then those will be falsely detected as Start bits. The following steps are recommended to clear the overflow condition:

- 1. Read RCREG to clear RCIF

- 2. If RCIDL is zero then wait for RCIF and repeat step 1.

- 3. Clear the ABDOVF bit.

### 22.4.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the baud rate generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 22-7), and asynchronously if the device is in Sleep mode (Figure 22-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 22.4.3.1 Special Considerations

Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

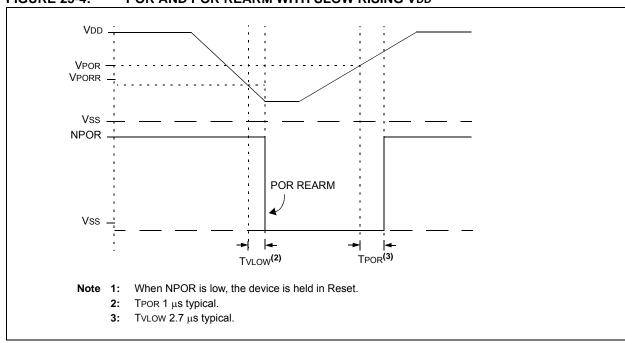

#### FIGURE 25-4: POR AND POR REARM WITH SLOW RISING VDD

### TABLE 25-9: LOW DROPOUT (LDO) REGULATOR CHARACTERISTICS

|              | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                        |     |     |   |    |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|------------------------|-----|-----|---|----|--|--|

| Param<br>No. | Sym Characteristic Min Typt Max Units Conditions                                                                     |                        |     |     |   |    |  |  |

| LDO01        |                                                                                                                      | LDO Regulation Voltage |     | 3.0 |   | V  |  |  |

| LDO02        |                                                                                                                      | LDO External Capacitor | 0.1 | _   | 1 | μF |  |  |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

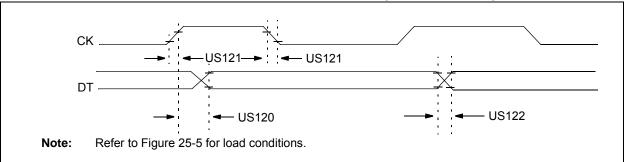

### FIGURE 25-14: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

### TABLE 25-10: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                   |          |   |     |    |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------|----------|---|-----|----|--|--|--|

| Param.<br>No. Symbol Characteristic Min. Max. Units Condition                                                        |          |                                   |          |   |     |    |  |  |  |

| US120                                                                                                                | TCKH2DTV | SYNC XMIT (Master and Slave)      | 3.0-5.5V | _ | 80  | ns |  |  |  |

|                                                                                                                      |          | Clock high to data-out valid      | 1.8-5.5V |   | 100 | ns |  |  |  |

| US121                                                                                                                | TCKRF    | Clock out rise time and fall time | 3.0-5.5V |   | 45  | ns |  |  |  |

|                                                                                                                      |          | (Master mode)                     | 1.8-5.5V | — | 50  | ns |  |  |  |

| US122                                                                                                                | TDTRF    | Data-out rise time and fall time  | 3.0-5.5V | — | 45  | ns |  |  |  |

|                                                                                                                      |          |                                   | 1.8-5.5V | _ | 50  | ns |  |  |  |

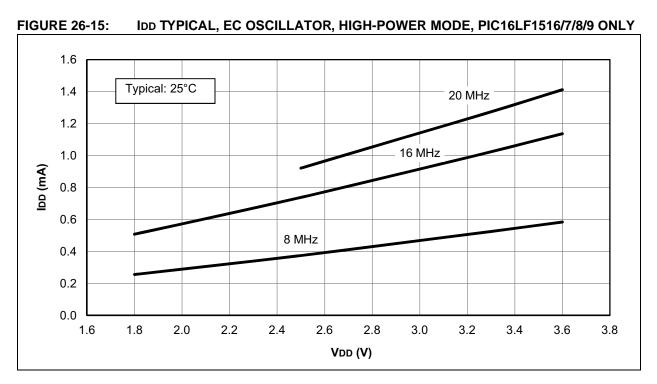

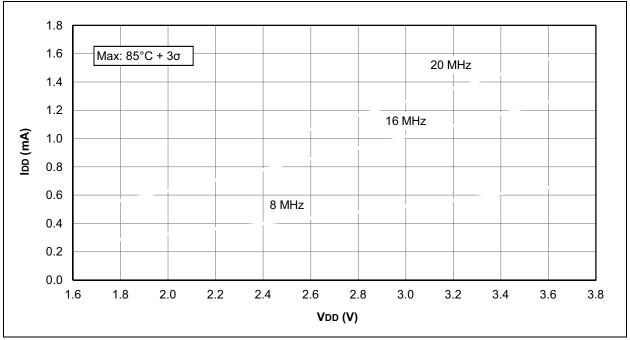

FIGURE 26-16: IDD MAXIMUM, EC OSCILLATOR, HIGH-POWER MODE, PIC16LF1516/7/8/9 ONLY

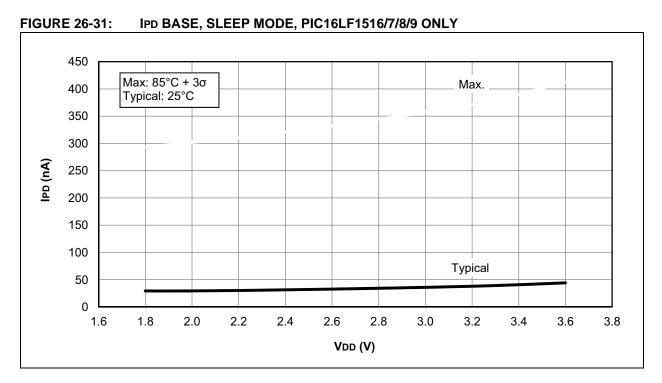

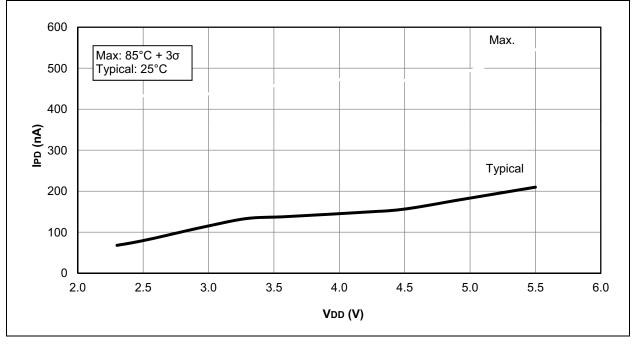

FIGURE 26-32: IPD BASE, LOW-POWER SLEEP MODE (VREGPM = 1), PIC16F1516/7/8/9 ONLY

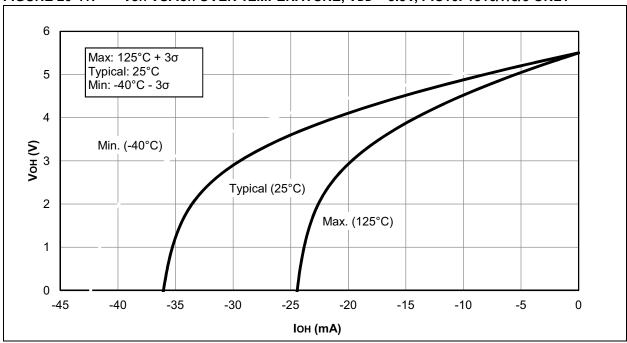

#### FIGURE 26-41: VOH VS. IOH OVER TEMPERATURE, VDD = 5.5V, PIC16F1516/7/8/9 ONLY

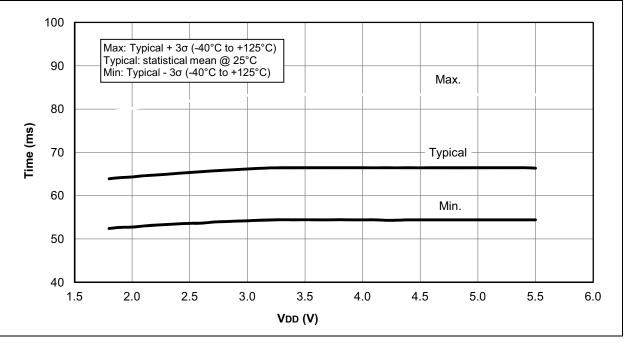

# 40-Lead Plastic Dual In-Line (P) – 600 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |       | INCHES   |       |

|----------------------------|------------------|-------|----------|-------|

|                            | Dimension Limits | MIN   | NOM      | MAX   |

| Number of Pins             | N                |       | 40       |       |

| Pitch                      | е                |       | .100 BSC |       |

| Top to Seating Plane       | A                | -     | -        | .250  |

| Molded Package Thickness   | A2               | .125  | -        | .195  |

| Base to Seating Plane      | A1               | .015  | -        | _     |

| Shoulder to Shoulder Width | E                | .590  | -        | .625  |

| Molded Package Width       | E1               | .485  | -        | .580  |

| Overall Length             | D                | 1.980 | -        | 2.095 |

| Tip to Seating Plane       | L                | .115  | -        | .200  |

| Lead Thickness             | С                | .008  | -        | .015  |

| Upper Lead Width           | b1               | .030  | -        | .070  |

| Lower Lead Width           | b                | .014  | -        | .023  |

| Overall Row Spacing §      | eB               | _     | -        | .700  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-016B