Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1516t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 3-3:** PIC16(L)F1516/7 MEMORY MAP

|      | BANK 0                        |      | BANK 1                        |      | BANK 2                        |      | BANK 3                        |      | BANK 4                        |      | BANK 5                        |      | BANK 6                        |      | BANK 7                        |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| 000h |                               | 080h |                               | 100h |                               | 180h |                               | 200h |                               | 280h |                               | 300h |                               | 380h |                               |

|      | Core Registers<br>(Table 3-2) |

| 00Bh |                               | 08Bh |                               | 10Bh |                               | 18Bh |                               | 20Bh |                               | 28Bh |                               | 30Bh |                               | 38Bh |                               |

| 00Ch | PORTA                         | 08Ch | TRISA                         | 10Ch | LATA                          | 18Ch | ANSELA                        | 20Ch | _                             | 28Ch | _                             | 30Ch | _                             | 38Ch | _                             |

| 00Dh | PORTB                         | 08Dh | TRISB                         | 10Dh | LATB                          | 18Dh | ANSELB                        | 20Dh | WPUB                          | 28Dh | —                             | 30Dh | —                             | 38Dh | —                             |

| 00Eh | PORTC                         | 08Eh | TRISC                         | 10Eh | LATC                          | 18Eh | ANSELC                        | 20Eh | —                             | 28Eh | —                             | 30Eh | —                             | 38Eh | —                             |

| 00Fh | PORTD <sup>(1)</sup>          | 08Fh | TRISD <sup>(1)</sup>          | 10Fh | LATD <sup>(1)</sup>           | 18Fh | ANSELD <sup>(1)</sup>         | 20Fh | _                             | 28Fh | _                             | 30Fh | _                             | 38Fh | _                             |

| 010h | PORTE                         | 090h | TRISE                         | 110h | LATE <sup>(1)</sup>           | 190h | ANSELE <sup>(1)</sup>         | 210h | WPUE                          | 290h | _                             | 310h | _                             | 390h | _                             |

| 011h | PIR1                          | 091h | PIE1                          | 111h | _                             | 191h | PMADRL                        | 211h | SSPBUF                        | 291h | CCPR1L                        | 311h |                               | 391h | _                             |

| 012h | PIR2                          | 092h | PIE2                          | 112h | —                             | 192h | PMADRH                        | 212h | SSPADD                        | 292h | CCPR1H                        | 312h | —                             | 392h | —                             |

| 013h | —                             | 093h | —                             | 113h | _                             | 193h | PMDATL                        | 213h | SSPMSK                        | 293h | CCP1CON                       | 313h | —                             | 393h | —                             |

| 014h | —                             | 094h | _                             | 114h | _                             | 194h | PMDATH                        | 214h | SSPSTAT                       | 294h | —                             | 314h | —                             | 394h | IOCBP                         |

| 015h | TMR0                          | 095h | OPTION_REG                    | 115h | —                             | 195h | PMCON1                        | 215h | SSPCON1                       | 295h | —                             | 315h | —                             | 395h | IOCBN                         |

| 016h | TMR1L                         | 096h | PCON                          | 116h | BORCON                        | 196h | PMCON2                        | 216h | SSPCON2                       | 296h | —                             | 316h | _                             | 396h | IOCBF                         |

| 017h | TMR1H                         | 097h | WDTCON                        | 117h | FVRCON                        | 197h | VREGCON <sup>(2)</sup>        | 217h | SSPCON3                       | 297h | —                             | 317h | _                             | 397h | _                             |

| 018h | T1CON                         | 098h | _                             | 118h | —                             | 198h | _                             | 218h | _                             | 298h | CCPR2L                        | 318h | _                             | 398h | _                             |

| 019h | T1GCON                        | 099h | OSCCON                        | 119h |                               | 199h | RCREG                         | 219h | _                             | 299h | CCPR2H                        | 319h |                               | 399h | _                             |

| 01Ah | TMR2                          | 09Ah | OSCSTAT                       | 11Ah | —                             | 19Ah | TXREG                         | 21Ah | —                             | 29Ah | CCP2CON                       | 31Ah | —                             | 39Ah | —                             |

| 01Bh | PR2                           | 09Bh | ADRESL                        | 11Bh | —                             | 19Bh | SPBRG                         | 21Bh | —                             | 29Bh | —                             | 31Bh | —                             | 39Bh | _                             |

| 01Ch | T2CON                         | 09Ch | ADRESH                        | 11Ch | —                             | 19Ch | SPBRGH                        | 21Ch | _                             | 29Ch | —                             | 31Ch | _                             | 39Ch | _                             |

| 01Dh | _                             | 09Dh | ADCON0                        | 11Dh | APFCON                        | 19Dh | RCSTA                         | 21Dh | _                             | 29Dh | _                             | 31Dh | _                             | 39Dh | _                             |

| 01Eh |                               | 09Eh | ADCON1                        | 11Eh | _                             | 19Eh | TXSTA                         | 21Eh |                               | 29Eh | _                             | 31Eh |                               | 39Eh | _                             |

| 01Fh | —                             | 09Fh | —                             | 11Fh | —                             | 19Fh | BAUDCON                       | 21Fh |                               | 29Fh | —                             | 31Fh | —                             | 39Fh | _                             |

| 020h |                               | 0A0h |                               | 120h |                               | 1A0h |                               | 220h |                               | 2A0h |                               | 320h | General Purpose               | 3A0h |                               |

|      | General                       |      | Register                      |      |                               |

|      | Purpose                       | 32Fh | 16 Bytes                      |      | Unimplemented                 |

|      | Register<br>80 Bytes          | 330h | Unimplemented                 |      | Read as '0'                   |

|      | 00 Dytes                      |      | 00 Dytes                      |      | 00 Dytes                      |      | oo bytes                      |      | 00 Dyies                      |      | oo bytes                      |      | Read as '0'                   |      |                               |

| 06Fh |                               | 0EFh |                               | 16Fh |                               | 1EFh |                               | 26Fh |                               | 2EFh |                               | 36Fh |                               | 3EFh |                               |

| 070h |                               | 0F0h | Common RAM                    | 170h | Common RAM                    | 1F0h | Common RAM                    | 270h | Common RAM                    | 2F0h | Common RAM                    | 370h | Common RAM                    | 3F0h | Common RAM                    |

|      | Common RAM                    |      | (Accesses                     |

| 07Fh |                               | 0FFh | 70h – 7Fh)                    | 17Fh | 70h – 7Fh)                    | 1FFh | 70h – 7Fh)                    | 27Fh | 70h – 7Fh)                    | 2FFh | 70h – 7Fh)                    | 37Fh | 70h – 7Fh)                    | 3FFh | 70h – 7Fh)                    |

| U/Fn |                               | UFFN |                               | 17FN |                               | IFFN |                               | 27FN |                               | ZEEN |                               | SIFN |                               | SEEU |                               |

d: = Unimplemented data memory locations, read as '0'.

1: PIC16F/LF1516/7/8/9 only.

2: PIC16F1516/7 only. Legend: Note 1:

#### 3.5 PCL and PCLATH

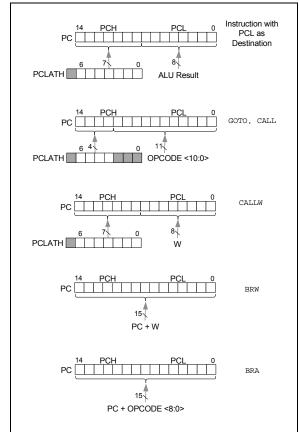

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 3-4 shows the five situations for the loading of the PC.

FIGURE 3-4: LOADING OF PC IN DIFFERENT SITUATIONS

#### 3.5.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register.

#### 3.5.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the Application Note *AN556*, *Implementing a Table Read* (DS00556).

#### 3.5.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

#### 3.5.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 +, the signed value of the operand of the BRA instruction.

### 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

#### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

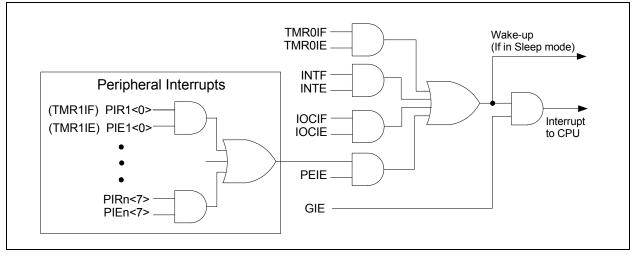

### 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 7-1.

#### FIGURE 7-1: INTERRUPT LOGIC

#### 8.2 Low-Power Sleep Mode

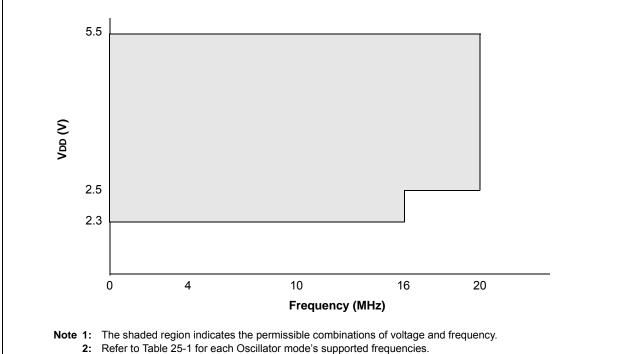

The PIC16F1516/7/8/9 device contains an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode. The PIC16F1516/7/8/9 allows the user to optimize the operating current in Sleep, depending on the application requirements.

A Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register. With this bit set, the LDO and reference circuitry are placed in a low-power state when the device is in Sleep.

## 8.2.1 SLEEP CURRENT VS. WAKE-UP TIME

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

#### 8.2.2 PERIPHERAL USAGE IN SLEEP

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The LDO will remain in the normal power mode when those peripherals are enabled. The Low-Power Sleep mode is intended for use with these peripherals:

- Brown-Out Reset (BOR)

- Watchdog Timer (WDT)

- · External interrupt pin/Interrupt-on-change pins

- Timer1 (with external clock source)

- CCP (Capture mode)

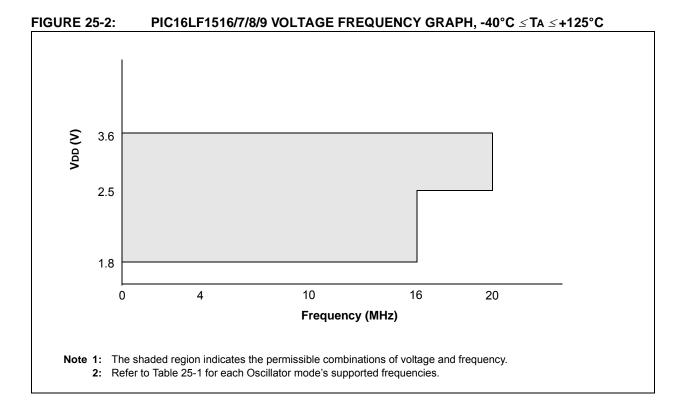

- Note: The PIC16LF1516/7/8/9 does not have a configurable Low-Power Sleep mode. PIC16LF1516/7/8/9 is an unregulated device and is always in the lowest power state when in Sleep, with no wake-up time penalty. This device has a lower maximum VDD and I/O voltage than the PIC16F1516/7/8/9. See Section 25.0 "Electrical Specifications" for more information.

## TABLE 11-1:FLASH MEMORY<br/>ORGANIZATION BY DEVICE

| Device        | Row Erase<br>(words) | Write<br>Latches<br>(words) |

|---------------|----------------------|-----------------------------|

| PIC16(L)F1516 |                      |                             |

| PIC16(L)F1517 | 32                   | 32                          |

| PIC16(L)F1518 | 52                   | 52                          |

| PIC16(L)F1519 |                      |                             |

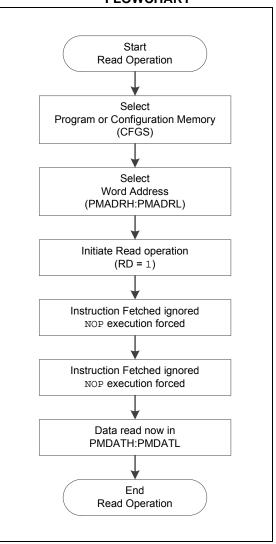

## 11.2.1 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must:

- 1. Write the desired address to the PMADRH:PMADRL register pair.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Then, set control bit RD of the PMCON1 register.

Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF PMCON1, RD" instruction to be ignored. The data is available in the very next cycle, in the PMDATH:PMDATL register pair; therefore, it can be read as two bytes in the following instructions.

PMDATH:PMDATL register pair will hold this value until another read or until it is written to by the user.

| Note: | The two instructions following a program    |

|-------|---------------------------------------------|

|       | memory read are required to be NOPS.        |

|       | This prevents the user from executing a     |

|       | 2-cycle instruction on the next instruction |

|       | after the RD bit is set.                    |

#### FIGURE 11-1:

#### FLASH PROGRAM MEMORY READ FLOWCHART

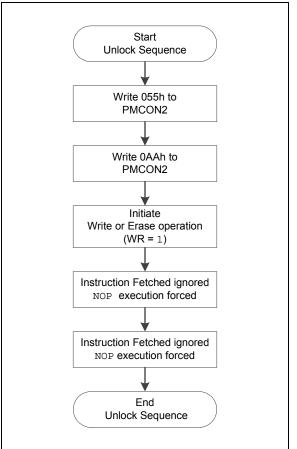

#### 11.2.2 FLASH MEMORY UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the Flash program memory from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- Row Erase

- Load program memory write latches

- Write of program memory write latches to program memory

- Write of program memory write latches to User IDs

The unlock sequence consists of the following steps:

- 1. Write 55h to PMCON2

- 2. Write AAh to PMCON2

- 3. Set the WR bit in PMCON1

- 4. NOP instruction

- 5. NOP instruction

Once the WR bit is set, the processor will always force two NOP instructions. When an Erase Row or Program Row operation is being performed, the processor will stall internal operations (typical 2 ms), until the operation is complete and then resume with the next instruction. When the operation is loading the program memory write latches, the processor will always force the two NOP instructions and continue uninterrupted with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

#### FIGURE 11-3:

#### FLASH PROGRAM MEMORY UNLOCK SEQUENCE FLOWCHART

# PIC16(L)F1516/7/8/9

#### EXAMPLE 11-2: ERASING ONE ROW OF PROGRAM MEMORY

- ; This row erase routine assumes the following:

- ; 1. A valid address within the erase row is loaded in ADDRH:ADDRL

; 2. ADDRH and ADDRL are located in shared data memory  $0\,\mathrm{x}70$  -  $0\,\mathrm{x}7F$  (common RAM)

| BCF<br>BANKSEL<br>MOVF<br>MOVWF<br>MOVF<br>BCF<br>BSF<br>BSF      | INTCON,GIE<br>PMADRL<br>ADDRL,W<br>PMADRL<br>ADDRH,W<br>PMADRH<br>PMCON1,CFGS<br>PMCON1,FREE<br>PMCON1,WREN | <pre>; Disable ints so required sequences will execute properly ; Load lower 8 bits of erase address boundary ; Load upper 6 bits of erase address boundary ; Not configuration space ; Specify an erase operation ; Enable writes</pre>                                                                                                                                    |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BSF<br>MOVLW<br>MOVWF<br>MOVWF<br>BSF<br>NOP<br>NOP<br>BCF<br>BSF | PMCON1, WREN<br>55h<br>PMCON2<br>0AAh<br>PMCON2<br>PMCON1, WR<br>PMCON1, WREN<br>INTCON, GIE                | <pre>; Enable writes ; Start of required sequence to initiate erase ; Write 55h ; ; Write AAh ; Set WR bit to begin erase ; NOP instructions are forced as processor starts ; row erase of program memory. ; ; ; The processor stalls until the erase process is complete ; after erase processor continues with 3rd instruction ; Disable writes ; Enable interrupts</pre> |

| U-0                               | U-0                                             | U-0               | U-0      | R/W-1/1                                               | U-0 | U-0 | U-0   |  |  |  |

|-----------------------------------|-------------------------------------------------|-------------------|----------|-------------------------------------------------------|-----|-----|-------|--|--|--|

| —                                 | _                                               | —                 | _        | WPUE3                                                 | _   | —   | —     |  |  |  |

| bit 7                             |                                                 |                   |          |                                                       |     |     | bit 0 |  |  |  |

|                                   |                                                 |                   |          |                                                       |     |     |       |  |  |  |

| Legend:                           |                                                 |                   |          |                                                       |     |     |       |  |  |  |

| R = Readable bit W = Writable bit |                                                 |                   |          | U = Unimplemented bit, read as '0'                    |     |     |       |  |  |  |

| u = Bit is un                     | u = Bit is unchanged x = Bit is unknown         |                   |          | -n/n = Value at POR and BOR/Value at all other Resets |     |     |       |  |  |  |

| '1' = Bit is se                   | et                                              | '0' = Bit is clea | ared     |                                                       |     |     |       |  |  |  |

| bit 7-4                           | Unimplomon                                      | ted: Dood op '    | <u>,</u> |                                                       |     |     |       |  |  |  |

|                                   | -                                               | ted: Read as '    |          |                                                       |     |     |       |  |  |  |

| bit 3                             | WPUE: Weak<br>1 = Pull-up er<br>0 = Pull-up dis |                   | er bit   |                                                       |     |     |       |  |  |  |

#### REGISTER 12-23: WPUE: WEAK PULL-UP PORTE REGISTER<sup>(1,2)</sup>

bit 2-0 Unimplemented: Read as '0'

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

| Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4    | Bit 3      | Bit 2                | Bit 1                 | Bit 0                | Register<br>on Page |

|-----------------------|-------|-------|-------|----------|------------|----------------------|-----------------------|----------------------|---------------------|

| ADCON0                |       |       |       | CHS<4:0> |            |                      | GO/DONE               | ADON                 | 137                 |

| ANSELE <sup>(1)</sup> | _     | —     | _     | _        | _          | ANSE2                | ANSE1                 | ANSE0                | 121                 |

| CCPxCON               | —     | —     | DCxB  | <1:0>    | CCPxM<3:0> |                      |                       |                      | 168                 |

| LATE                  | —     | —     | _     | _        | —          | LATE2 <sup>(1)</sup> | LATE1 <sup>(1)</sup>  | LATE0 <sup>(1)</sup> | 121                 |

| PORTE                 | _     | _     | _     | _        | RE3        | RE2 <sup>(1)</sup>   | RE1 <sup>(1)</sup>    | RE0 <sup>(1)</sup>   | 120                 |

| TRISE                 | —     | —     | —     | _        | (2)        | TRISE2(1)            | TRISE1 <sup>(1)</sup> | TRISE0(1)            | 120                 |

| WPUE                  | _     | _     | _     | —        | WPUE3      | _                    |                       | _                    | 122                 |

#### TABLE 12-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTE.

Note 1: These bits are not implemented on the PIC16(L)F1516/8 devices, read as '0'.

2: Unimplemented, read as '1'.

#### TABLE 12-11: SUMMARY OF CONFIGURATION WORD WITH PORTE

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2  | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|-----------|---------|---------|---------------------|

|         | 13:8 |         |         | FCMEN    | IESO     | CLKOUTEN | BOREI     | N<1:0>  | —       | 40                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | =<1:0>   | FOSC<2:0> |         |         | 42                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTE.

#### 13.6 Register Definitions: Interrupt-on-change Control

| R/W-0/0         R/W-0/0 <t< th=""><th colspan="6">-n/n = Value at POR and BOR/Value at all other Resets</th></t<> | -n/n = Value at POR and BOR/Value at all other Resets |         |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------|--|--|--|--|

| IOCBP7 IOCBP6 IOCBP5 IOCBP4 IOCBP3 IOCBP2<br>bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U = Unimplemented bit, read as '0'                    |         |  |  |  |  |

| IOCBP7 IOCBP6 IOCBP5 IOCBP4 IOCBP3 IOCBP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                       |         |  |  |  |  |

| IOCBP7 IOCBP6 IOCBP5 IOCBP4 IOCBP3 IOCBP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                       | bit 0   |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       | bit 0   |  |  |  |  |

| R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IOCBP1                                                | IOCBP0  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0/0                                               | R/W-0/0 |  |  |  |  |

#### REGISTER 13-1: IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER

bit 7-0

1' = Bit is set

IOCBP<7:0>: Interrupt-on-Change PORTB Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

'0' = Bit is cleared

#### REGISTER 13-2: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | IOCBN3  | IOCBN2  | IOCBN1  | IOCBN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

**IOCBN<7:0>:** Interrupt-on-Change PORTB Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-3: IOCBF: INTERRUPT-ON-CHANGE PORTB FLAG REGISTER

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | IOCBF3     | IOCBF2     | IOCBF1     | IOCBF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

IOCBF7:0>: Interrupt-on-Change PORTB Flag bits

1 = An enabled change was detected on the associated pin.

- Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was detected on RBx.

- 0 = No change was detected, or the user cleared the detected change.

#### 16.2 ADC Operation

#### 16.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 16.2.6 "ADC Conver-     |

|       | sion Procedure".                         |

#### 16.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 16.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

#### 16.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC oscillator source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 16.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCPx module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

#### TABLE 16-2: SPECIAL EVENT TRIGGER

| Device        | ССР  |

|---------------|------|

| PIC16(L)F1516 |      |

| PIC16(L)F1517 | CCP2 |

| PIC16(L)F1518 | 0072 |

| PIC16(L)F1519 |      |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to **Section 20.0** "Capture/Compare/PWM **Modules**" for more information.

#### 20.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPx module does not assert control of the CCPx pin (see the CCPxCON register).

#### 20.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is chosen (CCPxM<3:0> = 1011), the CCPx module does the following:

- Resets Timer1

- Starts an ADC conversion if ADC is enabled

The CCPx module does not assert control of the CCPx pin in this mode.

The Special Event Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPRxH, CCPRxL register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. The Special Event Trigger output starts an ADC conversion (if the ADC module is enabled). This allows the CCPRxH, CCPRxL register pair to effectively provide a 16-bit programmable period register for Timer1.

#### TABLE 20-2: SPECIAL EVENT TRIGGER

| Device              | CCPx |

|---------------------|------|

| PIC16(L)F1516/7/8/9 | CCP2 |

Refer to **Section 16.2.5 "Special Event Trigger"** for more information.

- Note 1: The Special Event Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

- 2: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Special Event Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

#### 20.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

#### 20.2.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function**" for more information.

#### 20.3 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 20-3 shows a typical waveform of the PWM signal.

#### 20.3.1 STANDARD PWM OPERATION

The standard PWM function described in this section is available and identical for all CCP modules.

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to 10 bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PR2 registers

- T2CON registers

- CCPRxL registers

- CCPxCON registers

Figure 20-4 shows a simplified block diagram of PWM operation.

Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

2: Clearing the CCPxCON register will relinquish control of the CCPx pin.

#### 21.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high. When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the 8th bit is shifted out (the falling edge of the 8th clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an  $\overline{ACK}$  bit during the 9th bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKSTAT bit on the rising edge of the 9th clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the 9th clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 21-28).

After the write to the SSPBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the 8th clock, the master will release the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the 9th clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPCON2 register. Following the falling edge of the 9th clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 21.6.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPSTAT register is set when the CPU writes to SSPBUF and is cleared when all eight bits are shifted out.

#### 21.6.6.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

WCOL must be cleared by software before the next transmission.

#### 21.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPCON2 register is cleared when the slave has sent an Acknowledge (ACK = 0) and is set when the slave does not Acknowledge (ACK = 1). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

21.6.6.4 Typical transmit sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPCON2 register.

- 2. SSPIF is set by hardware on completion of the Start.

- 3. SSPIF is cleared by software.

- 4. The MSSP module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPBUF with the slave address to transmit.

- 6. Address is shifted out the SDA pin until all 8 bits are transmitted. Transmission begins as soon as SSPBUF is written to.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPCON2 register.

- 8. The MSSP module generates an interrupt at the end of the 9th clock cycle by setting the SSPIF bit.

- 9. The user loads the SSPBUF with eight bits of data.

- 10. Data is shifted out the SDA pin until all eight bits are transmitted.

- 11. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- 13. The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPCON2 register. Interrupt is generated once the Stop/Restart condition is complete.

| R/W-0/0          | R/W-0/0                     | R/W-0/0                             | R/W-0/0        | R/W-0/0         | R-0/0            | R-0/0            | R-0/0       |

|------------------|-----------------------------|-------------------------------------|----------------|-----------------|------------------|------------------|-------------|

| SPEN             | RX9                         | SREN                                | CREN           | ADDEN           | FERR             | OERR             | RX9D        |

| bit 7            | •                           |                                     |                |                 |                  |                  | bit (       |

| <u> </u>         |                             |                                     |                |                 |                  |                  |             |

| Legend:          |                             |                                     |                |                 |                  |                  |             |

| R = Readable     |                             | W = Writable                        |                | •               | nented bit, reac |                  |             |

| u = Bit is uncl  | •                           | x = Bit is unk                      |                | -n/n = Value a  | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |                             | '0' = Bit is cle                    | ared           |                 |                  |                  |             |

| bit 7            | SPEN: Seria                 | I Port Enable b                     | it             |                 |                  |                  |             |

|                  | 1 = Serial po               | ort enabled (cor                    | nfigures RX/D  | T and TX/CK pi  | ins as serial po | rt pins)         |             |

|                  |                             | ort disabled (he                    |                | ·               | ·                | . ,              |             |

| bit 6            | <b>RX9:</b> 9-bit Re        | eceive Enable b                     | pit            |                 |                  |                  |             |

|                  |                             | 9-bit reception<br>8-bit reception  |                |                 |                  |                  |             |

| bit 5            | SREN: Singl                 | e Receive Enal                      | ole bit        |                 |                  |                  |             |

|                  | Asynchronou                 | <u>is mode</u> :                    |                |                 |                  |                  |             |

|                  | Don't care                  |                                     |                |                 |                  |                  |             |

|                  | •                           | <u>s mode – Maste</u>               | <u>:r</u> :    |                 |                  |                  |             |

|                  |                             | single receive                      |                |                 |                  |                  |             |

|                  |                             | s single receive<br>ared after rece | ntion is compl | oto             |                  |                  |             |

|                  |                             | <u>s mode – Slave</u>               |                | cic.            |                  |                  |             |

|                  | Don't care                  |                                     |                |                 |                  |                  |             |

| bit 4            | CREN: Conti                 | inuous Receive                      | Enable bit     |                 |                  |                  |             |

|                  | Asynchronou                 | <u>is mode</u> :                    |                |                 |                  |                  |             |

|                  | 1 = Enables                 | receiver                            |                |                 |                  |                  |             |

|                  | 0 = Disables                |                                     |                |                 |                  |                  |             |

|                  | Synchronous                 |                                     |                |                 |                  |                  |             |

|                  |                             | continuous rec<br>continuous rec    |                | ole bit CREN is | cleared (CREN    | I overrides SRI  | EN)         |

| bit 3            | ADDEN: Add                  | dress Detect Er                     | able bit       |                 |                  |                  |             |

|                  | Asynchronou                 | is mode 9-bit (F                    | RX9 = 1):      |                 |                  |                  |             |

|                  |                             | address detect                      |                |                 |                  |                  |             |

|                  |                             | address detec                       |                | are received a  | nd 9th bit can b | e used as parit  | y bit       |

|                  | -                           | is mode 8-bit (F                    | (xy = 0):      |                 |                  |                  |             |

| L:1 0            | Don't care                  | in a Fana a bit                     |                |                 |                  |                  |             |

| bit 2            | FERR: Fram                  | -                                   | indated by rea |                 | agistar and raa  | oive povt velid  | huto)       |

|                  | 1 = Framing<br>0 = No frami | error (can be ι<br>ing error        | ipualeu by rea | IUNIY KOREG I   | egister and rec  | eive next valiu  | byte)       |

| bit 1            | OERR: Over                  | run Error bit                       |                |                 |                  |                  |             |

|                  |                             | error (can be c                     | leared by clea | ring bit CREN)  | I                |                  |             |

| <b>h</b> :+ 0    | 0 = No overi                |                                     | Data           |                 |                  |                  |             |

| bit 0            |                             | bit of Received<br>address/data bi  |                |                 |                  | c                |             |

|                  |                             |                                     |                |                 |                  |                  |             |

#### REGISTER 22-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

|        |                   |            |                             |                | SYNC       | <b>C</b> = 0, BRGH          | l = 0, BRC     | <b>616 =</b> 0 |                             |                    |            |                             |

|--------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|----------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Fosc = 20.000 MHz |            | Fosc = 18.432 MHz           |                |            | Foso                        | : = 16.00      | 0 MHz          | Fosc                        | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _                 | _          | _                           | _              | _          | _                           | _              | _              | _                           | _                  | _          | _                           |

| 1200   | 1221              | 1.73       | 255                         | 1200           | 0.00       | 239                         | 1202           | 0.16           | 207                         | 1200               | 0.00       | 143                         |

| 2400   | 2404              | 0.16       | 129                         | 2400           | 0.00       | 119                         | 2404           | 0.16           | 103                         | 2400               | 0.00       | 71                          |

| 9600   | 9470              | -1.36      | 32                          | 9600           | 0.00       | 29                          | 9615           | 0.16           | 25                          | 9600               | 0.00       | 17                          |

| 10417  | 10417             | 0.00       | 29                          | 10286          | -1.26      | 27                          | 10417          | 0.00           | 23                          | 10165              | -2.42      | 16                          |

| 19.2k  | 19.53k            | 1.73       | 15                          | 19.20k         | 0.00       | 14                          | 19.23k         | 0.16           | 12                          | 19.20k             | 0.00       | 8                           |

| 57.6k  | —                 | _          | _                           | 57.60k         | 0.00       | 7                           | —              | _              | _                           | 57.60k             | 0.00       | 2                           |

| 115.2k | —                 | _          | —                           | _              | _          | —                           | —              | _              | —                           | —                  | _          | —                           |

| TABLE $22^{-4}$ . DAUD RATES FOR ASTINGTRUNUUS WUDES | <b>TABLE 22-4:</b> | <b>BAUD RATES FOR ASYNCHRONOUS MODES</b> |

|------------------------------------------------------|--------------------|------------------------------------------|

|------------------------------------------------------|--------------------|------------------------------------------|

|        |                  | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------|------------------|-------------------------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz |                               |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _                | _                             | _                           | 300              | 0.16       | 207                         | 300               | 0.00       | 191                         | 300              | 0.16       | 51                          |

| 1200   | 1202             | 0.16                          | 103                         | 1202             | 0.16       | 51                          | 1200              | 0.00       | 47                          | 1202             | 0.16       | 12                          |

| 2400   | 2404             | 0.16                          | 51                          | 2404             | 0.16       | 25                          | 2400              | 0.00       | 23                          | —                | _          | _                           |

| 9600   | 9615             | 0.16                          | 12                          | _                | _          | _                           | 9600              | 0.00       | 5                           | _                | _          | _                           |

| 10417  | 10417            | 0.00                          | 11                          | 10417            | 0.00       | 5                           | _                 | _          | _                           | _                | _          | _                           |

| 19.2k  | —                | _                             | _                           | _                | _          | _                           | 19.20k            | 0.00       | 2                           | _                | _          | _                           |

| 57.6k  | —                | —                             | _                           | —                | —          | —                           | 57.60k            | 0.00       | 0                           | —                | —          | —                           |

| 115.2k | —                | _                             | _                           | —                | _          | _                           | _                 |            | _                           | —                | _          | —                           |

|        |                   | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                   |            |                             |                   |            |                             |                    |            |                             |

|--------|-------------------|-------------------------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Fosc = 20.000 MHz |                               | 0 MHz                       | Fosc = 18.432 MHz |            |                             | Fosc = 16.000 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    |                   |                               | _                           |                   |            | _                           |                   | _          | _                           |                    | _          | _                           |

| 1200   | _                 | _                             | _                           | _                 | _          | _                           | _                 | _          | _                           | _                  | _          | _                           |

| 2400   |                   | _                             | _                           | _                 | _          | _                           | _                 | _          | _                           | _                  | _          | _                           |

| 9600   | 9615              | 0.16                          | 129                         | 9600              | 0.00       | 119                         | 9615              | 0.16       | 103                         | 9600               | 0.00       | 71                          |

| 10417  | 10417             | 0.00                          | 119                         | 10378             | -0.37      | 110                         | 10417             | 0.00       | 95                          | 10473              | 0.53       | 65                          |

| 19.2k  | 19.23k            | 0.16                          | 64                          | 19.20k            | 0.00       | 59                          | 19.23k            | 0.16       | 51                          | 19.20k             | 0.00       | 35                          |

| 57.6k  | 56.82k            | -1.36                         | 21                          | 57.60k            | 0.00       | 19                          | 58.82k            | 2.12       | 16                          | 57.60k             | 0.00       | 11                          |

| 115.2k | 113.64k           | -1.36                         | 10                          | 115.2k            | 0.00       | 9                           | 111.1k            | -3.55      | 8                           | 115.2k             | 0.00       | 5                           |

|              | DC CI | HARACTERISTICS                                   | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature -40°C} \leq TA \leq +85°C \mbox{ for industrial} \\ -40°C \leq TA \leq +125°C \mbox{ for extended} \end{array}$ |      |      |       |                                                                            |  |  |  |

|--------------|-------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|----------------------------------------------------------------------------|--|--|--|

| Param<br>No. | Sym.  | Characteristic                                   | Min.                                                                                                                                                                                                                            | Тур† | Max. | Units | Conditions                                                                 |  |  |  |

|              | Voн   | Output High Voltage <sup>(4)</sup>               |                                                                                                                                                                                                                                 |      |      |       |                                                                            |  |  |  |

| D090         |       | I/O ports                                        | Vdd - 0.7                                                                                                                                                                                                                       | _    | _    | V     | IOH = 3.5 mA, VDD = 5V<br>IOH = 3 mA, VDD = 3.3V<br>IOH = 1 mA, VDD = 1.8V |  |  |  |

|              |       | Capacitive Loading Specs or                      | Output Pins                                                                                                                                                                                                                     |      |      |       |                                                                            |  |  |  |

| D101*        | COSC2 | OSC2 pin                                         | —                                                                                                                                                                                                                               | —    | 15   | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1     |  |  |  |

| D101A*       | Сю    | All I/O pins                                     | —                                                                                                                                                                                                                               | _    | 50   | pF    |                                                                            |  |  |  |

|              |       | VCAP Capacitor Charging                          |                                                                                                                                                                                                                                 |      |      |       |                                                                            |  |  |  |

| D102*        |       | Charging current                                 | —                                                                                                                                                                                                                               | _    | 200  | μA    |                                                                            |  |  |  |

| D102A*       |       | Source/Sink capability when<br>charging complete | -                                                                                                                                                                                                                               | —    | 0.0  | mA    |                                                                            |  |  |  |

#### 25.6 DC Characteristics: I/O Ports (Continued)

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are t not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: Including OSC2 in CLKOUT mode.

# PIC16(L)F1516/7/8/9

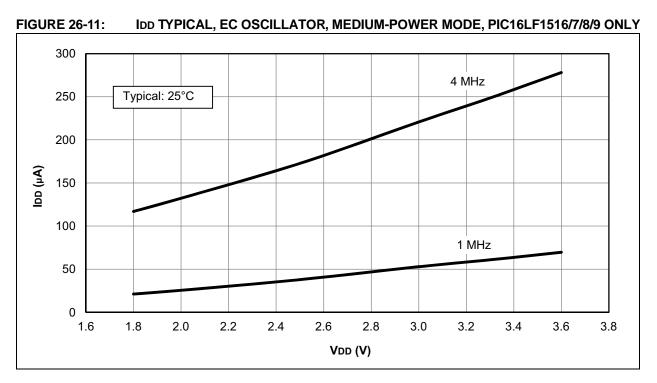

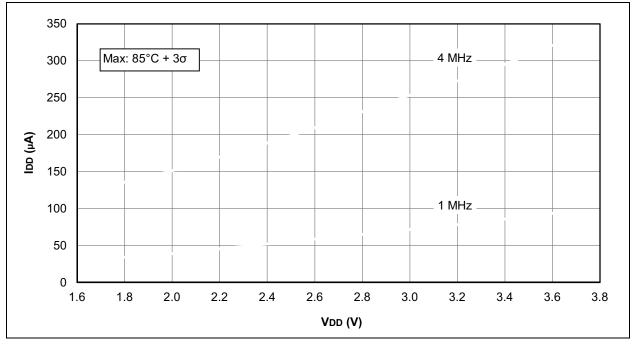

FIGURE 26-12: IDD MAXIMUM, EC OSCILLATOR, MEDIUM-POWER MODE, PIC16LF1516/7/8/9 ONLY

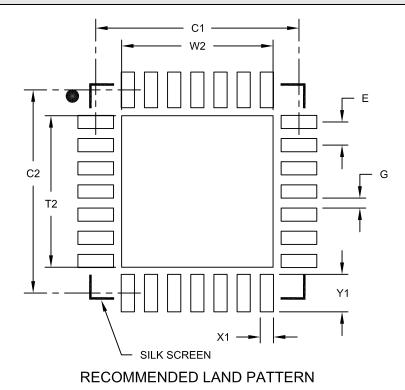

#### 28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS      |           |          |      |  |  |

|------------------------|------------------|-----------|----------|------|--|--|

| Dimensior              | Dimension Limits |           |          |      |  |  |

| Number of Pins         | N                |           | 28       |      |  |  |

| Pitch                  | е                |           | 0.40 BSC |      |  |  |

| Overall Height         | A                | 0.45      | 0.50     | 0.55 |  |  |

| Standoff               | A1               | 0.00      | 0.02     | 0.05 |  |  |

| Contact Thickness      | A3               | 0.127 REF |          |      |  |  |

| Overall Width          | E                | 4.00 BSC  |          |      |  |  |

| Exposed Pad Width      | E2               | 2.55      | 2.65     | 2.75 |  |  |

| Overall Length         | D                |           | 4.00 BSC |      |  |  |

| Exposed Pad Length     | D2               | 2.55      | 2.65     | 2.75 |  |  |

| Contact Width          | b                | 0.15      | 0.20     | 0.25 |  |  |

| Contact Length         | L                | 0.30      | 0.40     | 0.50 |  |  |