#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                |                                                                           |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 28x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

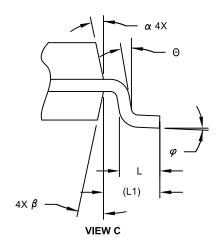

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1517-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F1516/7/8/9

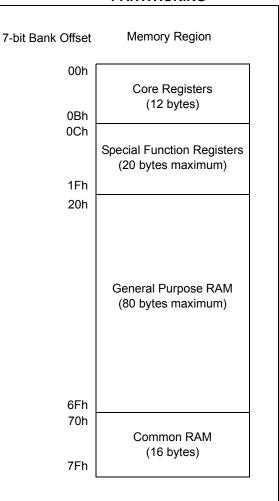

## 3.4.1 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh). The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

#### 3.4.2 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh).

#### 3.4.2.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.7.2** "Linear Data Memory" for more information.

#### 3.4.3 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### FIGURE 3-3: BANKED MEMORY PARTITIONING

#### 3.4.4 DEVICE MEMORY MAPS

The memory maps for PIC16(L)F1516/7 and PIC16(L)F1518/9 are as shown in Table 3-3 and Table 3-4, respectively.

# PIC16(L)F1516/7/8/9

| IABI               | _E 3-8: S              | PECIAL    | FUNCTI                      | ON REG        | SISTER S       | UMMAR         | Y (CONI | INUED) |           |                      |                                 |

|--------------------|------------------------|-----------|-----------------------------|---------------|----------------|---------------|---------|--------|-----------|----------------------|---------------------------------|

| Addr               | Name                   | Bit 7     | Bit 6                       | Bit 5         | Bit 4          | Bit 3         | Bit 2   | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| Banl               | k 2                    |           |                             |               |                |               |         |        |           |                      |                                 |

| 10Ch               | LATA                   | PORTA Dat | ta Latch                    |               |                |               |         |        |           | xxxx xxxx            | uuuu uuuu                       |

| 10Dh               | LATB                   | PORTB Da  | ta Latch                    |               |                |               |         |        |           | xxxx xxxx            | uuuu uuuu                       |

| 10Eh               | LATC                   | PORTC Da  | ita Latch                   |               |                |               |         |        |           | xxxx xxxx            | uuuu uuuu                       |

| 10Fh               | LATD <sup>(2)</sup>    | PORTD Da  | ta Latch                    |               |                |               |         |        |           | xxxx xxxx            | uuuu uuuu                       |

| 110h               | LATE <sup>(2)</sup>    | —         | _                           | _             | _              | _             | LATE2   | LATE1  | LATE0     | xxx                  | uuu                             |

| 111h<br>to<br>115h | _                      | Unimpleme | ented                       |               |                |               |         |        |           | _                    | _                               |

| 116h               | BORCON                 | SBOREN    | BORFS                       | _             | _              | _             | _       | _      | BORRDY    | 10q                  | uuu                             |

| 117h               | FVRCON                 | FVREN     | FVRRDY                      | TSEN          | TSRNG          | _             | _       | ADFV   | R<1:0>    | 0q0000               | 0q0000                          |

| 118h<br>to<br>11Ch | _                      | Unimpleme | ented                       |               |                |               |         |        |           | _                    | _                               |

| 11Dh               | APFCON                 |           | —                           | -             | —              | _             | —       | SSSEL  | CCP2SEL   | 00                   | 00                              |

| 11Eh               | _                      | Unimpleme | ented                       |               |                |               |         |        |           | _                    | _                               |

| 11Fh               | _                      | Unimpleme | ented                       |               |                |               |         |        |           | _                    | _                               |

| Ban                | k 3                    |           |                             |               |                |               |         |        |           |                      |                                 |

| 18Ch               | ANSELA                 | _         | _                           | ANSA5         | _              | ANSA3         | ANSA2   | ANSA1  | ANSA0     | 1- 1111              | 1- 1111                         |

| 18Dh               | ANSELB                 | —         | _                           | ANSB5         | ANSB4          | ANSB3         | ANSB2   | ANSB1  | ANSB0     | 11 1111              | 11 1111                         |

| 18Eh               | ANSELC                 | ANSC7     | ANSC6                       | ANSC5         | ANSC4          | ANSC3         | ANSC2   | —      | _         | 1111 11              | 1111 11                         |

| 18Fh               | ANSELD <sup>(2)</sup>  | ANSD7     | ANSD6                       | ANSD5         | ANSD4          | ANSD3         | ANSD2   | ANSD1  | ANSD0     | 1111 1111            | 1111 1111                       |

| 190h               | ANSELE <sup>(2)</sup>  |           | _                           | -             | _              | _             | ANSE2   | ANSE1  | ANSE0     | 111                  | 111                             |

| 191h               | PMADRL                 | Program M | emory Addre                 | ess Register  | Low Byte       |               |         |        |           | 0000 0000            | 0000 0000                       |

| 192h               | PMADRH                 | _(3)      | Program M                   | emory Addre   | ess Register H | High Byte     |         |        |           | 1000 0000            | 1000 0000                       |

| 193h               | PMDATL                 | Program M | emory Data                  | Register Lov  | w Byte         |               |         |        |           | xxxx xxxx            | uuuu uuuu                       |

| 194h               | PMDATH                 | _         | _                           | Program M     | emory Data F   | Register High | Byte    |        |           | xx xxxx              | uu uuuu                         |

| 195h               | PMCON1                 | _(3)      | CFGS                        | LWLO          | FREE           | WRERR         | WREN    | WR     | RD        | 1000 x000            | 1000 q000                       |

| 196h               | PMCON2                 | Program M | emory contro                | ol register 2 |                |               |         |        |           | 0000 0000            | 0000 0000                       |

| 197h               | VREGCON <sup>(1)</sup> | _         | _                           | _             | _              | _             | _       | VREGPM | Reserved  | 01                   | 01                              |

| 198h               | _                      | Unimpleme | ented                       |               |                | 1             |         |        |           | _                    |                                 |

| 199h               | RCREG                  | USART Re  | USART Receive Data Register |               |                |               |         |        |           | 0000 0000            | 0000 0000                       |

| 19Ah               | TXREG                  |           | -                           |               |                |               |         |        | 0000 0000 | 0000 0000            |                                 |

| 19Bh               | SPBRG                  |           |                             |               |                |               |         |        | 0000 0000 | 0000 0000            |                                 |

| -                  | SPBRGH                 |           |                             |               | BRG<           |               |         |        |           | 0000 0000            | 0000 0000                       |

|                    | RCSTA                  | SPEN      | RX9                         | SREN          | CREN           | ADDEN         | FERR    | OERR   | RX9D      | 0000 000x            | 0000 000x                       |

|                    | TXSTA                  | CSRC      | TX9                         | TXEN          | SYNC           | SENDB         | BRGH    | TRMT   | TX9D      | 0000 0000k           | 0000 00010                      |

|                    | BAUDCON                | ABDOVF    | RCIDL                       |               | SCKP           | BRG16         | _       | WUE    | ABDEN     | 01-0 0-00            | 01-0 0-00                       |

|                    |                        |           |                             |               |                |               |         | -      |           | 01 0 0 00            | 01 0 0 00                       |

TABLE 3-8 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend: Note

PIC16F1516/7/8/9 only. 1:

PIC16(L)F1517/9 only. Unimplemented, read as '1'. 2: 3:

## 3.5 PCL and PCLATH

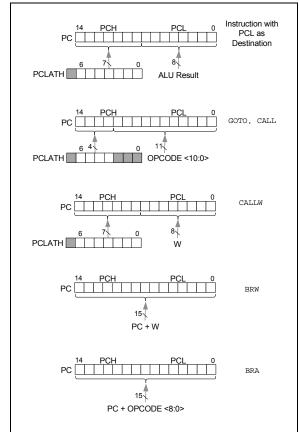

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 3-4 shows the five situations for the loading of the PC.

FIGURE 3-4: LOADING OF PC IN DIFFERENT SITUATIONS

#### 3.5.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register.

### 3.5.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the Application Note *AN556*, *Implementing a Table Read* (DS00556).

#### 3.5.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

#### 3.5.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 +, the signed value of the operand of the BRA instruction.

### 3.6 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figures 3-5 through 3-8). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer if the STVREN bit is programmed to '0' (Configuration Words). This means that after the stack has been PUSHed 16 times, the 17th PUSH overwrites the value that was stored from the first PUSH. The 18th PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

Note 1: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

### 3.6.1 ACCESSING THE STACK

The stack is available through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is five bits to allow detection of overflow and underflow.

| Note: | Care should be taken when modifying the |

|-------|-----------------------------------------|

|       | STKPTR while interrupts are enabled.    |

During normal program operation, CALL, CALLW and Interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. At any time STKPTR can be inspected to see how much stack is left. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC and then decrement STKPTR.

Reference Figure 3-5 through 3-8 for examples of accessing the stack.

#### FIGURE 3-5: ACCESSING THE STACK EXAMPLE 1

| TOSH:TOSL 0x0F |        | STKPTR = 0x1F Stack Reset Disabled (STVREN = 0)                                      |

|----------------|--------|--------------------------------------------------------------------------------------|

| 0x0D           |        |                                                                                      |

| 0x0C           |        |                                                                                      |

| 0x08           |        |                                                                                      |

|                |        |                                                                                      |

| A0x0           |        | Initial Stack Configuration:                                                         |

| 0x09           |        | After Reset, the stack is empty. The                                                 |

| 0x08           |        | empty stack is initialized so the Stack<br>Pointer is pointing at 0x1F. If the Stack |

| 0x07           |        | Overflow/Underflow Reset is enabled, the                                             |

| 0x06           |        | TOSH/TOSL registers will return '0'. If<br>the Stack Overflow/Underflow Reset is     |

| 0x05           |        | disabled, the TOSH/TOSL registers will<br>return the contents of stack address 0x0F. |

| 0x04           |        |                                                                                      |

| 0x03           |        |                                                                                      |

| 0x02           |        |                                                                                      |

| 0x01           |        |                                                                                      |

| 0x00           |        | 1                                                                                    |

| TOSH:TOSL 0x1F | 0x0000 | STKPTR = 0x1F Stack Reset Enabled (STVREN = 1)                                       |

|                |        | ·                                                                                    |

## PIC16(L)F1516/7/8/9

## 4.2 Register Definitions: Configuration Words

## REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/P-1                                                              | R/P-1         | R/P-1              | R/P-1              | R/P-1     | U-1   |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------|--------------------|--------------------|-----------|-------|

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | FCMEN                                                              | IESO          | CLKOUTEN           | BORE               | EN<1:0>   | _     |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 13                                                             |               |                    |                    |           | bit 8 |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |               |                    |                    |           |       |

| R/P-1                | R/P-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/P-1                                                              | R/P-1         | R/P-1              | R/P-1              | R/P-1     | R/P-1 |

| CP                   | MCLRE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PWRTE                                                              | WD.           | FE<1:0>            |                    | FOSC<2:0> |       |

| bit 7                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |               |                    |                    |           | bit ( |

| Legend:              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |               |                    |                    |           |       |

| R = Readable bit     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P = Programmab                                                     | e bit         | U = Unimplemente   | d bit, read as '1' |           |       |

| '0' = Bit is cleared |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | '1' = Bit is set                                                   |               | -n = Value when bl | ank or after Bulk  | Erase     |       |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |               |                    |                    |           |       |

| bit 13               | 1 = Fail-Safe Cloo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | e Clock Monitor En<br>ck Monitor is enable<br>ck Monitor is disabl | ed            |                    |                    |           |       |

| bit 12               | 1 = Internal/Exter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ternal Switchover b<br>nal Switchover mo<br>nal Switchover mo      | de is enabled |                    |                    |           |       |

| bit 11               | CLKOUTEN: Clock Out Enable bit         If FOSC Configuration bits are set to LP. XT. HS modes:         This bit is ignored, CLKOUT function is disabled. Oscillator function on the CLKOUT pin.         All other FOSC modes:         1 = CLKOUT function is disabled. I/O function on the CLKOUT pin.         0 = CLKOUT function is enabled on the CLKOUT pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    |               |                    |                    |           |       |

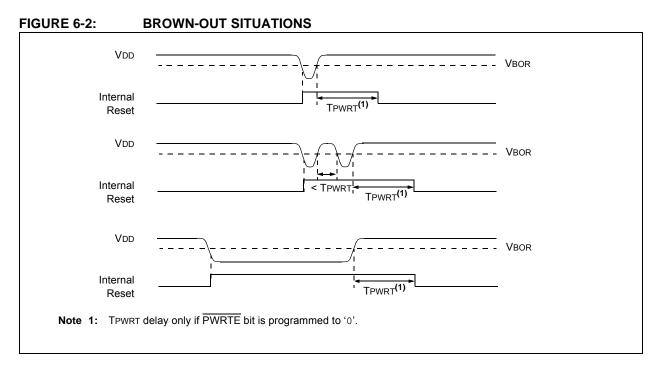

| bit 10-9             | BOREN<1:0>: Brown-out Reset Enable bits<br>11 = BOR enabled<br>10 = BOR enabled during operation and disabled in Sleep<br>01 = BOR controlled by SBOREN bit of the BORCON register<br>00 = BOR disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |               |                    |                    |           |       |

| bit 8                | Unimplemented:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Read as '1'                                                        |               |                    |                    |           |       |

| bit 7                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nory code protectio                                                |               |                    |                    |           |       |

| bit 6                | 0 = Program memory code protection is enabled<br>MCLRE: MCLR/VPP Pin Function Select bit<br>If LVP bit = 1:<br>This bit is ignored.<br>If LVP bit = 0:<br>1 = MCLR/VPP pin function is MCLR; Weak pull-up enabled.<br>0 = MCLR/VPP pin function is digital input; MCLR internally disabled; Weak pull-up under control of<br>WPUE3 bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |               |                    |                    |           |       |

| bit 5                | <b>PWRTE:</b> Power-u<br>1 = PWRT disal<br>0 = PWRT enab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |               |                    |                    |           |       |

| bit 4-3              | WDTE<1:0>: Watchdog Timer Enable bit<br>11 = WDT enabled<br>10 = WDT enabled while running and disabled in Sleep<br>01 = WDT controlled by the SWDTEN bit in the WDTCON register<br>00 = WDT disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                    |               |                    |                    |           |       |

| bit 2-0              | FOSC<2:0>: Oscillator Selection bits         111 =       ECH: External Clock, High-Power mode (4-20 MHz): device clock supplied to CLKIN pin         110 =       ECM: External Clock, Medium-Power mode (0.5-4 MHz): device clock supplied to CLKIN pin         101 =       ECL: External Clock, Low-Power mode (0.05-4 MHz): device clock supplied to CLKIN pin         101 =       EXErnal Clock, Low-Power mode (0.05 MHz): device clock supplied to CLKIN pin         101 =       EXTRC oscillator: I/O function on CLKIN pin         011 =       EXTRC oscillator: External RC circuit connected to CLKIN pin         010 =       HS oscillator: High-speed crystal/resonator connected between OSC1 and OSC2 pins         000 =       LP oscillator: Low-power crystal connected between OSC1 and OSC2 pins |                                                                    |               |                    |                    |           |       |

## 6.3 Register Definitions: BOR Control

## REGISTER 6-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | R/W-0/u | U-0 | U-0 | U-0 | U-0 | U-0   | R-q/u  |

|---------|---------|-----|-----|-----|-----|-------|--------|

| SBOREN  | BORFS   | —   | —   | —   | —   | —     | BORRDY |

| bit 7   |         |     |     |     |     | bit 0 |        |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-out Reset Enable bit <sup>(1)</sup> If BOREN <1:0> in Configuration Words ≠ 01: SBOREN is read/write, but has no effect on the BOR If BOREN <1:0> in Configuration Words = 01: 1 = BOR Enabled 0 = BOR Disabled                                                                                                                                                                                                                            |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | <ul> <li>BORFS: Brown-out Reset Fast Start bit<sup>(1)</sup></li> <li>If BOREN&lt;1:0&gt; = 11 (Always on) or BOREN&lt;1:0&gt; = 00 (Always off)</li> <li>BORFS is Read/Write, but has no effect.</li> <li>If BOREN &lt;1:0&gt; = 10 (Disabled in Sleep) or BOREN&lt;1:0&gt; = 01 (Under software control):</li> <li>1 = Band gap is forced on always (covers sleep/wake-up/operating cases)</li> <li>0 = Band gap operates normally, and may turn off</li> </ul> |

| bit 5-1 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bit 0   | <b>BORRDY:</b> Brown-out Reset Circuit Ready Status bit<br>1 = The Brown-out Reset circuit is active<br>0 = The Brown-out Reset circuit is inactive                                                                                                                                                                                                                                                                                                               |

**Note 1:** BOREN<1:0> bits are located in Configuration Words.

## 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIEx register)

The INTCON, PIR1 and PIR2 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- · Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See Section 7.5 "Automatic Context Saving")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

## 7.2 Interrupt Latency

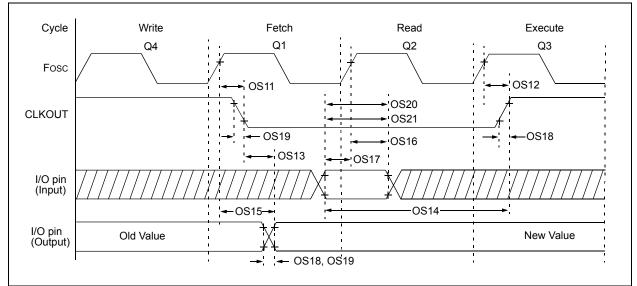

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7-3 for more details.

| R/W-0/       | 0 R/W-0/0                  | R-0/0                                          | R-0/0           | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |

|--------------|----------------------------|------------------------------------------------|-----------------|----------------|------------------|------------------|--------------|--|--|--|

| TMR1G        | IF ADIF                    | RCIF                                           | TXIF            | SSPIF          | CCP1IF           | TMR2IF           | TMR1IF       |  |  |  |

| bit 7        | ·                          |                                                | •               | ÷              | ·                | •                | bit C        |  |  |  |

|              |                            |                                                |                 |                |                  |                  |              |  |  |  |

| Legend:      | - <b>b</b> 1 - <b>b</b> :4 |                                                | L.14            |                |                  |                  |              |  |  |  |

| R = Reada    |                            | W = Writable                                   |                 |                | mented bit, read |                  |              |  |  |  |

|              | inchanged                  | x = Bit is unk                                 |                 | -n/n = value   | at POR and BO    | R/value at all c | other Resets |  |  |  |

| '1' = Bit is | set                        | '0' = Bit is cle                               | ared            |                |                  |                  |              |  |  |  |

| bit 7        | TMR1GIF:                   | : Timer1 Gate Inte                             | errupt Flag bit |                |                  |                  |              |  |  |  |

|              |                            | pt is pending                                  |                 |                |                  |                  |              |  |  |  |

|              | 0 = Interru                | pt is not pending                              |                 |                |                  |                  |              |  |  |  |

| bit 6        |                            | C Interrupt Flag b                             | it              |                |                  |                  |              |  |  |  |

|              |                            | pt is pending                                  |                 |                |                  |                  |              |  |  |  |

| L:1 F        |                            | pt is not pending                              |                 |                |                  |                  |              |  |  |  |

| bit 5        |                            | ART Receive Inte                               | rrupt Flag bit  |                |                  |                  |              |  |  |  |

|              |                            | pt is pending<br>pt is not pending             |                 |                |                  |                  |              |  |  |  |

| bit 4        |                            | <b>TXIF:</b> USART Transmit Interrupt Flag bit |                 |                |                  |                  |              |  |  |  |

|              |                            | 1 = Interrupt is pending                       |                 |                |                  |                  |              |  |  |  |

|              | 0 = Interru                | pt is not pending                              |                 |                |                  |                  |              |  |  |  |

| bit 3        | SSPIF: Sy                  | nchronous Serial                               | Port (MSSP)     | Interrupt Flag | oit              |                  |              |  |  |  |

|              |                            | pt is pending                                  |                 |                |                  |                  |              |  |  |  |

|              |                            | pt is not pending                              |                 |                |                  |                  |              |  |  |  |

| bit 2        |                            | CP1 Interrupt Fla                              | ag bit          |                |                  |                  |              |  |  |  |

|              |                            | pt is pending<br>pt is not pending             |                 |                |                  |                  |              |  |  |  |

| bit 1        |                            | Timer2 to PR2 Inte                             | errupt Flag bit |                |                  |                  |              |  |  |  |

|              |                            | pt is pending                                  |                 |                |                  |                  |              |  |  |  |

|              |                            | pt is not pending                              |                 |                |                  |                  |              |  |  |  |

| bit 0        | TMR1IF: 7                  | imer1 Overflow I                               | nterrupt Flag I | bit            |                  |                  |              |  |  |  |

|              |                            | pt is pending                                  |                 |                |                  |                  |              |  |  |  |

|              | 0 = Interru                | pt is not pending                              |                 |                |                  |                  |              |  |  |  |

| Note:        | Interrupt flag bit         | s are set when ar                              | n interrupt     |                |                  |                  |              |  |  |  |

|              |                            | s, regardless of th                            |                 |                |                  |                  |              |  |  |  |

|              |                            | ng enable bit or the<br>E, of the INTCON       |                 |                |                  |                  |              |  |  |  |

|              | User software              |                                                | •               |                |                  |                  |              |  |  |  |

|              |                            | rrupt flag bits are o                          |                 |                |                  |                  |              |  |  |  |

|              | to enabling an i           | nterrupt.                                      |                 |                |                  |                  |              |  |  |  |

## REGISTER 7-4: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

## 8.0 POWER-DOWN MODE (SLEEP)

The Power-Down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3. TO bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 and peripherals that operate from Timer1 continue operation in Sleep when the Timer1 clock source selected is:

- LFINTOSC

- T1CKI

- Secondary oscillator

- 7. ADC is unaffected, if the dedicated FRC oscillator is selected.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

- 9. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- · Internal circuitry sourcing current from I/O pins

- · Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- · Modules using secondary oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include the FVR module. See **Section 14.0 "Fixed Voltage Reference (FVR)"** for more information on this module.

### 8.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 6.12 "Determining the Cause of a Reset"**.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

| Name    | Bit 7                                        | Bit 6                           | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|---------|----------------------------------------------|---------------------------------|--------|-------|-------|--------|---------|--------|---------------------|

| CCP1CON | —                                            | —                               | DC1B   | <1:0> |       | CCP1   | √<3:0>  |        | 168                 |

| CCP2CON | —                                            | —                               | DC2B   | <1:0> |       | CCP2   | ∕l<3:0> |        | 168                 |

| INTCON  | GIE                                          | PEIE                            | TMR0IE | INTE  | IOCIE | TMR0IF | INTF    | IOCIF  | 74                  |

| PIE1    | TMR1GIE                                      | ADIE                            | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE  | TMR1IE | 75                  |

| PIR1    | TMR1GIF                                      | ADIF                            | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF  | TMR1IF | 77                  |

| PR2     | Timer2 Module Period Register                |                                 |        |       |       |        |         |        | 158*                |

| T2CON   | _                                            | T2OUTPS<3:0> TMR2ON T2CKPS<1:0> |        |       |       |        | S<1:0>  | 160    |                     |

| TMR2    | Holding Register for the 8-bit TMR2 Register |                                 |        |       |       |        |         | 158*   |                     |

## TABLE 19-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module.

\* Page provides register information.

#### 21.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK line. The master determines when the slave (Processor 2, Figure 21-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and Status bits appropriately set). The clock polarity is selected by appropriately programming the CKP bit of the SSPCON1 register and the CKE bit of the SSPSTAT register. This then, would give waveforms for SPI communication as shown in Figure 21-6, Figure 21-8, Figure 21-9 and Figure 21-10, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- · Timer2 output/2

- Fosc/(4 \* (SSPADD + 1))

Figure 21-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

Write to SSPBUF SCK (CKP = 0  $\dot{C}KE = 0$ ) SCK (CKP = 1  $\dot{C}KE = 0$ ) 4 Clock Modes SCK (CKP = 0 CKE = 1) SCK (CKP = 1 CKE = 1) bit 6 bit 2 SDO bit 7 bit 5 bit 4 bit 3 bit 1 bit 0 (CKE = 0) bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 SDO (CKE = 1) SDI (SMP = 0)bit 7 bit 0 Input Sample (SMP = 0)SDI (SMP = 1) bit 7 hi 0 Input Sample (SMP = 1)1 SSPIF SSPSR to SSPBUF

FIGURE 21-6: SPI MODE WAVEFORM (MASTER MODE)

| R/W-1/1          | R/W-1/1     | R/W-1/1                                                                                                                                                                                                           | R/W-1/1         | R/W-1/1                                               | R/W-1/1       | R/W-1/1 | R/W-1/1 |  |  |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------|---------------|---------|---------|--|--|

|                  |             |                                                                                                                                                                                                                   | MSK             | <7:0>                                                 |               |         |         |  |  |

| bit 7            |             |                                                                                                                                                                                                                   |                 |                                                       |               |         | bit 0   |  |  |

|                  |             |                                                                                                                                                                                                                   |                 |                                                       |               |         |         |  |  |

| Legend:          |             |                                                                                                                                                                                                                   |                 |                                                       |               |         |         |  |  |

| R = Readable     | bit         | W = Writable bit                                                                                                                                                                                                  |                 | U = Unimplemented bit, read as '0'                    |               |         |         |  |  |

| u = Bit is unch  | nanged      | x = Bit is unkr                                                                                                                                                                                                   | nown            | -n/n = Value at POR and BOR/Value at all other Resets |               |         |         |  |  |

| '1' = Bit is set |             | '0' = Bit is cle                                                                                                                                                                                                  | ared            |                                                       |               |         |         |  |  |

|                  |             |                                                                                                                                                                                                                   |                 |                                                       |               |         |         |  |  |

| bit 7-1          | MSK<7:1>:   |                                                                                                                                                                                                                   |                 |                                                       |               |         |         |  |  |

|                  | 1 = The rec | <ul> <li>1 = The received address bit n is compared to SSPADD<n> to detect I<sup>2</sup>C address match</n></li> <li>0 = The received address bit n is not used to detect I<sup>2</sup>C address match</li> </ul> |                 |                                                       |               |         |         |  |  |

|                  | 0 = The rec | eived address b                                                                                                                                                                                                   | it n is not use | d to detect I <sup>2</sup> C                          | address match |         |         |  |  |

## REGISTER 21-7: SSPMSK: SSP MASK REGISTER

|       | 1 = The received address bit n is compared to SSPADD <n> to detect <math>I^2C</math> address match 0 = The received address bit n is not used to detect <math>I^2C</math> address match</n>                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 0 | <b>MSK&lt;0&gt;:</b> Mask bit for I <sup>2</sup> C Slave mode, 10-bit Address<br>I <sup>2</sup> C Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111):<br>1 = The received address bit 0 is compared to SSPADD<0> to detect I <sup>2</sup> C address match |

|       | 0 = The received address bit 0 is compared to 337ADD<02 to detect 1 C address match<br>0 = The received address bit 0 is not used to detect I <sup>2</sup> C address match<br>I <sup>2</sup> C Slave mode, 7-bit address, the bit is ignored                 |

## REGISTER 21-8: SSPADD: MSSP ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

|                                         |         |                   |                |                  |                |              | -,      |

|-----------------------------------------|---------|-------------------|----------------|------------------|----------------|--------------|---------|

| R/W-0/0                                 | R/W-0/0 | R/W-0/0           | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      | R/W-0/0 |

|                                         |         |                   | ADD            | <7:0>            |                |              |         |

| bit 7                                   |         |                   |                |                  |                |              | bit 0   |

|                                         |         |                   |                |                  |                |              |         |

| Legend:                                 |         |                   |                |                  |                |              |         |

| R = Readable bit W = Writable bit       |         | oit               | U = Unimpler   | nented bit, read | d as '0'       |              |         |

| u = Bit is unchanged x = Bit is unknown |         | own               | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |         |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared           |                  |                |              |         |

## Master mode:

| bit 7-0 | ADD<7:0>: Baud Rate Clock Divider bits          |

|---------|-------------------------------------------------|

|         | SCL pin clock period = ((ADD<7:0> + 1) *4)/Fosc |

### <u>10-Bit Slave mode — Most Significant Address Byte:</u>

- bit 7-3 **Not used:** Unused for Most Significant Address byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

## <u> 10-Bit Slave mode — Least Significant Address Byte:</u>

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

## 7-Bit Slave mode:

| bit 7-1 | ADD<7:1>: 7-bit address |

|---------|-------------------------|

|         |                         |

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

## 22.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VoL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 22-4 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the 9th data bit.

#### 22.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 22-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREG register.

#### 22.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note 1:** The TXIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

#### 22.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the Stop bit of the previous character has been transmitted. The pending character in the TXREG is then transferred to the TSR in one TCY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREG.

#### 22.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDCON register. The default state of this bit is '0' which selects high true transmit ldle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true ldle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 22.5.1.2 "Clock Polarity"**.

#### 22.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXREG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXREG.

#### 22.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 22-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 22.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

**Note 1:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

## 22.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 22.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

| Note: | If the receive FIFO is overrun, no additional |

|-------|-----------------------------------------------|

|       | characters will be received until the overrun |

|       | condition is cleared. See Section 22.1.2.5    |

|       | "Receive Overrun Error" for more              |

|       | information on overrun errors.                |

### 22.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE, Interrupt Enable bit of the PIE1 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register