Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 28x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1517-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 7.5 "Automatic Context Saving"**, for more information.

#### 2.2 16-Level Stack with Overflow and Underflow

These devices have an external stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled will cause a software Reset. See **Section 3.6 "Stack"** for more details.

## 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.7 "Indirect Addressing"** for more details.

### 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 24.0 "Instruction Set Summary"** for more details.

## 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

#### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

## 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection is controlled independently. Internal access to the program memory is unaffected by any code protection setting.

#### 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4** "Write **Protection**" for more information.

#### 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

### 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 11.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the "*PIC16(L)F151X/152X Memory Programming Specification*" (DS41442).

#### 8.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared

- If the interrupt occurs **during or after** the execution of a SLEEP instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

| OSC1 <sup>(1)</sup><br>CLKOUT <sup>(2)</sup> | 1                                                                                           | Q1 Q2 Q3  Q4                             | <u></u>               | Tost <sup>(3)</sup> |                 | Q1 Q2 Q3 Q4<br>/~_/~_/ | Q1 Q2 Q3 Q4<br>//////////////////////////////////// | Q1 Q2 Q3 Q4<br>     |

|----------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------|-----------------------|---------------------|-----------------|------------------------|-----------------------------------------------------|---------------------|

| Interrupt flag                               | 1<br>H                                                                                      | 1<br>+                                   | ·                     |                     | Interrupt Laten | cy <sup>(4)</sup>      | · · ·                                               |                     |

| GIE bit<br>(INTCON reg.)                     | '                                                                                           | I<br>I<br>I<br>I<br>I<br>I               | Processor in<br>Sleep |                     |                 | ·                      |                                                     |                     |

| Instruction Flow                             | ,<br>,<br>,                                                                                 | 1<br>1<br>1                              | 1                     | 1<br>1              | ·<br>·          | 1<br>1<br>1            | , , , , , , , , , , , , , , , , , , ,               | 1                   |

| PC                                           | X PC                                                                                        | X PC + 1                                 | X PC                  | + 2                 | X PC + 2        | X PC + 2               | <u>χ 0004h</u>                                      | X 0005h             |

| Instruction {<br>Fetched                     | Inst(PC) = Sleep                                                                            | Inst(PC + 1)                             |                       |                     | Inst(PC + 2)    | י<br>ו<br>ו            | Inst(0004h)                                         | Inst(0005h)         |

| Instruction {<br>Executed {                  | Inst(PC - 1)                                                                                | Sleep                                    | 1<br>1<br>1           |                     | Inst(PC + 1)    | Forced NOP             | Forced NOP                                          | Inst(0004h)         |

| 2: (<br>3:                                   | XT, HS or LP Oscil<br>CLKOUT is not ava<br>Tost=1024 Tosc. <sup>-</sup><br>Speed Clock Star | ailable in XT, HS,<br>This delay does no | or LP Oscillato       |                     | ·               | 0                      |                                                     | e Section 5.4 "Two- |

4: GIE = 1 assumed. In this case after wake-up, the processor calls the ISR at 0004h. If GIE = 0, execution will continue in-line.

#### FIGURE 8-1: WAKE-UP FROM SLEEP THROUGH INTERRUPT

## 10.6 Register Definitions: Watchdog Control

| U-0                           | U-0                | R/W-0/0                                                        | R/W-1/1        | R/W-0/0                   | R/W-1/1         | R/W-1/1         | R/W-0/0      |

|-------------------------------|--------------------|----------------------------------------------------------------|----------------|---------------------------|-----------------|-----------------|--------------|

| _                             | —                  |                                                                |                | WDTPS<4:0                 | >               |                 | SWDTEN       |

| pit 7                         |                    | •                                                              |                |                           |                 |                 | bit          |

| agandi                        |                    |                                                                |                |                           |                 |                 |              |

| <b>.egend:</b><br>R = Readabl | e hit              | W = Writable                                                   | bit            | U = Unimpler              | nented bit, rea | 1 as '0'        |              |

| u = Bit is und                |                    | x = Bit is unkr                                                |                | •                         |                 | DR/Value at all | other Pesets |

| 1' = Bit is se                | •                  | 0' = Bit is clear                                              |                |                           |                 |                 |              |

|                               | ι.<br>             |                                                                | areu           |                           |                 |                 |              |

| bit 7-6                       | Unimpleme          | nted: Read as '                                                | 0'             |                           |                 |                 |              |

| bit 5-1                       | WDTPS<4:0          | )>: Watchdog Ti                                                | mer Period S   | elect bits <sup>(1)</sup> |                 |                 |              |

|                               | Bit Value =        | Prescale Rate                                                  |                |                           |                 |                 |              |

|                               | 11111 = R          | eserved. Result                                                | s in minimum   | interval (1:32)           |                 |                 |              |

|                               | •                  |                                                                |                | . ,                       |                 |                 |              |

|                               | •                  |                                                                |                |                           |                 |                 |              |

|                               | •                  | annual Descrit                                                 |                | interval (1.20)           |                 |                 |              |

|                               | 10011 = R          | eserved. Result                                                | s in minimum   | interval (1:32)           |                 |                 |              |

|                               | 10010 = <b>1</b> : | 8388608 (2 <sup>23</sup> ) (                                   | Interval 256s  | nominal)                  |                 |                 |              |

|                               | 10001 = <b>1</b> : | 8388608 (2 <sup>23</sup> ) (<br>4194304 (2 <sup>22</sup> ) (   | Interval 128s  | nominal)                  |                 |                 |              |

|                               | 10000 = 1:         | 2097152 (2 <sup>21</sup> ) (                                   | Interval 64s n | ominal)                   |                 |                 |              |

|                               | 01111 = 1:         | 1048576 (2 <sup>20</sup> ) (                                   | Interval 32s n | ominal)                   |                 |                 |              |

|                               | 01110 = 1          | 524288 (2 <sup>19</sup> ) (Ir                                  | iterval 16s no | minal)                    |                 |                 |              |

|                               | 01101 = 1          | 262144 (2 <sup>18</sup> ) (Ir<br>131072 (2 <sup>17</sup> ) (Ir | iterval 8s non | ninal)                    |                 |                 |              |

|                               |                    | 65536 (Interval                                                |                |                           |                 |                 |              |

|                               |                    | 32768 (Interval                                                |                |                           |                 |                 |              |

|                               |                    | 16384 (Interval                                                |                | nal)                      |                 |                 |              |

|                               |                    | 8192 (Interval 2                                               |                | ,                         |                 |                 |              |

|                               |                    | 4096 (Interval 1                                               |                |                           |                 |                 |              |

|                               | 00110 <b>= 1</b> : | 2048 (Interval 6                                               | 4 ms nominal   | )                         |                 |                 |              |

|                               |                    | 1024 (Interval 3                                               |                | )                         |                 |                 |              |

|                               |                    | 512 (Interval 16                                               |                |                           |                 |                 |              |

|                               |                    | 256 (Interval 8 r                                              |                |                           |                 |                 |              |

|                               |                    | 128 (Interval 4 r                                              | ,              |                           |                 |                 |              |

|                               |                    | 64 (Interval 2 m<br>32 (Interval 1 m                           |                |                           |                 |                 |              |

| oit 0                         |                    | Software Enable/                                               |                | /atchdog Timer            | hit             |                 |              |

|                               | If WDTE<1:         |                                                                |                | atonuog milei             | UIL .           |                 |              |

|                               | This bit is ig     |                                                                |                |                           |                 |                 |              |

|                               | If WDTE<1:         |                                                                |                |                           |                 |                 |              |

|                               | 1 = WDT is         |                                                                |                |                           |                 |                 |              |

|                               | 0 = WDT is         | turned off                                                     |                |                           |                 |                 |              |

|                               | If WDTE<1:         |                                                                |                |                           |                 |                 |              |

|                               | This bit is ig     |                                                                |                |                           |                 |                 |              |

#### **REGISTER 10-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER**

DS40001452F-page 95

PIC16(L)F1516/7/8/9

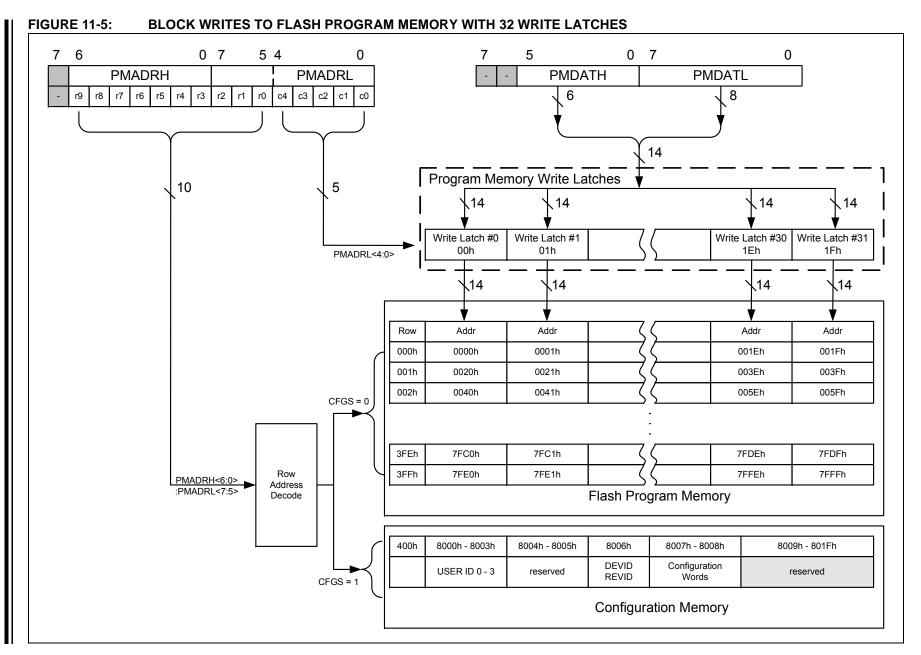

#### 11.4 User ID, Device ID and Configuration Word Access

Instead of accessing program memory, the User ID's, Device ID/Revision ID and Configuration Words can be accessed when CFGS = 1 in the PMCON1 register. This is the region that would be pointed to by PC<15> = 1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table .

When read access is initiated on an address outside the parameters listed in Table , the PMDATH:PMDATL register pair is cleared, reading back '0's.

#### TABLE 11-1:USER ID, DEVICE ID AND CONFIGURATION WORD ACCESS (CFGS = 1)

| Address     | Function                    | Read Access | Write Access |

|-------------|-----------------------------|-------------|--------------|

| 8000h-8003h | User IDs                    | Yes         | Yes          |

| 8006h       | Device ID/Revision ID       | Yes         | No           |

| 8007h-8008h | Configuration Words 1 and 2 | Yes         | No           |

#### EXAMPLE 11-4: CONFIGURATION WORD AND DEVICE ID ACCESS

This code block will read 1 word of program memory at the memory address: PROG\_ADDR\_LO (must be 00h-08h) data will be returned in the variables; PROG\_DATA\_HI, PROG\_DATA\_LO MOVLW PROG\_ADDR\_LO ; Select correct Bank MOVWF PMADR MOVWF PMADRL ; Store LSB of address CLRF PMADRH ; Clear MSB of address ; Select Configuration Space PMCON1,CFGS BSF INTCON,GIE BCF ; Disable interrupts PMCON1,RD BSF ; Initiate read NOP ; Executed (See Figure 11-2) NOP ; Ignored (See Figure 11-2) INTCON,GIE BSF ; Restore interrupts MOVF PMDATL,W ; Get LSB of word MOVWF PROG\_DATA\_LO ; Store in user location MOVF PMDATH,W ; Get MSB of word PROG\_DATA\_HI ; Store in user location MOVWF

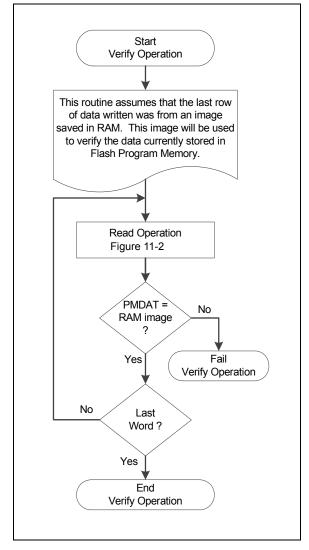

### 11.5 Write Verify

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full page then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

FIGURE 11-8: FLASH PROGRAM MEMORY VERIFY FLOWCHART

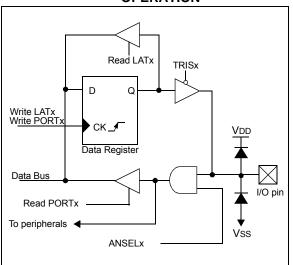

## 12.0 I/O PORTS

Each port has three standard registers for its operation. These registers are:

- TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- ANSELx (analog select)

- WPUx (weak pull-up)

In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

#### TABLE 12-1: PORT AVAILABILITY PER DEVICE

| Device          | PORTA | РОКТВ | PORTC | PORTD | PORTE |

|-----------------|-------|-------|-------|-------|-------|

| PIC16(L)F1516/8 | •     | •     | ٠     |       | •     |

| PIC16(L)F1517/9 | •     | •     | •     | •     | •     |

The Data Latch (LATx register) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 12-1.

#### FIGURE 12-1: GENERIC I/O PORT OPERATION

## 19.5 Register Definitions: Timer2 Control

| U-0            | R/W-0/0                                | R/W-0/0                   | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|----------------|----------------------------------------|---------------------------|----------------|----------------|------------------|----------------|--------------|

| _              | T2OUTPS<3:0>                           |                           |                |                | TMR2ON           | T2CKF          | 'S<1:0>      |

| bit 7          |                                        |                           |                |                |                  |                | bit          |

|                |                                        |                           |                |                |                  |                |              |

| Legend:        |                                        |                           |                |                |                  |                |              |

| R = Readal     |                                        | W = Writable              |                | -              | mented bit, read |                |              |

| u = Bit is ur  | -                                      | x = Bit is unkr           | iown           | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is s | et                                     | '0' = Bit is clea         | ared           |                |                  |                |              |

| bit 7          | Unimpleme                              | ented: Read as '          | 0'             |                |                  |                |              |

| bit 6-3        | T2OUTPS<                               | 3:0>: Timer2 Ou           | tput Postscale | er Select bits |                  |                |              |

|                | 1111 <b>= 1:16</b>                     | Postscaler                |                |                |                  |                |              |

|                | 1110 <b>= 1:15</b>                     | 5 Postscaler              |                |                |                  |                |              |

|                | 1101 <b>= 1:14</b>                     | Postscaler                |                |                |                  |                |              |

|                | 1100 <b>= 1:13</b>                     | 8 Postscaler              |                |                |                  |                |              |

|                | 1011 <b>= 1:12</b>                     |                           |                |                |                  |                |              |

|                | 1010 = 1:11                            |                           |                |                |                  |                |              |

|                | 1001 = 1:10                            |                           |                |                |                  |                |              |

|                | 1000 <b>= 1:9</b><br>0111 <b>= 1:8</b> |                           |                |                |                  |                |              |

|                | 0111 <b>- 1.8</b><br>0110 <b>= 1:7</b> |                           |                |                |                  |                |              |

|                | 0110 = 1.7<br>0101 = 1.6               |                           |                |                |                  |                |              |

|                | 0100 = 1:5                             |                           |                |                |                  |                |              |

|                | 0011 = 1:4                             |                           |                |                |                  |                |              |

|                | 0010 <b>= 1</b> :3                     | Postscaler                |                |                |                  |                |              |

|                | 0001 = 1:2                             | Postscaler                |                |                |                  |                |              |

|                | 0000 = 1:1                             | Postscaler                |                |                |                  |                |              |

| bit 2          | TMR2ON: T                              | ïmer2 On bit              |                |                |                  |                |              |

|                | 1 = Timer2                             | is ON                     |                |                |                  |                |              |

|                | 0 = Timer2                             | is OFF                    |                |                |                  |                |              |

| bit 1-0        | T2CKPS<1:                              | <b>0&gt;:</b> Timer2 Cloc | k Prescale Se  | elect bits     |                  |                |              |

|                | 11 = Presca                            | ller is 64                |                |                |                  |                |              |

|                | 10 = Presca                            |                           |                |                |                  |                |              |

|                | 01 = Presca                            |                           |                |                |                  |                |              |

|                | 00 = Presca                            |                           |                |                |                  |                |              |

### REGISTER 19-1: T2CON: TIMER2 CONTROL REGISTER

| FIGURE 21-9:                                      | SPI N                      | IODE W                     | AVEFO                                          | RM (SL                               | AVE MC       | DE WIT            | HCKE                         | = 0)                  |                                                 |                                        |                       |

|---------------------------------------------------|----------------------------|----------------------------|------------------------------------------------|--------------------------------------|--------------|-------------------|------------------------------|-----------------------|-------------------------------------------------|----------------------------------------|-----------------------|

|                                                   |                            |                            |                                                |                                      |              |                   |                              |                       |                                                 |                                        | , yaaana<br>Le        |

| 647%<br>(CESE = 6<br>67%E = 6)                    | ·<br>·<br>·<br>·           |                            |                                                |                                      |              |                   |                              |                       |                                                 |                                        | :<br>:<br>:<br>:<br>: |

|                                                   | •<br>•<br>•<br>•<br>•<br>• |                            |                                                | ·<br>·                               | ,<br>,       |                   | <pre></pre>                  | ·<br>·                | ,<br>,<br>,<br>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                                        | 3<br>                 |

| - Constant Constant<br>Sector Sciences<br>Network | ·<br>·<br>·<br>·           |                            | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | s<br>s<br>s<br>s                     | <<br>        | :<br>:<br>:<br>:  | 5<br>5<br>7<br>8<br>8        | <<br><<br>:<br>:<br>: | <<br><<br>s<br>s<br>s                           | :<br>:<br>:<br>:                       |                       |

| - 8920                                            |                            | V 732.7                    |                                                | X 88.8<br>,<br>,                     | X 333 4      | (198.3<br>/////// | X 333.2.<br>                 | X 222                 |                                                 | . 82 0<br>                             |                       |

| SEN                                               | 4.<br>                     | - 1995, 7<br>- 1995, 7<br> | ,                                              | aad <i>aalaa</i><br>;<br>;<br>;<br>; |              |                   | ,<br>                        |                       |                                                 | (///////////////////////////////////// | :                     |

| <br>- Særepie<br>-                                | ·<br>·<br>·<br>·           | . //p.                     | . //.<br>                                      |                                      | . 49.<br>    | . <i>11</i> 9.    | , <i>Ig</i><br>5<br>6.<br>6. | ; <i>4</i> 2-<br>;    | 5 4<br>3<br>2<br>2                              | ().                                    |                       |

| BSPR<br>Internups<br>Plag                         | ·<br>;<br>;<br>;           |                            | 5<br>5<br>6                                    | 5<br>5<br>2                          |              |                   | 5<br>5<br>6                  | 5<br>5                | <<br><<br>&<br>\$                               | · · · · · · · · · · · · · · · · · · ·  |                       |

| \$\$89\$8 80<br>\$\$\$7607                        | ,<br>,<br>,<br>,           |                            | ,<br>,<br>,<br>,                               | ,<br>;<br>,                          | •<br>\$<br>• |                   | *<br>*<br>*                  | ,<br>,<br>,<br>,      | • ;<br>• ;<br>•                                 | , //p.                                 |                       |

| Write Collision<br>detection active               |                            |                            |                                                |                                      |              |                   |                              |                       |                                                 |                                        |                       |

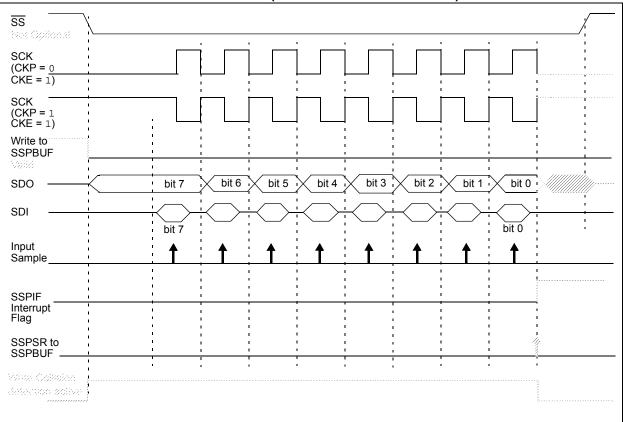

#### FIGURE 21-10: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

#### 21.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high. When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the 8th bit is shifted out (the falling edge of the 8th clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an  $\overline{ACK}$  bit during the 9th bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKSTAT bit on the rising edge of the 9th clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the 9th clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 21-28).

After the write to the SSPBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the 8th clock, the master will release the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the 9th clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPCON2 register. Following the falling edge of the 9th clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 21.6.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPSTAT register is set when the CPU writes to SSPBUF and is cleared when all eight bits are shifted out.

#### 21.6.6.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

WCOL must be cleared by software before the next transmission.

#### 21.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPCON2 register is cleared when the slave has sent an Acknowledge (ACK = 0) and is set when the slave does not Acknowledge (ACK = 1). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

21.6.6.4 Typical transmit sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPCON2 register.

- 2. SSPIF is set by hardware on completion of the Start.

- 3. SSPIF is cleared by software.

- 4. The MSSP module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPBUF with the slave address to transmit.

- 6. Address is shifted out the SDA pin until all 8 bits are transmitted. Transmission begins as soon as SSPBUF is written to.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPCON2 register.

- 8. The MSSP module generates an interrupt at the end of the 9th clock cycle by setting the SSPIF bit.

- 9. The user loads the SSPBUF with eight bits of data.

- 10. Data is shifted out the SDA pin until all eight bits are transmitted.

- 11. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- 13. The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPCON2 register. Interrupt is generated once the Stop/Restart condition is complete.

| RRF              | Rotate Right f through Carry                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                           |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                 |

| Operation:       | See description below                                                                                                                                                                                              |

| Status Affected: | С                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |

|                  | C Register f                                                                                                                                                                                                       |

| SUBLW            | Subtract W                                                                                                                            | / from literal  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|

| Syntax:          | [label] Sl                                                                                                                            | JBLW k          |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                   |                 |  |  |

| Operation:       | $k \operatorname{-}(W) \operatorname{\rightarrow}(W)$                                                                                 | /)              |  |  |

| Status Affected: | C, DC, Z                                                                                                                              |                 |  |  |

| Description:     | The W register is subtracted (2's com-<br>plement method) from the 8-bit literal<br>'k'. The result is placed in the W regis-<br>ter. |                 |  |  |

|                  | C = 0                                                                                                                                 | W > k           |  |  |

|                  | <b>C =</b> 1                                                                                                                          | $W \le k$       |  |  |

|                  | DC = 0                                                                                                                                | W<3:0> > k<3:0> |  |  |

|                  | DC = 1                                                                                                                                | W<3:0> ≤ k<3:0> |  |  |

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |

| Operands:        | None                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT}, \\ 0 \rightarrow \text{WDT prescaler}, \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$                                                |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |

| Description:     | The power-down Status bit, $\overline{\text{PD}}$ is cleared. Time-out Status bit, $\overline{\text{TO}}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into Sleep mode with the oscillator stopped. |

| SUBWF            | Subtract W from f                                                                                                                                                              |                 |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|

| Syntax:          | [label] SU                                                                                                                                                                     | JBWF f,d        |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                              |                 |  |  |  |  |

| Operation:       | (f) - $(W)$ → $(c)$                                                                                                                                                            | lestination)    |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                       |                 |  |  |  |  |

| Description:     | Subtract (2's complement method) W register from register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f. |                 |  |  |  |  |

|                  | <b>C</b> = 0                                                                                                                                                                   | W > f           |  |  |  |  |

|                  | C = 1                                                                                                                                                                          | $W \leq f$      |  |  |  |  |

|                  | DC = 0                                                                                                                                                                         | W<3:0> > f<3:0> |  |  |  |  |

$W<3:0> \le f<3:0>$

| SUBWFB           | Subtract W from f with Borrow                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | SUBWFB f {,d}                                                                                                                                                                                       |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                  |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                                                                                            |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's comple-<br>ment method). If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |

DC = 1

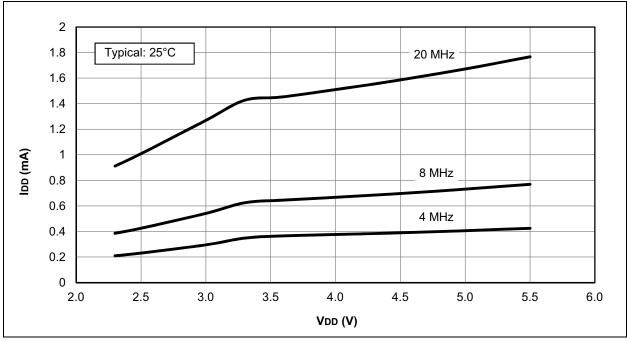

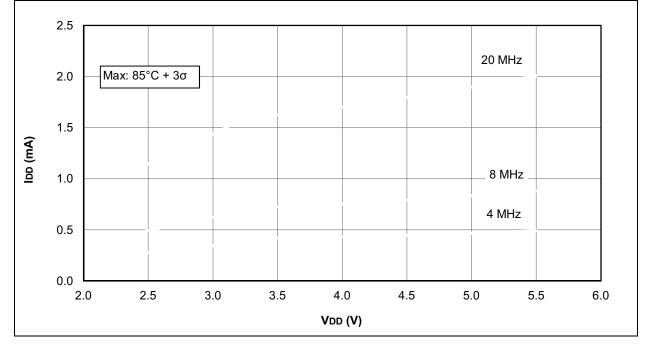

| 25.4 | DC Characteristics: | Supply | Current ( | IDD) |

|------|---------------------|--------|-----------|------|

|------|---------------------|--------|-----------|------|

| PIC16LF1516/7/8/9                         |                 |                         |       |      | ditions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |            |                                                         |  |

|-------------------------------------------|-----------------|-------------------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------|--|

| PIC16F1516/7/8/9                          |                 | Operating temperature - |       |      | itions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended  |            |                                                         |  |

| Param Device                              |                 |                         | Truct |      |                                                                                                                                | Conditions |                                                         |  |

| No.                                       | Characteristics | Min.                    | Тур†  | Max. | Units                                                                                                                          | VDD        | Note                                                    |  |

| Supply Current (IDD) <sup>(1, 2, 3)</sup> |                 |                         |       |      |                                                                                                                                |            |                                                         |  |

| D010                                      |                 | —                       | 8.0   | 14   | μA                                                                                                                             | 1.8        | Fosc = 32 kHz                                           |  |

|                                           |                 | —                       | 12.0  | 31   | μA                                                                                                                             | 3.0        | LP Oscillator<br>-40°C $\leq$ TA $\leq$ +85°C           |  |

| D010                                      |                 |                         | 11    | 28   | μA                                                                                                                             | 2.3        | Fosc = 32 kHz                                           |  |

|                                           |                 | —                       | 13    | 38   | μA                                                                                                                             | 3.0        | LP Oscillator<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ |  |

|                                           |                 | —                       | 14    | 45   | μA                                                                                                                             | 5.0        |                                                         |  |

| D011                                      |                 | —                       | 60    | 95   | μA                                                                                                                             | 1.8        | Fosc = 1 MHz                                            |  |

|                                           |                 | —                       | 110   | 180  | μA                                                                                                                             | 3.0        | XT Oscillator                                           |  |

| D011                                      |                 | _                       | 92    | 170  | μA                                                                                                                             | 2.3        | Fosc = 1 MHz                                            |  |

|                                           |                 | —                       | 140   | 230  | μA                                                                                                                             | 3.0        | XT Oscillator                                           |  |

|                                           |                 | —                       | 170   | 350  | μA                                                                                                                             | 5.0        |                                                         |  |

| D012                                      |                 | —                       | 150   | 240  | μA                                                                                                                             | 1.8        | Fosc = 4 MHz                                            |  |

|                                           |                 | —                       | 260   | 430  | μA                                                                                                                             | 3.0        | XT Oscillator                                           |  |

| D012                                      |                 | —                       | 190   | 450  | μA                                                                                                                             | 2.3        | Fosc = 4 MHz                                            |  |

|                                           |                 | —                       | 310   | 500  | μA                                                                                                                             | 3.0        | XT Oscillator                                           |  |

|                                           |                 | —                       | 370   | 650  | μA                                                                                                                             | 5.0        |                                                         |  |

| D013                                      |                 | —                       | 25    | 31   | μA                                                                                                                             | 1.8        | Fosc = 500 kHz                                          |  |

|                                           |                 | —                       | 35    | 50   | μA                                                                                                                             | 3.0        | EC Oscillator<br>Low-Power mode                         |  |

| D013                                      |                 | -                       | 25    | 40   | μA                                                                                                                             | 2.3        | Fosc = 500 kHz                                          |  |

|                                           |                 | _                       | 35    | 55   | μA                                                                                                                             | 3.0        | EC Oscillator<br>Low-Power mode                         |  |

|                                           |                 | —                       | 40    | 60   | μA                                                                                                                             | 5.0        |                                                         |  |

| D014                                      |                 | _                       | 120   | 210  | μA                                                                                                                             | 1.8        | Fosc = 4 MHz                                            |  |

|                                           |                 | -                       | 210   | 380  | μA                                                                                                                             | 3.0        | EC Oscillator<br>Medium-Power mode                      |  |

| D014                                      |                 | _                       | 160   | 250  | μA                                                                                                                             | 2.3        | Fosc = 4 MHz                                            |  |

|                                           |                 | _                       | 260   | 380  | μA                                                                                                                             | 3.0        | EC Oscillator<br>Medium-Power mode                      |  |

|                                           |                 | —                       | 330   | 480  | μA                                                                                                                             | 5.0        |                                                         |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- 3: 0.1 μF capacitor on VCAP pin, PIC16F1516/7/8/9 only.

- 4: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

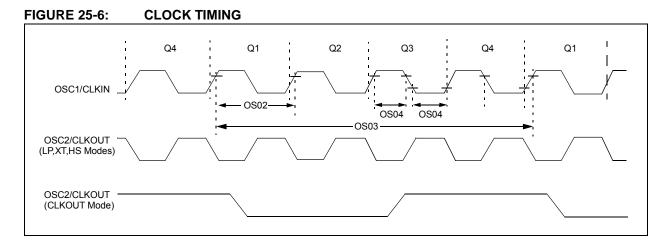

#### 25.10 AC Characteristics

#### TABLE 25-1: CLOCK OSCILLATOR TIMING REQUIREMENTS

|              | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                         |      |        |        |       |                                |

|--------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------|--------|--------|-------|--------------------------------|

| Param<br>No. | Sym.                                                                                                                     | Characteristic                          | Min. | Тур†   | Max.   | Units | Conditions                     |

| OS01         | Fosc                                                                                                                     | External CLKIN Frequency <sup>(1)</sup> | DC   | —      | 0.5    | MHz   | EC Oscillator mode (low)       |

|              |                                                                                                                          |                                         | DC   | _      | 4      | MHz   | EC Oscillator mode (medium)    |

|              |                                                                                                                          |                                         | DC   | _      | 20     | MHz   | EC Oscillator mode (high)      |

|              |                                                                                                                          | Oscillator Frequency <sup>(1)</sup>     | —    | 32.768 | —      | kHz   | LP Oscillator mode             |

|              |                                                                                                                          |                                         | 0.1  | _      | 4      | MHz   | XT Oscillator mode             |

|              |                                                                                                                          |                                         | 1    | _      | 4      | MHz   | HS Oscillator mode             |

|              |                                                                                                                          |                                         | 1    | _      | 20     | MHz   | HS Oscillator mode, VDD > 2.7V |

|              |                                                                                                                          |                                         | DC   | _      | 4      | MHz   | RC Oscillator mode, VDD > 2.0V |

| OS02         | Tosc                                                                                                                     | External CLKIN Period <sup>(1)</sup>    | 27   | _      | ×      | μs    | LP Oscillator mode             |

|              |                                                                                                                          |                                         | 250  | _      | ×      | ns    | XT Oscillator mode             |

|              |                                                                                                                          |                                         | 50   | _      | ×      | ns    | HS Oscillator mode             |

|              |                                                                                                                          |                                         | 50   | _      | ×      | ns    | EC Oscillator mode             |

|              |                                                                                                                          | Oscillator Period <sup>(1)</sup>        | —    | 30.5   | —      | μs    | LP Oscillator mode             |

|              |                                                                                                                          |                                         | 250  | _      | 10,000 | ns    | XT Oscillator mode             |

|              |                                                                                                                          |                                         | 50   | _      | 1,000  | ns    | HS Oscillator mode             |

|              |                                                                                                                          |                                         | 250  | _      | —      | ns    | RC Oscillator mode             |

| OS03         | TCY                                                                                                                      | Instruction Cycle Time <sup>(1)</sup>   | 200  | TCY    | DC     | ns    | Tcy = Fosc/4                   |

| OS04*        | TosH,                                                                                                                    | External CLKIN High,                    | 2    | —      | —      | μS    | LP oscillator                  |

|              | TosL                                                                                                                     | External CLKIN Low                      | 100  | —      | —      | ns    | XT oscillator                  |

|              |                                                                                                                          |                                         | 20   | —      | —      | ns    | HS oscillator                  |

| OS05*        | TosR,                                                                                                                    | External CLKIN Rise,                    | 0    | —      | ×      | ns    | LP oscillator                  |

|              | TosF                                                                                                                     | External CLKIN Fall                     | 0    | —      | ×      | ns    | XT oscillator                  |

|              |                                                                                                                          |                                         | 0    | —      | ×      | ns    | HS oscillator                  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

### 27.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 27.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 27.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 27.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

### 27.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC<sup>®</sup> MCUs and dsPIC<sup>®</sup> DSCs, KEELOQ<sup>®</sup> code hopping devices; Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2010-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0681-5