Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1518-e-ml |

FIGURE 3-9: **INDIRECT ADDRESSING** 0x0000 0x0000 **Traditional Data Memory** 0x0FFF 0x0FFF 0x1000 Reserved 0x1FFF 0x2000 Linear **Data Memory** 0x29AF 0x29B0 Reserved **FSR** 0x7FFF Address 0x8000 Range 0x0000 **Program** Flash Memory 0xFFFF 0x7FFF Note: Not all memory regions are completely implemented. Consult device memory tables for memory limits.

TABLE 6-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0  | Register on Page |

|--------|--------|--------|-------|-------|--------|-------|-------|--------|------------------|

| BORCON | SBOREN | BORFS  | -     | _     | _      | _     | _     | BORRDY | 63               |

| PCON   | STKOVF | STKUNF |       | RWDT  | RMCLR  | RI    | POR   | BOR    | 67               |

| STATUS | _      | _      | _     | TO    | PD     | Z     | DC    | С      | 21               |

| WDTCON | _      | _      |       | V     | SWDTEN | 86    |       |        |                  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by Resets.

**Note 1:** Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

#### REGISTER 7-5: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| R/W-0/0 | U-0 | U-0 | U-0 | R/W-0/0 | U-0 | U-0 | R/W-0/0 |

|---------|-----|-----|-----|---------|-----|-----|---------|

| OSFIF   | _   | _   | _   | BCLIF   | _   | _   | CCP2IF  |

| bit 7   |     |     |     |         |     |     | bit 0   |

Legend:

bit 2-1

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 OSFIF: Oscillator Fail Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

bit 6-4 **Unimplemented:** Read as '0'

bit 3 BCLIF: MSSP Bus Collision Interrupt Flag bit

1 = Interrupt is pending 0 = Interrupt is not pending Unimplemented: Read as '0'

bit 0 **CCP2IF:** CCP2 Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

**Note:** Interrupt flag bits are set when an interrupt

condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior

to enabling an interrupt.

#### TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1   | Bit 0  | Register on Page |

|------------|---------|--------|--------|--------|-------|--------|---------|--------|------------------|

| INTCON     | GIE     | PEIE   | TMR0IE | INTE   | IOCIE | TMR0IF | INTF    | IOCIF  | 74               |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA   |        | PS<2:0> |        | 146              |

| PIE1       | TMR1GIE | ADIE   | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE  | TMR1IE | 75               |

| PIE2       | OSFIE   | _      | _      | _      | BCLIE | _      | _       | CCP2IE | 76               |

| PIR1       | TMR1GIF | ADIF   | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF  | TMR1IF | 77               |

| PIR2       | OSFIF   | _      | _      | _      | BCLIF | _      | 1       | CCP2IF | 78               |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used by Interrupts.

#### TABLE 10-3: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0  | Register on Page |

|--------|-------|-------|-------|-------|------------|-------|-------|--------|------------------|

| OSCCON | _     |       | IRCF  | <3:0> |            | _     | SCS   | 59     |                  |

| STATUS | _     | _     | _     | TO    | PD         | Z     | DC    | С      | 21               |

| WDTCON | _     | _     |       |       | WDTPS<4:0> |       |       | SWDTEN | 86               |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

#### TABLE 10-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2   | Bit 9/1 | Bit 8/0 | Register on Page |

|---------|------|---------|---------|----------|----------|----------|------------|---------|---------|------------------|

| CONFICA | 13:8 |         |         | FCMEN    | IESO     | CLKOUTEN | BOREN<1:0> |         | _       | 40               |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | E<1:0>   | FOSC<2:0>  |         |         | 42               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

#### 15.4 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait at least 200  $\mu s$  after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu s$  between sequential conversions of the temperature indicator output.

#### TABLE 15-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register on page |

|--------|-------|--------|-------|-------|-------|-------|-------|--------|------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | _     | _     | ADFVI | R<1:0> | 128              |

Legend: Shaded cells are unused by the temperature indicator module.

#### 16.3 **Register Definitions: ADC Control**

#### REGISTER 16-1: ADCON0: ADC CONTROL REGISTER 0

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|----------|---------|---------|---------|---------|

| _     |         |         | CHS<4:0> |         |         | GO/DONE | ADON    |

| bit 7 |         |         |          |         |         |         | bit 0   |

Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n/n = Value at POR and BOR/Value at all other Resets u = Bit is unchanged x = Bit is unknown'1' = Bit is set '0' = Bit is cleared

bit 7 Unimplemented: Read as '0' CHS<4:0>: Analog Channel Select bits bit 6-2 11111 = FVR (Fixed Voltage Reference) Buffer 1 Output(1) 11110 = Temperature Indicator<sup>(2)</sup>. 11101 = Reserved. No channel connected. 11100 = Reserved. No channel connected.  $11011 = AN27^{(3)}$  $10100 = AN20^{(3)}$ 10011 = AN19 10010 = AN18 10001 = AN17 10000 = AN1601111 = AN1501110 = AN1401101 = AN13 01100 = AN12 01011 = AN11 01010 = AN1001001 = AN901000 = AN8 $00111 = AN7^{(3)}$  $00110 = AN6^{(3)}$  $00101 = AN5^{(3)}$ 00100 = AN400011 = AN300010 = AN2 00001 = AN1 00000 = AN0GO/DONE: ADC Conversion Status bit bit 1 1 = ADC conversion cycle in progress. Setting this bit starts an ADC conversion cycle. This bit is automatically cleared by hardware when the ADC conversion has completed. 0 = ADC conversion completed/not in progress bit 0 ADON: ADC Enable bit 1 = ADC is enabled

0 = ADC is disabled and consumes no operating current

Note 1: See Section 14.0 "Fixed Voltage Reference (FVR)" for more information.

See Section 15.0 "Temperature Indicator Module" for more information.

3: AN<7:5> and AN<27:20> are PIC16(L)F1517/9 only.

#### REGISTER 16-2: ADCON1: ADC CONTROL REGISTER 1

| R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-----------|---------|-----|-----|---------|---------|

| ADFM    |         | ADCS<2:0> |         | _   | _   | ADPRE   | F<1:0>  |

| bit 7   |         |           |         |     |     |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 ADFM: ADC Result Format Select bit

- 1 = Right justified. Six Most Significant bits of ADRESH are set to '0' when the conversion result is loaded.

- 0 = Left justified. Six Least Significant bits of ADRESL are set to '0' when the conversion result is loaded.

- bit 6-4 ADCS<2:0>: ADC Conversion Clock Select bits

000 = Fosc/2

001 = Fosc/8

010 = Fosc/32

011 = FRC (clock supplied from a dedicated FRC oscillator)

100 = Fosc/4

101 = Fosc/16

110 = Fosc/64

111 = FRC (clock supplied from a dedicated FRC oscillator)

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 ADPREF<1:0>: ADC Positive Voltage Reference Configuration bits

00 = VREF is connected to VDD

01 = Reserved

10 = VREF is connected to external VREF+ pin<sup>(1)</sup>

11 = VREF is connected to internal Fixed Voltage Reference (FVR) module<sup>(1)</sup>

**Note 1:** When selecting the FVR or the VREF+ pin as the source of the positive reference, be aware that a minimum voltage specification exists. See **Section 25.0 "Electrical Specifications"** for details.

#### 18.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, the user must set these bits:

- · TMR1ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- PEIE bit of the INTCON register

- · GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

#### 18.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- · PEIE bit of the INTCON register must be set

- T1SYNC bit of the T1CON register must be set

- TMR1CS bits of the T1CON register must be configured

- T1OSCEN bit of the T1CON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

Timer1 secondary oscillator will continue to operate in Sleep regardless of the  $\overline{\text{T1SYNC}}$  bit setting.

#### 18.9 CCP Capture/Compare Time Base

The CCP modules use the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

For more information, see Section 20.0 "Capture/Compare/PWM Modules".

#### 18.10 CCP Special Event Trigger

When the CCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair becomes the period register for Timer1.

Timer1 should be synchronized and Fosc/4 should be selected as the clock source in order to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the CCP, the write will take precedence.

For more information, see **Section 16.2.5 "Special Event Trigger"**.

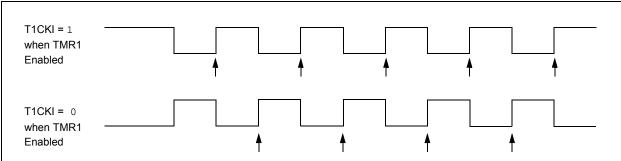

Note 1: Arrows indicate counter increments.

2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

#### 21.2.4 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit of the SSPCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCK pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

#### 21.2.4.1 Daisy-Chain Configuration

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 21-7 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPCON3 register will enable writes to the SSPBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

### 21.2.5 SLAVE SELECT SYNCHRONIZATION

The Slave Select can also be used to synchronize communication. The Slave Select line is held high until the master device is ready to communicate. When the Slave Select line is pulled low, the slave knows that a new transmission is starting.

If the slave fails to receive the communication properly, it will be reset at the end of the transmission, when the Slave Select line returns to a high state. The slave is then ready to receive a new transmission when the Slave Select line is pulled low again. If the Slave Select line is not used, there is a risk that the slave will eventually become out of sync with the master. If the slave misses a bit, it will always be one bit off in future transmissions. Use of the Slave Select line allows the slave and master to align themselves at the beginning of each transmission.

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 0100).

When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven.

When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

- Note 1: When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 0100), the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

- 2: When the SPI is used in Slave mode with CKE set; the user must enable SS pin control.

- **3:** While operated in SPI Slave mode the SMP bit of the SSPSTAT register must remain clear.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

#### 21.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCL line low effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCL.

The CKP bit of the SSPCON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. Setting CKP will release SCL and allow more communication.

#### 21.5.6.1 Normal Clock Stretching

Following an  $\overline{ACK}$  if the R/W bit of SSPSTAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSPBUF with data to transfer to the master. If the SEN bit of SSPCON2 is set, the slave hardware will always stretch the clock after the  $\overline{ACK}$  sequence. Once the slave is ready; CKP is set by software and communication resumes.

- Note 1: The BF bit has no effect on if the clock will be stretched or not. This is different than previous versions of the module that would not stretch the clock, clear CKP, if SSPBUF was read before the 9th falling edge of SCL.

- 2: Previous versions of the module did not stretch the clock for a transmission if SSP-BUF was loaded before the 9th falling edge of SCL. It is now always cleared for read requests.

#### 21.5.6.2 10-bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set the clock is always stretched. This is the only time the SCL is stretched without CKP being cleared. SCL is released immediately after a write to SSPADD.

**Note:** Previous versions of the module did not stretch the clock if the second address byte did not match.

#### 21.5.6.3 Byte NACKing

When AHEN bit of SSPCON3 is set; CKP is cleared by hardware after the 8th falling edge of SCL for a received matching address byte. When DHEN bit of SSPCON3 is set; CKP is cleared after the 8th falling edge of SCL for received data.

Stretching after the 8th falling edge of SCL allows the slave to look at the received address or data and decide if it wants to ACK the received data.

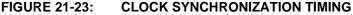

### 21.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external I<sup>2</sup>C master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the I<sup>2</sup>C bus have released SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 21-23).

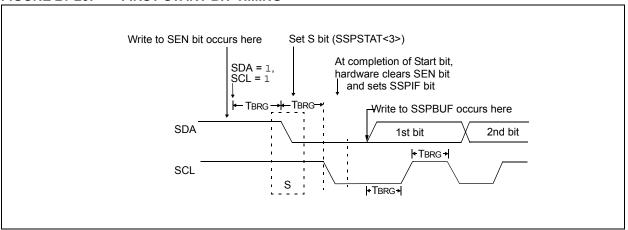

### 21.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition (Figure 21-26), the user sets the Start Enable bit, SEN bit of the SSPCON2 register. If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<7:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit of the SSPSTAT register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPCON2 register will be automatically cleared by hardware; the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

- Note 1: If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

- 2: The Philips I<sup>2</sup>C Specification states that a bus collision cannot occur on a Start.

#### FIGURE 21-26: FIRST START BIT TIMING

# 22.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate.

The Auto-Baud Detect feature (see Section 22.4.1, Auto-Baud Detect) can be used to compensate for changes in the INTOSC frequency.

There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

TABLE 22-4: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

| BAUD   | Fos            | c = 8.000  | ) MHz                       | Fosc = 4.000 MHz |            |                             | Fosc           | = 3.686    | 4 MHz                       | Fosc = 1.000 MHz |            |                             |

|--------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _              | _          | _                           | _                | _          | _                           | _              | _          | _                           | 300              | 0.16       | 207                         |

| 1200   | _              | _          | _                           | 1202             | 0.16       | 207                         | 1200           | 0.00       | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404           | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400           | 0.00       | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615           | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600           | 0.00       | 23                          | _                | _          | _                           |

| 10417  | 10417          | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473          | 0.53       | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19231          | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.2k          | 0.00       | 11                          | _                | _          | _                           |

| 57.6k  | 55556          | -3.55      | 8                           | _                | _          | _                           | 57.60k         | 0.00       | 3                           | _                | _          | _                           |

| 115.2k | _              | _          | _                           | _                | _          | _                           | 115.2k         | 0.00       | 1                           | _                | _          | _                           |

|        |                | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                |            |                             |                |            |                             |                    |            |                             |  |  |  |

|--------|----------------|-------------------------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|--|--|

| BAUD   | Fosc           | = 20.00                       | 0 MHz                       | Fosc           | = 18.43    | 2 MHz                       | Fosc           | = 16.00    | 0 MHz                       | Fosc = 11.0592 MHz |            |                             |  |  |  |

| RATE   | Actual<br>Rate | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 300    | 300.0          | -0.01                         | 4166                        | 300.0          | 0.00       | 3839                        | 300.03         | 0.01       | 3332                        | 300.0              | 0.00       | 2303                        |  |  |  |

| 1200   | 1200           | -0.03                         | 1041                        | 1200           | 0.00       | 959                         | 1200.5         | 0.04       | 832                         | 1200               | 0.00       | 575                         |  |  |  |

| 2400   | 2399           | -0.03                         | 520                         | 2400           | 0.00       | 479                         | 2398           | -0.08      | 416                         | 2400               | 0.00       | 287                         |  |  |  |

| 9600   | 9615           | 0.16                          | 129                         | 9600           | 0.00       | 119                         | 9615           | 0.16       | 103                         | 9600               | 0.00       | 71                          |  |  |  |

| 10417  | 10417          | 0.00                          | 119                         | 10378          | -0.37      | 110                         | 10417          | 0.00       | 95                          | 10473              | 0.53       | 65                          |  |  |  |

| 19.2k  | 19.23k         | 0.16                          | 64                          | 19.20k         | 0.00       | 59                          | 19.23k         | 0.16       | 51                          | 19.20k             | 0.00       | 35                          |  |  |  |

| 57.6k  | 56.818         | -1.36                         | 21                          | 57.60k         | 0.00       | 19                          | 58.82k         | 2.12       | 16                          | 57.60k             | 0.00       | 11                          |  |  |  |

| 115.2k | 113.636        | -1.36                         | 10                          | 115.2k         | 0.00       | 9                           | 111.11k        | -3.55      | 8                           | 115.2k             | 0.00       | 5                           |  |  |  |

|        |                             | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                  |            |                             |                |            |                             |                  |            |                             |  |  |  |

|--------|-----------------------------|-------------------------------|-----------------------------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|--|--|--|

| BAUD   | Fos                         | c = 8.000                     | ) MHz                       | Fosc = 4.000 MHz |            |                             | Fosc           | = 3.686    | 4 MHz                       | Fosc = 1.000 MHz |            |                             |  |  |  |

| RATE   | RATE Actual %<br>Rate Error |                               | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 300    | 299.9                       | -0.02                         | 1666                        | 300.1            | 0.04       | 832                         | 300.0          | 0.00       | 767                         | 300.5            | 0.16       | 207                         |  |  |  |

| 1200   | 1199                        | -0.08                         | 416                         | 1202             | 0.16       | 207                         | 1200           | 0.00       | 191                         | 1202             | 0.16       | 51                          |  |  |  |

| 2400   | 2404                        | 0.16                          | 207                         | 2404             | 0.16       | 103                         | 2400           | 0.00       | 95                          | 2404             | 0.16       | 25                          |  |  |  |

| 9600   | 9615                        | 0.16                          | 51                          | 9615             | 0.16       | 25                          | 9600           | 0.00       | 23                          | _                | _          | _                           |  |  |  |

| 10417  | 10417                       | 0.00                          | 47                          | 10417            | 0.00       | 23                          | 10473          | 0.53       | 21                          | 10417            | 0.00       | 5                           |  |  |  |

| 19.2k  | 19.23k                      | 0.16                          | 25                          | 19.23k           | 0.16       | 12                          | 19.20k         | 0.00       | 11                          | _                | _          | _                           |  |  |  |

| 57.6k  | 55556                       | -3.55                         | 8                           | _                | _          | _                           | 57.60k         | 0.00       | 3                           | _                | _          | _                           |  |  |  |

| 115.2k | _                           | _                             | _                           | _                | _          | _                           | 115.2k         | 0.00       | 1                           | _                | _          | _                           |  |  |  |

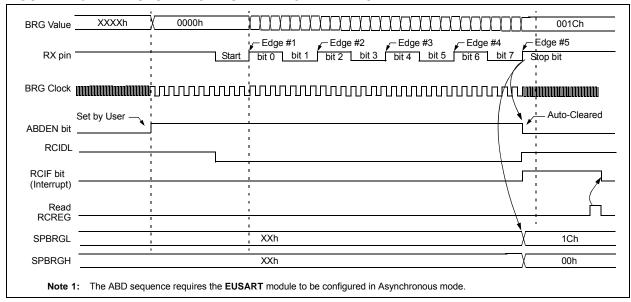

#### 22.4.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCON register starts the auto-baud calibration sequence (Figure 22-6). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Table. The fifth rising edge will occur on the RX pin at the end of the 8th bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRGL register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRGL register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table . During ABD, both the SPBRGH and SPBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH

and SPBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 22.4.3 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRGL register pair.

TABLE 22-5: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

Note:

During the ABD sequence, SPBRGL and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

FIGURE 22-6: AUTOMATIC BAUD RATE CALIBRATION

#### TABLE 25-7: ANALOG-TO-DIGITAL CONVERTER (ADC) CHARACTERISTICS:(1,2,3)

|              | Standard Operating Conditions (unless otherwise stated)  Operating temperature Tested at +25°C |                                                   |      |      |      |       |                                                                     |  |  |  |

|--------------|------------------------------------------------------------------------------------------------|---------------------------------------------------|------|------|------|-------|---------------------------------------------------------------------|--|--|--|

| Param<br>No. | Sym.                                                                                           | Characteristic                                    | Min. | Typ† | Max. | Units | Conditions                                                          |  |  |  |

| AD01         | NR                                                                                             | Resolution                                        | _    | _    | 10   | bit   |                                                                     |  |  |  |

| AD02         | EIL                                                                                            | Integral Error                                    | _    | ±1   | ±1.7 | LSb   | VREF = 3.0V                                                         |  |  |  |

| AD03         | EDL                                                                                            | Differential Error                                | _    | ±1   | ±1   | LSb   | No missing codes<br>VREF = 3.0V                                     |  |  |  |

| AD04         | Eoff                                                                                           | Offset Error                                      | _    | ±1   | ±2.5 | LSb   | VREF = 3.0V                                                         |  |  |  |

| AD05         | Egn                                                                                            | Gain Error                                        | _    | ±1   | ±2.0 | LSb   | VREF = 3.0V                                                         |  |  |  |

| AD06         | VREF                                                                                           | Reference Voltage <sup>(4)</sup>                  | 1.8  | _    | VDD  | V     | VREF = (VREF+ minus VREF-)                                          |  |  |  |

| AD07         | VAIN                                                                                           | Full-Scale Range                                  | Vss  | _    | VREF | V     |                                                                     |  |  |  |

| AD08         | ZAIN                                                                                           | Recommended Impedance of<br>Analog Voltage Source | _    | _    | 10   | kΩ    | Can go higher if external 0.01μF capacitor is present on input pin. |  |  |  |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: Total Absolute Error includes integral, differential, offset and gain errors.

- 2: The ADC conversion result never decreases with an increase in the input voltage and has no missing codes.

- 3: ADC VREF is from external VREF, VDD pin or FVR, whichever is selected as reference input.

- 4: ADC Reference Voltage (Ref+) is the selected reference input, VREF+ pin, VDD pin or the FVR selected as the reference input, the FVR Buffer1 output selection must be 2.048V or 4.096V, (ADFVR<1:0> = 1x).

#### **TABLE 25-8: ADC CONVERSION REQUIREMENTS**

| Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ |      |                                                                 |      |                                            |      |       |                                         |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------|------|--------------------------------------------|------|-------|-----------------------------------------|--|--|

| Param<br>No.                                                                                                                                  | Sym. | Characteristic                                                  | Min. | Тур†                                       | Max. | Units | Conditions                              |  |  |

| AD130*                                                                                                                                        | TAD  | ADC Clock Period                                                | 1.0  | _                                          | 9.0  | μS    | Fosc-based                              |  |  |

|                                                                                                                                               |      | FRC Oscillator Period                                           | 1.0  | 2.5                                        | 6.0  | μS    | ADCS<1:0> = 11<br>(FRC Oscillator mode) |  |  |

| AD131                                                                                                                                         | TCNV | Conversion Time (not including Acquisition Time) <sup>(1)</sup> | _    | 11                                         | _    | TAD   | Set GO/DONE bit to conversion complete  |  |  |

| AD132*                                                                                                                                        | TACQ | Acquisition Time                                                | _    | 5.0                                        | _    | μS    |                                         |  |  |

| AD133*                                                                                                                                        | THCD | Holding Capacitor Disconnect                                    | _    | 0.5*TAD + 40 ns<br>(0.5*TAD + 40 ns)<br>to | _    |       | ADCS<2:0> = X11 (Fosc-based)            |  |  |

|                                                                                                                                               |      |                                                                 | _    | (0.5*TAD + 40 ns)                          | _    |       | ADCS<2:0> = X11 (ADC FRC mode)          |  |  |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The ADRES register may be read on the following TcY cycle.

#### TABLE 25-9: LOW DROPOUT (LDO) REGULATOR CHARACTERISTICS

| Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ |                                                              |                        |   |     |   |   |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------|---|-----|---|---|--|--|--|

| Param<br>No.                                                                                                                               | Sym   Characteristic   Min   Lynt   May   Units   Conditions |                        |   |     |   |   |  |  |  |

| LDO01                                                                                                                                      |                                                              | LDO Regulation Voltage | _ | 3.0 | _ | V |  |  |  |

| LDO02                                                                                                                                      | LDO02 LDO External Capacitor 0.1 — 1 μF                      |                        |   |     |   |   |  |  |  |

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

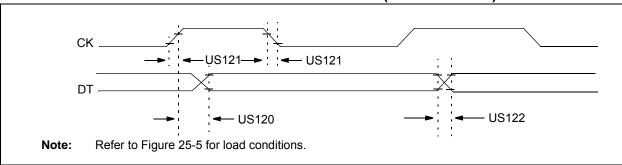

#### FIGURE 25-14: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 25-10: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)  Operating Temperature $-40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C}$ |                                               |                                   |          |      |       |            |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------|----------|------|-------|------------|--|--|--|--|

| Param.<br>No.                                                                                                                                 | Symbol                                        | Characteristic                    | Min.     | Max. | Units | Conditions |  |  |  |  |

| US120                                                                                                                                         | S120 TCKH2DTV SYNC XMIT (Master and Slave)    | 3.0-5.5V                          | _        | 80   | ns    |            |  |  |  |  |

|                                                                                                                                               |                                               | Clock high to data-out valid      | 1.8-5.5V | _    | 100   | ns         |  |  |  |  |

| US121                                                                                                                                         | US121 TCKRF Clock out rise time and fall time | Clock out rise time and fall time | 3.0-5.5V | _    | 45    | ns         |  |  |  |  |

|                                                                                                                                               |                                               | (Master mode)                     | 1.8-5.5V | _    | 50    | ns         |  |  |  |  |

| US122                                                                                                                                         | JS122 TDTRF Data-out rise time and fall time  |                                   | 3.0-5.5V | _    | 45    | ns         |  |  |  |  |

|                                                                                                                                               |                                               |                                   | 1.8-5.5V | _    | 50    | ns         |  |  |  |  |

**TABLE 25-12: SPI MODE REQUIREMENTS**

| Param<br>No. | Symbol                     | Characteristic                            | Min.      | Тур†           | Max. | Unit<br>s | Conditions |  |

|--------------|----------------------------|-------------------------------------------|-----------|----------------|------|-----------|------------|--|

| SP70*        | TssL2scH,<br>TssL2scL      | SSx ↓ to SCKx ↓ or SCKx ↑ input           | 2.25 TcY  | _              | _    | ns        |            |  |

| SP71*        | TscH                       | SCKx input high time (Slave mo            | Tcy + 20  | _              | _    | ns        |            |  |

| SP72*        | TscL                       | SCKx input low time (Slave mod            | e)        | Tcy + 20       | _    | _         | ns         |  |

| SP73*        | TDIV2scH,<br>TDIV2scL      | Setup time of SDIx data input to          | SCKx edge | 100            | _    | _         | ns         |  |

| SP74*        | TSCH2DIL,<br>TSCL2DIL      | Hold time of SDIx data input to S         | SCKx edge | 100            | _    | _         | ns         |  |

| SP75*        | TDOR                       | SDO data output rise time 3.0-5.5         |           | _              | 10   | 25        | ns         |  |

|              |                            |                                           | 1.8-5.5V  | _              | 25   | 50        | ns         |  |

| SP76*        | TDOF                       | SDOx data output fall time                |           | _              | 10   | 25        | ns         |  |

| SP77*        | TssH2DoZ                   | SSx <sup>↑</sup> to SDOx output high-impe | dance     | 10             | _    | 50        | ns         |  |

| SP78*        | TscR SCKx output rise time |                                           | 3.0-5.5V  | _              | 10   | 25        | ns         |  |

|              |                            | (Master mode)                             | 1.8-5.5V  | _              | 25   | 50        | ns         |  |

| SP79*        | TscF                       | SCKx output fall time (Master me          | ode)      | _              | 10   | 25        | ns         |  |

| SP80*        | TscH2DoV,                  | SDOx data output valid after              | 3.0-5.5V  | _              | _    | 50        | ns         |  |

|              | TscL2doV                   | SCKx edge                                 | 1.8-5.5V  | _              | _    | 145       | ns         |  |

| SP81*        | TDOV2scH                   | SDOx data output setup to SCKx edge       |           | Tcy            | _    | _         | ns         |  |

|              | ,<br>TDOV2scL              |                                           |           |                |      |           |            |  |

| SP82*        | TssL2DoV                   | SDOx data output valid after SS           | _         | _              | 50   | ns        |            |  |

| SP83*        | TscH2ssH,<br>TscL2ssH      | SSx ↑ after SCKx edge                     |           | 1.5Tcy +<br>40 | _    | _         | ns         |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

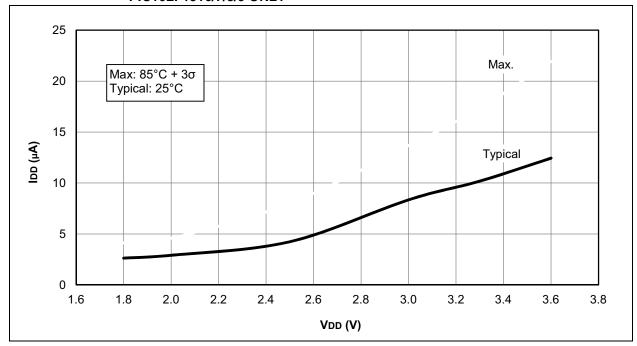

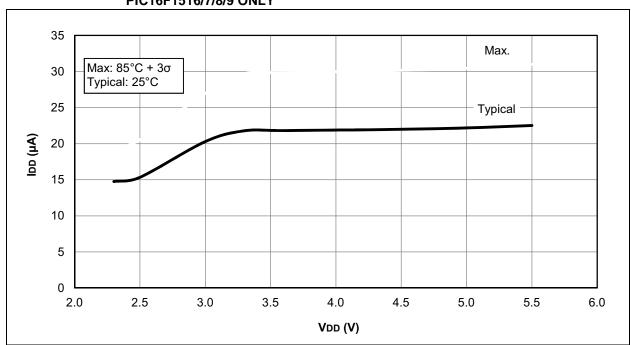

FIGURE 26-7: IDD, EC OSCILLATOR, LOW-POWER MODE, FOSC = 32 kHz, PIC16LF1516/7/8/9 ONLY

FIGURE 26-8: IDD, EC OSCILLATOR, LOW-POWER MODE, FOSC = 32 kHz, PIC16F1516/7/8/9 ONLY

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- · Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### **Trademarks**

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2010-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0681-5