#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

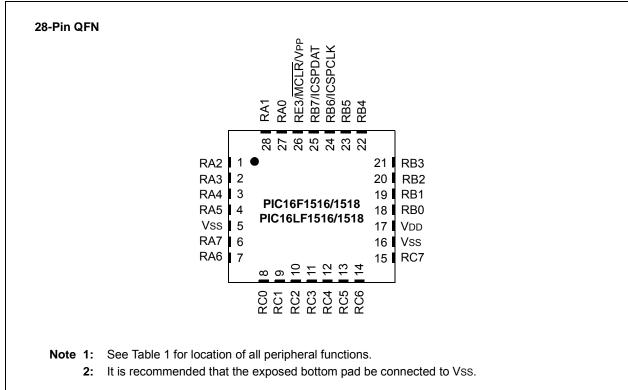

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

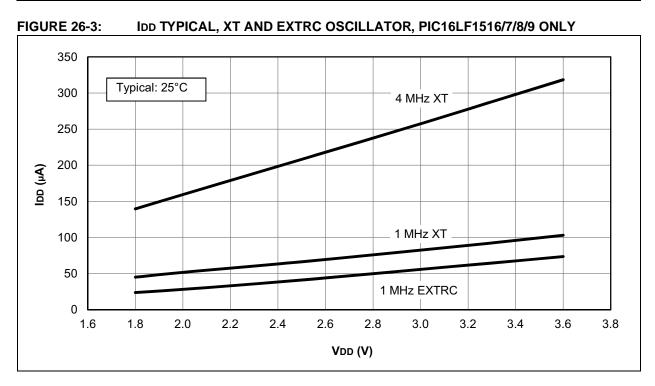

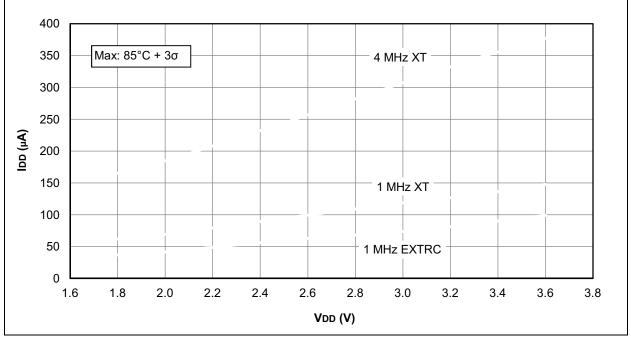

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1518-e-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                     | Function   | Input<br>Type  | Output<br>Type | Description                           |  |  |  |

|--------------------------|------------|----------------|----------------|---------------------------------------|--|--|--|

| RD7 <sup>(3)</sup> /AN27 | RD7        | ST             | CMOS           | General purpose I/O.                  |  |  |  |

|                          | AN27       | AN             | _              | ADC Channel 27 input.                 |  |  |  |

| RE0 <sup>(3)</sup> /AN5  | RE0        | ST             | CMOS           | General purpose I/O.                  |  |  |  |

|                          | AN5        | AN             | _              | ADC Channel 5 input.                  |  |  |  |

| RE1 <sup>(3)</sup> /AN6  | RE1        | ST             | CMOS           | General purpose I/O.                  |  |  |  |

|                          | AN6        | AN             | _              | ADC Channel 6 input.                  |  |  |  |

| RE2 <sup>(3)</sup> /AN7  | RE2        | ST             | CMOS           | General purpose I/O.                  |  |  |  |

|                          | AN7        | AN             | _              | ADC Channel 7 input.                  |  |  |  |

| RE3/MCLR/VPP             | RE3        | ST             | _              | General purpose input with WPU.       |  |  |  |

|                          | MCLR       | ST             | _              | Master Clear with internal pull-up.   |  |  |  |

|                          | VPP        | HV             | _              | Programming voltage.                  |  |  |  |

| VDD                      | Vdd        | Power          | _              | Positive supply.                      |  |  |  |

| Vss                      | Vss        | Power          |                | Ground reference.                     |  |  |  |

|                          | Vdd<br>Vss | Power<br>Power |                | Positive supply.<br>Ground reference. |  |  |  |

#### **TABLE 1-2: PINOUT DESCRIPTION (CONTINUED)**

= Open-Drain

Legend: AN = Analog input or output

CMOS = CMOS compatible input or output

OD

TTL = TTL compatible input

ST

= Schmitt Trigger input with CMOS levels

I<sup>2</sup>C

= Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal levels

Note 1: Peripheral pin location selected using APFCON register (Register 12-1). Default location.

2: Peripheral pin location selected using APFCON register (Register 12-1). Alternate location.

3: PORTD and RE<2:0> available on PIC16(L)F1517/9 only.

#### 3.3 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-3):

- 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.7** "Indirect Addressing" for more information.

Data Memory uses a 12-bit address. The upper five bits of the address define the Bank address, and the lower seven bits select the individual SFR, GPR and common RAM locations in that bank.

#### 3.3.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-7.

| TABLE 3-2: CORE REGISTERS | TABLE 3-2: | CORE REGISTERS |

|---------------------------|------------|----------------|

|---------------------------|------------|----------------|

| Addresses    | BANKx  |

|--------------|--------|

| x00h or x80h | INDF0  |

| x01h or x81h | INDF1  |

| x02h or x82h | PCL    |

| x03h or x83h | STATUS |

| x04h or x84h | FSR0L  |

| x05h or x85h | FSR0H  |

| x06h or x86h | FSR1L  |

| x07h or x87h | FSR1H  |

| x08h or x88h | BSR    |

| x09h or x89h | WREG   |

| x0Ah or x8Ah | PCLATH |

| x0Bh or x8Bh | INTCON |

### 5.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Words

- Secondary oscillator 32 kHz crystal

- Internal Oscillator Block (INTOSC)

#### 5.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by value of the FOSC<2:0> bits in the Configuration Words.

- When the SCS bits of the OSCCON register = 01, the system clock source is the secondary oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

- Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bits of the OSCCON register. The user can monitor the OSTS bit of the OSCSTAT register to determine the current system clock source.

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 5-1.

#### 5.3.2 OSCILLATOR START-UP TIMER STATUS (OSTS) BIT

The Oscillator Start-up Timer Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes. The OSTS does not reflect the status of the secondary oscillator.

#### 5.3.3 SECONDARY OSCILLATOR

The secondary oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the SOSCO and SOSCI device pins.

The secondary oscillator is enabled using the T1OSCEN control bit in the T1CON register. See **Section 18.0 "Timer1 Module with Gate Control"** for more information about the Timer1 peripheral.

#### 5.3.4 SECONDARY OSCILLATOR READY (SOSCR) BIT

The user must ensure that the secondary oscillator is ready to be used before it is selected as a system clock source. The Secondary Oscillator Ready (SOSCR) bit of the OSCSTAT register indicates whether the secondary oscillator is ready to be used. After the SOSCR bit is set, the SCS bits can be configured to select the secondary oscillator.

| R/W-0/       | 0 R/W-0/0                  | R-0/0                                    | R-0/0           | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|--------------|----------------------------|------------------------------------------|-----------------|----------------|------------------|------------------|--------------|

| TMR1G        | IF ADIF                    | RCIF                                     | TXIF            | SSPIF          | CCP1IF           | TMR2IF           | TMR1IF       |

| bit 7        | ·                          |                                          | •               | ÷              | ·                | •                | bit C        |

|              |                            |                                          |                 |                |                  |                  |              |

| Legend:      | - <b>b</b> 1 - <b>b</b> :4 |                                          | L.14            |                |                  |                  |              |

| R = Reada    |                            | W = Writable                             |                 |                | mented bit, read |                  |              |

|              | inchanged                  | x = Bit is unk                           |                 | -n/n = value   | at POR and BO    | R/value at all c | other Resets |

| '1' = Bit is | set                        | '0' = Bit is cle                         | ared            |                |                  |                  |              |

| bit 7        | TMR1GIF:                   | : Timer1 Gate Inte                       | errupt Flag bit |                |                  |                  |              |

|              |                            | pt is pending                            |                 |                |                  |                  |              |

|              | 0 = Interru                | pt is not pending                        |                 |                |                  |                  |              |

| bit 6        |                            | C Interrupt Flag b                       | it              |                |                  |                  |              |

|              |                            | pt is pending                            |                 |                |                  |                  |              |

| L:1 F        |                            | pt is not pending                        |                 |                |                  |                  |              |

| bit 5        |                            | ART Receive Inte                         | rrupt Flag bit  |                |                  |                  |              |

|              |                            | pt is pending<br>pt is not pending       |                 |                |                  |                  |              |

| bit 4        |                            | RT Transmit Inte                         | rrupt Flag bit  |                |                  |                  |              |

|              |                            | pt is pending                            |                 |                |                  |                  |              |

|              | 0 = Interru                | pt is not pending                        |                 |                |                  |                  |              |

| bit 3        | SSPIF: Sy                  | nchronous Serial                         | Port (MSSP)     | Interrupt Flag | oit              |                  |              |

|              |                            | pt is pending                            |                 |                |                  |                  |              |

|              |                            | pt is not pending                        |                 |                |                  |                  |              |

| bit 2        |                            | CP1 Interrupt Fla                        | ag bit          |                |                  |                  |              |

|              |                            | pt is pending<br>pt is not pending       |                 |                |                  |                  |              |

| bit 1        |                            | Timer2 to PR2 Inte                       | errupt Flag bit |                |                  |                  |              |

|              |                            | pt is pending                            |                 |                |                  |                  |              |

|              |                            | pt is not pending                        |                 |                |                  |                  |              |

| bit 0        | TMR1IF: 7                  | imer1 Overflow I                         | nterrupt Flag I | bit            |                  |                  |              |

|              |                            | pt is pending                            |                 |                |                  |                  |              |

|              | 0 = Interru                | pt is not pending                        |                 |                |                  |                  |              |

| Note:        | Interrupt flag bit         | s are set when ar                        | n interrupt     |                |                  |                  |              |

|              |                            | s, regardless of th                      |                 |                |                  |                  |              |

|              |                            | ng enable bit or the<br>E, of the INTCON |                 |                |                  |                  |              |

|              | User software              |                                          | •               |                |                  |                  |              |

|              |                            | rrupt flag bits are o                    |                 |                |                  |                  |              |

|              | to enabling an i           | nterrupt.                                |                 |                |                  |                  |              |

#### REGISTER 7-4: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-x/u                                                              | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |

|----------------------------------------------------------------------|---------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|

| LATA7                                                                | LATA6   | LATA5             | LATA4   | LATA3                                                 | LATA2   | LATA1   | LATA0   |  |

| bit 7                                                                |         |                   |         | · · · ·                                               |         |         | bit 0   |  |

|                                                                      |         |                   |         |                                                       |         |         |         |  |

| Legend:                                                              |         |                   |         |                                                       |         |         |         |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |         |                   |         |                                                       |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown                              |         |                   | nown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set                                                     |         | '0' = Bit is clea | ared    |                                                       |         |         |         |  |

#### REGISTER 12-4: LATA: PORTA DATA LATCH REGISTER

#### LATA<7:0>: PORTA Output Latch Value bits<sup>(1)</sup> bit 7-4

Note 1: Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is the return of actual I/O pin values.

#### REGISTER 12-5: ANSELA: PORTA ANALOG SELECT REGISTER

| U-0   | U-0 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|-----|---------|---------|---------|---------|

| _     | —   | ANSA5   | —   | ANSA3   | ANSA2   | ANSA1   | ANSA0   |

| bit 7 |     |         |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                                                        |

|---------|---------------------------------------------------------------------------------------------------|

| bit 5   | ANSA5: Analog Select between Analog or Digital Function on pins RA5, respectively                 |

|         | 0 = Digital I/O. Pin is assigned to port or digital special function.                             |

|         | 1 = Analog input. Pin is assigned as analog input <sup>(1)</sup> . Digital input buffer disabled. |

| bit 4   | Unimplemented: Read as '0'                                                                        |

| hit 3-0 | ANSA-2:0>: Analog Select between Analog or Digital Function on hins BA-3:0> respect               |

- ANSA<3:0>: Analog Select between Analog or Digital Function on pins RA<3:0>, respectively bit 3-0 0 = Digital I/O. Pin is assigned to port or digital special function.

- 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

- Note 1: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| U-0                | U-0 | R/W-1/1          | R/W-1/1 | R/W-1/1                                               | R/W-1/1            | R/W-1/1 | R/W-1/1 |

|--------------------|-----|------------------|---------|-------------------------------------------------------|--------------------|---------|---------|

| —                  | —   | ANSB5            | ANSB4   | ANSB3                                                 | ANSB2              | ANSB1   | ANSB0   |

| bit 7              |     |                  |         | •                                                     |                    |         | bit 0   |

|                    |     |                  |         |                                                       |                    |         |         |

| Legend:            |     |                  |         |                                                       |                    |         |         |

| R = Readable bit   |     | W = Writable bi  | t       | U = Unimpleme                                         | ented bit, read as | ʻ0'     |         |

| u = Bit is unchang | ged | x = Bit is unkno | wn      | -n/n = Value at POR and BOR/Value at all other Resets |                    |         | Resets  |

#### REGISTER 12-9: ANSELB: PORTB ANALOG SELECT REGISTER

'0' = Bit is cleared

bit 7-6 Unimplemented: Read as '0'

'1' = Bit is set

| bit 5-0 | ANSB<5:0>: Analog Select between Analog or Digital Function on pins RB<5:0>, respectively         |

|---------|---------------------------------------------------------------------------------------------------|

|         | 0 = Digital I/O. Pin is assigned to port or digital special function.                             |

|         | 1 = Analog input. Pin is assigned as analog input <sup>(1)</sup> . Digital input buffer disabled. |

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### REGISTER 12-10: WPUB: WEAK PULL-UP PORTB REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUB7   | WPUB6   | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **WPUB<7:0>**: Weak Pull-up Register bits

1 = Pull-up enabled 0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

| Nome       | Bit 7  | <b>D</b> <sup>1</sup> / <sub>2</sub> <b>D</b> <sup>1</sup> / <sub>2</sub> <b>D</b> <sup>1</sup> / <sub>2</sub> | 54.5   |        | 57.0   | <b>D</b> i4 0 | Dit 4  | DH 0    | Register |

|------------|--------|----------------------------------------------------------------------------------------------------------------|--------|--------|--------|---------------|--------|---------|----------|

| Name       |        | Bit 6                                                                                                          | Bit 5  | Bit 4  | Bit 3  | Bit 2         | Bit 1  | Bit 0   | on Page  |

| ANSELB     | —      | _                                                                                                              | ANSB5  | ANSB4  | ANSB3  | ANSB2         | ANSB1  | ANSB0   | 112      |

| APFCON     | —      |                                                                                                                |        | _      | _      |               | SSSEL  | CCP2SEL | 105      |

| LATB       | LATB7  | LATB6                                                                                                          | LATB5  | LATB4  | LATB3  | LATB2         | LATB1  | LATB0   | 111      |

| OPTION_REG | WPUEN  | INTEDG                                                                                                         | TMR0CS | TMR0SE | PSA    | PS<2:0>       |        |         | 146      |

| PORTB      | RB7    | RB6                                                                                                            | RB5    | RB4    | RB3    | RB2           | RB1    | RB0     | 111      |

| TRISB      | TRISB7 | TRISB6                                                                                                         | TRISB5 | TRISB4 | TRISB3 | TRISB2        | TRISB1 | TRISB0  | 111      |

| WPUB       | WPUB7  | WPUB6                                                                                                          | WPUB5  | WPUB4  | WPUB3  | WPUB2         | WPUB1  | WPUB0   | 112      |

#### TABLE 12-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

| R/W-x/u                               | R/W-x/u | R/W-x/u         | R/W-x/u | R/W-x/u                            | R/W-x/u       | R/W-x/u          | R/W-x/u     |  |

|---------------------------------------|---------|-----------------|---------|------------------------------------|---------------|------------------|-------------|--|

| RC7                                   | RC6     | RC5             | RC4     | RC3                                | RC2           | RC1              | RC0         |  |

| bit 7                                 |         |                 |         |                                    |               |                  | bit 0       |  |

|                                       |         |                 |         |                                    |               |                  |             |  |

| Legend:                               |         |                 |         |                                    |               |                  |             |  |

| R = Readable                          | bit     | W = Writable    | bit     | U = Unimplemented bit, read as '0' |               |                  |             |  |

| u = Bit is unch                       | anged   | x = Bit is unkr | nown    | -n/n = Value a                     | at POR and BO | R/Value at all c | ther Resets |  |

| '1' = Bit is set '0' = Bit is cleared |         |                 | ared    |                                    |               |                  |             |  |

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is the return of actual I/O pin values.

#### REGISTER 12-12: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TRISC<7:0>: PORTC Tri-State Control bits

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

#### REGISTER 12-13: LATC: PORTC DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATC<7:0>: PORTC Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is the return of actual I/O pin values.

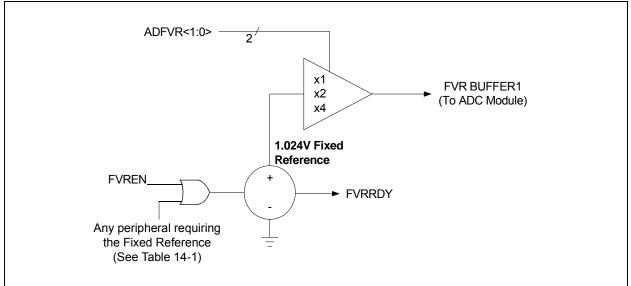

### 14.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- · ADC positive reference

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

#### 14.1 Independent Gain Amplifiers

The output of the FVR supplied to the ADC module is routed through a programmable gain amplifier. The amplifier can be configured to amplify the reference voltage by 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 16.0** "**Analog-to-Digital Converter** (**ADC**) **Module**" for additional information.

To minimize current consumption when the FVR is disabled, the FVR buffers should be turned off by clearing the Buffer Gain Selection bits.

#### 14.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set. See **Section 25.0** "**Electrical Specifications**" for the minimum delay requirement.

#### FIGURE 14-1: VOLTAGE REFERENCE BLOCK DIAGRAM

#### TABLE 14-1: PERIPHERALS REQUIRING THE FIXED VOLTAGE REFERENCE (FVR)

| Peripheral | Conditions                                                        | Description                                                        |

|------------|-------------------------------------------------------------------|--------------------------------------------------------------------|

| HFINTOSC   | FOSC<2:0> = 100 and<br>IRCF<3:0> = 000x                           | INTOSC is active and device is not in Sleep                        |

|            | BOREN<1:0> = 11                                                   | BOR always enabled                                                 |

| BOR        | BOREN<1:0> = 10 and BORFS = 1                                     | BOR disabled in Sleep mode, BOR Fast Start enabled.                |

|            | BOREN<1:0> = 01 and BORFS = 1                                     | BOR under software control, BOR Fast Start enabled                 |

| LDO        | All PIC16F1516/7/8/9 devices, when<br>VREGPM = 1 and not in Sleep | The device runs off of the low-power regulator when in Sleep mode. |

© 2010-2016 Microchip Technology Inc.

#### 16.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- Port configuration

- · Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- · Interrupt control

- · Result formatting

#### 16.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 12.0 "I/O Ports"** for more information.

| Note: | Analog voltages on any pin that is defined |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | as a digital input may cause the input     |  |  |  |  |  |  |  |  |

|       | buffer to conduct excess current.          |  |  |  |  |  |  |  |  |

#### 16.1.2 CHANNEL SELECTION

There are up to 30 channel selections available:

- AN<19:8, 4:0> pins (PIC16(L)F1516/8 only)

- AN<27:0> pins (PIC16(L)F1517/9 only)

- Temperature Indicator

- FVR (Fixed Voltage Reference) Output

Refer to Section 14.0 "Fixed Voltage Reference (FVR)" and Section 15.0 "Temperature Indicator Module" for more information on these channel selections.

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 16.2** "**ADC Operation**" for more information.

#### 16.1.3 ADC VOLTAGE REFERENCE

The ADPREF bits of the ADCON1 register provides control of the positive voltage reference. The positive voltage reference can be:

- VREF+ pin

- Vdd

See Section 14.0 "Fixed Voltage Reference (FVR)" for more details on the Fixed Voltage Reference.

#### 16.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- · FRC (dedicated internal FRC oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11.5 TAD periods as shown in Figure 16-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the ADC conversion requirements in **Section 25.0 "Electrical Specifications"** for more information. Table gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

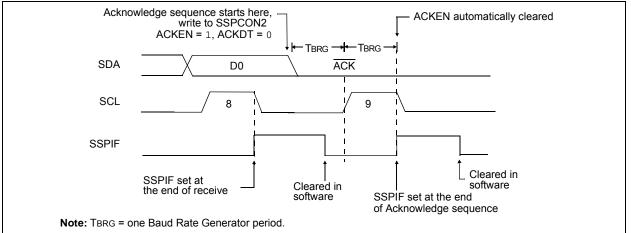

#### 21.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPCON2 register. When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 21-30).

#### 21.6.8.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

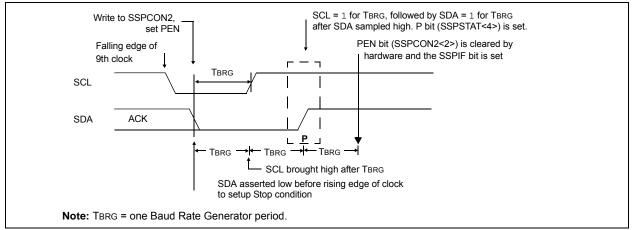

#### 21.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPCON2 register. At the end of a receive/transmit, the SCL line is held low after the falling edge of the 9th clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit of the SSPSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 21-31).

#### 21.6.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

#### FIGURE 21-30: ACKNOWLEDGE SEQUENCE WAVEFORM

#### FIGURE 21-31: STOP CONDITION RECEIVE OR TRANSMIT MODE

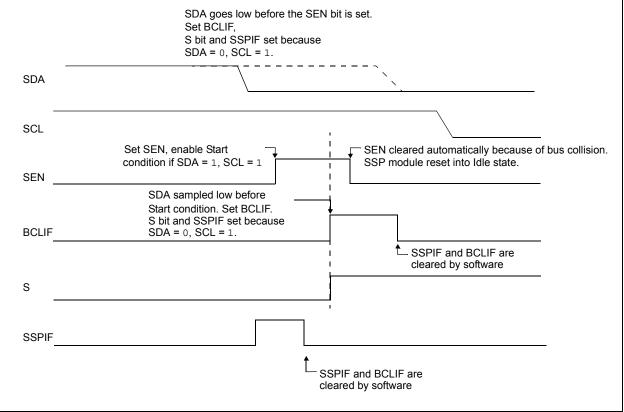

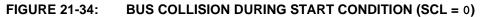

## 21.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 21-33).

- b) SCL is sampled low before SDA is asserted low (Figure 21-34).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- · the Start condition is aborted,

- · the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 21-33).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

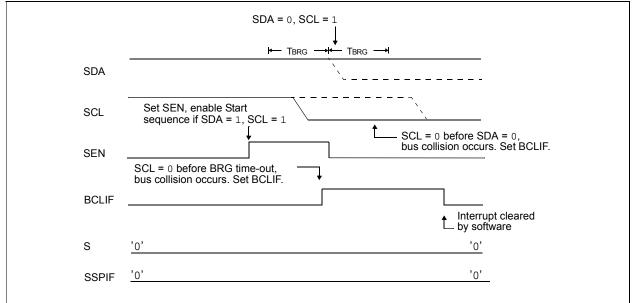

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 21-35). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

#### FIGURE 21-35: BRG RESET DUE TO SDA ARBITRATION DURING START CONDITION

|         |            | -        |        |               |             |              |        |        |                     |

|---------|------------|----------|--------|---------------|-------------|--------------|--------|--------|---------------------|

| Name    | Bit 7      | Bit 6    | Bit 5  | Bit 4         | Bit 3       | Bit 2        | Bit 1  | Bit 0  | Register<br>on Page |

| BAUDCON | ABDOVF     | RCIDL    | _      | SCKP          | BRG16       | —            | WUE    | ABDEN  | 232                 |

| INTCON  | GIE        | PEIE     | TMR0IE | INTE          | IOCIE       | TMR0IF       | INTF   | IOCIF  | 74                  |

| PIE1    | TMR1GIE    | ADIE     | RCIE   | TXIE          | SSPIE       | CCP1IE       | TMR2IE | TMR1IE | 75                  |

| PIR1    | TMR1GIF    | ADIF     | RCIF   | TXIF          | SSPIF       | CCP1IF       | TMR2IF | TMR1IF | 77                  |

| RCREG   |            |          | EUS    | ART Receiv    | ve Data Reg | gister       |        |        | 225*                |

| RCSTA   | SPEN       | RX9      | SREN   | CREN          | ADDEN       | FERR         | OERR   | RX9D   | 231                 |

| SPBRGL  |            | BRG<7:0> |        |               |             |              |        |        |                     |

| SPBRGH  | BRG<15:8>  |          |        |               |             |              | 233*   |        |                     |

| TRISC   | TRISC7     | TRISC6   | TRISC5 | TRISC4        | TRISC3      | TRISC2       | TRISC1 | TRISC0 | 114                 |

| TXSTA   | CSRC       | TX9      | TXEN   | SYNC          | SENDB       | BRGH         | TRMT   | TX9D   | 230                 |

| Logondy | – unimplom |          |        | ممامم ممالم م |             | for one work |        | ntinn  |                     |

#### TABLE 22-2: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for asynchronous reception.

\* Page provides register information.

| R/W-0/0          | R/W-0/0                                                                                                                                        | R/W-0/0                                                                                      | R/W-0/0        | R/W-0/0        | R-0/0            | R-0/0            | R-0/0       |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------|----------------|------------------|------------------|-------------|--|--|--|--|--|

| SPEN             | RX9                                                                                                                                            | SREN                                                                                         | CREN           | ADDEN          | FERR             | OERR             | RX9D        |  |  |  |  |  |

| bit 7            | •                                                                                                                                              |                                                                                              |                |                |                  |                  | bit (       |  |  |  |  |  |

| <u> </u>         |                                                                                                                                                |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

| Legend:          |                                                                                                                                                |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

| R = Readable     |                                                                                                                                                | W = Writable                                                                                 |                | •              | nented bit, reac |                  |             |  |  |  |  |  |

| u = Bit is uncl  | •                                                                                                                                              | x = Bit is unk                                                                               |                | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |  |  |  |  |  |

| '1' = Bit is set |                                                                                                                                                | '0' = Bit is cle                                                                             | ared           |                |                  |                  |             |  |  |  |  |  |

| bit 7            | SPEN: Seria                                                                                                                                    | I Port Enable b                                                                              | it             |                |                  |                  |             |  |  |  |  |  |

|                  | 1 = Serial po                                                                                                                                  | ort enabled (cor                                                                             | nfigures RX/D  | T and TX/CK pi | ins as serial po | rt pins)         |             |  |  |  |  |  |

|                  |                                                                                                                                                | ort disabled (he                                                                             |                | ·              | ·                | . ,              |             |  |  |  |  |  |

| bit 6            | <b>RX9:</b> 9-bit Re                                                                                                                           | eceive Enable b                                                                              | pit            |                |                  |                  |             |  |  |  |  |  |

|                  |                                                                                                                                                | 9-bit reception<br>8-bit reception                                                           |                |                |                  |                  |             |  |  |  |  |  |

| bit 5            | SREN: Singl                                                                                                                                    | e Receive Enal                                                                               | ole bit        |                |                  |                  |             |  |  |  |  |  |

|                  | Asynchronou                                                                                                                                    | Asynchronous mode:                                                                           |                |                |                  |                  |             |  |  |  |  |  |

|                  | Don't care                                                                                                                                     |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

|                  | Synchronous mode – Master:                                                                                                                     |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

|                  | 1 = Enables single receive                                                                                                                     |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

|                  | <ul> <li>Disables single receive</li> <li>This bit is cleared after reception is complete.</li> </ul>                                          |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

|                  | Synchronous mode – Slave                                                                                                                       |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

|                  | Don't care                                                                                                                                     |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

| bit 4            | CREN: Conti                                                                                                                                    | inuous Receive                                                                               | Enable bit     |                |                  |                  |             |  |  |  |  |  |

|                  | Asynchronou                                                                                                                                    | Asynchronous mode:                                                                           |                |                |                  |                  |             |  |  |  |  |  |

|                  | 1 = Enables receiver                                                                                                                           |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

|                  | 0 = Disables receiver                                                                                                                          |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

|                  | Synchronous mode:                                                                                                                              |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

|                  | <ol> <li>Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)</li> <li>D = Disables continuous receive</li> </ol> |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

| bit 3            | ADDEN: Address Detect Enable bit                                                                                                               |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

|                  | Asynchronous mode 9-bit (RX9 = 1):                                                                                                             |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

|                  | 1 = Enables address detection, enable interrupt and load the receive buffer when RSR<8> is set                                                 |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

|                  |                                                                                                                                                | 0 = Disables address detection, all bytes are received and 9th bit can be used as parity bit |                |                |                  |                  |             |  |  |  |  |  |

|                  | Asynchronous mode 8-bit ( $RX9 = 0$ ):                                                                                                         |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

| L:1 0            | Don't care                                                                                                                                     | in a Fana a hit                                                                              |                |                |                  |                  |             |  |  |  |  |  |

| bit 2            | FERR: Fram                                                                                                                                     | -                                                                                            | indated by rea |                | agistar and raa  | oive povt velid  | huto)       |  |  |  |  |  |

|                  | <ul> <li>1 = Framing error (can be updated by reading RCREG register and receive next valid byte)</li> <li>0 = No framing error</li> </ul>     |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

| bit 1            | OERR: Over                                                                                                                                     | run Error bit                                                                                |                |                |                  |                  |             |  |  |  |  |  |

|                  |                                                                                                                                                | error (can be c                                                                              | leared by clea | ring bit CREN) | I                |                  |             |  |  |  |  |  |

| <b>h</b> :+ 0    | 0 = No overi                                                                                                                                   |                                                                                              | Data           |                |                  |                  |             |  |  |  |  |  |

| bit 0            |                                                                                                                                                | bit of Received<br>address/data bi                                                           |                |                |                  | c                |             |  |  |  |  |  |

|                  |                                                                                                                                                |                                                                                              |                |                |                  |                  |             |  |  |  |  |  |

### REGISTER 22-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

#### 25.6 DC Characteristics: I/O Ports

| DC CHARACTERISTICS |      |                                      | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature -40°C } \le TA \leq +85°C \mbox{ for industrial} \\ -40°C \leq TA \leq +125°C \mbox{ for extended} \end{array}$ |      |          |       |                                                                            |  |  |

|--------------------|------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|----------------------------------------------------------------------------|--|--|

| Param<br>No.       | Sym. | Characteristic                       | Min.                                                                                                                                                                                                                            | Тур† | Max.     | Units | Conditions                                                                 |  |  |

|                    | VIL  | Input Low Voltage                    |                                                                                                                                                                                                                                 |      | •        |       | •                                                                          |  |  |

|                    |      | I/O PORT:                            |                                                                                                                                                                                                                                 |      |          |       |                                                                            |  |  |

| D030               |      | with TTL buffer                      | —                                                                                                                                                                                                                               | _    | 0.8      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                           |  |  |

| D030A              |      |                                      | —                                                                                                                                                                                                                               | _    | 0.15 VDD | V     | $1.8V \leq V\text{DD} \leq 4.5V$                                           |  |  |

| D031               |      | with Schmitt Trigger buffer          | —                                                                                                                                                                                                                               | _    | 0.2 VDD  | V     | $2.0V \leq V\text{DD} \leq 5.5V$                                           |  |  |

|                    |      | with I <sup>2</sup> C levels         | _                                                                                                                                                                                                                               | _    | 0.3 Vdd  | V     |                                                                            |  |  |

|                    |      | with SMBus levels                    | _                                                                                                                                                                                                                               |      | 0.8      | V     | $2.7V \le V\text{DD} \le 5.5V$                                             |  |  |

| D032               |      | MCLR, OSC1 (RC mode) <sup>(1)</sup>  | _                                                                                                                                                                                                                               | _    | 0.2 VDD  | V     | (Note 1)                                                                   |  |  |

| D033               |      | OSC1 (HS mode)                       | _                                                                                                                                                                                                                               | _    | 0.3 Vdd  | V     |                                                                            |  |  |

|                    | Vih  | Input High Voltage                   |                                                                                                                                                                                                                                 |      |          |       |                                                                            |  |  |

|                    |      | I/O ports:                           |                                                                                                                                                                                                                                 | _    | —        |       |                                                                            |  |  |

| D040               |      | with TTL buffer                      | 2.0                                                                                                                                                                                                                             | _    | —        | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                           |  |  |

| D040A              |      |                                      | 0.25 VDD +<br>0.8                                                                                                                                                                                                               | —    | —        | V     | $1.8V \leq V\text{DD} \leq 4.5V$                                           |  |  |

| D041               |      | with Schmitt Trigger buffer          | 0.8 VDD                                                                                                                                                                                                                         | _    | _        | V     | $2.0V \leq V\text{DD} \leq 5.5V$                                           |  |  |

|                    |      | with I <sup>2</sup> C levels         | 0.7 Vdd                                                                                                                                                                                                                         | _    | _        | V     |                                                                            |  |  |

|                    |      | with SMBus levels                    | 2.1                                                                                                                                                                                                                             | _    | _        | V     | $2.7V \leq V\text{DD} \leq 5.5V$                                           |  |  |

| D042               |      | MCLR                                 | 0.8 VDD                                                                                                                                                                                                                         | _    | _        | V     |                                                                            |  |  |

| D043A              |      | OSC1 (HS mode)                       | 0.7 Vdd                                                                                                                                                                                                                         |      | _        | V     |                                                                            |  |  |

| D043B              |      | OSC1 (RC mode)                       | 0.9 VDD                                                                                                                                                                                                                         | _    | _        | V     | VDD > 2.0V (Note 1)                                                        |  |  |

|                    | lı∟  | Input Leakage Current <sup>(2)</sup> |                                                                                                                                                                                                                                 |      |          |       |                                                                            |  |  |

| D060               |      | I/O ports                            | —                                                                                                                                                                                                                               | ± 5  | ± 125    | nA    | $Vss \leq VPIN \leq VDD, Pin at high-impedance at 85^{\circ}C$             |  |  |

|                    |      |                                      |                                                                                                                                                                                                                                 | ± 5  | ± 1000   | nA    | 125°C                                                                      |  |  |

| D061               |      | MCLR <sup>(3)</sup>                  | —                                                                                                                                                                                                                               | ± 50 | ± 200    | nA    | $Vss \leq V \text{PIN} \leq V \text{DD} \text{ at } 85^\circ C$            |  |  |

|                    | Ipur | Weak Pull-up Current                 | ,                                                                                                                                                                                                                               |      | 1        |       | Γ                                                                          |  |  |

| D070*              |      |                                      | 25                                                                                                                                                                                                                              | 100  | 200      | μA    | VDD = 3.3V, $VPIN = VSS$                                                   |  |  |

|                    | Vol  | Output Low Voltage <sup>(4)</sup>    | 25                                                                                                                                                                                                                              | 140  | 300      | μA    | VDD = 5.0V, VPIN = VSS                                                     |  |  |

| D080               |      | I/O ports                            | _                                                                                                                                                                                                                               | _    | 0.6      | v     | IOL = 8 mA, VDD = 5V<br>IOL = 6 mA, VDD = 3.3V<br>IOL = 1.8 mA, VDD = 1.8V |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: Including OSC2 in CLKOUT mode.

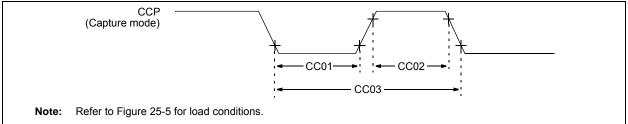

#### FIGURE 25-11: CAPTURE/COMPARE/PWM TIMINGS (CCP)

#### TABLE 25-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP)

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                     |                |                       |      |       |            |                                 |  |

|--------------------------------------------------------------------------------------------------------------------------|------|---------------------|----------------|-----------------------|------|-------|------------|---------------------------------|--|

| Param<br>No.                                                                                                             | Sym. | Characteri          | Min.           | Тур†                  | Max. | Units | Conditions |                                 |  |

| CC01*                                                                                                                    | TccL | CCP Input Low Time  | No Prescaler   | 0.5Tcy + 20           | -    | _     | ns         |                                 |  |

|                                                                                                                          |      |                     | With Prescaler | 20                    | _    | _     | ns         |                                 |  |

| CC02*                                                                                                                    | TccH | CCP Input High Time | No Prescaler   | 0.5Tcy + 20           | _    | _     | ns         |                                 |  |

|                                                                                                                          |      |                     | With Prescaler | 20                    | _    | _     | ns         |                                 |  |

| CC03*                                                                                                                    | TccP | CCP Input Period    |                | <u>3Tcy + 40</u><br>N | —    | —     | ns         | N = prescale value (1, 4 or 16) |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

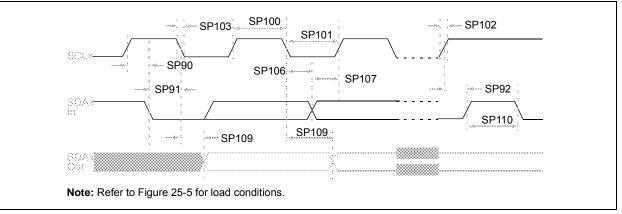

#### FIGURE 25-21: I<sup>2</sup>C BUS DATA TIMING

| Param.<br>No. | Symbol  | Characte                   | eristic      | Min.       | Max. | Units | Conditions                                  |  |

|---------------|---------|----------------------------|--------------|------------|------|-------|---------------------------------------------|--|

| SP100*        | Тнідн   | Clock high time            | 100 kHz mode | 4.0        | —    | μS    | Device must operate at a minimum of 1.5 MHz |  |

|               |         |                            | 400 kHz mode | 0.6        | -    | μS    | Device must operate at a minimum of 10 MHz  |  |

|               |         |                            | SSP module   | 1.5Tcy     |      | —     |                                             |  |

| SP101*        | TLOW    | Clock low time             | 100 kHz mode | 4.7        | -    | μS    | Device must operate at a minimum of 1.5 MHz |  |

|               |         |                            | 400 kHz mode | 1.3        | —    | μS    | Device must operate at a minimum of 10 MHz  |  |

|               |         |                            | SSP module   | 1.5Tcy     | _    | _     |                                             |  |

| SP102*        | TR      | SDAx and SCLx rise time    | 100 kHz mode | —          | 1000 | ns    |                                             |  |

|               |         |                            | 400 kHz mode | 20 + 0.1CB | 300  | ns    | CB is specified to be from 10-400 pF        |  |

| SP103*        | TF      | SDAx and SCLx fall time    | 100 kHz mode | —          | 250  | ns    |                                             |  |

|               |         |                            | 400 kHz mode | 20 + 0.1Св | 250  | ns    | CB is specified to be from 10-400 pF        |  |

| SP106*        | THD:DAT | Data input hold time       | 100 kHz mode | 0          |      | ns    |                                             |  |

|               |         |                            | 400 kHz mode | 0          | 0.9  | μS    |                                             |  |

| SP107*        | TSU:DAT | Data input setup time      | 100 kHz mode | 250        |      | ns    | (Note 2)                                    |  |

|               |         |                            | 400 kHz mode | 100        | —    | ns    | ]                                           |  |

| SP109*        | ΤΑΑ     | Output valid from<br>clock | 100 kHz mode | _          | 3500 | ns    | (Note 1)                                    |  |

|               |         |                            | 400 kHz mode | _          |      | ns    |                                             |  |

| SP110*        | TBUF    | Bus free time              | 100 kHz mode | 4.7        | —    | μs    | Time the bus must be free                   |  |

|               |         |                            | 400 kHz mode | 1.3        | —    | μS    | before a new transmission<br>can start      |  |

| SP111         | Св      | Bus capacitive loading     |              | —          | 400  | pF    |                                             |  |

#### TABLE 25-14: I<sup>2</sup>C BUS DATA REQUIREMENTS

These parameters are characterized but not tested.

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCLx to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement Tsu:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCLx signal. If such a device does stretch the low period of the SCLx signal, it must output the next data bit to the SDAx line TR max. + Tsu:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCLx line is released.

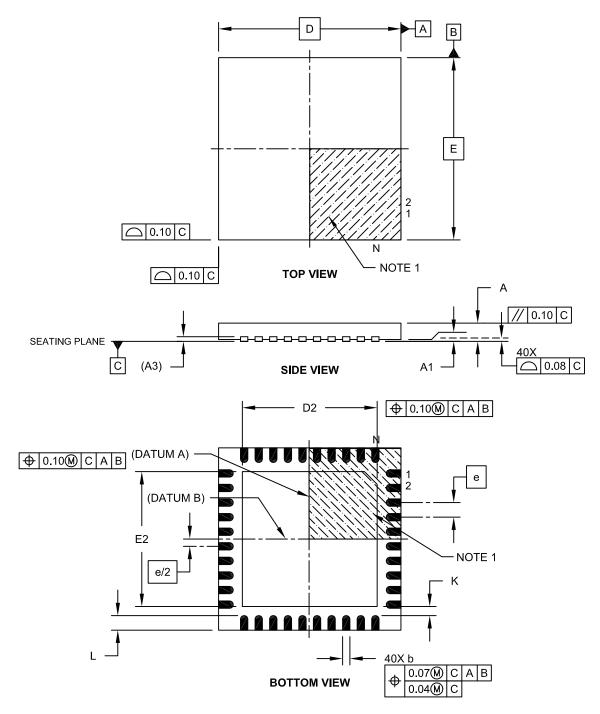

#### 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-156A Sheet 1 of 2