#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1518-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Master Synchronous Serial Port (MSSP) with SPI and I<sup>2</sup>C with:

- 7-bit address masking

- SMBus/PMBus™ compatibility

- Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module:

- RS-232, RS-485 and LIN compatible

- Auto-Baud Detect

- Auto-wake-up on start

### PIC16(L)F151X/152X Family Types

|               | ~                | >                               |                      | Flash                         |                       | A           | C                |                      |        |                             |     |                      |     |

|---------------|------------------|---------------------------------|----------------------|-------------------------------|-----------------------|-------------|------------------|----------------------|--------|-----------------------------|-----|----------------------|-----|

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | High Endurance Fla<br>(bytes) | (2) <sup>S,</sup> O/I | 10-bit (ch) | Advanced Control | Timers<br>(8/16-bit) | EUSART | MSSP (I <sup>2</sup> C/SPI) | ССР | Debug <sup>(1)</sup> | ХГР |

| PIC16(L)F1512 | (1)              | 2048                            | 128                  | 128                           | 25                    | 17          | Y                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1513 | (1)              | 4096                            | 256                  | 128                           | 25                    | 17          | Y                | 2/1                  | 1      | 1                           | 2   |                      | Y   |

| PIC16(L)F1516 | (2)              | 8192                            | 512                  | 128                           | 25                    | 17          | Ν                | 2/1                  | 1      | 1                           | 2   | -                    | Y   |

| PIC16(L)F1517 | (2)              | 8192                            | 512                  | 128                           | 36                    | 28          | Ν                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1518 | (2)              | 16384                           | 1024                 | 128                           | 25                    | 17          | Ν                | 2/1                  | 1      | 1                           | 2   |                      | Y   |

| PIC16(L)F1519 | (2)              | 16384                           | 1024                 | 128                           | 36                    | 28          | Ν                | 2/1                  | 1      | 1                           | 2   | Ι                    | Y   |

| PIC16(L)F1526 | (3)              | 8192                            | 768                  | 128                           | 54                    | 30          | Ν                | 6/3                  | 2      | 2                           | 10  |                      | Y   |

| PIC16(L)F1527 | (3)              | 16384                           | 1536                 | 128                           | 54                    | 30          | Ν                | 6/3                  | 2      | 2                           | 10  |                      | Y   |

Note 1: I - Debugging, Integrated on Chip; H - Debugging, available using Debug Header.

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

1: DS40001624 PIC16(L)F1512/13 Data Sheet, 28-Pin Flash, 8-bit Microcontrollers.

- **2:** DS40001452 PIC16(L)F1516/7/8/9 Data Sheet, 28/40/44-Pin Flash, 8-bit MCUs.

- **3:** DS40001458 PIC16(L)F1526/27 Data Sheet, 64-Pin Flash, 8-bit MCUs.

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

#### 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection is controlled independently. Internal access to the program memory is unaffected by any code protection setting.

#### 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4** "Write **Protection**" for more information.

#### 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

#### 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 11.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the "*PIC16(L)F151X/152X Memory Programming Specification*" (DS41442).

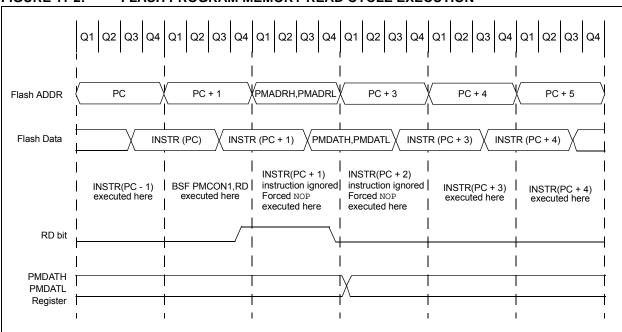

#### FIGURE 11-2: FLASH PROGRAM MEMORY READ CYCLE EXECUTION

#### EXAMPLE 11-1: FLASH PROGRAM MEMORY READ

\* This code block will read 1 word of program

- \* memory at the memory address:

- PROG\_ADDR\_HI : PROG\_ADDR\_LO

- \* data will be returned in the variables;

- \* PROG\_DATA\_HI, PROG\_DATA\_LO

| BANKSEL<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWL | PMADRL<br>PROG_ADDR_LO<br>PMADRL<br>PROG_ADDR_HI<br>PMADRH | ;<br>;<br>; | Select Bank for PMCON registers<br>Store LSB of address<br>Store MSB of address                      |

|---------------------------------------------|------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------|

| BCF<br>BSF<br>NOP<br>NOP                    | PMCON1,CFGS<br>PMCON1,RD                                   | ;<br>;      | Do not select Configuration Space<br>Initiate read<br>Ignored (Figure 11-2)<br>Ignored (Figure 11-2) |

| MOVF<br>MOVWF<br>MOVF<br>MOVWF              | PMDATL,W<br>PROG_DATA_LO<br>PMDATH,W<br>PROG_DATA_HI       | ;;          | Get LSB of word<br>Store in user location<br>Get MSB of word<br>Store in user location               |

#### 11.2.4 WRITING TO FLASH PROGRAM MEMORY

Program memory is programmed using the following steps:

- 1. Load the address in PMADRH:PMADRL of the row to be programmed.

- 2. Load each write latch with data.

- 3. Initiate a programming operation.

- 4. Repeat steps 1 through 3 until all data is written.

Before writing to program memory, the word(s) to be written must be erased or previously unwritten. Program memory can only be erased one row at a time. No automatic erase occurs upon the initiation of the write.

Program memory can be written one or more words at a time. The maximum number of words written at one time is equal to the number of write latches. See Figure 11-5 (row writes to program memory with 32 write latches) for more details.

The write latches are aligned to the Flash row address boundary defined by the upper ten bits of PMADRH:PMADRL, (PMADRH<6:0>:PMADRL<7:5>) with the lower five bits of PMADRL, (PMADRL<7:5>) determining the write latch being loaded. Write operations do not cross these boundaries. At the completion of a program memory write operation, the data in the write latches is reset to contain 0x3FFF. The following steps should be completed to load the write latches and program a row of program memory. These steps are divided into two parts. First, each write latch is loaded with data from the PMDATH:PMDATL using the unlock sequence with LWLO = 1. When the last word to be loaded into the write latch is ready, the LWLO bit is cleared and the unlock sequence executed. This initiates the programming operation, writing all the latches into Flash program memory.

- Note: The special unlock sequence is required to load a write latch with data or initiate a Flash programming operation. If the unlock sequence is interrupted, writing to the latches or program memory will not be initiated.

- 1. Set the WREN bit of the PMCON1 register.

- 2. Clear the CFGS bit of the PMCON1 register.

- Set the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '1', the write sequence will only load the write latches and will not initiate the write to Flash program memory.

- 4. Load the PMADRH:PMADRL register pair with the address of the location to be written.

- 5. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- Execute the unlock sequence (Section 11.2.2 "Flash Memory Unlock Sequence"). The write latch is now loaded.

- 7. Increment the PMADRH:PMADRL register pair to point to the next location.

- 8. Repeat steps 5 through 7 until all but the last write latch has been loaded.

- Clear the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '0', the write sequence will initiate the write to Flash program memory.

- 10. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- 11. Execute the unlock sequence (Section 11.2.2 "Flash Memory Unlock Sequence"). The entire program memory latch content is now written to Flash program memory.

- **Note:** The program memory write latches are reset to the blank state (0x3FFF) at the completion of every write or erase operation. As a result, it is not necessary to load all the program memory write latches. Unloaded latches will remain in the blank state.

An example of the complete write sequence is shown in Example 11-3. The initial address is loaded into the PMADRH:PMADRL register pair; the data is loaded using indirect addressing.

#### 12.6 PORTE Registers

#### 12.6.1 DATA REGISTER

PORTE is a 4-bit wide, bidirectional port. The corresponding data direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). The exception is RE3, which is input only and its TRIS bit will always read as '1'. Example 12-1 shows how to initialize an I/O port.

Reading the PORTE register (Register 12-19) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATE). RE3 reads '0' when MCLRE = 1.

| Note: | RE<2:0>     | and    | TRISE<2:0>     | pins  | are |

|-------|-------------|--------|----------------|-------|-----|

|       | available o | on PIC | 16(L)F1517/9 c | only. |     |

#### 12.6.2 ANALOG CONTROL

The ANSELE register (Register 12-22) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELE bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELE bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

The TRISE register (Register 12-20) controls the PORTE pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISE register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSELE bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

#### 12.6.3 PORTE FUNCTIONS AND OUTPUT PRIORITIES

PORTE has no peripheral outputs, so the PORTE output has no priority function.

| R/W-0/u          | R/W-0/u                                      | R/W-0/u                                                                                                                             | R/W-0/u         | R/W/HC-0/u       | R-x/x            | R/W-0/u          | R/W-0/u      |  |  |  |  |

|------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|------------------|------------------|--------------|--|--|--|--|

| TMR1GE           | T1GPOL                                       | T1GTM                                                                                                                               | T1GSPM          | T1GGO/<br>DONE   | T1GVAL           | T1GS             | 6<1:0>       |  |  |  |  |

| bit 7            | •                                            |                                                                                                                                     |                 |                  |                  |                  | bit (        |  |  |  |  |

|                  |                                              |                                                                                                                                     |                 |                  |                  |                  |              |  |  |  |  |

| Legend:          |                                              |                                                                                                                                     |                 |                  |                  |                  |              |  |  |  |  |

| R = Readable     |                                              | W = Writable                                                                                                                        | bit             | U = Unimplen     | nented bit, read | d as '0'         |              |  |  |  |  |

| u = Bit is uncl  | hanged                                       | x = Bit is unkr                                                                                                                     | nown            | -n/n = Value a   | at POR and BC    | R/Value at all o | other Resets |  |  |  |  |

| '1' = Bit is set |                                              | '0' = Bit is cle                                                                                                                    | ared            | HC = Bit is cle  | eared by hardw   | /are             |              |  |  |  |  |

| bit 7            | TMR1GE: Ti                                   | mer1 Gate Ena                                                                                                                       | ble bit         |                  |                  |                  |              |  |  |  |  |

|                  | If TMR10N =                                  | <u>= 0</u> :                                                                                                                        |                 |                  |                  |                  |              |  |  |  |  |

|                  | This bit is igr                              |                                                                                                                                     |                 |                  |                  |                  |              |  |  |  |  |

|                  | $\frac{\text{If TMR1ON}}{1 = \text{Timer1}}$ | <u>= ⊥</u> :<br>counting is cont                                                                                                    | rolled by the T | imer1 gate fund  | tion             |                  |              |  |  |  |  |

|                  |                                              | counts regardle                                                                                                                     |                 |                  |                  |                  |              |  |  |  |  |

| bit 6            | T1GPOL: Til                                  | Timer1 Gate Polarity bit                                                                                                            |                 |                  |                  |                  |              |  |  |  |  |

|                  |                                              | = Timer1 gate is active-high (Timer1 counts when gate is high)                                                                      |                 |                  |                  |                  |              |  |  |  |  |

|                  |                                              | gate is active-lo                                                                                                                   |                 | nts when gate i  | s low)           |                  |              |  |  |  |  |

| bit 5            |                                              | er1 Gate Toggle Mode bit                                                                                                            |                 |                  |                  |                  |              |  |  |  |  |

|                  |                                              | Gate Toggle mo                                                                                                                      |                 | and to cale flip | flow is closed   |                  |              |  |  |  |  |

|                  |                                              | Gate Toggle mo<br>flip-flop toggles                                                                                                 |                 |                  | nop is cleared   |                  |              |  |  |  |  |

| bit 4            | •                                            | mer1 Gate Sing                                                                                                                      |                 |                  |                  |                  |              |  |  |  |  |

|                  |                                              | Gate Single-Pul                                                                                                                     |                 |                  | ntrolling Timer  | 1 gate           |              |  |  |  |  |

|                  |                                              | Gate Single-Pul                                                                                                                     |                 |                  | 0                | 0                |              |  |  |  |  |

| bit 3            | T1GGO/DO                                     | NE: Timer1 Gat                                                                                                                      | e Single-Pulse  | Acquisition Sta  | atus bit         |                  |              |  |  |  |  |

|                  |                                              | gate single-puls                                                                                                                    |                 |                  |                  |                  |              |  |  |  |  |

|                  |                                              | gate single-puls                                                                                                                    | •               | as completed c   | or has not beer  | started          |              |  |  |  |  |

|                  |                                              | <b>1GVAL:</b> Timer1 Gate Current State bit<br>ndicates the current state of the Timer1 gate that could be provided to TMR1H:TMR1L. |                 |                  |                  |                  |              |  |  |  |  |

|                  |                                              | y Timer1 Gate                                                                                                                       |                 |                  | e provided to 1  | MR1H: IMR1L      |              |  |  |  |  |

| bit 1-0          |                                              | <ul> <li>Timer1 Gate</li> </ul>                                                                                                     |                 |                  |                  |                  |              |  |  |  |  |

|                  | 11 = Reserv                                  |                                                                                                                                     |                 |                  |                  |                  |              |  |  |  |  |

|                  | 10 = Timer2                                  |                                                                                                                                     |                 |                  |                  |                  |              |  |  |  |  |

|                  |                                              | overflow output                                                                                                                     | t               |                  |                  |                  |              |  |  |  |  |

|                  | 00 = Timer1                                  | gate pin                                                                                                                            |                 |                  |                  |                  |              |  |  |  |  |

#### REGISTER 18-2: T1GCON: TIMER1 GATE CONTROL REGISTER

#### 20.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPx module does not assert control of the CCPx pin (see the CCPxCON register).

#### 20.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is chosen (CCPxM<3:0> = 1011), the CCPx module does the following:

- Resets Timer1

- Starts an ADC conversion if ADC is enabled

The CCPx module does not assert control of the CCPx pin in this mode.

The Special Event Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPRxH, CCPRxL register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. The Special Event Trigger output starts an ADC conversion (if the ADC module is enabled). This allows the CCPRxH, CCPRxL register pair to effectively provide a 16-bit programmable period register for Timer1.

#### TABLE 20-2: SPECIAL EVENT TRIGGER

| Device              | CCPx |

|---------------------|------|

| PIC16(L)F1516/7/8/9 | CCP2 |

Refer to **Section 16.2.5 "Special Event Trigger"** for more information.

- Note 1: The Special Event Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

- 2: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Special Event Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

#### 20.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

#### 20.2.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function**" for more information.

#### 20.3 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 20-3 shows a typical waveform of the PWM signal.

#### 20.3.1 STANDARD PWM OPERATION

The standard PWM function described in this section is available and identical for all CCP modules.

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to 10 bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PR2 registers

- T2CON registers

- CCPRxL registers

- CCPxCON registers

Figure 20-4 shows a simplified block diagram of PWM operation.

Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

2: Clearing the CCPxCON register will relinquish control of the CCPx pin.

### 21.5 I<sup>2</sup>C SLAVE MODE OPERATION

The MSSP Slave mode operates in one of four modes selected in the SSPM bits of SSPCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSPIF additionally getting set upon detection of a Start, Restart, or Stop condition.

#### 21.5.1 SLAVE MODE ADDRESSES

The SSPADD register (Register 21-8) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register (Register 21-7) affects the address matching process. See **Section 21.5.9** "**SSP Mask Register**" for more information.

#### 21.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

#### 21.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb of the 10-bit address and stored in bits 2 and 1 of the SSPADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPADD. Even if there is not an address match; SSPIF and UA are set, and SCL is held low until SSPADD is updated to receive a high byte again. When SSPADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

#### 21.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPSTAT register is set, or bit SSPOV of the SSPCON1 register is set. The BOEN bit of the SSPCON3 register modifies this operation. For more information see Register 21-6.

An MSSP interrupt is generated for each transferred data byte. Flag bit, SSPIF, must be cleared by software.

When the SEN bit of the SSPCON2 register is set, SCL will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPCON1 register, except sometimes in 10-bit mode. See **Section 21.2.3 "SPI Master Mode"** for more detail.

#### 21.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  Slave in 7-bit Addressing mode. All decisions made by hardware or software and their effect on reception. Figure 21-14 and Figure 21-15 is used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish  $\mathsf{I}^2\mathsf{C}$  communication.

- 1. Start bit detected.

- 2. S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- 3. Matching address with  $R/\overline{W}$  bit clear is received.

- 4. The slave pulls SDA low sending an ACK to the master, and sets SSPIF bit.

- 5. Software clears the SSPIF bit.

- 6. Software reads received address from SSPBUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCL line.

- 8. The master clocks out a data byte.

- Slave drives SDA low sending an ACK to the master, and sets SSPIF bit.

- 10. Software clears SSPIF.

- 11. Software reads the received byte from SSPBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the master.

- 13. Master sends Stop condition, setting P bit of SSPSTAT, and the bus goes idle.

| R/W-0/0                                  | R-0/0                                                                                                                                                                                                                                                                          | R/W-0/0                                                 | R/S/HS-0/0                    | R/S/HS-0/0                   | R/S/HS-0/0        | R/S/HS-0/0       | R/W/HS-0/0   |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------|------------------------------|-------------------|------------------|--------------|

| GCEN                                     | ACKSTAT                                                                                                                                                                                                                                                                        | ACKDT                                                   | ACKEN                         | RCEN                         | PEN               | RSEN             | SEN          |

| bit 7                                    |                                                                                                                                                                                                                                                                                |                                                         |                               |                              |                   |                  | bit (        |

| Legend:                                  |                                                                                                                                                                                                                                                                                |                                                         |                               |                              |                   |                  |              |

| R = Readable                             | bit                                                                                                                                                                                                                                                                            | W = Writable                                            | hit                           | =   Inimpler                 | mented bit, read  | 1 as 'O'         |              |

|                                          |                                                                                                                                                                                                                                                                                | x = Bit is unk                                          |                               | •                            | at POR and BO     |                  | thar Pasats  |

| u = Bit is unchanged<br>'1' = Bit is set |                                                                                                                                                                                                                                                                                | 6' = Bit is cle                                         |                               |                              | d by hardware     |                  |              |

| 1 - Dit 13 3et                           |                                                                                                                                                                                                                                                                                |                                                         | aicu                          |                              | a by hardware     | 0 - 0361 361     |              |

| bit 7                                    | 1 = Enable in                                                                                                                                                                                                                                                                  | eral Call Enable<br>Iterrupt when a<br>call address dis | general call ad               | • •                          | or 00h) is receiv | red in the SSPS  | SR           |

| bit 6                                    | 1 = Acknowle                                                                                                                                                                                                                                                                   | cknowledge St<br>edge was not re<br>edge was recei      | eceived                       | mode only)                   |                   |                  |              |

| bit 5                                    | ACKDT: Ack                                                                                                                                                                                                                                                                     | nowledge Data                                           | bit (in I <sup>2</sup> C mod  | le only)                     |                   |                  |              |

|                                          | In Receive m<br>Value transm<br>1 = Not Ackn<br>0 = Acknowle                                                                                                                                                                                                                   | itted when the owledge                                  | user initiates a              | n Acknowledg                 | je sequence at t  | the end of a red | ceive        |

| bit 4                                    |                                                                                                                                                                                                                                                                                | 0                                                       | Jence Enable I                | oit (in I <sup>2</sup> C Mas | ter mode only)    |                  |              |

|                                          | Automat                                                                                                                                                                                                                                                                        |                                                         | y hardware.                   | SDA and S                    | CL pins, and      | transmit ACk     | KDT data bi  |

| bit 3                                    |                                                                                                                                                                                                                                                                                | ive Enable bit (<br>Receive mode<br>dle                 |                               | mode only)                   |                   |                  |              |

| bit 2                                    | PEN: Stop Co                                                                                                                                                                                                                                                                   | ondition Enable                                         | e bit (in I <sup>2</sup> C Ma | ster mode onl                | y)                |                  |              |

|                                          |                                                                                                                                                                                                                                                                                |                                                         | -                             | L pins. Autom                | atically cleared  | by hardware.     |              |

| bit 1                                    | <ul> <li>Stop condition falle</li> <li>RSEN: Repeated Start Condition Enable bit (in I<sup>2</sup>C Master mode only)</li> <li>1 = Initiate Repeated Start condition on SDA and SCL pins. Automatically cleared by hards</li> <li>0 = Repeated Start condition Idle</li> </ul> |                                                         |                               |                              |                   |                  |              |

| bit 0                                    | SEN: Start C                                                                                                                                                                                                                                                                   | ondition Enable                                         | e/Stretch Enab                | le bit                       |                   |                  |              |

|                                          | <u>In Master mo</u><br>1 = Initiate St<br>0 = Start cone                                                                                                                                                                                                                       | art condition of                                        | n SDA and SC                  | L pins. Autom                | atically cleared  | by hardware.     |              |

|                                          |                                                                                                                                                                                                                                                                                |                                                         |                               | ave transmit a               | nd slave receive  | e (stretch enabl | ed)          |

| Note 1: For                              | bits ACKEN F                                                                                                                                                                                                                                                                   | RCEN, PEN, R                                            | SEN, SEN: If th               | ne l <sup>2</sup> C module   | is not in the IdI | e mode, this bi  | t may not be |

#### REGISTER 21-5: SSPCON2: SSP CONTROL REGISTER 2

**Note 1:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

|         |            | -         |        |               |             |              |        |        |                     |

|---------|------------|-----------|--------|---------------|-------------|--------------|--------|--------|---------------------|

| Name    | Bit 7      | Bit 6     | Bit 5  | Bit 4         | Bit 3       | Bit 2        | Bit 1  | Bit 0  | Register<br>on Page |

| BAUDCON | ABDOVF     | RCIDL     | _      | SCKP          | BRG16       | —            | WUE    | ABDEN  | 232                 |

| INTCON  | GIE        | PEIE      | TMR0IE | INTE          | IOCIE       | TMR0IF       | INTF   | IOCIF  | 74                  |

| PIE1    | TMR1GIE    | ADIE      | RCIE   | TXIE          | SSPIE       | CCP1IE       | TMR2IE | TMR1IE | 75                  |

| PIR1    | TMR1GIF    | ADIF      | RCIF   | TXIF          | SSPIF       | CCP1IF       | TMR2IF | TMR1IF | 77                  |

| RCREG   |            |           | EUS    | ART Receiv    | ve Data Reg | gister       |        |        | 225*                |

| RCSTA   | SPEN       | RX9       | SREN   | CREN          | ADDEN       | FERR         | OERR   | RX9D   | 231                 |

| SPBRGL  |            |           |        | BRG           | <7:0>       |              |        |        | 233*                |

| SPBRGH  |            | BRG<15:8> |        |               |             |              |        | 233*   |                     |

| TRISC   | TRISC7     | TRISC6    | TRISC5 | TRISC4        | TRISC3      | TRISC2       | TRISC1 | TRISC0 | 114                 |

| TXSTA   | CSRC       | TX9       | TXEN   | SYNC          | SENDB       | BRGH         | TRMT   | TX9D   | 230                 |

| Logondy | – unimplom |           |        | ممامم ممالم م |             | for one work |        | ntinn  |                     |

#### TABLE 22-2: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for asynchronous reception.

\* Page provides register information.

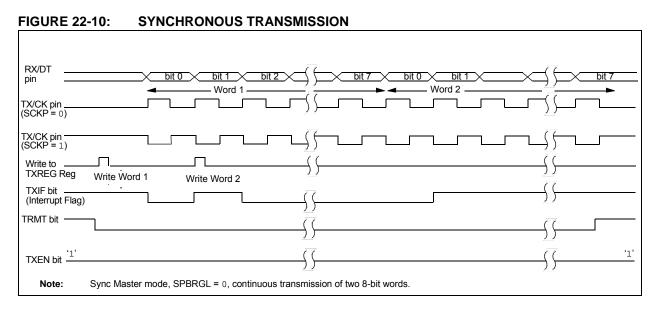

## TABLE 22-5:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>TRANSMISSION

| Name    | Bit 7                         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                        | RCIDL  | —      | SCKP   | BRG16  | —      | WUE    | ABDEN  | 232                 |

| INTCON  | GIE                           | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 74                  |

| PIE1    | TMR1GIE                       | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 75                  |

| PIR1    | TMR1GIF                       | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 77                  |

| RCSTA   | SPEN                          | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 231                 |

| SPBRGL  |                               |        |        | BRG    | <7:0>  |        |        |        | 233*                |

| SPBRGH  |                               |        |        | BRG<   | :15:8> |        |        |        | 233*                |

| TRISC   | TRISC7                        | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 114                 |

| TXREG   | EUSART Transmit Data Register |        |        |        |        |        |        | 222*   |                     |

| TXSTA   | CSRC                          | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 230                 |

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

#### 22.5.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

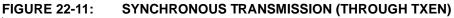

#### 22.5.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 22.5.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 22.5.2.2 Synchronous Slave Transmission Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant 8 bits to the TXREG register.

#### TABLE 22-7: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Name    | Bit 7                         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                        | RCIDL  | —      | SCKP   | BRG16  | —      | WUE    | ABDEN  | 232                 |

| INTCON  | GIE                           | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 74                  |

| PIE1    | TMR1GIE                       | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 75                  |

| PIR1    | TMR1GIF                       | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 77                  |

| RCSTA   | SPEN                          | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 231                 |

| TRISC   | TRISC7                        | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 114                 |

| TXREG   | EUSART Transmit Data Register |        |        |        |        |        | 222*   |        |                     |

| TXSTA   | CSRC                          | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 230                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

\* Page provides register information.

| RRF              | Rotate Right f through Carry                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                           |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                 |

| Operation:       | See description below                                                                                                                                                                                              |

| Status Affected: | С                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |

|                  | C Register f                                                                                                                                                                                                       |

| SUBLW            | Subtract W from literal                                                                                                               |                          |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|--|--|

| Syntax:          | [label] Sl                                                                                                                            | [ <i>label</i> ] SUBLW k |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                   |                          |  |  |  |

| Operation:       | $k \operatorname{-}(W) \operatorname{\rightarrow}(W$                                                                                  | /)                       |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                              | C, DC, Z                 |  |  |  |

| Description:     | The W register is subtracted (2's com-<br>plement method) from the 8-bit literal<br>'k'. The result is placed in the W regis-<br>ter. |                          |  |  |  |

|                  | <b>C</b> = 0                                                                                                                          | W > k                    |  |  |  |

|                  | <b>C =</b> 1                                                                                                                          | $W \le k$                |  |  |  |

|                  | DC = 0                                                                                                                                | W<3:0> > k<3:0>          |  |  |  |

|                  | DC = 1 W<3:0> ≤ k<3:0>                                                                                                                |                          |  |  |  |

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                     |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |  |

| Operands:        | None                                                                                                                                                                                                                                 |  |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT}, \\ 0 \rightarrow \text{WDT prescaler}, \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$                                                |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |  |

| Description:     | The power-down Status bit, $\overline{PD}$ is<br>cleared. Time-out Status bit, $\overline{TO}$ is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into Sleep mode<br>with the oscillator stopped. |  |

| SUBWF            | Subtract W from f                                                                                                                                                                          |            |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|

| Syntax:          | [label] SU                                                                                                                                                                                 | JBWF f,d   |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                          |            |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                      |            |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                   |            |  |  |  |

| Description:     | Subtract (2's complement method) W<br>register from register 'f'. If 'd' is '0', the<br>result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f. |            |  |  |  |

|                  | <b>C =</b> 0                                                                                                                                                                               | W > f      |  |  |  |

|                  | C = 1                                                                                                                                                                                      | $W \leq f$ |  |  |  |

|                  | DC = 0 W<3:0> > f<3:0>                                                                                                                                                                     |            |  |  |  |

$W<3:0> \le f<3:0>$

| SUBWFB           | Subtract W from f with Borrow                                                                                                                                                                       |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | SUBWFB f {,d}                                                                                                                                                                                       |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                  |  |  |  |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                       |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                            |  |  |  |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's comple-<br>ment method). If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |

DC = 1

|                   |        |                                                                                                                                                                                         | Standa     | rd Oper | ating Co   | ondition | s (unless otherwise stated)                                                                                   |

|-------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|------------|----------|---------------------------------------------------------------------------------------------------------------|

| PIC16LF1516/7/8/9 |        | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended                                                        |            |         |            |          |                                                                                                               |

| PIC16F1516/7/8/9  |        | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |            |         |            |          |                                                                                                               |

| Param.<br>No.     | Sym.   | Characteristic                                                                                                                                                                          | Min.       | Тур†    | Max.       | Units    | Conditions                                                                                                    |

| D001              | Vdd    | Supply Voltage (VDDMIN, VDDMAX)                                                                                                                                                         |            |         |            |          |                                                                                                               |

|                   |        |                                                                                                                                                                                         | 1.8<br>2.5 | -       | 3.6<br>3.6 | V<br>V   | Fosc ≤ 16 MHz:<br>Fosc ≤ 20 MHz                                                                               |

| D001              |        |                                                                                                                                                                                         | 2.3<br>2.5 | _       | 5.5<br>5.5 | V<br>V   | Fosc ≤ 16 MHz:<br>Fosc ≤ 20 MHz                                                                               |

| D002*             | Vdr    | VDR RAM Data Retention Voltage <sup>(1)</sup>                                                                                                                                           |            |         |            |          |                                                                                                               |

|                   |        |                                                                                                                                                                                         | 1.5        | -       | _          | V        | Device in Sleep mode                                                                                          |

| D002*             |        |                                                                                                                                                                                         | 1.7        | _       | -          | V        | Device in Sleep mode                                                                                          |

| D002A*            | VPOR   | Power-on Reset Release Voltage                                                                                                                                                          | —          | 1.6     | _          | V        |                                                                                                               |

| D002B*            | VPORR  | Power-on Reset Rearm Voltage                                                                                                                                                            |            |         |            |          |                                                                                                               |

|                   |        |                                                                                                                                                                                         | _          | 0.8     | _          | V        |                                                                                                               |

| D002B*            |        |                                                                                                                                                                                         | _          | 1.42    | _          | V        |                                                                                                               |

| D003              | VADFVR | Fixed Voltage Reference Voltage for ADC                                                                                                                                                 | -8         | _       | 6          | %        | $\begin{array}{l} 1.024V, \ Vdd \geq 2.5V \\ 2.048V, \ Vdd \geq 2.5V \\ 4.096V, \ Vdd \geq 4.75V \end{array}$ |

| D004*             | SVDD   | VDD Rise Rate to ensure internal<br>Power-on Reset signal                                                                                                                               | 0.05       | —       | —          | V/ms     | See Section 6.1 "Power-On Reset (POR)" for details.                                                           |

### 25.3 DC Characteristics: Supply Voltage

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

## TABLE 25-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET PARAMETERS

|              | Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature -40°C $\leq$ TA $\leq$ +125°C |                                                             |                      |                      |                      |             |                                                                         |

|--------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------|----------------------|----------------------|-------------|-------------------------------------------------------------------------|

| Param<br>No. | Sym.                                                                                                           | Characteristic                                              | Min.                 | Тур†                 | Max.                 | Units       | Conditions                                                              |

| 30           | TMCL                                                                                                           | MCLR Pulse Width (low)                                      | 2                    |                      | _                    | μS          |                                                                         |

| 31           | TWDTLP                                                                                                         | Low-Power Watchdog Timer<br>Time-out Period                 | 10                   | 16                   | 27                   | ms          | VDD = 3.3V-5V,<br>1:512 Prescaler used                                  |

| 32           | Tost                                                                                                           | Oscillator Start-up Timer Period <sup>(1)</sup>             |                      | 1024                 | _                    | Tosc        |                                                                         |

| 33*          | TPWRT                                                                                                          | Power-up Timer Period, $\overline{PWRTE} = 0$               | 40                   | 65                   | 140                  | ms          |                                                                         |

| 34*          | Tioz                                                                                                           | I/O high-impedance from MCLR Low<br>or Watchdog Timer Reset | _                    | —                    | 2.0                  | μS          |                                                                         |

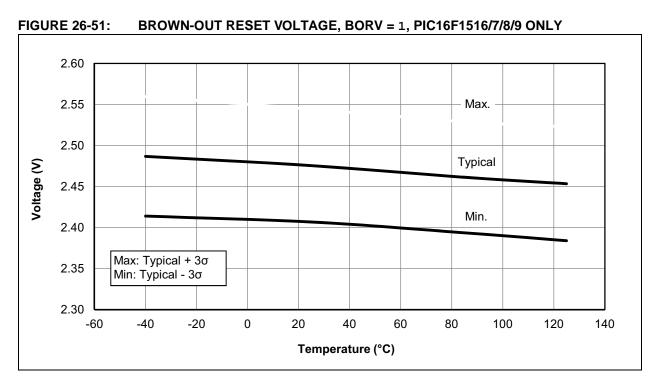

| 35           | VBOR                                                                                                           | Brown-out Reset Voltage <sup>(2)</sup>                      | 2.55<br>2.35<br>1.80 | 2.70<br>2.45<br>1.90 | 2.85<br>2.58<br>2.00 | V<br>V<br>V | BORV = 0<br>BORV = 1 (PIC16F1516/7/8/9)<br>BORV = 1 (PIC16LF1516/7/8/9) |

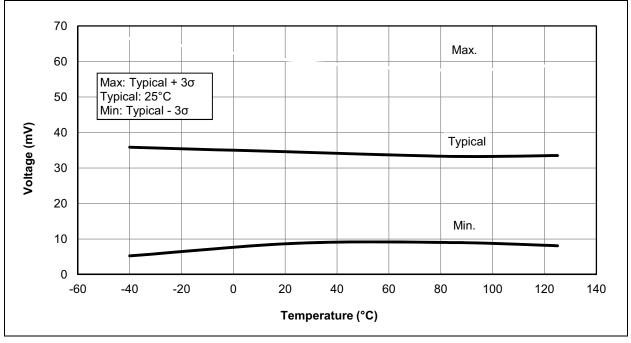

| 36*          | VHYST                                                                                                          | Brown-out Reset Hysteresis                                  | 0                    | 25                   | 60                   | mV          | -40°C to +85°C                                                          |

| 37*          | TBORDC                                                                                                         | Brown-out Reset DC Response<br>Time                         | 1                    | 3                    | 35                   | μS          | $VDD \leq VBOR$                                                         |

| 38           | Vlpbor                                                                                                         | Low-Power Brown-out Reset<br>Voltage                        | 1.8                  | 2.1                  | 2.5                  | V           | LPBOR = 0                                                               |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: By design, the Oscillator Start-up Timer (OST) counts the first 1024 cycles, independent of frequency.

2: To ensure these voltage tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1 μF and 0.01 μF values in parallel are recommended.

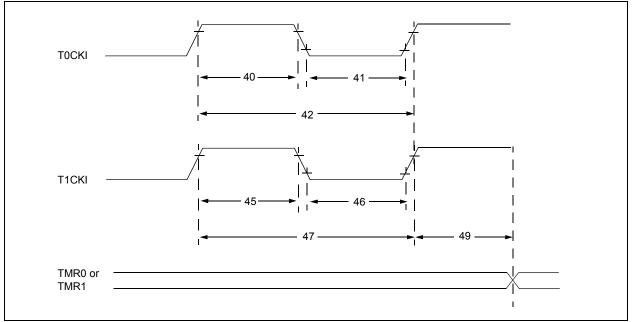

#### FIGURE 25-10: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

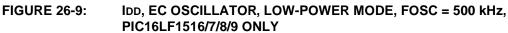

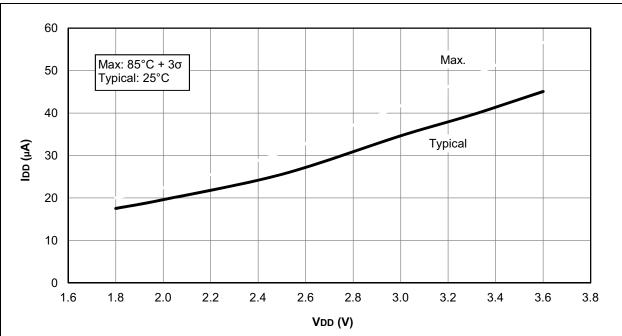

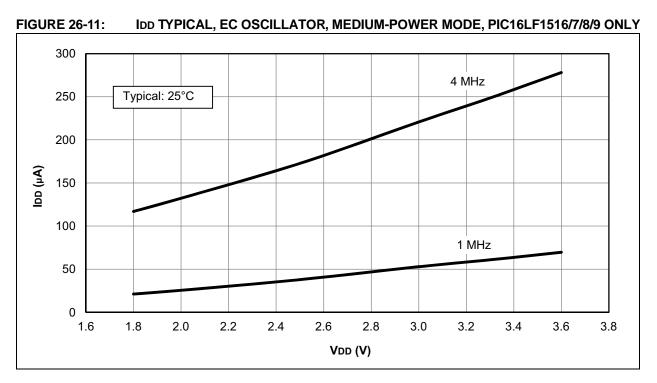

FIGURE 26-10: IDD, EC OSCILLATOR, LOW-POWER MODE, FOSC = 500 kHz, PIC16F1516/7/8/9 ONLY

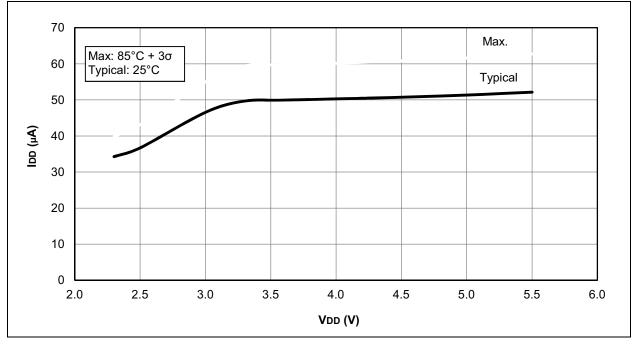

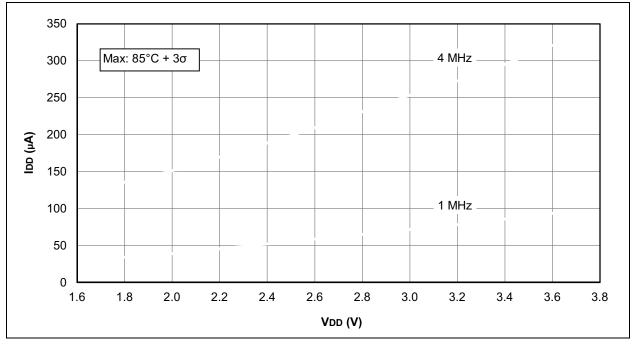

FIGURE 26-12: IDD MAXIMUM, EC OSCILLATOR, MEDIUM-POWER MODE, PIC16LF1516/7/8/9 ONLY

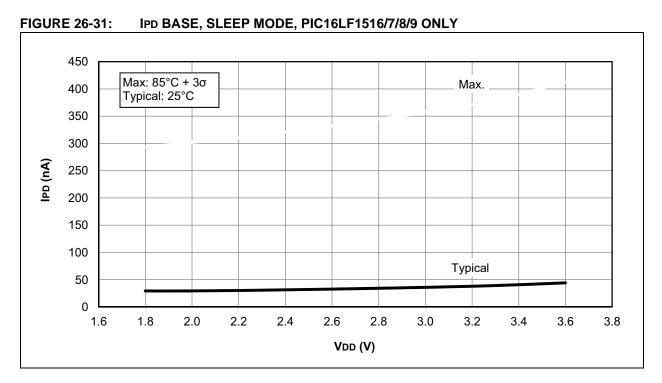

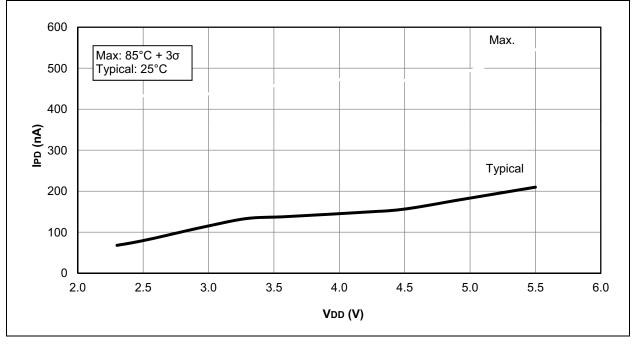

FIGURE 26-32: IPD BASE, LOW-POWER SLEEP MODE (VREGPM = 1), PIC16F1516/7/8/9 ONLY

FIGURE 26-52: BROWN-OUT RESET HYSTERESIS, BORV = 1, PIC16F1516/7/8/9 ONLY

### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | [X] <sup>(1)</sup> - <u>X</u> /XX                                                                                                                                                   | XXX<br>Pattern | Examples:<br>a) PIC16F1516T - I/MV 301<br>Tape and Reel,<br>Industrial temperature,<br>UQFN package,                                                                                                                                                                                                                                                                                                                               |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                  | PIC16F1516, PIC16LF1516<br>PIC16F1517, PIC16LF1517<br>PIC16F1518, PIC16LF1518<br>PIC16F1519, PIC16LF1519                                                                            |                | QTP pattern #301<br>b) PIC16F1519 - I/P<br>Industrial temperature<br>PDIP package<br>c) PIC16F1518 - E/SS<br>Extended temperature,                                                                                                                                                                                                                                                                                                 |