#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1518-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

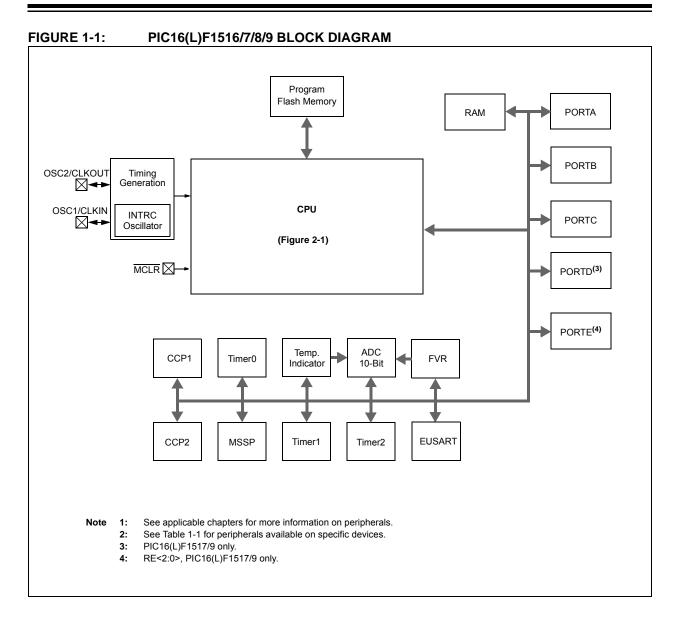

# PIC16(L)F1516/7/8/9

#### TABLE 3-4: PIC16(L)F1518/9 MEMORY MAP

|      | BANK 0                                     | •    | ,<br>BANK 1                                |      | BANK 2                                     |      | BANK 3                                     |      | BANK 4                                     |      | BANK 5                                     |      | BANK 6                                     |      | BANK 7                                     |

|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|

| 000h |                                            | 080h |                                            | 100h |                                            | 180h |                                            | 200h |                                            | 280h |                                            | 300h |                                            | 380h |                                            |

|      | Core Registers<br>(Table 3-2)              |

| 00Bh |                                            | 08Bh |                                            | 10Bh |                                            | 18Bh |                                            | 20Bh |                                            | 28Bh |                                            | 30Bh |                                            | 38Bh |                                            |

| 00Ch | PORTA                                      | 08Ch | TRISA                                      | 10Ch | LATA                                       | 18Ch | ANSELA                                     | 20Ch | _                                          | 28Ch | —                                          | 30Ch | _                                          | 38Ch | _                                          |

| 00Dh | PORTB                                      | 08Dh | TRISB                                      | 10Dh | LATB                                       | 18Dh | ANSELB                                     | 20Dh | WPUB                                       | 28Dh | _                                          | 30Dh | —                                          | 38Dh | —                                          |

| 00Eh | PORTC                                      | 08Eh | TRISC                                      | 10Eh | LATC                                       | 18Eh | ANSELC                                     | 20Eh | _                                          | 28Eh | _                                          | 30Eh | _                                          | 38Eh | —                                          |

| 00Fh | PORTD <sup>(1)</sup>                       | 08Fh | TRISD <sup>(1)</sup>                       | 10Fh | LATD <sup>(1)</sup>                        | 18Fh | ANSELD <sup>(1)</sup>                      | 20Fh | _                                          | 28Fh | _                                          | 30Fh | _                                          | 38Fh | _                                          |

| 010h | PORTE                                      | 090h | TRISE                                      | 110h | LATE <sup>(1)</sup>                        | 190h | ANSELE <sup>(1)</sup>                      | 210h | WPUE                                       | 290h |                                            | 310h | _                                          | 390h | _                                          |

| 011h | PIR1                                       | 091h | PIE1                                       | 111h | —                                          | 191h | PMADRL                                     | 211h | SSPBUF                                     | 291h | CCPR1L                                     | 311h | —                                          | 391h | —                                          |

| 012h | PIR2                                       | 092h | PIE2                                       | 112h | —                                          | 192h | PMADRH                                     | 212h | SSPADD                                     | 292h | CCPR1H                                     | 312h | _                                          | 392h | —                                          |

| 013h | —                                          | 093h | —                                          | 113h | _                                          | 193h | PMDATL                                     | 213h | SSPMSK                                     | 293h | CCP1CON                                    | 313h | —                                          | 393h | _                                          |

| 014h | —                                          | 094h | —                                          | 114h |                                            | 194h | PMDATH                                     | 214h | SSPSTAT                                    | 294h | —                                          | 314h | —                                          | 394h | IOCBP                                      |

| 015h | TMR0                                       | 095h | OPTION_REG                                 | 115h | —                                          | 195h | PMCON1                                     | 215h | SSPCON1                                    | 295h | —                                          | 315h | —                                          | 395h | IOCBN                                      |

| 016h | TMR1L                                      | 096h | PCON                                       | 116h | BORCON                                     | 196h | PMCON2                                     | 216h | SSPCON2                                    | 296h | —                                          | 316h | —                                          | 396h | IOCBF                                      |

| 017h | TMR1H                                      | 097h | WDTCON                                     | 117h | FVRCON                                     | 197h | VREGCON <sup>(2)</sup>                     | 217h | SSPCON3                                    | 297h | —                                          | 317h | _                                          | 397h | _                                          |

| 018h | T1CON                                      | 098h | —                                          | 118h |                                            | 198h | _                                          | 218h | —                                          | 298h | CCPR2L                                     | 318h | —                                          | 398h | —                                          |

| 019h | T1GCON                                     | 099h | OSCCON                                     | 119h | _                                          | 199h | RCREG                                      | 219h | —                                          | 299h | CCPR2H                                     | 319h | —                                          | 399h | —                                          |

| 01Ah | TMR2                                       | 09Ah | OSCSTAT                                    | 11Ah | _                                          | 19Ah | TXREG                                      | 21Ah | —                                          | 29Ah | CCP2CON                                    | 31Ah | —                                          | 39Ah | _                                          |

| 01Bh | PR2                                        | 09Bh | ADRESL                                     | 11Bh | —                                          | 19Bh | SPBRG                                      | 21Bh | _                                          | 29Bh | —                                          | 31Bh | _                                          | 39Bh | _                                          |

| 01Ch | T2CON                                      | 09Ch | ADRESH                                     | 11Ch | _                                          | 19Ch | SPBRGH                                     | 21Ch | —                                          | 29Ch | —                                          | 31Ch | —                                          | 39Ch | —                                          |

| 01Dh | —                                          | 09Dh | ADCON0                                     | 11Dh | APFCON                                     | 19Dh | RCSTA                                      | 21Dh | —                                          | 29Dh | —                                          | 31Dh | —                                          | 39Dh | —                                          |

| 01Eh | —                                          | 09Eh | ADCON1                                     | 11Eh | _                                          | 19Eh | TXSTA                                      | 21Eh | —                                          | 29Eh | —                                          | 31Eh | —                                          | 39Eh | —                                          |

| 01Fh | —                                          | 09Fh | —                                          | 11Fh | —                                          | 19Fh | BAUDCON                                    | 21Fh | _                                          | 29Fh | _                                          | 31Fh | _                                          | 39Fh | _                                          |

| 020h |                                            | 0A0h |                                            | 120h |                                            | 1A0h |                                            | 220h |                                            | 2A0h |                                            | 320h |                                            | 3A0h |                                            |

|      | General<br>Purpose<br>Register<br>80 Bytes |

| 06Fh |                                            | 0EFh |                                            | 16Fh |                                            | 1EFh |                                            | 26Fh |                                            | 2EFh |                                            | 36Fh |                                            | 3EFh |                                            |

| 070h |                                            | 0F0h |                                            | 170h |                                            | 1F0h |                                            | 270h |                                            | 2F0h |                                            | 370h |                                            | 3F0h |                                            |

|      | Common RAM                                 |      | Accesses<br>70h – 7Fh                      |

| 07Fh |                                            | 0FFh |                                            | 17Fh |                                            | 1FFh |                                            | 27Fh |                                            | 2FFh |                                            | 37Fh |                                            | 3FFh |                                            |

Legend:

= Unimplemented data memory locations, read as '0'.

Note

1:

DSTEMP only.

2:

PIC16F1518/9 only.

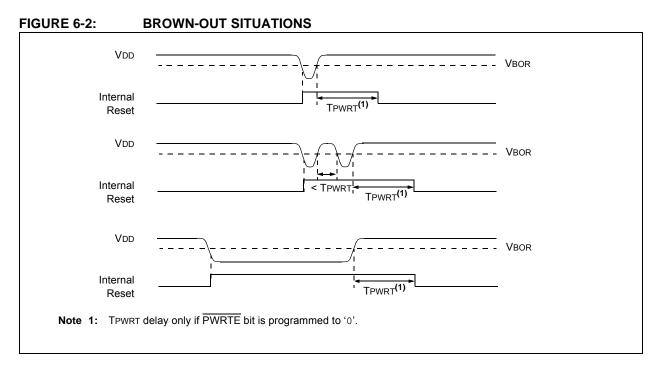

### 6.3 Register Definitions: BOR Control

#### REGISTER 6-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u     | R/W-0/u | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |  |

|-------------|---------|-----|-----|-----|-----|-----|--------|--|

| SBOREN      | BORFS   | —   | —   | —   | —   | —   | BORRDY |  |

| bit 7 bit 0 |         |     |     |     |     |     |        |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-out Reset Enable bit <sup>(1)</sup> If BOREN <1:0> in Configuration Words ≠ 01: SBOREN is read/write, but has no effect on the BOR If BOREN <1:0> in Configuration Words = 01: 1 = BOR Enabled 0 = BOR Disabled                                                                                                                                                                                                                            |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | <ul> <li>BORFS: Brown-out Reset Fast Start bit<sup>(1)</sup></li> <li>If BOREN&lt;1:0&gt; = 11 (Always on) or BOREN&lt;1:0&gt; = 00 (Always off)</li> <li>BORFS is Read/Write, but has no effect.</li> <li>If BOREN &lt;1:0&gt; = 10 (Disabled in Sleep) or BOREN&lt;1:0&gt; = 01 (Under software control):</li> <li>1 = Band gap is forced on always (covers sleep/wake-up/operating cases)</li> <li>0 = Band gap operates normally, and may turn off</li> </ul> |

| bit 5-1 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bit 0   | <b>BORRDY:</b> Brown-out Reset Circuit Ready Status bit<br>1 = The Brown-out Reset circuit is active<br>0 = The Brown-out Reset circuit is inactive                                                                                                                                                                                                                                                                                                               |

**Note 1:** BOREN<1:0> bits are located in Configuration Words.

| R/W-0/0          | R/W-0/0       | R/W-0/0                                                                                           | R/W-0/0        | R/W-0/0         | R/W-0/0          | R/W-0/0  | R/W-0/0     |  |  |  |  |

|------------------|---------------|---------------------------------------------------------------------------------------------------|----------------|-----------------|------------------|----------|-------------|--|--|--|--|

| TMR1GIE          | ADIE          | RCIE                                                                                              | TXIE           | SSPIE           | CCP1IE           | TMR2IE   | TMR1IE      |  |  |  |  |

| bit 7            |               |                                                                                                   |                |                 |                  |          | bit         |  |  |  |  |

| Legend:          |               |                                                                                                   |                |                 |                  |          |             |  |  |  |  |

| R = Readable     | bit           | W = Writable                                                                                      | bit            | U = Unimpler    | mented bit, read | l as '0' |             |  |  |  |  |

| u = Bit is unch  |               | x = Bit is unkr                                                                                   |                | •               | at POR and BO    |          | ther Resets |  |  |  |  |

| '1' = Bit is set | 0.1           | '0' = Bit is clea                                                                                 | ared           |                 |                  |          |             |  |  |  |  |

|                  |               |                                                                                                   |                |                 |                  |          |             |  |  |  |  |

| bit 7            |               | mer1 Gate Inte                                                                                    | •              |                 |                  |          |             |  |  |  |  |

|                  |               | the Timer1 Gate<br>the Timer1 Gat                                                                 |                |                 |                  |          |             |  |  |  |  |

| bit 6            | ADIE: Analog  | g-to-Digital Con                                                                                  | verter (ADC)   | Interrupt Enabl | le bit           |          |             |  |  |  |  |

|                  |               | the ADC interru                                                                                   |                |                 |                  |          |             |  |  |  |  |

|                  |               | the ADC interru                                                                                   | -              |                 |                  |          |             |  |  |  |  |

| bit 5            |               | T Receive Inter                                                                                   | •              | it              |                  |          |             |  |  |  |  |

|                  |               | Enables the USART receive interrupt<br>Disables the USART receive interrupt                       |                |                 |                  |          |             |  |  |  |  |

| bit 4            |               |                                                                                                   | -              | it              |                  |          |             |  |  |  |  |

|                  |               | <b>FXIE:</b> USART Transmit Interrupt Enable bit         - = Enables the USART transmit interrupt |                |                 |                  |          |             |  |  |  |  |

|                  | 0 = Disables  | the USART tra                                                                                     | nsmit interrup | t               |                  |          |             |  |  |  |  |

| bit 3            |               | hronous Serial                                                                                    | . ,            | Interrupt Enabl | le bit           |          |             |  |  |  |  |

|                  |               | the MSSP inter                                                                                    |                |                 |                  |          |             |  |  |  |  |

| hit O            |               | the MSSP inter                                                                                    |                |                 |                  |          |             |  |  |  |  |

| bit 2            |               | P1 Interrupt En<br>the CCP1 interr                                                                |                |                 |                  |          |             |  |  |  |  |

|                  |               | the CCP1 inter                                                                                    |                |                 |                  |          |             |  |  |  |  |

| bit 1            |               | R2 to PR2 Mate                                                                                    |                | nable bit       |                  |          |             |  |  |  |  |

|                  |               | the Timer2 to P                                                                                   |                |                 |                  |          |             |  |  |  |  |

|                  |               | the Timer2 to F                                                                                   |                | •               |                  |          |             |  |  |  |  |

| bit 0            |               | er1 Overflow Ir                                                                                   |                |                 |                  |          |             |  |  |  |  |

|                  |               | the Timer1 over                                                                                   |                |                 |                  |          |             |  |  |  |  |

|                  |               | the Timer1 ove                                                                                    | mow interrupt  |                 |                  |          |             |  |  |  |  |

| Note: Bit        |               | TCON register                                                                                     | must he        |                 |                  |          |             |  |  |  |  |

|                  | to enable any |                                                                                                   |                |                 |                  |          |             |  |  |  |  |

#### REGISTER 7-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

#### 8.0 POWER-DOWN MODE (SLEEP)

The Power-Down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3. TO bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 and peripherals that operate from Timer1 continue operation in Sleep when the Timer1 clock source selected is:

- LFINTOSC

- T1CKI

- Secondary oscillator

- 7. ADC is unaffected, if the dedicated FRC oscillator is selected.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

- 9. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- · Internal circuitry sourcing current from I/O pins

- · Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- · Modules using secondary oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include the FVR module. See **Section 14.0 "Fixed Voltage Reference (FVR)"** for more information on this module.

#### 8.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 6.12 "Determining the Cause of a Reset"**.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

#### 12.4 PORTC Registers

#### 12.4.1 DATA REGISTER

PORTC is a 8-bit wide bidirectional port. The corresponding data direction register is TRISC (Register 12-12). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 12-11) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

#### 12.4.2 DIRECTION CONTROL

The TRISC register (Register 12-12) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 12.4.3 ANALOG CONTROL

The ANSELC register (Register 12-14) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELC bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELC bits has no effect on digital output functions. A pin with TRIS clear and ANSELC set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELC bits default to the Analog        |  |  |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|--|--|

|       | mode after Reset. To use any pins as         |  |  |  |  |  |  |  |  |

|       | digital general purpose or peripheral        |  |  |  |  |  |  |  |  |

|       | inputs, the corresponding ANSEL bits         |  |  |  |  |  |  |  |  |

|       | must be initialized to '0' by user software. |  |  |  |  |  |  |  |  |

## 12.4.4 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each PORTC pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-7.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in the priority list.

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RC0      | SOSCO<br>RC0                     |

| RC1      | SOSCI<br>CCP2<br>RC1             |

| RC2      | CCP1<br>RC2                      |

| RC3      | SCL<br>SCK<br>RC3 <sup>(2)</sup> |

| RC4      | SDA<br>RC4 <sup>(2)</sup>        |

| RC5      | SDO<br>RC5                       |

| RC6      | CK<br>TX<br>RC6                  |

| RC7      | DT<br>RC7                        |

| TABLE 12-7: | PORTC OUTPUT PRIORITY |

|-------------|-----------------------|

|-------------|-----------------------|

Note 1: Priority listed from highest to lowest.

**2:** RC3 and RC4 read the  $I^2C$  ST input when  $I^2C$  mode is enabled.

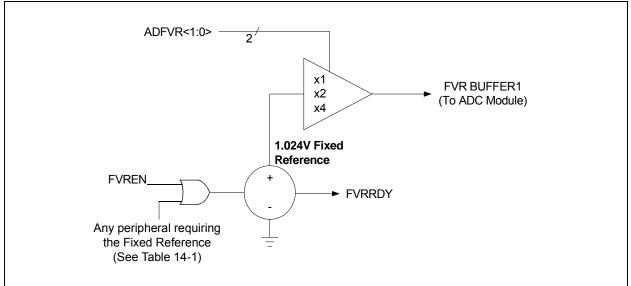

#### 14.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- · ADC positive reference

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

#### 14.1 Independent Gain Amplifiers

The output of the FVR supplied to the ADC module is routed through a programmable gain amplifier. The amplifier can be configured to amplify the reference voltage by 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 16.0** "**Analog-to-Digital Converter** (**ADC**) **Module**" for additional information.

To minimize current consumption when the FVR is disabled, the FVR buffers should be turned off by clearing the Buffer Gain Selection bits.

#### 14.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set. See **Section 25.0** "**Electrical Specifications**" for the minimum delay requirement.

#### FIGURE 14-1: VOLTAGE REFERENCE BLOCK DIAGRAM

#### TABLE 14-1: PERIPHERALS REQUIRING THE FIXED VOLTAGE REFERENCE (FVR)

| Peripheral | Conditions                                                        | Description                                                        |

|------------|-------------------------------------------------------------------|--------------------------------------------------------------------|

| HFINTOSC   | FOSC<2:0> = 100 and<br>IRCF<3:0> = 000x                           | INTOSC is active and device is not in Sleep                        |

|            | BOREN<1:0> = 11                                                   | BOR always enabled                                                 |

| BOR        | BOREN<1:0> = 10 and BORFS = 1                                     | BOR disabled in Sleep mode, BOR Fast Start enabled.                |

|            | BOREN<1:0> = 01 and BORFS = 1                                     | BOR under software control, BOR Fast Start enabled                 |

| LDO        | All PIC16F1516/7/8/9 devices, when<br>VREGPM = 1 and not in Sleep | The device runs off of the low-power regulator when in Sleep mode. |

© 2010-2016 Microchip Technology Inc.

#### 18.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

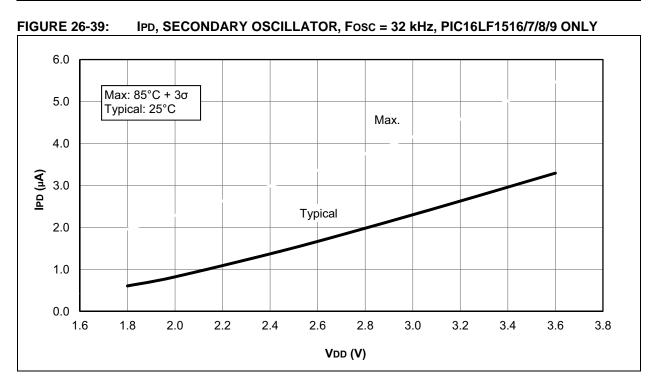

#### 18.4 Secondary Oscillator

Timer1 uses the low-power secondary oscillator circuit on pins SOSCI and SOSCO. The secondary oscillator is designed to use an external 32.768 kHz crystal.

The secondary oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

#### 18.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 18.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

Note: When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

#### 18.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

#### 18.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

#### 18.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 18-3 for timing details.

TABLE 18-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

#### 18.6.2 TIMER1 GATE SOURCE SELECTION

The Timer1 gate source can be selected from one of four different sources. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

#### 19.1 Timer2 Operation

The clock input to the Timer2 modules is the system instruction clock (Fosc/4).

TMR2 increments from 00h on each clock edge.

A 4-bit counter/prescaler on the clock input allows direct input, divide-by-4 and divide-by-16 prescale options. These options are selected by the prescaler control bits, T2CKPS<1:0> of the T2CON register. The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/postscaler (see Section 19.2 "Timer2 Interrupt").

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, whereas the PR2 register initializes to FFh. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- a write to the T2CON register

- · Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- · Watchdog Timer (WDT) Reset

- Stack Overflow Reset

- Stack Underflow Reset

- RESET Instruction

Note: TMR2 is not cleared when T2CON is written.

#### **19.2 Timer2 Interrupt**

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2-to-PR2 match) provides the input for the 4-bit counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF of the PIR1 register. The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE of the PIE1 register.

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0>, of the T2CON register.

#### 19.3 Timer2 Output

The unscaled output of TMR2 is available primarily to the CCP1 module, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP module operating in SPI mode. Additional information is provided in Section 21.0 "Master Synchronous Serial Port (MSSP) Module"

#### 19.4 Timer2 Operation During Sleep

Timer2 cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and PR2 registers will remain unchanged while the processor is in Sleep mode.

| Name    | Bit 7                         | Bit 6                             | Bit 5        | Bit 4             | Bit 3 | Bit 2      | Bit 1  | Bit 0  | Register<br>on Page |  |

|---------|-------------------------------|-----------------------------------|--------------|-------------------|-------|------------|--------|--------|---------------------|--|

| CCP1CON | —                             | —                                 | DC1B         | <1:0>             |       | CCP1M<3:0> |        |        |                     |  |

| CCP2CON | —                             | —                                 | DC2B         | 3<1:0> CCP2M<3:0> |       |            |        |        | 168                 |  |

| INTCON  | GIE                           | PEIE                              | TMR0IE       | INTE              | IOCIE | TMR0IF     | INTF   | IOCIF  | 74                  |  |

| PIE1    | TMR1GIE                       | ADIE                              | RCIE         | TXIE              | SSPIE | CCP1IE     | TMR2IE | TMR1IE | 75                  |  |

| PIR1    | TMR1GIF                       | ADIF                              | RCIF         | TXIF              | SSPIF | CCP1IF     | TMR2IF | TMR1IF | 77                  |  |

| PR2     | Timer2 Module Period Register |                                   |              |                   |       |            |        |        |                     |  |

| T2CON   | _                             | - T2OUTPS<3:0> TMR2ON T2CKPS<1:0> |              |                   |       |            |        |        |                     |  |

| TMR2    | Holding Re                    | gister for the                    | e 8-bit TMR2 | 2 Register        |       |            |        |        | 158*                |  |

#### TABLE 19-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module.

\* Page provides register information.

# PIC16(L)F1516/7/8/9

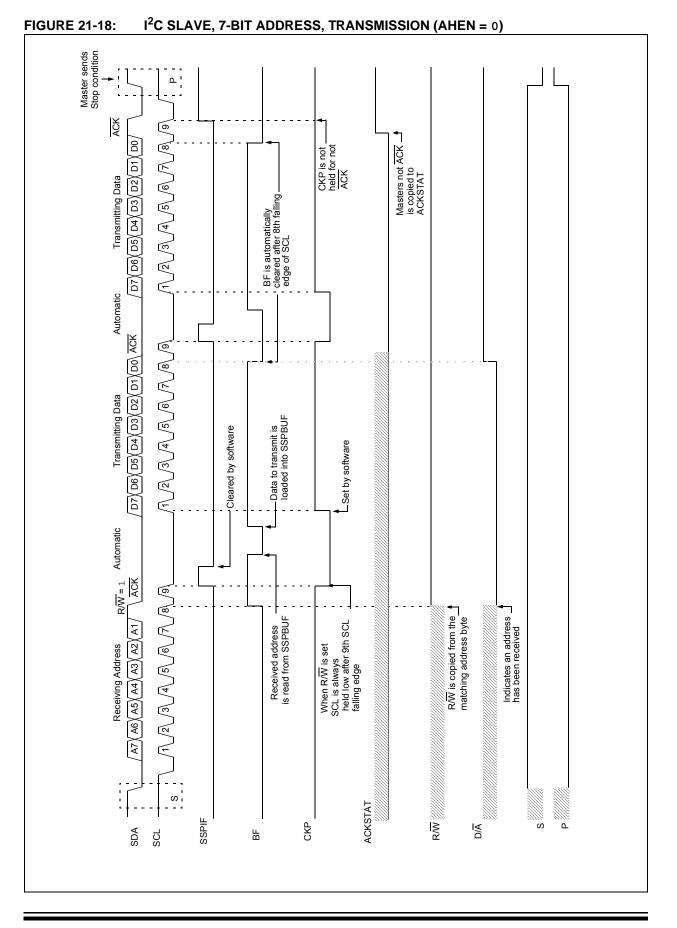

The I<sup>2</sup>C interface supports the following modes and features:

- · Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited Multi-master support

- 7-bit and 10-bit addressing

- · Start and Stop interrupts

- Interrupt masking

- Clock stretching

- · Bus collision detection

- · General call address matching

- Address masking

- · Address Hold and Data Hold modes

- Selectable SDA hold times

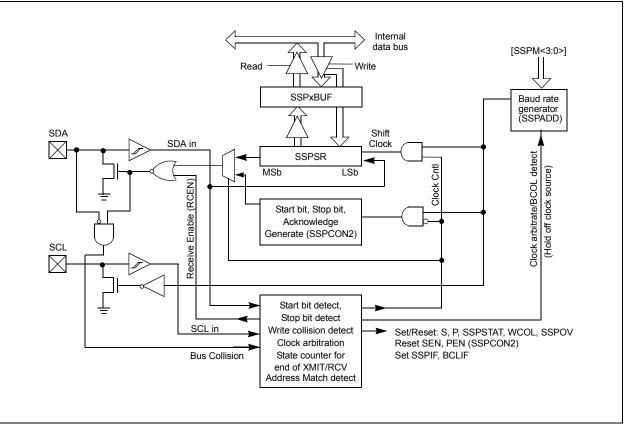

Figure 21-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 21-3 is a diagram of the  $I^2C$  interface module in Slave mode.

#### FIGURE 21-2: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

#### 21.2.4 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit of the SSPCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCK pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

#### 21.2.4.1 Daisy-Chain Configuration

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 21-7 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPCON3 register will enable writes to the SSPBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

#### 21.2.5 SLAVE SELECT SYNCHRONIZATION

The Slave Select can also be used to synchronize communication. The Slave Select line is held high until the master device is ready to communicate. When the Slave Select line is pulled low, the slave knows that a new transmission is starting.

If the slave fails to receive the communication properly, it will be reset at the end of the transmission, when the Slave Select line returns to a high state. The slave is then ready to receive a new transmission when the Slave Select line is pulled low again. If the Slave Select line is not used, there is a risk that the slave will eventually become out of sync with the master. If the slave misses a bit, it will always be one bit off in future transmissions. Use of the Slave Select line allows the slave and master to align themselves at the beginning of each transmission.

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 0100).

When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven.

When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When the SPI is in Slave mode with $\overline{SS}$ pin<br>control enabled (SSPCON1<3:0> =<br>0100), the SPI module will reset if the $\overline{SS}$<br>pin is set to VDD. |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | When the SPI is used in Slave mode with CKE set; the user must enable $\overline{SS}$ pin control.                                                                         |

**3:** While operated in SPI Slave mode the SMP bit of the SSPSTAT register must remain clear.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

#### 21.2.6 SPI OPERATION IN SLEEP MODE

In SPI Master mode, module clocks may be operating at a different speed than when in Full-Power mode; in the case of the Sleep mode, all clocks are halted.

Special care must be taken by the user when the MSSP clock is much faster than the system clock.

In Slave mode, when MSSP interrupts are enabled, after the master completes sending data, an MSSP interrupt will wake the controller from Sleep.

If an exit from Sleep mode is not desired, MSSP interrupts should be disabled.

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

| Name    | Bit 7                                                    | Bit 6                     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|----------------------------------------------------------|---------------------------|--------|--------|--------|--------|--------|---------|---------------------|

| ANSELA  | —                                                        |                           | ANSA5  | -      | ANSA3  | ANSA2  | ANSA1  | ANSA0   | 108                 |

| ANSELC  | SELC ANSC7                                               |                           | ANSC5  | ANSC4  | ANSC3  | ANSC2  | _      | _       | 115                 |

| APFCON  | _                                                        |                           | -      | -      | _      | —      | SSSEL  | CCP2SEL | 105                 |

| INTCON  | GIE                                                      | PEIE                      | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF   | 74                  |

| PIE1    | TMR1GIE                                                  | ADIE                      | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE  | 75                  |

| PIR1    | TMR1GIF                                                  | ADIF                      | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF  | 77                  |

| SSPBUF  | Synchronous Serial Port Receive Buffer/Transmit Register |                           |        |        |        |        |        |         | 172*                |

| SSPCON1 | WCOL                                                     | SSPOV SSPEN CKP SSPM<3:0> |        |        |        |        |        | 216     |                     |

| SSPCON3 | ACKTIM                                                   | PCIE                      | SCIE   | BOEN   | SDAHT  | SBCDE  | AHEN   | DHEN    | 218                 |

| SSPSTAT | SMP                                                      | CKE                       | D/A    | Р      | S      | R/W    | UA     | BF      | 215                 |

| TRISA   | TRISA7                                                   | TRISA6                    | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0  | 107                 |

| TRISC   | TRISC7                                                   | TRISC6                    | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0  | 114                 |

#### TABLE 21-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

\* Page provides register information.

| TABLE 21-1:         | I-C BUS TERMS                                                                                                                                                                         |  |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Term                | Description                                                                                                                                                                           |  |  |  |  |  |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                        |  |  |  |  |  |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                         |  |  |  |  |  |

| Master              | The device that initiates a transfer,<br>generates clock signals and termi-<br>nates a transfer.                                                                                      |  |  |  |  |  |

| Slave               | The device addressed by the mas-<br>ter.                                                                                                                                              |  |  |  |  |  |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                     |  |  |  |  |  |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                   |  |  |  |  |  |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                |  |  |  |  |  |

| Idle                | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                          |  |  |  |  |  |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                          |  |  |  |  |  |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                          |  |  |  |  |  |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPADD.                                                                                                    |  |  |  |  |  |

| Write Request       | Slave receives a matching address with R/W bit clear, and is ready to clock in data.                                                                                                  |  |  |  |  |  |

| Read Request        | Master sends an address byte with the $R/W$ bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |  |  |  |  |  |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                         |  |  |  |  |  |

| Bus Collision       | Any time the SDA line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                            |  |  |  |  |  |

#### TABLE 21-1: I<sup>2</sup>C BUS TERMS

#### 21.4.5 START CONDITION

The  $I^2C$  specification defines a Start condition as a transition of SDA from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 21-12 shows wave forms for Start and Stop conditions.

A bus collision can occur on a Start condition if the module samples the SDA line low before asserting it low. This does not conform to the  $I^2C$  Specification that states no bus collision can occur on a Start.

#### 21.4.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

| Note: | At least one SCL low time must appear         |

|-------|-----------------------------------------------|

|       | before a Stop is valid, therefore, if the SDA |

|       | line goes low then high again while the SCL   |

|       | line stays high, only the Start condition is  |

|       | detected.                                     |

#### 21.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 21-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the  $R/\overline{W}$  bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with  $R/\overline{W}$  clear in 10-bit mode, a prior match flag is set and maintained. Until a Stop condition, a high address with  $R/\overline{W}$  clear, or high address match fails.

#### 21.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

## PIC16(L)F1516/7/8/9

#### 21.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high. When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the 8th bit is shifted out (the falling edge of the 8th clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an  $\overline{ACK}$  bit during the 9th bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKSTAT bit on the rising edge of the 9th clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the 9th clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 21-28).

After the write to the SSPBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the 8th clock, the master will release the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the 9th clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPCON2 register. Following the falling edge of the 9th clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 21.6.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPSTAT register is set when the CPU writes to SSPBUF and is cleared when all eight bits are shifted out.

#### 21.6.6.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

WCOL must be cleared by software before the next transmission.

#### 21.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPCON2 register is cleared when the slave has sent an Acknowledge (ACK = 0) and is set when the slave does not Acknowledge (ACK = 1). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

21.6.6.4 Typical transmit sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPCON2 register.

- 2. SSPIF is set by hardware on completion of the Start.

- 3. SSPIF is cleared by software.

- 4. The MSSP module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPBUF with the slave address to transmit.

- 6. Address is shifted out the SDA pin until all 8 bits are transmitted. Transmission begins as soon as SSPBUF is written to.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPCON2 register.

- 8. The MSSP module generates an interrupt at the end of the 9th clock cycle by setting the SSPIF bit.

- 9. The user loads the SSPBUF with eight bits of data.

- 10. Data is shifted out the SDA pin until all eight bits are transmitted.

- 11. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- 13. The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPCON2 register. Interrupt is generated once the Stop/Restart condition is complete.

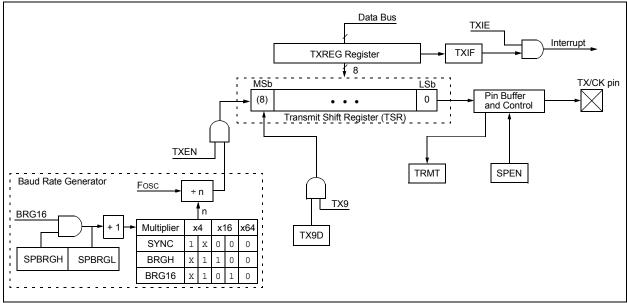

### 22.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- · Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 22-1 and Figure 22-2.

#### FIGURE 22-1: EUSART TRANSMIT BLOCK DIAGRAM

#### 22.5.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 22.5.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 22.5.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 22.5.2.2 Synchronous Slave Transmission Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant 8 bits to the TXREG register.

#### TABLE 22-7: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Name    | Bit 7                         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                        | RCIDL  | —      | SCKP   | BRG16  | —      | WUE    | ABDEN  | 232                 |

| INTCON  | GIE                           | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 74                  |

| PIE1    | TMR1GIE                       | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 75                  |

| PIR1    | TMR1GIF                       | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 77                  |

| RCSTA   | SPEN                          | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 231                 |

| TRISC   | TRISC7                        | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 114                 |

| TXREG   | EUSART Transmit Data Register |        |        |        |        |        |        |        | 222*                |

| TXSTA   | CSRC                          | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 230                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

\* Page provides register information.

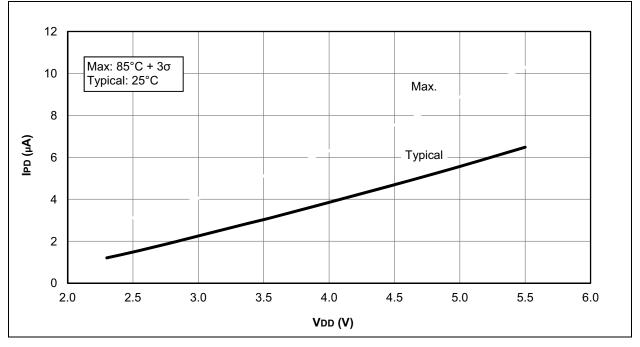

| 25.4 | DC Characteristics: | Supply | Current ( | IDD) |

|------|---------------------|--------|-----------|------|

|------|---------------------|--------|-----------|------|

| PIC16LF1516/7/8/9 |                                     |                       | Standard Operating Cond<br>Operating temperature |      |                                                                                                                               | litions (unless otherwise stated)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                                         |  |

|-------------------|-------------------------------------|-----------------------|--------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|

| PIC16F1516/7/8/9  |                                     | Operating temperature |                                                  |      | itions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |                                                                                                                                                    |                                                         |  |

| Param             | Device                              | Mi                    |                                                  |      |                                                                                                                               | Conditions                                                                                                                                         |                                                         |  |

| No.               | Characteristics                     | Min.                  | Тур†                                             | Max. | Units                                                                                                                         | VDD                                                                                                                                                | Note                                                    |  |

|                   | Supply Current (IDD) <sup>(1,</sup> | 2, 3)                 |                                                  |      |                                                                                                                               |                                                                                                                                                    |                                                         |  |

| D010              |                                     | —                     | 8.0                                              | 14   | μA                                                                                                                            | 1.8                                                                                                                                                | Fosc = 32 kHz                                           |  |

|                   |                                     | —                     | 12.0                                             | 31   | μA                                                                                                                            | 3.0                                                                                                                                                | LP Oscillator<br>-40°C $\leq$ TA $\leq$ +85°C           |  |

| D010              |                                     |                       | 11                                               | 28   | μA                                                                                                                            | 2.3                                                                                                                                                | Fosc = 32 kHz                                           |  |

|                   |                                     | —                     | 13                                               | 38   | μA                                                                                                                            | 3.0                                                                                                                                                | LP Oscillator<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ |  |

|                   |                                     | —                     | 14                                               | 45   | μA                                                                                                                            | 5.0                                                                                                                                                |                                                         |  |

| D011              |                                     | —                     | 60                                               | 95   | μA                                                                                                                            | 1.8                                                                                                                                                | Fosc = 1 MHz                                            |  |

|                   |                                     | —                     | 110                                              | 180  | μA                                                                                                                            | 3.0                                                                                                                                                | XT Oscillator                                           |  |

| D011              |                                     | _                     | 92                                               | 170  | μA                                                                                                                            | 2.3                                                                                                                                                | Fosc = 1 MHz                                            |  |

|                   |                                     | —                     | 140                                              | 230  | μA                                                                                                                            | 3.0                                                                                                                                                | XT Oscillator                                           |  |

|                   |                                     | —                     | 170                                              | 350  | μA                                                                                                                            | 5.0                                                                                                                                                |                                                         |  |

| D012              |                                     | —                     | 150                                              | 240  | μA                                                                                                                            | 1.8                                                                                                                                                | Fosc = 4 MHz                                            |  |

|                   |                                     | —                     | 260                                              | 430  | μA                                                                                                                            | 3.0                                                                                                                                                | XT Oscillator                                           |  |

| D012              |                                     | —                     | 190                                              | 450  | μA                                                                                                                            | 2.3                                                                                                                                                | Fosc = 4 MHz                                            |  |