Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1518t-i-so |

#### 5.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators that are used to generate the internal system clock sources: the 16 MHz High-Frequency Internal Oscillator and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 5.3** "Clock Switching" for additional information.

#### 5.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Secondary oscillator during run time, or

- An external clock source determined by the value of the FOSC bits.

See Section 5.3 "Clock Switching" for more information.

#### 5.2.1.1 EC Mode

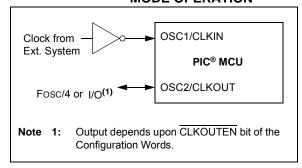

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 5-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- High power, 4-20 MHz (FOSC = 111)

- Medium power, 0.5-4 MHz (FOSC = 110)

- Low power, 0-0.5 MHz (FOSC = 101)

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC® MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

# FIGURE 5-2: EXTERNAL CLOCK (EC) MODE OPERATION

#### 5.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 5-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 5-3 and Figure 5-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

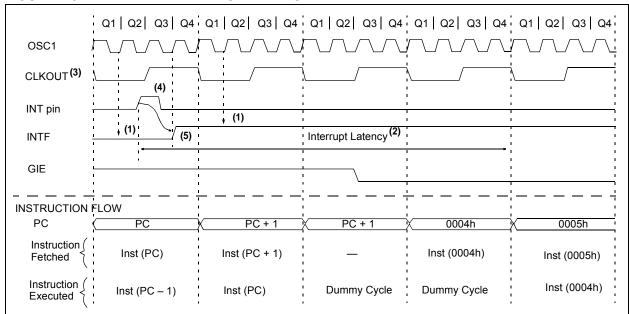

FIGURE 7-3: INT PIN INTERRUPT TIMING

- Note 1: INTF flag is sampled here (every Q1).

- 2: Asynchronous interrupt latency = 3-5 TcY. Synchronous latency = 3-4 TcY, where TcY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT not available in all oscillator modes.

- 4: For minimum width of INT pulse, refer to AC specifications in Section 25.0 "Electrical Specifications".

- 5: INTF is enabled to be set any time during the Q4-Q1 cycles.

### 10.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See Section 25.0 "Electrical Specifications" for the LFINTOSC tolerances.

### 10.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table .

#### 10.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always ON.

WDT protection is active during Sleep.

#### 10.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is ON, except in Sleep.

WDT protection is not active during Sleep.

#### 10.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table for more details

TABLE 10-1: WDT OPERATING MODES

| WDTE<1:0> | SWDTE<br>N | Device<br>Mode | WDT<br>Mode |  |

|-----------|------------|----------------|-------------|--|

| 11        | X          | Х              | Active      |  |

| 1.0       | v          | Awake          | Active      |  |

| 10        | X          | Sleep          | Disabled    |  |

| 0.1       | 1          | X              | Active      |  |

| 01        | 0          | ^              | Disabled    |  |

| 00        | Х          | Х              | Disabled    |  |

#### 10.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

#### 10.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- · Any Reset

- CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- · Oscillator fail

- · WDT is disabled

- · Oscillator Start-up Timer (OST) is running

See Table 10-2 for more information.

### 10.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See Section 5.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register are changed to indicate the event. The  $\overline{\text{RWDT}}$  bit in the PCON register can also be used. See **Section 3.0 "Memory Organization"** and The STATUS register (Register 3-1) for more information.

TABLE 10-2: WDT CLEARING CONDITIONS

| Conditions                                              | WDT                          |

|---------------------------------------------------------|------------------------------|

| WDTE<1:0> = 00                                          |                              |

| WDTE<1:0> = 01 and SWDTEN = 0                           |                              |

| WDTE<1:0> = 10 and enter Sleep                          | Cleared                      |

| CLRWDT Command                                          | Cleared                      |

| Oscillator Fail Detected                                |                              |

| Exit Sleep + System Clock = SOSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                  | Cleared until the end of OST |

| Change INTOSC divider (IRCF bits)                       | Unaffected                   |

#### **EXAMPLE 11-2: ERASING ONE ROW OF PROGRAM MEMORY**

```

; This row erase routine assumes the following:

; 1. A valid address within the erase row is loaded in ADDRH:ADDRL

; 2. ADDRH and ADDRL are located in shared data memory 0x70 - 0x7F (common RAM)

BCF

INTCON, GIE

; Disable ints so required sequences will execute properly

BANKSEL

PMADRI.

; Load lower 8 bits of erase address boundary

MOVF

ADDRL,W

MOVWF

PMADRL

MOVF

ADDRH,W

; Load upper 6 bits of erase address boundary

MOVWF

PMADRH

BCF

PMCON1,CFGS

; Not configuration space

; Specify an erase operation

PMCON1,FREE

BSF

BSF

PMCON1, WREN

; Enable writes

MOVLW

55h

; Start of required sequence to initiate erase

; Write 55h

MOVWF

PMCON2

MOVLW

0AAh

MOVWF

PMCON2

; Write AAh

BSF

PMCON1,WR

; Set WR bit to begin erase

NOP

; NOP instructions are forced as processor starts

NOP

; row erase of program memory.

; The processor stalls until the erase process is complete

; after erase processor continues with 3rd instruction

BCF

PMCON1,WREN

; Disable writes

BSF

INTCON, GIE

; Enable interrupts

```

### 16.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- · ADC voltage reference selection

- · ADC conversion clock source

- · Interrupt control

- · Result formatting

### 16.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 12.0 "I/O Ports"** for more information.

**Note:** Analog voltages on any pin that is defined as a digital input may cause the input buffer to conduct excess current.

### 16.1.2 CHANNEL SELECTION

There are up to 30 channel selections available:

- AN<19:8, 4:0> pins (PIC16(L)F1516/8 only)

- AN<27:0> pins (PIC16(L)F1517/9 only)

- · Temperature Indicator

- · FVR (Fixed Voltage Reference) Output

Refer to Section 14.0 "Fixed Voltage Reference (FVR)" and Section 15.0 "Temperature Indicator Module" for more information on these channel selections.

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 16.2** "**ADC Operation**" for more information.

#### 16.1.3 ADC VOLTAGE REFERENCE

The ADPREF bits of the ADCON1 register provides control of the positive voltage reference. The positive voltage reference can be:

- VREF+ pin

- VDD

See Section 14.0 "Fixed Voltage Reference (FVR)" for more details on the Fixed Voltage Reference.

#### 16.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal FRC oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11.5 TAD periods as shown in Figure 16-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the ADC conversion requirements in **Section 25.0 "Electrical Specifications"** for more information. Table gives examples of appropriate ADC clock selections.

Note: Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

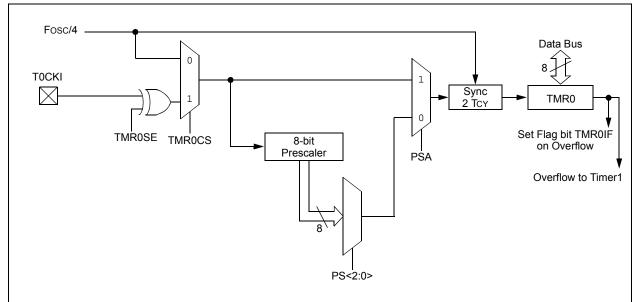

### 17.0 TIMERO MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- · 8-bit timer/counter register (TMR0)

- 8-bit prescaler (independent of Watchdog Timer)

- · Programmable internal or external clock source

- · Programmable external clock edge selection

- · Interrupt on overflow

- · TMR0 can be used to gate Timer1

Figure 17-1 is a block diagram of the Timer0 module.

## 17.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 17.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-Bit Timer mode is selected by clearing the TMR0CS bit of the OPTION\_REG register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

Note:

The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

#### 17.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin.

8-Bit Counter mode, using the T0CKI pin, is selected by setting the TMR0CS bit in the OPTION\_REG register to  $^{\circ}$ 1,

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION REG register.

### FIGURE 17-1: BLOCK DIAGRAM OF THE TIMER0

#### REGISTER 18-2: T1GCON: TIMER1 GATE CONTROL REGISTER

| R/W-0/u     | R/W-0/u | R/W-0/u | R/W-0/u | R/W/HC-0/u     | R-x/x | R/W-0/u | R/W-0/u |  |

|-------------|---------|---------|---------|----------------|-------|---------|---------|--|

| TMR1GE      | T1GPOL  | T1GTM   | T1GSPM  | T1GGO/<br>DONE |       |         | S<1:0>  |  |

| bit 7 bit 0 |         |         |         |                |       |         |         |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared HC = Bit is cleared by hardware

bit 7 TMR1GE: Timer1 Gate Enable bit

If TMR1ON = 0: This bit is ignored If TMR1ON = 1:

1 = Timer1 counting is controlled by the Timer1 gate function

0 = Timer1 counts regardless of Timer1 gate function

bit 6 T1GPOL: Timer1 Gate Polarity bit

1 = Timer1 gate is active-high (Timer1 counts when gate is high)

0 = Timer1 gate is active-low (Timer1 counts when gate is low)

bit 5 T1GTM: Timer1 Gate Toggle Mode bit

1 = Timer1 Gate Toggle mode is enabled

0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared

Timer1 gate flip-flop toggles on every rising edge.

bit 4 T1GSPM: Timer1 Gate Single-Pulse Mode bit

1 = Timer1 Gate Single-Pulse mode is enabled and is controlling Timer1 gate

0 = Timer1 Gate Single-Pulse mode is disabled

bit 3 T1GGO/DONE: Timer1 Gate Single-Pulse Acquisition Status bit

1 = Timer1 gate single-pulse acquisition is ready, waiting for an edge

0 = Timer1 gate single-pulse acquisition has completed or has not been started

bit 2 T1GVAL: Timer1 Gate Current State bit

Indicates the current state of the Timer1 gate that could be provided to TMR1H:TMR1L.

Unaffected by Timer1 Gate Enable (TMR1GE).

bit 1-0 T1GSS<1:0>: Timer1 Gate Source Select bits

11 = Reserved

10 = Timer2 Match PR2

01 = Timer0 overflow output

00 = Timer1 gate pin

#### 19.5 **Register Definitions: Timer2 Control**

### REGISTER 19-1: T2CON: TIMER2 CONTROL REGISTER

| U-0   | R/W-0/0      | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|--------------|---------|---------|---------|---------|---------|---------|

| _     | T2OUTPS<3:0> |         |         |         | TMR2ON  | T2CKP   | S<1:0>  |

| bit 7 |              |         |         |         |         |         | bit 0   |

Legend: U = Unimplemented bit, read as '0' R = Readable bit W = Writable bit u = Bit is unchanged -n/n = Value at POR and BOR/Value at all other Resets x = Bit is unknown'1' = Bit is set '0' = Bit is cleared

bit 7 Unimplemented: Read as '0'

bit 6-3 T2OUTPS<3:0>: Timer2 Output Postscaler Select bits

> 1111 = 1:16 Postscaler 1110 = 1:15 Postscaler 1101 = 1:14 Postscaler 1100 = 1:13 Postscaler 1011 = 1:12 Postscaler 1010 = 1:11 Postscaler 1001 = 1:10 Postscaler 1000 = 1:9 Postscaler

0111 = 1:8 Postscaler 0110 = 1:7 Postscaler

0101 = 1:6 Postscaler 0100 = 1:5 Postscaler 0011 = 1:4 Postscaler

0010 = 1:3 Postscaler 0001 = 1:2 Postscaler 0000 = 1:1 Postscaler

bit 2 TMR2ON: Timer2 On bit

> 1 = Timer2 is ON 0 = Timer2 is OFF

bit 1-0 T2CKPS<1:0>: Timer2 Clock Prescale Select bits

> 11 = Prescaler is 64 10 = Prescaler is 16 01 = Prescaler is 4 00 = Prescaler is 1

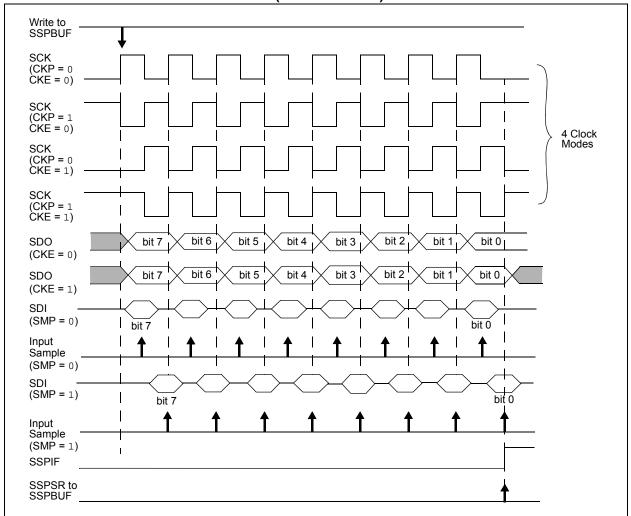

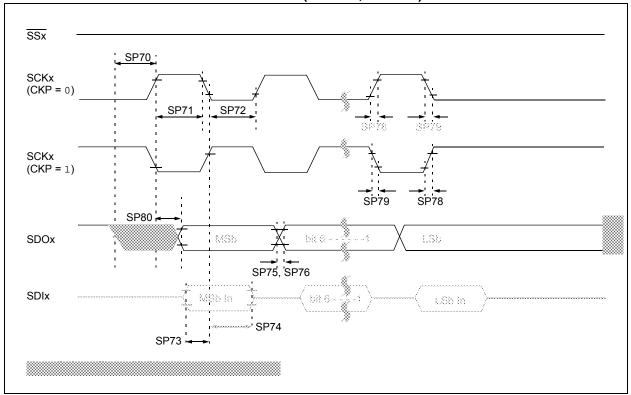

#### 21.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK line. The master determines when the slave (Processor 2, Figure 21-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and Status bits appropriately set).

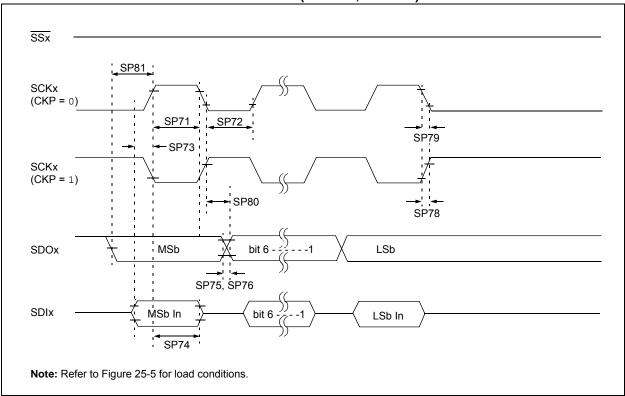

The clock polarity is selected by appropriately programming the CKP bit of the SSPCON1 register and the CKE bit of the SSPSTAT register. This then, would give waveforms for SPI communication as shown in Figure 21-6, Figure 21-8, Figure 21-9 and Figure 21-10, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- · Timer2 output/2

- Fosc/(4 \* (SSPADD + 1))

Figure 21-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

FIGURE 21-6: SPI MODE WAVEFORM (MASTER MODE)

#### REGISTER 21-5: SSPCON2: SSP CONTROL REGISTER 2

| R/W-0/0 | R-0/0   | R/W-0/0 | R/S/HS-0/0 | R/S/HS-0/0 | R/S/HS-0/0 | R/S/HS-0/0 | R/W/HS-0/0 |

|---------|---------|---------|------------|------------|------------|------------|------------|

| GCEN    | ACKSTAT | ACKDT   | ACKEN      | RCEN       | PEN        | RSEN       | SEN        |

| bit 7   |         |         |            |            |            |            | bit 0      |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is clearedHC = Cleared by hardwareS = User set

bit 7 **GCEN:** General Call Enable bit (in I<sup>2</sup>C Slave mode only)

1 = Enable interrupt when a general call address (0x00 or 00h) is received in the SSPSR

0 = General call address disabled

bit 6 ACKSTAT: Acknowledge Status bit (in I<sup>2</sup>C mode only)

1 = Acknowledge was not received0 = Acknowledge was received

bit 5 **ACKDT:** Acknowledge Data bit (in I<sup>2</sup>C mode only)

In Receive mode:

Value transmitted when the user initiates an Acknowledge sequence at the end of a receive

1 = Not Acknowledge0 = Acknowledge

bit 4 **ACKEN:** Acknowledge Sequence Enable bit (in I<sup>2</sup>C Master mode only)

In Master Receive mode:

1 = Initiate Acknowledge sequence on SDA and SCL pins, and transmit ACKDT data bit. Automatically cleared by hardware.

0 = Acknowledge sequence idle

bit 3 RCEN: Receive Enable bit (in I<sup>2</sup>C Master mode only)

1 = Enables Receive mode for  $I^2C$

0 = Receive idle

bit 2 **PEN:** Stop Condition Enable bit (in I<sup>2</sup>C Master mode only)

SCKMSSP Release Control:

1 = Initiate Stop condition on SDA and SCL pins. Automatically cleared by hardware.

0 = Stop condition Idle

bit 1 **RSEN:** Repeated Start Condition Enable bit (in I<sup>2</sup>C Master mode only)

1 = Initiate Repeated Start condition on SDA and SCL pins. Automatically cleared by hardware.

0 = Repeated Start condition Idle

bit 0 SEN: Start Condition Enable/Stretch Enable bit

In Master mode:

1 = Initiate Start condition on SDA and SCL pins. Automatically cleared by hardware.

0 = Start condition Idle

In Slave mode:

1 = Clock stretching is enabled for both slave transmit and slave receive (stretch enabled)

0 = Clock stretching is disabled

**Note 1:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

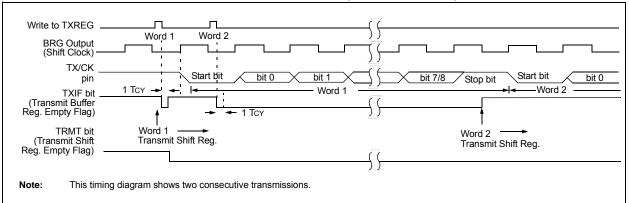

#### 22.1.1.5 TSR Status

The TRMT bit of the TXSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

**Note:** The TSR register is not mapped in data memory, so it is not available to the user.

### 22.1.1.6 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXSTA register is set, the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXSTA register is the 9th, and Most Significant, data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 22.1.2.7 "Address Detection"** for more information on the address mode.

#### 22.1.1.7 Asynchronous Transmission Setup:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 22.4 "EUSART Baud Rate Generator (BRG)").

- Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- If 9-bit transmission is desired, set the TX9 control bit. A set 9th data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- Set SCKP bit if inverted transmit is desired.

- Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- If 9-bit transmission is selected, the 9th bit should be loaded into the TX9D data bit.

- Load 8-bit data into the TXREG register. This will start the transmission.

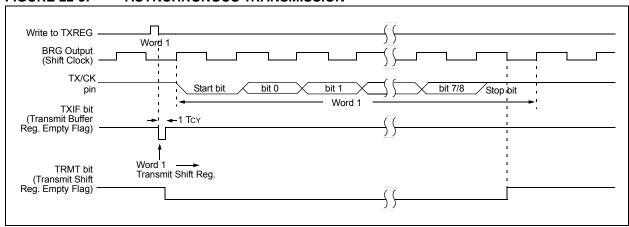

#### FIGURE 22-4: ASYNCHRONOUS TRANSMISSION (BACK-TO-BACK)

# 23.0 IN-CIRCUIT SERIAL PROGRAMMING™ (ICSP™)

ICSP<sup>TM</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process, allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>TM</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP $^{\text{TM}}$  refer to the "PIC16(L)F151X/152X Memory Programming Specification", (DS41442).

# 23.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

# 23.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC® Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

$\overline{\text{If low-voltage}}$  programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 6.5 "MCLR"** for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

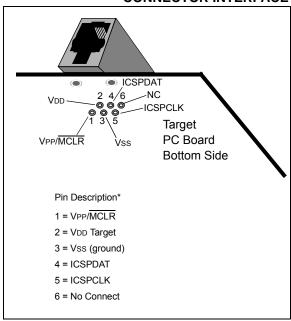

### 23.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP™ header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 23-1.

FIGURE 23-1: ICD RJ-11 STYLE CONNECTOR INTERFACE

Another connector often found in use with the PICkit™ programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 23-2.

For additional interface recommendations, refer to the specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 23-3 for more information.

**TABLE 24-3: INSTRUCTION SET**

| Mnemonic,<br>Operands                  |                    | Description                                          | Cycles       | 14-Bit Opcode |      |             | Status | Notes    |       |

|----------------------------------------|--------------------|------------------------------------------------------|--------------|---------------|------|-------------|--------|----------|-------|

|                                        |                    | Description                                          |              | MSb           |      |             | LSb    | Affected | Notes |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |                    |                                                      |              |               |      |             |        |          |       |

| ADDWF                                  | f, d               | Add W and f                                          | 1            | 00            | 0111 | dfff        | ffff   | C, DC, Z | 2     |

| ADDWFC                                 | f, d               | Add with Carry W and f                               | 1            | 11            | 1101 | dfff        | ffff   | C, DC, Z | 2     |

| ANDWF                                  | f, d               | AND W with f                                         | 1            | 00            | 0101 | dfff        | ffff   | Z        | 2     |

| ASRF                                   | f, d               | Arithmetic Right Shift                               | 1            | 11            | 0111 | dfff        | ffff   | C, Z     | 2     |

| LSLF                                   | f, d               | Logical Left Shift                                   | 1            | 11            | 0101 | dfff        | ffff   | C, Z     | 2     |

| LSRF                                   | f, d               | Logical Right Shift                                  | 1            | 11            | 0110 | dfff        | ffff   | C, Z     | 2     |

| CLRF                                   | f                  | Clear f                                              | 1            | 00            | 0001 | lfff        | ffff   | Z        | 2     |

| CLRW                                   | _                  | Clear W                                              | 1            | 00            | 0001 | 0000        | 00xx   | Z        |       |

| COMF                                   | f, d               | Complement f                                         | 1            | 00            | 1001 | dfff        | ffff   | Z        | 2     |

| DECF                                   | f, d               | Decrement f                                          | 1            | 00            | 0011 | dfff        | ffff   | Z        | 2     |

| INCF                                   | f, d               | Increment f                                          | 1            | 00            | 1010 | dfff        | ffff   | Z        | 2     |

| IORWF                                  | f. d               | Inclusive OR W with f                                | 1            | 00            |      | dfff        |        | z        | 2     |

| MOVF                                   | f, d               | Move f                                               | 1            | 00            |      | dfff        |        | Z        | 2     |

| MOVWF                                  | f                  | Move W to f                                          | 1            | 00            | 0000 | 1fff        |        |          | 2     |

| RLF                                    | f. d               | Rotate Left f through Carry                          | 1            | 0.0           |      | dfff        |        | С        | 2     |

| RRF                                    | f, d               | Rotate Right f through Carry                         | 1            | 0.0           |      | dfff        |        | c        | 2     |

| SUBWF                                  | f, d               | Subtract W from f                                    | 1            | 00            |      | dfff        |        | _        | 2     |

| SUBWFB                                 | f, d               | Subtract with Borrow W from f                        | 1            | 11            |      | dfff        |        | C, DC, Z | 2     |

| SWAPF                                  | f, d               | Swap nibbles in f                                    | 1            | 00            | 1110 |             | ffff   | 0, 00, 2 | 2     |

| XORWF                                  | f, d               | Exclusive OR W with f                                | 1            | 0.0           | 0110 |             | ffff   | z        | 2     |

| XOIWI                                  | 1, u               | BYTE-ORIENTED SKIP O                                 |              |               | 0110 | <u>urii</u> |        |          | -     |

|                                        | f, d               | Decrement f, Skip if 0                               |              | 00            | 1011 | dfff        | ffff   |          | 1, 2  |

| DECFSZ                                 | f, d               | Increment f, Skip if 0                               | 1(2)<br>1(2) | 00            | 1111 | dfff        | ffff   |          | 1, 2  |

| INCFSZ                                 | ı, u               | Increment i, Skip ii o                               | 1(2)         | 00            | 1111 | alli        | TILL   |          | 1, 2  |

|                                        |                    | BIT-ORIENTED FILE REGIST                             | ER OPER      | RATION        | IS   |             |        |          |       |

| BCF                                    | f, b               | Bit Clear f                                          | 1            | 01            | 00bb | bfff        | ffff   |          | 2     |

| BSF                                    | f, b               | Bit Set f                                            | 1            | 01            | 01bb | bfff        | ffff   |          | 2     |

|                                        | •                  | BIT-ORIENTED SKIP O                                  | PERATIO      | NS            | •    |             |        |          | •     |

| BTFSC                                  | f, b               | Bit Test f, Skip if Clear                            | 1 (2)        | 01            | 10bb | bfff        | ffff   |          | 1, 2  |

| BTFSS                                  | f, b               | Bit Test f, Skip if Set                              | 1 (2)        | 01            | 11bb | bfff        | ffff   |          | 1, 2  |

| LITERAL (                              | LITERAL OPERATIONS |                                                      |              |               |      |             |        |          |       |

| ADDLW                                  | k                  | Add literal and W                                    | 1            | 11            | 1110 | kkkk        | kkkk   | C, DC, Z |       |

| ANDLW                                  | k                  | AND literal with W                                   | 1            | 11            | 1001 | kkkk        | kkkk   | Z        |       |

| IORLW                                  | k                  | Inclusive OR literal with W                          | 1            | 11            | 1000 | kkkk        | kkkk   | Z        |       |

| MOVLB                                  | k                  | Move literal to BSR                                  | 1            | 00            | 0000 | 001k        | kkkk   |          |       |

| MOVLP                                  | k                  | Move literal to PCLATH                               | 1            | 11            |      | 1kkk        |        |          |       |

| MOVLW                                  | k                  | Move literal to W                                    | 1            | 11            |      | kkkk        |        |          |       |

| SUBLW                                  | k                  | Subtract W from literal                              | 1            | 11            |      | kkkk        |        | C, DC, Z |       |

| XORLW                                  | k                  | Exclusive OR literal with W                          | 1            | 11            |      | kkkk        |        | Z Z      |       |

|                                        |                    | m Counter (PC) is modified, or a conditional test in |              |               |      |             |        |          |       |

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

<sup>2:</sup> If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

FIGURE 25-16: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

FIGURE 25-17: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

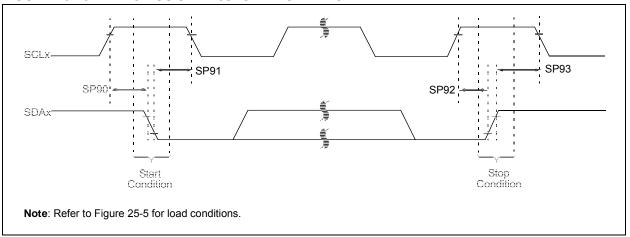

FIGURE 25-20: I<sup>2</sup>C BUS START/STOP BITS TIMING

TABLE 25-13: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Param<br>No. | Symbol  | Characteristic  |              | Min. | Тур | Max. | Unit<br>s | Conditions                   |

|--------------|---------|-----------------|--------------|------|-----|------|-----------|------------------------------|

| SP90*        | Tsu:sta | Start condition | 100 kHz mode | 4700 | _   | _    | ns        | Only relevant for Repeated   |

|              |         | Setup time      | 400 kHz mode | 600  | _   | _    |           | Start condition              |

| SP91*        | THD:STA | Start condition | 100 kHz mode | 4000 | _   | _    | ns        | After this period, the first |

|              |         | Hold time       | 400 kHz mode | 600  | _   | _    |           | clock pulse is generated     |

| SP92*        | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | _   | _    | ns        |                              |

|              |         | Setup time      | 400 kHz mode | 600  | _   | _    |           |                              |

| SP93         | THD:STO | Stop condition  | 100 kHz mode | 4000 | _   | _    | ns        |                              |

|              |         | Hold time       | 400 kHz mode | 600  |     | _    |           |                              |

<sup>\*</sup> These parameters are characterized but not tested.

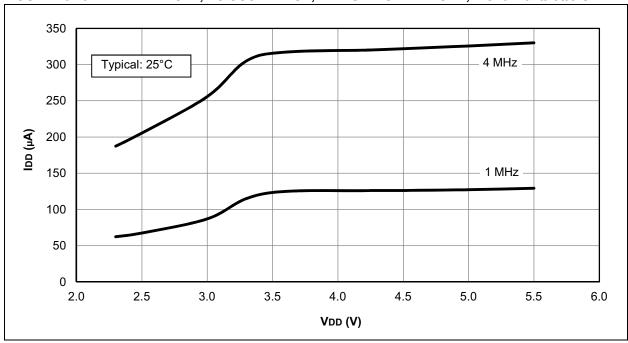

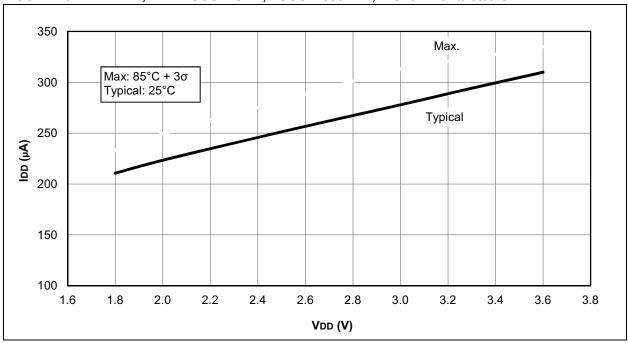

FIGURE 26-13: IDD TYPICAL, EC OSCILLATOR, MEDIUM-POWER MODE, PIC16F1516/7/8/9 ONLY

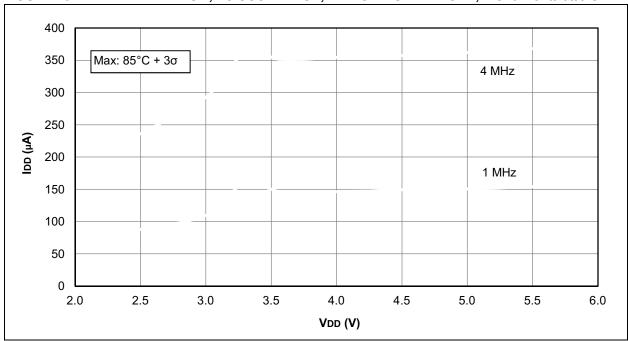

FIGURE 26-14: IDD MAXIMUM, EC OSCILLATOR, MEDIUM-POWER MODE, PIC16F1516/7/8/9 ONLY

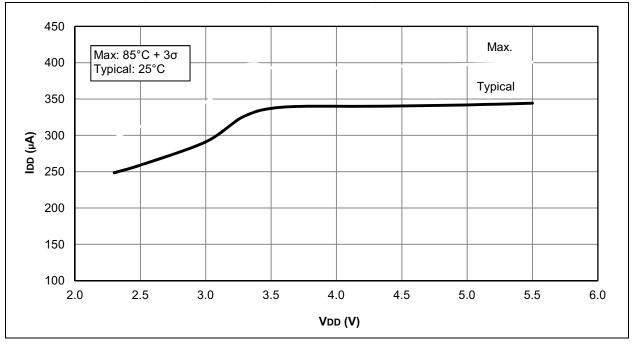

FIGURE 26-21: IDD, MFINTOSC MODE, FOSC = 500 kHz, PIC16LF1516/7/8/9 ONLY

FIGURE 26-22: IDD, MFINTOSC MODE, FOSC = 500 kHz, PIC16F1516/7/8/9 ONLY

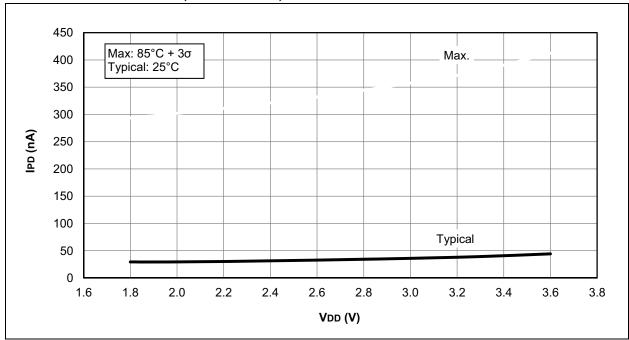

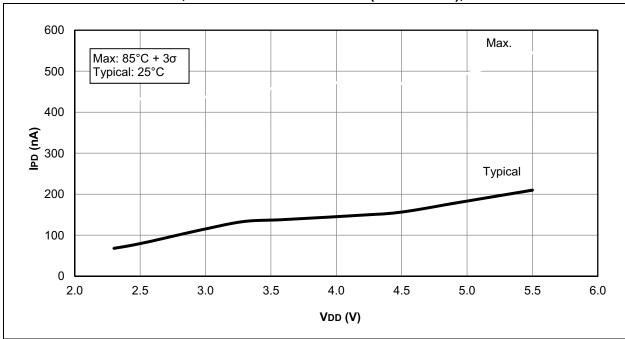

FIGURE 26-32: IPD BASE, LOW-POWER SLEEP MODE (VREGPM = 1), PIC16F1516/7/8/9 ONLY

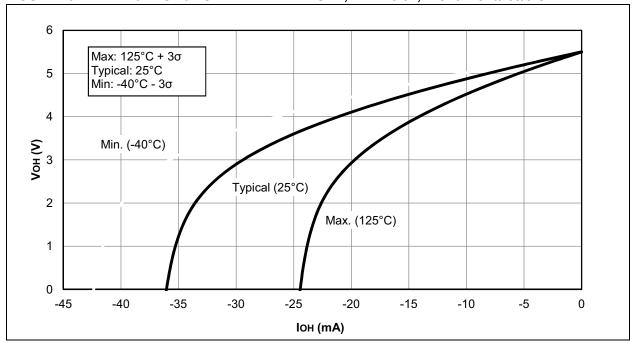

FIGURE 26-41: Voh VS. Ioh OVER TEMPERATURE, VDD = 5.5V, PIC16F1516/7/8/9 ONLY

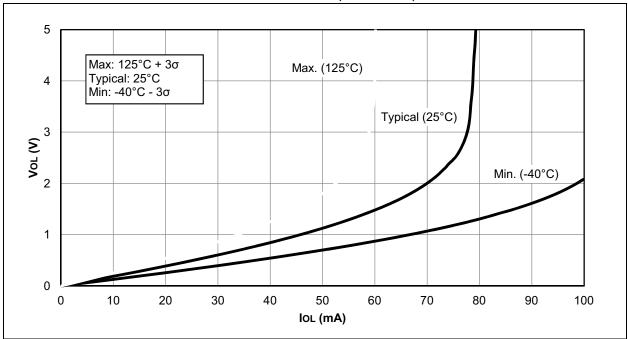

FIGURE 26-42: Vol VS. Iol OVER TEMPERATURE, VDD = 5.5V, PIC16F1516/7/8/9 ONLY

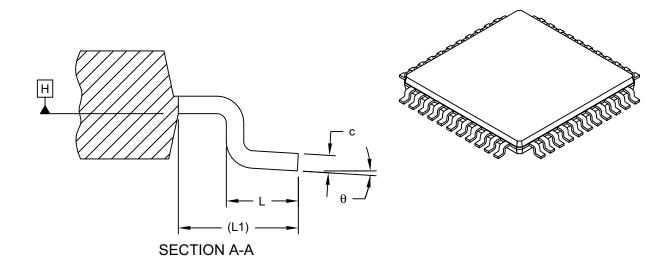

### 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |                |           |      |  |

|--------------------------|-------------|----------------|-----------|------|--|

| Dimension                | MIN         | NOM            | MAX       |      |  |

| Number of Leads          |             | 44             |           |      |  |

| Lead Pitch               | е           |                | 0.80 BSC  |      |  |

| Overall Height           | Α           | 1              | -         | 1.20 |  |

| Standoff                 | A1          | 0.05           | -         | 0.15 |  |

| Molded Package Thickness | A2          | 0.95           | 1.00      | 1.05 |  |

| Overall Width            | Е           | 12.00 BSC      |           |      |  |

| Molded Package Width     | E1          | 10.00 BSC      |           |      |  |

| Overall Length           | D           | 12.00 BSC      |           |      |  |

| Molded Package Length    | D1          |                | 10.00 BSC |      |  |

| Lead Width               | b           | 0.30           | 0.37      | 0.45 |  |

| Lead Thickness           | С           | 0.09           | -         | 0.20 |  |

| Lead Length              | L           | 0.45 0.60 0.75 |           |      |  |

| Footprint                | L1          | 1.00 REF       |           |      |  |

| Foot Angle               | θ           | 0°             | 3.5°      | 7°   |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Exact shape of each corner is optional.

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076C Sheet 2 of 2