Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1518t-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 3-5: PIC16(L)F1518/9 MEMORY MAP (CONTINUED)

|                      | BANK 8                                     | •                    | BANK 9                                     |                      | BANK 10                                    |                      | BANK 11                                    |                                      | BANK 12                                                                 |                      | BANK 13                               |                      | BANK 14                               |                      | BANK 15                               |

|----------------------|--------------------------------------------|----------------------|--------------------------------------------|----------------------|--------------------------------------------|----------------------|--------------------------------------------|--------------------------------------|-------------------------------------------------------------------------|----------------------|---------------------------------------|----------------------|---------------------------------------|----------------------|---------------------------------------|

| 400h<br>40Bh         | Core Registers<br>(Table 3-2)              | 480h<br>48Bh         | Core Registers<br>(Table 3-2)              | 500h<br>50Bh         | Core Registers<br>(Table 3-2)              | 580h<br>58Bh         | Core Registers<br>(Table 3-2)              | 600h<br>60Bh                         | Core Registers<br>(Table 3-2)                                           | 680h<br>68Bh         | Core Registers<br>(Table 3-2)         | 700h<br>70Bh         | Core Registers<br>(Table 3-2)         | 780h<br>78Bh         | Core Registers<br>(Table 3-2)         |

| 40Bh<br>40Ch         | Unimplemented<br>Read as '0'               | 48Ch                 | Unimplemented<br>Read as '0'               | 50Ch                 | Unimplemented<br>Read as '0'               | 58Ch                 | Unimplemented<br>Read as '0'               | 60Ch                                 | Unimplemented<br>Read as '0'                                            | 68Ch                 | Unimplemented<br>Read as '0'          | 70Bh                 | Unimplemented<br>Read as '0'          | 78Ch                 | Unimplemented<br>Read as '0'          |

| 41Fh<br>420h<br>46Fh | General<br>Purpose<br>Register<br>80 Bytes | 49Fh<br>4A0h<br>4EFh | General<br>Purpose<br>Register<br>80 Bytes | 51Fh<br>520h<br>56Fh | General<br>Purpose<br>Register<br>80 Bytes | 59Fh<br>5A0h<br>5EFh | General<br>Purpose<br>Register<br>80 Bytes | 61Fh<br>620h<br>64Fh<br>650h<br>66Fh | General Purpose<br>Register<br>48 Bytes<br>Unimplemented<br>Read as '0' | 69Fh<br>6A0h<br>6EFh | Unimplemented<br>Read as '0'          | 71Fh<br>720h<br>76Fh | Unimplemented<br>Read as '0'          | 79Fh<br>7A0h<br>7EFh | Unimplemented<br>Read as '0'          |

| 470h<br>47Fh         | Common RAM<br>(Accesses<br>70h – 7Fh)      | 4F0h<br>4FFh         | Common RAM<br>(Accesses<br>70h – 7Fh)      | 570h<br>57Fh         | Common RAM<br>(Accesses<br>70h – 7Fh)      | 5F0h<br>5FFh         | Common RAM<br>(Accesses<br>70h – 7Fh)      | 670h<br>67Fh                         | Common RAM<br>(Accesses<br>70h – 7Fh)                                   | 6F0h<br>6FFh         | Common RAM<br>(Accesses<br>70h – 7Fh) | 770h<br>77Fh         | Common RAM<br>(Accesses<br>70h – 7Fh) | 7F0h<br>7FFh         | Common RAM<br>(Accesses<br>70h – 7Fh) |

|              | BANK 16                               |              | BANK 17                               |              | BANK 18                               |              | BANK 19                               |              | BANK 20                               |              | BANK 21                               |              | BANK 22                               |              | BANK 23                               |

|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|

| 800h         | Core Registers<br>(Table 3-2)         | 880h         | Core Registers<br>(Table 3-2)         | 900h         | Core Registers<br>(Table 3-2)         | 980h         | Core Registers<br>(Table 3-2)         | A00h         | Core Registers<br>(Table 3-2)         | A80h         | Core Registers<br>(Table 3-2)         | B00h         | Core Registers<br>(Table 3-2)         | B80h         | Core Registers<br>(Table 3-2)         |

| 80Bh         |                                       | 88Bh         |                                       | 90Bh         |                                       | 98Bh         |                                       | A0Bh         |                                       | A8Bh         |                                       | B0Bh         |                                       | B8Bh         |                                       |

| 80Ch         |                                       | 88Ch         |                                       | 90Ch         |                                       | 98Ch         |                                       | A0Ch         |                                       | A8Ch         |                                       | B0Ch         |                                       | B8Ch         |                                       |

|              | Unimplemented<br>Read as '0'          |

| 86Fh         |                                       | 8EFh         |                                       | 96Fh         |                                       | 9EFh         |                                       | A6Fh         |                                       | AEFh         |                                       | B6Fh         |                                       | BEFh         |                                       |

| 870h<br>87Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | 8F0h<br>8FFh | Common RAM<br>(Accesses<br>70h – 7Fh) | 970h<br>97Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | 9F0h<br>9FFh | Common RAM<br>(Accesses<br>70h – 7Fh) | A70h<br>A7Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | AF0h<br>AFFh | Common RAM<br>(Accesses<br>70h – 7Fh) | B70h<br>B7Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | BF0h<br>BFFh | Common RAM<br>(Accesses<br>70h – 7Fh) |

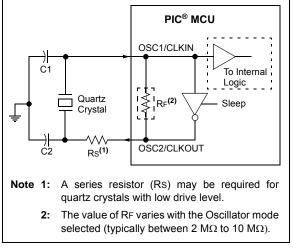

## FIGURE 5-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices (DS00826)

- AN849, Basic PIC<sup>®</sup> Oscillator Design (DS00849)

- AN943, Practical PIC<sup>®</sup> Oscillator Analysis and Design (DS00943)

- AN949, Making Your Oscillator Work (DS00949)

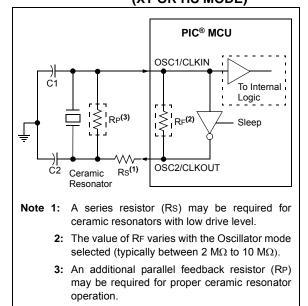

## FIGURE 5-4:

#### CERAMIC RESONATOR OPERATION (XT OR HS MODE)

### 5.2.1.3 Oscillator Start-up Timer (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended, unless either FSCM or Two-Speed Start-up are enabled. In this case, code will continue to execute at the selected INTOSC frequency while the OST is counting. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-Up mode can be selected (see **Section 5.4 "Two-Speed Clock Start-up Mode"**).

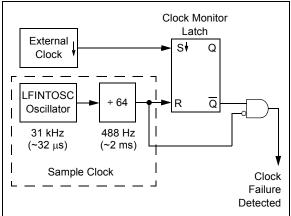

### 5.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Words. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, EC, RC and secondary oscillator).

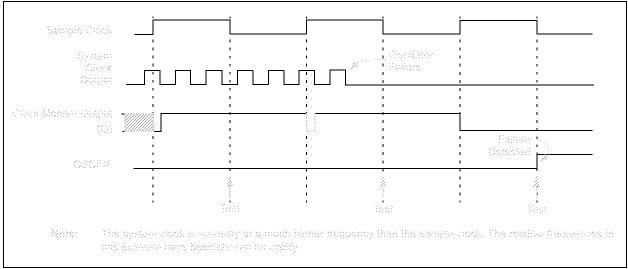

FIGURE 5-9: FSCM BLOCK DIAGRAM

### 5.5.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64 (see Figure 5-9). Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

#### 5.5.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<3:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

#### 5.5.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the SCS bits of the OSCCON register. When the SCS bits are changed, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared after successfully switching to the external clock source. The OSFIF bit should be cleared prior to switching to the external clock source. If the Fail-Safe condition still exists, the OSFIF flag will again become set by hardware.

#### 5.5.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

| Note: | Due to the wide range of oscillator start-up<br>times, the Fail-Safe circuit is not active<br>during oscillator start-up (i.e., after exiting<br>Reset or Sleep). After an appropriate |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | amount of time, the user should check the<br>Status bits in the OSCSTAT register to<br>verify the oscillator start-up and that the                                                     |

|       | system clock switchover has successfully<br>completed.                                                                                                                                 |

### 6.13 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON register bits are shown in Register 6-2.

### 6.14 Register Definitions: Power Control

#### REGISTER 6-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | —   | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      | •          |     |            |            |            |            | bit 0      |

| Legend:                        |                      |                                                       |  |  |  |  |

|--------------------------------|----------------------|-------------------------------------------------------|--|--|--|--|

| HC = Bit is cleared by hardwar | re                   | HS = Bit is set by hardware                           |  |  |  |  |

| R = Readable bit               | W = Writable bit     | U = Unimplemented bit, read as '0'                    |  |  |  |  |

| u = Bit is unchanged           | x = Bit is unknown   | -m/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |

| '1' = Bit is set               | '0' = Bit is cleared | q = Value depends on condition                        |  |  |  |  |

| bit 7 | <ul> <li>STKOVF: Stack Overflow Flag bit</li> <li>1 = A Stack Overflow occurred</li> <li>0 = A Stack Overflow has not occurred or cleared by firmware</li> </ul>                       |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>STKUNF:</b> Stack Underflow Flag bit<br>1 = A Stack Underflow occurred<br>0 = A Stack Underflow has not occurred or cleared by firmware                                             |

| bit 5 | Unimplemented: Read as '0'                                                                                                                                                             |

| bit 4 | <b>RWDT:</b> Watchdog Timer Reset Flag bit<br>1 = A Watchdog Timer Reset has not occurred or set to '1' by firmware<br>0 = A Watchdog Timer Reset has occurred (cleared by hardware)   |

| bit 3 | <b>RMCLR:</b> MCLR Reset Flag bit<br>1 = A MCLR Reset has not occurred or set to '1' by firmware<br>0 = A MCLR Reset has occurred (cleared by hardware)                                |

| bit 2 | <b>RI:</b> RESET Instruction Flag bit<br>1 = A RESET instruction has not been executed or set to '1' by firmware<br>0 = A RESET instruction has been executed (cleared by hardware)    |

| bit 1 | <b>POR</b> : Power-on Reset Status bit<br>1 = No Power-on Reset occurred<br>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                      |

| bit 0 | <b>BOR:</b> Brown-out Reset Status bit<br>1 = No Brown-out Reset occurred<br>0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurs) |

|       |                                                                                                                                                                                        |

### 14.3 Register Definitions: FVR Control

| R/W-0/        |                                                                                                                                                                                               | R/W-0/0                                                                                                                                                                                                                                                                                                                   | R/W-0/0              | U-0                         | U-0              | R/W-0/0 | R/W-0/0      |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------|------------------|---------|--------------|--|--|

| FVREN         | (1) FVRRDY <sup>(2)</sup>                                                                                                                                                                     | TSEN <sup>(3)</sup>                                                                                                                                                                                                                                                                                                       | TSRNG <sup>(3)</sup> | _                           | —                | ADFVR   | <1:0>(1)     |  |  |

| bit 7         |                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                           |                      |                             |                  |         | bit          |  |  |

| Legend:       |                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                           |                      |                             |                  |         |              |  |  |

| R = Reada     | able bit                                                                                                                                                                                      | W = Writable                                                                                                                                                                                                                                                                                                              | bit                  | U = Unimplei                | mented bit, read | as '0'  |              |  |  |

|               | unchanged                                                                                                                                                                                     | x = Bit is unk                                                                                                                                                                                                                                                                                                            |                      | •                           | at POR and BO    |         | other Resets |  |  |

| '1' = Bit is  | •                                                                                                                                                                                             | '0' = Bit is cle                                                                                                                                                                                                                                                                                                          |                      |                             | pends on condit  |         |              |  |  |

|               |                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                           |                      | •                           |                  | -       |              |  |  |

| bit 7         | 0 = Fixed Vo                                                                                                                                                                                  | d Voltage Refe<br>Itage Referenc<br>Itage Referenc                                                                                                                                                                                                                                                                        | e is disabled        | bit <sup>(1)</sup>          |                  |         |              |  |  |

| bit 6         | <b>FVRRDY:</b> Fixed Voltage Reference Ready Flag bit <sup>(2)</sup><br>0 = Fixed Voltage Reference output is not ready or not enabled<br>1 = Fixed Voltage Reference output is ready for use |                                                                                                                                                                                                                                                                                                                           |                      |                             |                  |         |              |  |  |

| bit 5         | 0 = Tempera                                                                                                                                                                                   | erature Indicator<br>ture Indicator i<br>ture Indicator i                                                                                                                                                                                                                                                                 | s disabled           | )                           |                  |         |              |  |  |

| bit 4         | 0 = VOUT = V                                                                                                                                                                                  | iperature Indica<br>/DD - 2V⊤ (Low<br>/DD - 4V⊤ (Higł                                                                                                                                                                                                                                                                     | Range)               | election bit <sup>(3)</sup> |                  |         |              |  |  |

| bit 3-2       | Unimplemen                                                                                                                                                                                    | ted: Read as                                                                                                                                                                                                                                                                                                              | 0'                   |                             |                  |         |              |  |  |

| bit 1-0       | 11 = ADC FV<br>10 = ADC FV<br>01 = ADC FV                                                                                                                                                     | ADFVR<1:0>: ADC FVR Buffer Gain Selection bits <sup>(1)</sup><br>11 = ADC FVR Buffer Gain is 4x, with output VADFVR = 4x VFVR <sup>(4)</sup><br>10 = ADC FVR Buffer Gain is 2x, with output VADFVR = 2x VFVR <sup>(4)</sup><br>01 = ADC FVR Buffer Gain is 1x, with output VADFVR = 1x VFVR<br>00 = ADC FVR Buffer is off |                      |                             |                  |         |              |  |  |

| Note 1:<br>2: | To minimize current consumption when the FVR is disabled, the FVR buffers should be turned off by clearing the Buffer Gain Selection bits.<br>FVRRDY is always '1' on PIC16F1516/7/8/9 only.  |                                                                                                                                                                                                                                                                                                                           |                      |                             |                  |         |              |  |  |

|               |                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                           |                      |                             |                  |         |              |  |  |

#### REGISTER 14-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

3: See Section 15.0 "Temperature Indicator Module" for additional information.

4: Fixed Voltage Reference output cannot exceed VDD.

#### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1      | Bit 0 | Register<br>on page |

|--------|-------|--------|-------|-------|-------|-------|------------|-------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | _     | _     | ADFVR<1:0> |       | 128                 |

Legend: Shaded cells are unused by the Fixed Voltage Reference module.

#### **15.4 ADC Acquisition Time**

To ensure accurate temperature measurements, the user must wait at least 200  $\mu s$  after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu s$  between sequential conversions of the temperature indicator output.

#### TABLE 15-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1      | Bit 0 | Register<br>on page |

|--------|-------|--------|-------|-------|-------|-------|------------|-------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | —     | _     | ADFVR<1:0> |       | 128                 |

Legend: Shaded cells are unused by the temperature indicator module.

| Name                  | Bit 7      | Bit 6        | Bit 5     | Bit 4    | Bit 3  | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|-----------------------|------------|--------------|-----------|----------|--------|-----------------------|-----------------------|-----------------------|---------------------|

| ADCON0                | -          |              |           | CHS<4:0> |        |                       | GO/DONE               | ADON                  | 137                 |

| ADCON1                | ADFM       |              | ADCS<2:0> |          | —      | —                     | ADPRE                 | 138                   |                     |

| ADRESH                | ADC Result | Register Hig | h         |          |        |                       |                       |                       | 139, 140            |

| ADRESL                | ADC Result | Register Lov | v         |          |        |                       |                       |                       | 139, 140            |

| ANSELA                | —          | —            | ANSA5     | —        | ANSA3  | ANSA2                 | ANSA1                 | ANSA0                 | 108                 |

| ANSELB                |            | _            | ANSB5     | ANSB4    | ANSB3  | ANSB2                 | ANSB1                 | ANSB0                 | 112                 |

| ANSELC                | ANSC7      | ANSC6        | ANSC5     | ANSC4    | ANSC3  | ANSC2                 | —                     | _                     | 115                 |

| ANSELD <sup>(1)</sup> | ANSD7      | ANSD6        | ANSD5     | ANSD4    | ANSD3  | ANSD2                 | ANSD1                 | ANSD0                 | 118                 |

| ANSELE <sup>(1)</sup> |            | _            | —         | —        | _      | ANSE2                 | ANSE1                 | ANSE0                 | 121                 |

| CCP1CON               | _          | _            | DC1E      | s<1:0>   |        | CCP1                  | V<3:0>                |                       | 168                 |

| CCP2CON               |            | _            | DC2B      | 3<1:0>   |        | 168                   |                       |                       |                     |

| FVRCON                | FVREN      | FVRRDY       | TSEN      | TSRNG    | _      | —                     | ADFV                  | 128                   |                     |

| INTCON                | GIE        | PEIE         | TMR0IE    | INTE     | IOCIE  | TMR0IF                | INTF                  | IOCIF                 | 74                  |

| PIE1                  | TMR1GIE    | ADIE         | RCIE      | TXIE     | SSPIE  | CCP1IE                | TMR2IE                | TMR1IE                | 75                  |

| PIR1                  | TMR1GIF    | ADIF         | RCIF      | TXIF     | SSPIF  | CCP1IF                | TMR2IF                | TMR1IF                | 77                  |

| TRISA                 | TRISA7     | TRISA6       | TRISA5    | TRISA4   | TRISA3 | TRISA2                | TRISA1                | TRISA0                | 107                 |

| TRISB                 | TRISB7     | TRISB6       | TRISB5    | TRISB4   | TRISB3 | TRISB2                | TRISB1                | TRISB0                | 111                 |

| TRISC                 | TRISC7     | TRISC6       | TRISC5    | TRISC4   | TRISC3 | TRISC2                | TRISC1                | TRISC0                | 114                 |

| TRISD <sup>(1)</sup>  | TRISD7     | TRISD6       | TRISD5    | TRISD4   | TRISD3 | TRISD2                | TRISD1                | TRISD0                | 117                 |

| TRISE                 | —          | —            | —         | —        | (2)    | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 120                 |

| TABLE 16-3: | SUMMARY OF REGISTERS ASSOCIATED WITH ADC |

|-------------|------------------------------------------|

|-------------|------------------------------------------|

**Legend:** — = unimplemented read as '0'. Shaded cells are not used for ADC module.

Note 1: PIC16(L)F1517/9 only.

#### 22.4.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCON register starts the auto-baud calibration sequence (Figure 22-6). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Table . The fifth rising edge will occur on the RX pin at the end of the 8th bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRGL register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRGL register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table . During ABD, both the SPBRGH and SPBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH

and SPBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 22.4.3 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRGL register pair.

| <b>TABLE 22-5:</b> | <b>BRG COUNTER CLOCK RATES</b> |

|--------------------|--------------------------------|

|                    |                                |

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |  |  |

|-------|------|-------------------|------------------|--|--|

| 0     | 0    | Fosc/64           | Fosc/512         |  |  |

| 0     | 1    | Fosc/16           | Fosc/128         |  |  |

| 1     | 0    | Fosc/16           | Fosc/128         |  |  |

| 1     | 1    | Fosc/4            | Fosc/32          |  |  |

Note: During the ABD sequence, SPBRGL and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

#### XXXXh 0000h 001Ch **BRG** Value Edge #1 Edge #2 Edge #3 Edge #4 Edge #5 RX pin Start bit 0 bit 1 bit 2 bit 3 bit 4 bit 5 bit 6 bit 7 Stop bit Auto-Cleared Set by User ABDEN bit RCIDL RCIF bit (Interrupt) Read RCREG SPBRGL XXh 1Ch SPBRGH 00h XXh Note 1: The ABD sequence requires the EUSART module to be configured in Asynchronous mode.

#### **FIGURE 22-6:** AUTOMATIC BAUD RATE CALIBRATION

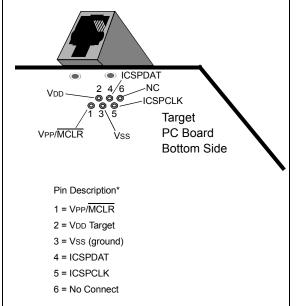

## 23.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process, allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP<sup>TM</sup> refer to the "PIC16(L)F151X/152X Memory Programming Specification", (DS41442).

#### 23.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

#### 23.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 6.5 "MCLR"** for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

### 23.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 23-1.

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 23-2.

For additional interface recommendations, refer to the specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 23-3 for more information.

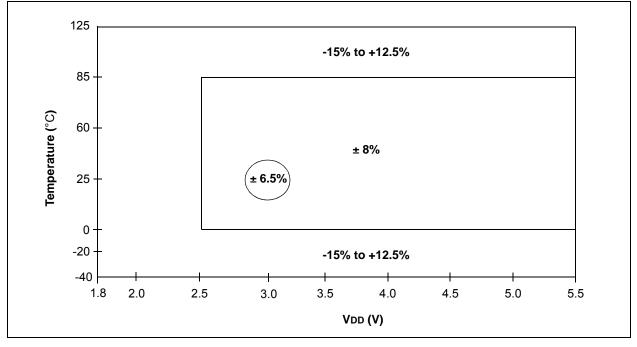

## 25.0 ELECTRICAL SPECIFICATIONS

## 25.1 Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                                  | 40°C to +125°C       |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|

| Storage temperature                                                                                                             | 65°C to +150°C       |  |  |  |  |

| Voltage on VDD with respect to Vss, PIC16F1516/7/8/9                                                                            | -0.3V to +6.5V       |  |  |  |  |

| Voltage on VDD with respect to Vss, PIC16LF1516/7/8/9                                                                           | -0.3V to +4.0V       |  |  |  |  |

| Voltage on MCLR with respect to Vss                                                                                             | -0.3V to +9.0V       |  |  |  |  |

| Voltage on all other pins with respect to Vss                                                                                   | 0.3V to (VDD + 0.3V) |  |  |  |  |

| Total power dissipation <sup>(2)</sup>                                                                                          | 800 mW               |  |  |  |  |

| Maximum current                                                                                                                 |                      |  |  |  |  |

| on Vss pin for 28-Pin devices <sup>(1)</sup>                                                                                    |                      |  |  |  |  |

| $\label{eq:alpha} \begin{array}{l} -40^\circ C \leq T_A \leq +85^\circ C \\ +85^\circ C \leq T_A \leq +125^\circ C \end{array}$ |                      |  |  |  |  |

| on VDD pin for 28-Pin devices <sup>(1)</sup>                                                                                    |                      |  |  |  |  |

| $\begin{array}{l} -40^{\circ}C \leq Ta \leq +85^{\circ}C \\ +85^{\circ}C \leq Ta \leq +125^{\circ}C \end{array}$                |                      |  |  |  |  |

| on Vss pin for 40/44-Pin devices <sup>(1)</sup>                                                                                 |                      |  |  |  |  |

| -40°C $\leq$ Ta $\leq$ +85°C                                                                                                    |                      |  |  |  |  |

| on VDD pin for 40/44-Pin devices <sup>(1)</sup>                                                                                 |                      |  |  |  |  |

| -40°C $\leq$ Ta $\leq$ +85°C                                                                                                    |                      |  |  |  |  |

| Clamp current, Ік (Vpin < 0 or Vpin > Vpd)                                                                                      | ± 20 mA              |  |  |  |  |

| Maximum output current sunk by any I/O pin                                                                                      |                      |  |  |  |  |

| Maximum output current sourced by any I/O pin                                                                                   |                      |  |  |  |  |

**Note 1:** Maximum current rating requires even load distribution across I/O pins. Maximum current rating may be limited by the device package power dissipation characterizations, see Table 25-5 to calculate device specifications.

2: Power dissipation is calculated as follows: PDIS = VDD x {IDD  $-\sum$  IOH} +  $\sum$  {(VDD - VOH) x IOH} +  $\sum$ (VOI x IOL)

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

### 25.4 DC Characteristics: Supply Current (IDD) (Continued)

| PIC16LF1516/7/8/9 |                                           |      |                                                      |              |       |            |                                |  |

|-------------------|-------------------------------------------|------|------------------------------------------------------|--------------|-------|------------|--------------------------------|--|

| PIC16F1516/7/8/9  |                                           |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |              |       |            |                                |  |

| Param             | Device<br>Characteristics                 | Min. | Тур†                                                 | Max.         | Units | Conditions |                                |  |

| No.               |                                           |      |                                                      |              |       | Vdd        | Note                           |  |

|                   | Supply Current (IDD) <sup>(1, 2, 3)</sup> |      |                                                      |              |       |            |                                |  |

| D020              |                                           |      | 1.0                                                  | 1.80         | mA    | 3.0        | Fosc = 20 MHz                  |  |

|                   |                                           |      | 1.2                                                  | 2.10         | mA    | 3.6        | HS Oscillator                  |  |

| D020              |                                           |      | 1.4                                                  | 1.70         | mA    | 3.0        | Fosc = 20 MHz<br>HS Oscillator |  |

|                   |                                           |      | 1.7                                                  | 2.10         | mA    | 5.0        |                                |  |

| D021              |                                           |      | 150                                                  | 220          | μA    | 1.8        | Fosc = 4 MHz                   |  |

|                   |                                           | l    | 250                                                  | 380          | μA    | 3.0        | EXTRC (Note 4)                 |  |

| D021              | D21 — 165 330                             | μA   | 2.3                                                  | Fosc = 4 MHz |       |            |                                |  |

|                   |                                           | _    | 280                                                  | 420          | μA    | 3.0        | EXTRC (Note 4)                 |  |

|                   |                                           | _    | 350                                                  | 500          | μA    | 5.0        |                                |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

3: 0.1 μF capacitor on VCAP pin, PIC16F1516/7/8/9 only.

4: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

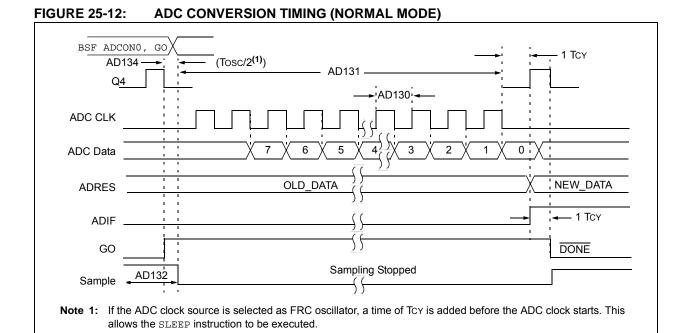

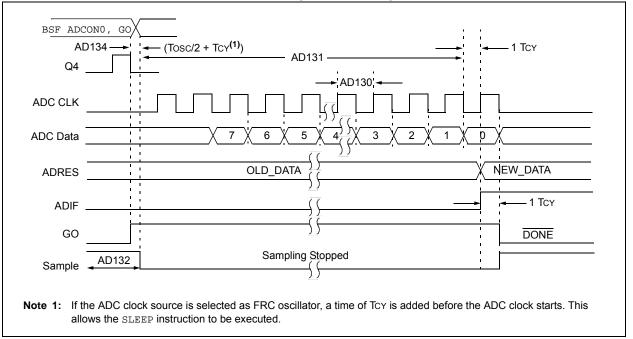

#### FIGURE 25-13: ADC CONVERSION TIMING (SLEEP MODE)

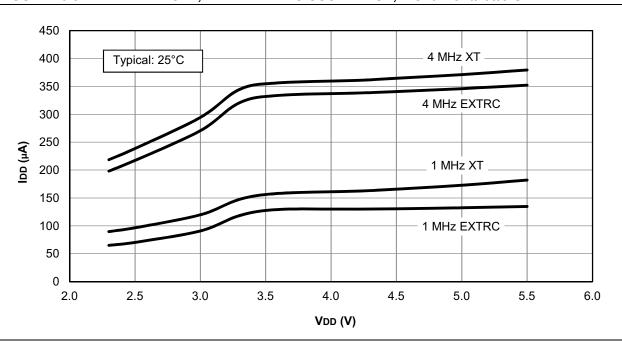

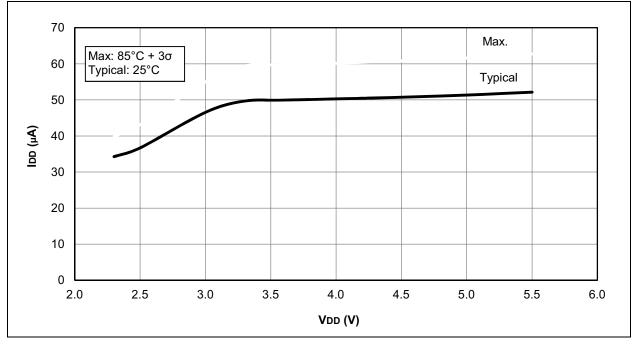

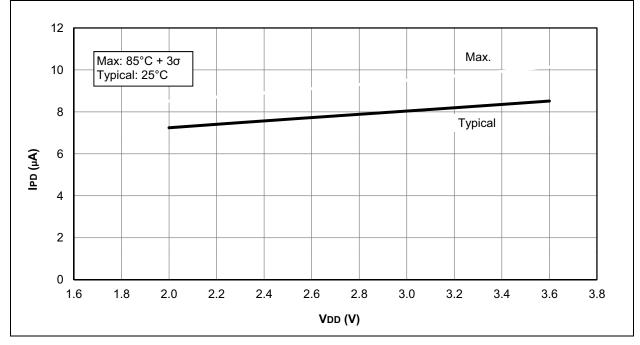

FIGURE 26-6: IDD MAXIMUM, XT AND EXTRC OSCILLATOR, PIC16F1516/7/8/9 ONLY

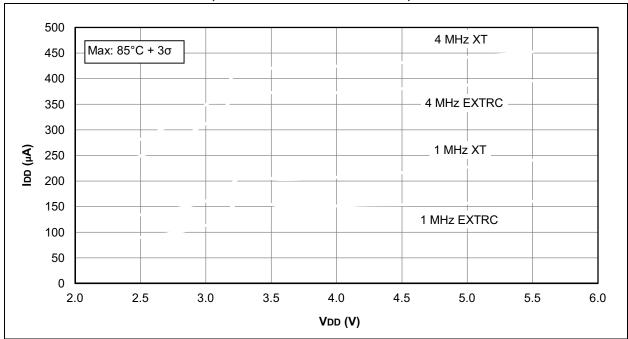

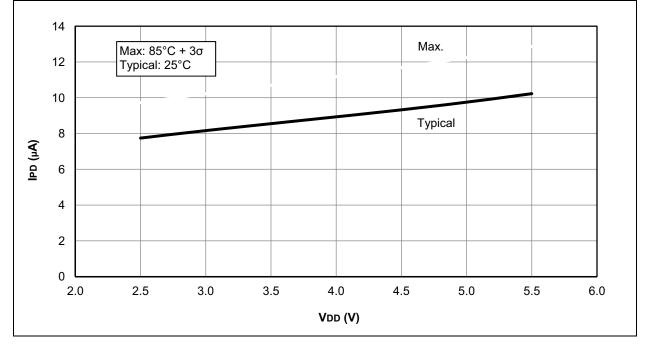

FIGURE 26-10: IDD, EC OSCILLATOR, LOW-POWER MODE, FOSC = 500 kHz, PIC16F1516/7/8/9 ONLY

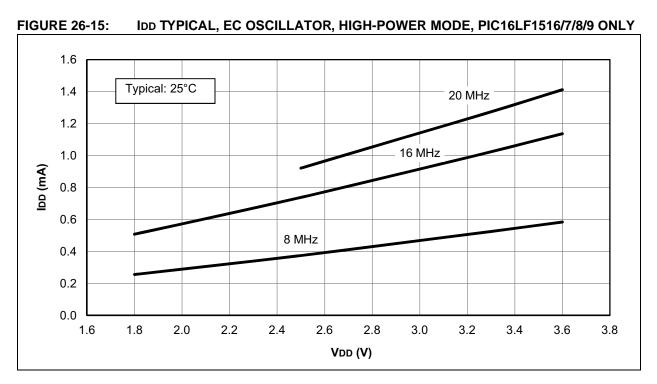

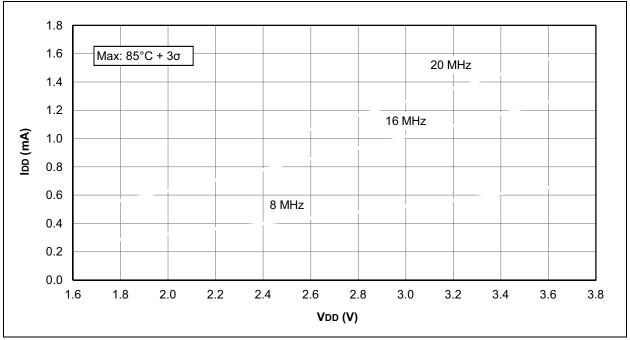

FIGURE 26-16: IDD MAXIMUM, EC OSCILLATOR, HIGH-POWER MODE, PIC16LF1516/7/8/9 ONLY

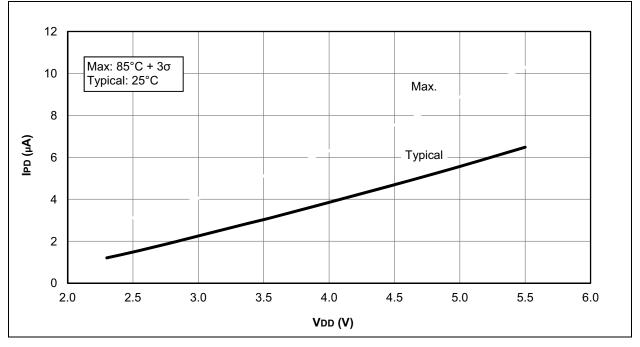

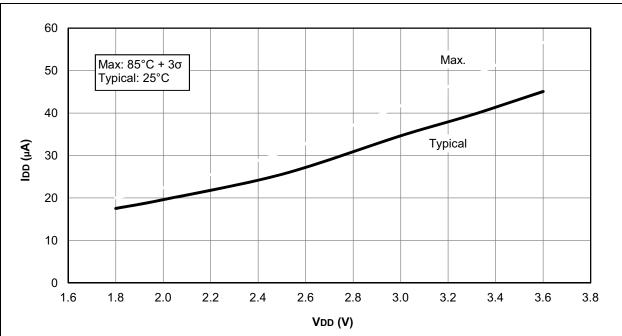

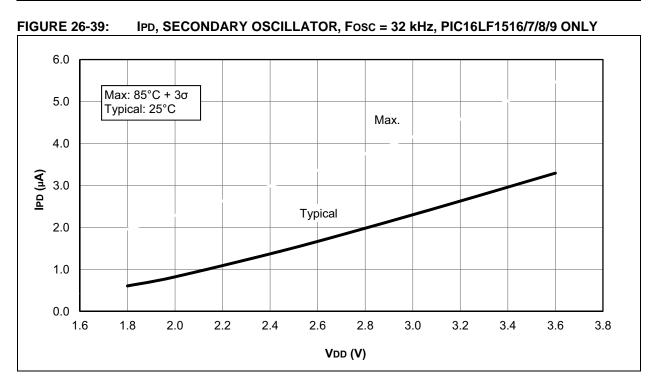

FIGURE 26-40: IPD, SECONDARY OSCILLATOR, Fosc = 32 kHz, PIC16F1516/7/8/9 ONLY