Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

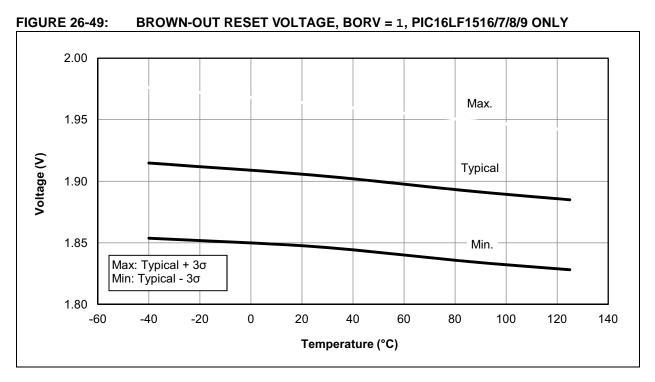

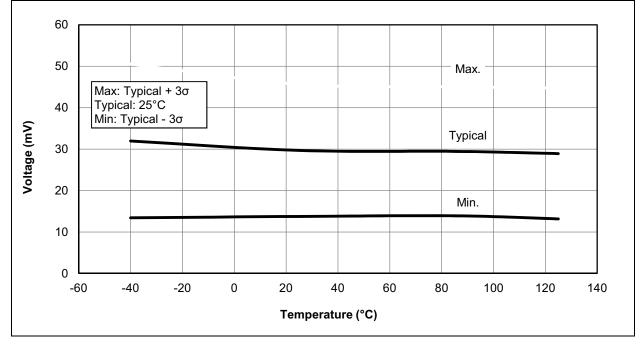

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 28x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 40-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 40-UQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1519-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F1516/7/8/9

### TABLE 1: 28/40/44-PIN ALLOCATION TABLE

| TABLE              | - ••                     | 28/40/44-PIN ALLOCATION TABLE |             |             |                         |           |             |                     |        |                   |           |         |                |

|--------------------|--------------------------|-------------------------------|-------------|-------------|-------------------------|-----------|-------------|---------------------|--------|-------------------|-----------|---------|----------------|

| O/I                | 28-Pin SPDIP, SOIC, SSOP | 28-Pin QFN, UQFN              | 40-Pin PDIP | 40-Pin UQFN | 44-Pin TQFP             | ADC       | Timers      | CCP                 | EUSART | dssm              | Interrupt | dn-llud | Basic          |

| RA0                | 2                        | 27                            | 2           | 17          | 19                      | AN0       | _           | _                   | _      | SS <sup>(2)</sup> | _         | _       | _              |

| RA1                | 3                        | 28                            | 3           | 18          | 20                      | AN1       | _           |                     | _      | _                 |           |         | —              |

| RA2                | 4                        | 1                             | 4           | 19          | 21                      | AN2       | _           |                     | —      | _                 |           |         | —              |

| RA3                | 5                        | 2                             | 5           | 20          | 22                      | AN3/VREF+ | _           | _                   | _      | _                 | -         | _       | —              |

| RA4                | 6                        | 3                             | 6           | 21          | 23                      | _         | TOCKI       | _                   | _      | _                 | -         | _       | —              |

| RA5                | 7                        | 4                             | 7           | 22          | 24                      | AN4       | _           |                     | _      | SS <sup>(1)</sup> |           |         | VCAP           |

| RA6                | 10                       | 7                             | 14          | 29          | 31                      | _         | _           |                     | —      | _                 |           |         | OSC2/CLKOUT    |

| RA7                | 9                        | 6                             | 13          | 28          | 30                      | _         | _           |                     | _      | _                 |           |         | OSC1/CLKIN     |

| RB0                | 21                       | 18                            | 33          | 8           | 8                       | AN12      | _           |                     | _      | —                 | INT/IOC   | Y       | _              |

| RB1                | 22                       | 19                            | 34          | 9           | 9                       | AN10      | _           |                     | _      | _                 | IOC       | Y       | _              |

| RB2                | 23                       | 20                            | 35          | 10          | 10                      | AN8       | _           | -                   | _      | _                 | IOC       | Y       | _              |

| RB3                | 24                       | 21                            | 36          | 11          | 11                      | AN9       | _           | CCP2 <sup>(2)</sup> | _      | _                 | IOC       | Y       | _              |

| RB4                | 25                       | 22                            | 37          | 12          | 14                      | AN11      | _           | _                   | _      | _                 | IOC       | Y       | _              |

| RB5                | 26                       | 23                            | 38          | 13          | 15                      | AN13      | T1G         | _                   | _      | _                 | IOC       | Y       | _              |

| RB6                | 27                       | 24                            | 39          | 14          | 16                      | _         | _           | _                   |        | —                 | IOC       | Y       | ICSPCLK/ICDCLK |

| RB7                | 28                       | 25                            | 40          | 15          | 17                      | _         | _           | _                   | _      | _                 | IOC       | Y       | ICSPDAT/ICDDAT |

| RC0                | 11                       | 8                             | 15          | 30          | 32                      | _         | SOSCO/T1CKI | _                   |        | _                 | _         | _       | -              |

| RC1                | 12                       | 9                             | 16          | 31          | 35                      |           | SOSCI       | CCP2 <sup>(1)</sup> | —      | _                 | _         | -       | _              |

| RC2                | 13                       | 10                            | 17          | 32          | 36                      | AN14      | _           | CCP1                | _      | _                 | _         | _       | -              |

| RC3                | 14                       | 11                            | 18          | 33          | 37                      | AN15      | _           | _                   | _      | SCK/SCL           | _         | _       | _              |

| RC4                | 15                       | 12                            | 23          | 38          | 42                      | AN16      | _           | _                   | _      | SDI/SDA           | _         | _       | _              |

| RC5                | 16                       | 13                            | 24          | 39          | 43                      | AN17      | _           | _                   | _      | SDO               | _         | _       | —              |

| RC6                | 17                       | 14                            | 25          | 40          | 44                      | AN18      | _           | _                   | TX/CK  | _                 | -         | _       | _              |

| RC7                | 18                       | 15                            | 26          | 1           | 1                       | AN19      | _           | _                   | RX/DT  | _                 | _         | -       | —              |

| RD0 <sup>(3)</sup> |                          | _                             | 19          | 34          | 38                      | AN20      | _           | _                   | _      | _                 | _         | _       | _              |

| RD1 <sup>(3)</sup> | —                        | —                             | 20          | 35          | 39                      | AN21      | _           |                     | _      | _                 |           | _       | _              |

| RD2 <sup>(3)</sup> | _                        | _                             | 21          | 36          | 40                      | AN22      | _           | _                   | _      | _                 | _         | _       | _              |

| RD3 <sup>(3)</sup> | _                        | _                             | 22          | 37          | 41                      | AN23      | _           | -                   | _      | _                 | -         | _       | _              |

| RD4 <sup>(3)</sup> |                          | _                             | 27          | 2           | 2                       | AN24      | _           | _                   |        | _                 | _         | _       | —              |

| RD5 <sup>(3)</sup> | _                        | _                             | 28          | 3           | 3                       | AN25      | _           | _                   | _      | _                 | _         | _       | _              |

| RD6 <sup>(3)</sup> |                          | _                             | 29          | 4           | 4                       | AN26      | _           | _                   | _      | _                 | _         | _       | _              |

| RD7 <sup>(3)</sup> | _                        | _                             | 30          | 5           | 5                       | AN27      | _           | -                   | _      | _                 | -         | _       | _              |

| RE0 <sup>(3)</sup> |                          | _                             | 8           | 23          | 25                      | AN5       | _           | _                   | _      | _                 | _         |         | _              |

| RE1 <sup>(3)</sup> | _                        | _                             | 9           | 24          | 26                      | AN6       | _           | _                   | _      | _                 | _         | _       | _              |

| RE2 <sup>(3)</sup> |                          |                               | 10          | 25          | 27                      | AN7       | _           | _                   | _      | _                 | _         | _       | _              |

| RE3                | 1                        | 26                            | 1           | 16          | 18                      | _         | _           | _                   | _      | _                 | _         | Y       | MCLR/VPP       |

| VDD                | 20                       | 17                            | 11,<br>32   | 7,<br>26    | 7,<br>28                | —         | —           | —                   | —      | —                 | —         | —       | —              |

| Vss                | 8,<br>19                 | 5,<br>16                      | 12,<br>31   | 6,<br>27    | 6,<br>29                | _         | _           | _                   | -      | —                 | _         | —       | _              |

| NC                 | —                        |                               | —           | —           | 12,<br>13,<br>33,<br>34 | —         | —           |                     | —      | _                 |           | _       | -              |

**Note 1:** Peripheral pin location selected using APFCON register. Default location.

2: Peripheral pin location selected using APFCON register. Alternate location.

3: PIC16(L)F1517/9 only.

## 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection is controlled independently. Internal access to the program memory is unaffected by any code protection setting.

### 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4** "Write **Protection**" for more information.

## 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

## 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 11.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the "*PIC16(L)F151X/152X Memory Programming Specification*" (DS41442).

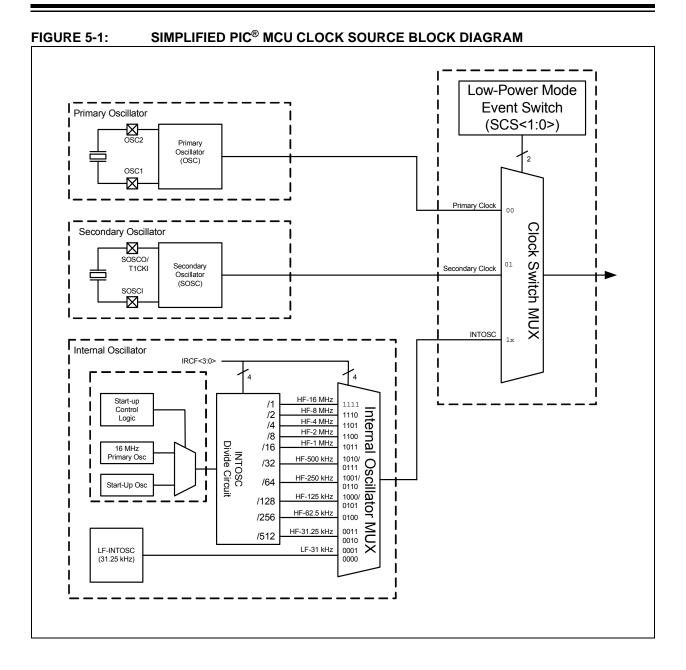

## 5.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators that are used to generate the internal system clock sources: the 16 MHz High-Frequency Internal Oscillator and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 5.3 "Clock Switching"** for additional information.

### 5.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Secondary oscillator during run time, or

- An external clock source determined by the value of the FOSC bits.

See Section 5.3 "Clock Switching" for more information.

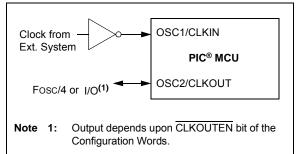

#### 5.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 5-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- High power, 4-20 MHz (FOSC = 111)

- Medium power, 0.5-4 MHz (FOSC = 110)

- Low power, 0-0.5 MHz (FOSC = 101)

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### EXTERNAL CLOCK (EC) MODE OPERATION

## 5.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 5-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 5-3 and Figure 5-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

## 6.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON register are updated to indicate the cause of the Reset. Table and Table show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, $\overline{PD}$ is set on $\overline{POR}$               |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

| TABLE 6-4: | <b>RESET CONDITION FOR SPECIAL REGISTERS</b> |

|------------|----------------------------------------------|

|------------|----------------------------------------------|

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

| R/W-1/1                                 | R/W-1/1 | R/W-1/1           | R/W-1/1                                               | R/W-1/1                            | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |

|-----------------------------------------|---------|-------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|--|

| ANSD7                                   | ANSD6   | ANSD5             | ANSD4                                                 | ANSD3                              | ANSD2   | ANSD1   | ANSD0   |  |  |

| bit 7                                   |         |                   |                                                       |                                    |         |         | bit 0   |  |  |

|                                         |         |                   |                                                       |                                    |         |         |         |  |  |

| Legend:                                 |         |                   |                                                       |                                    |         |         |         |  |  |

| R = Readable                            | bit     | W = Writable      | bit                                                   | U = Unimplemented bit, read as '0' |         |         |         |  |  |

| u = Bit is unchanged x = Bit is unknown |         |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared                                                  |                                    |         |         |         |  |  |

#### REGISTER 12-18: ANSELD: PORTD ANALOG SELECT REGISTER

bit 7-0 ANSD<7:0>: Analog Select between Analog or Digital Function on pins RD<7:0>, respectively 0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

Note 1: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| TABLE 12-9: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTD <sup>(1)</sup> |

|-------------|-----------------------------------------------------------|

| TABLE 12-9: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTD                |

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELD | ANSD7  | ANSD6  | ANSD5  | ANSD4  | ANSD3  | ANSD2  | ANSD1  | ANSD0  | 118                 |

| LATD   | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | 117                 |

| PORTD  | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | 117                 |

| TRISD  | TRISD7 | TRISD6 | TRISB5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | 117                 |

x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Legend: PORTD.

Note 1: PIC16F1517/1519 only.

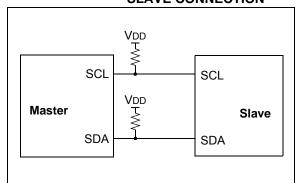

## 21.3 I<sup>2</sup>C MODE OVERVIEW

The Inter-Integrated Circuit Bus (I<sup>2</sup>C) is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A Slave device is controlled through addressing.

The I<sup>2</sup>C bus specifies two signal connections:

- Serial Clock (SCL)

- Serial Data (SDA)

Figure 21-1 shows the block diagram of the MSSP module when operating in  $I^2C$  mode.

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 21-11 shows a typical connection between two processors configured as master and slave devices.

The I<sup>2</sup>C bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode (master is transmitting data to a slave)

- Master Receive mode (master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDA line while the SCL line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

## FIGURE 21-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDA line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of a data bit is always performed while the SCL line is held low. Transitions that occur while the SCL line is held high are used to indicate Start and Stop bits.

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an  $\overrightarrow{ACK}$  bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an ACK bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDA line while the SCL line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last ACK bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

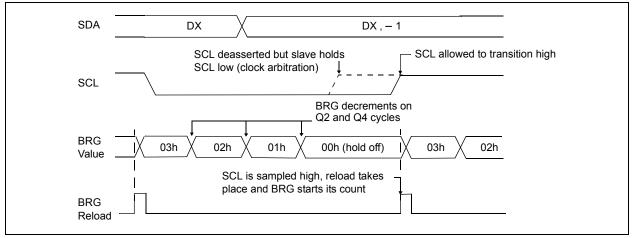

## 21.6.2 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<7:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 21-25).

## FIGURE 21-25: BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

## 21.6.3 WCOL STATUS FLAG

If the user writes the SSPBUF when a Start, Restart, Stop, Receive or Transmit sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur). Any time the WCOL bit is set it indicates that an action on SSPBUF was attempted while the module was not idle.

| Note: | Because queuing of events is not allowed, |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|

|       | writing to the lower five bits of SSPCON2 |  |  |  |  |  |  |  |  |

|       | is disabled until the Start condition is  |  |  |  |  |  |  |  |  |

|       | complete.                                 |  |  |  |  |  |  |  |  |

| R/W-1/1          | R/W-1/1             | R/W-1/1                                                                                                                                                                                   | R/W-1/1         | R/W-1/1                                               | R/W-1/1       | R/W-1/1 | R/W-1/1 |  |  |  |

|------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------|---------------|---------|---------|--|--|--|

|                  |                     |                                                                                                                                                                                           | MSK             | <7:0>                                                 |               |         |         |  |  |  |

| bit 7            |                     |                                                                                                                                                                                           |                 |                                                       |               |         | bit 0   |  |  |  |

|                  |                     |                                                                                                                                                                                           |                 |                                                       |               |         |         |  |  |  |

| Legend:          |                     |                                                                                                                                                                                           |                 |                                                       |               |         |         |  |  |  |

| R = Readable bit |                     | W = Writable                                                                                                                                                                              | bit             | U = Unimplemented bit, read as '0'                    |               |         |         |  |  |  |

| u = Bit is unch  | nanged              | x = Bit is unkr                                                                                                                                                                           | nown            | -n/n = Value at POR and BOR/Value at all other Resets |               |         |         |  |  |  |

| '1' = Bit is set |                     | '0' = Bit is cle                                                                                                                                                                          | ared            |                                                       |               |         |         |  |  |  |

|                  |                     |                                                                                                                                                                                           |                 |                                                       |               |         |         |  |  |  |

| bit 7-1          | MSK<7:1>: Mask bits |                                                                                                                                                                                           |                 |                                                       |               |         |         |  |  |  |

|                  | 1 = The rec         | L = The received address bit n is compared to SSPADD <n> to detect I<sup>2</sup>C address match<br/>D = The received address bit n is not used to detect I<sup>2</sup>C address match</n> |                 |                                                       |               |         |         |  |  |  |

|                  | 0 = The rec         | eived address b                                                                                                                                                                           | it n is not use | d to detect I <sup>2</sup> C                          | address match |         |         |  |  |  |

## REGISTER 21-7: SSPMSK: SSP MASK REGISTER

|       | 1 = The received address bit n is compared to SSPADD <n> to detect <math>I^2C</math> address match 0 = The received address bit n is not used to detect <math>I^2C</math> address match</n>                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 0 | <b>MSK&lt;0&gt;:</b> Mask bit for I <sup>2</sup> C Slave mode, 10-bit Address<br>I <sup>2</sup> C Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111):<br>1 = The received address bit 0 is compared to SSPADD<0> to detect I <sup>2</sup> C address match |

|       | 0 = The received address bit 0 is compared to 337ADD<02 to detect 1 C address match<br>0 = The received address bit 0 is not used to detect I <sup>2</sup> C address match<br>I <sup>2</sup> C Slave mode, 7-bit address, the bit is ignored                 |

## REGISTER 21-8: SSPADD: MSSP ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

|                                                                                            |         |                   |         |              |                  |              | -,      |

|--------------------------------------------------------------------------------------------|---------|-------------------|---------|--------------|------------------|--------------|---------|

| R/W-0/0                                                                                    | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0      | R/W-0/0          | R/W-0/0      | R/W-0/0 |

|                                                                                            |         |                   | ADD     | <7:0>        |                  |              |         |

| bit 7                                                                                      |         |                   |         |              |                  |              | bit 0   |

|                                                                                            |         |                   |         |              |                  |              |         |

| Legend:                                                                                    |         |                   |         |              |                  |              |         |

| R = Readable                                                                               | bit     | W = Writable b    | oit     | U = Unimpler | nented bit, read | d as '0'     |         |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Res |         |                   |         |              |                  | other Resets |         |

| '1' = Bit is set                                                                           |         | '0' = Bit is clea | ared    |              |                  |              |         |

#### Master mode:

| bit 7-0 | ADD<7:0>: Baud Rate Clock Divider bits          |

|---------|-------------------------------------------------|

|         | SCL pin clock period = ((ADD<7:0> + 1) *4)/Fosc |

#### <u>10-Bit Slave mode — Most Significant Address Byte:</u>

- bit 7-3 **Not used:** Unused for Most Significant Address byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### <u>10-Bit Slave mode — Least Significant Address Byte:</u>

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-Bit Slave mode:

| bit 7-1 | ADD<7:1>: 7-bit address |

|---------|-------------------------|

|         |                         |

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### 22.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 22-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 22.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

**Note 1:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

## 22.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 22.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

| Note: | If the receive FIFO is overrun, no additional |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|

|       | characters will be received until the overrun |  |  |  |  |  |  |  |

|       | condition is cleared. See Section 22.1.2.5    |  |  |  |  |  |  |  |

|       | "Receive Overrun Error" for more              |  |  |  |  |  |  |  |

|       | information on overrun errors.                |  |  |  |  |  |  |  |

## 22.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE, Interrupt Enable bit of the PIE1 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

| R-0/0            | R-1/1                              | U-0                                         | R/W-0/0                             | R/W-0/0          | U-0               | R/W-0/0           | R/W-0/0       |  |  |  |  |

|------------------|------------------------------------|---------------------------------------------|-------------------------------------|------------------|-------------------|-------------------|---------------|--|--|--|--|

| ABDOVF           | RCIDL                              |                                             | SCKP                                | BRG16            |                   | WUE               | ABDEN         |  |  |  |  |

| bit 7            |                                    | •                                           |                                     | •                |                   |                   | bit C         |  |  |  |  |

| Legend:          |                                    |                                             |                                     |                  |                   |                   |               |  |  |  |  |

| R = Readable     | bit                                | W = Writable                                | e bit                               | U = Unimple      | mented bit, rea   | d as '0'          |               |  |  |  |  |

| u = Bit is unch  |                                    | x = Bit is unl                              |                                     | •                | -                 | DR/Value at all c | ther Resets   |  |  |  |  |

| '1' = Bit is set | •                                  | '0' = Bit is cl                             | eared                               |                  |                   |                   |               |  |  |  |  |

|                  |                                    |                                             |                                     |                  |                   |                   |               |  |  |  |  |

| bit 7            |                                    |                                             | ct Overflow bit                     |                  |                   |                   |               |  |  |  |  |

|                  | Asynchronou                        | i <u>s mode</u> :<br>id timer overflo       | wed                                 |                  |                   |                   |               |  |  |  |  |

|                  |                                    | d timer did no                              |                                     |                  |                   |                   |               |  |  |  |  |

|                  | Synchronous                        | <u>mode</u> :                               |                                     |                  |                   |                   |               |  |  |  |  |

|                  | Don't care                         |                                             |                                     |                  |                   |                   |               |  |  |  |  |

| bit 6            |                                    | eive Idle Flag b                            | bit                                 |                  |                   |                   |               |  |  |  |  |

|                  | <u>Asynchronou</u><br>1 = Receiver |                                             |                                     |                  |                   |                   |               |  |  |  |  |

|                  |                                    |                                             | ved and the red                     | ceiver is receiv | /ing              |                   |               |  |  |  |  |

|                  | Synchronous                        |                                             |                                     |                  | 0                 |                   |               |  |  |  |  |

|                  | Don't care                         |                                             |                                     |                  |                   |                   |               |  |  |  |  |

| bit 5            | -                                  | nted: Read as                               |                                     |                  |                   |                   |               |  |  |  |  |

| bit 4            | -                                  | SCKP: Synchronous Clock Polarity Select bit |                                     |                  |                   |                   |               |  |  |  |  |

|                  | Asynchronou                        |                                             |                                     |                  |                   |                   |               |  |  |  |  |

|                  | 0 = Transmit                       | non-inverted of                             | to the TX/CK pi<br>lata to the TX/0 |                  |                   |                   |               |  |  |  |  |

|                  |                                    |                                             | on the falling e                    | dge of the clo   | ck. Received d    | ata is sampled o  | on the rising |  |  |  |  |

|                  | 0 = Transmit                       |                                             | on the rising e                     | dge of the cloo  | ck. Received da   | ata is sampled o  | n the falling |  |  |  |  |

| bit 3            | <b>BRG16:</b> 16-b                 | oit Baud Rate                               | Generator bit                       |                  |                   |                   |               |  |  |  |  |

|                  |                                    | aud Rate Gener<br>ud Rate Gener             |                                     |                  |                   |                   |               |  |  |  |  |

| bit 2            | Unimplemer                         | nted: Read as                               | <b>'</b> 0 <b>'</b>                 |                  |                   |                   |               |  |  |  |  |

| bit 1            | WUE: Wake-                         | up Enable bit                               |                                     |                  |                   |                   |               |  |  |  |  |

|                  | <u>Asynchronou</u>                 |                                             |                                     |                  |                   |                   |               |  |  |  |  |

|                  | automatio                          | cally clear after                           | RCIF is set.                        | No character w   | vill be received, | RCIF bit will be  | set. WUE wil  |  |  |  |  |

|                  |                                    | is operating n                              | ormally                             |                  |                   |                   |               |  |  |  |  |

|                  | <u>Synchronous</u><br>Don't care   | <u>i mode</u> .                             |                                     |                  |                   |                   |               |  |  |  |  |

| bit 0            |                                    | o-Baud Detect                               | Enable bit                          |                  |                   |                   |               |  |  |  |  |

|                  | ASynchronou                        |                                             |                                     |                  |                   |                   |               |  |  |  |  |

|                  | -                                  |                                             | le is enabled (c                    | lears when a     | to-baud is com    | plete)            |               |  |  |  |  |

|                  |                                    | ud Detect mod                               |                                     |                  |                   |                   |               |  |  |  |  |

|                  | Synchronous                        | <u>mode</u> :                               |                                     |                  |                   |                   |               |  |  |  |  |

|                  | Don't care                         |                                             |                                     |                  |                   |                   |               |  |  |  |  |

## REGISTER 22-3: BAUDCON: BAUD RATE CONTROL REGISTER

## 22.4.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TXSTA register. The Break character transmission is then initiated by a write to the TXREG. The value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TXSTA register indicates when the transmit operation is active or idle, just as it does during normal transmission. See Figure 22-9 for the timing of the Break character sequence.

#### 22.4.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### **FIGURE 22-9:** SEND BREAK CHARACTER SEQUENCE Write to TXREG -Dummy Write **BRG** Output (Shift Clock) TX (pin) Start bit bit 0 bit 1 Stop bit Break TXIF bit (Transmit Interrupt Flag) TRMT bit (Transmit Shift Empty Flag) SENDB Sampled Here Auto Cleared SENDB (send Break control bit)

## 22.4.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCSTA register and the Received data as indicated by RCREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when;

- RCIF bit is set

- FERR bit is set

- RCREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 22.4.3** "**Auto-Wake-up on Break**". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDCON register before placing the EUSART in Sleep mode.

| Mnemonic,<br>Operands |      | Description                   |          | 14-Bit Opcode |      |      |      | Status   | Natas |

|-----------------------|------|-------------------------------|----------|---------------|------|------|------|----------|-------|

|                       |      | Description                   | Cycles   | MSb           |      |      | LSb  | Affected | Notes |

|                       |      | BYTE-ORIENTED FILE REG        | STER OPE | RATIC         | NS   |      |      |          |       |

| ADDWF                 | f, d | Add W and f                   | 1        | 00            | 0111 | dfff | ffff | C, DC, Z | 2     |

| ADDWFC                | f, d | Add with Carry W and f        | 1        | 11            | 1101 | dfff | ffff | C, DC, Z | 2     |

| ANDWF                 | f, d | AND W with f                  | 1        | 00            | 0101 | dfff | ffff | Z        | 2     |

| ASRF                  | f, d | Arithmetic Right Shift        | 1        | 11            | 0111 | dfff | ffff | C, Z     | 2     |

| LSLF                  | f, d | Logical Left Shift            | 1        | 11            | 0101 | dfff | ffff | C, Z     | 2     |

| LSRF                  | f, d | Logical Right Shift           | 1        | 11            | 0110 | dfff | ffff | C, Z     | 2     |

| CLRF                  | f    | Clear f                       | 1        | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW                  | -    | Clear W                       | 1        | 00            | 0001 | 0000 | 00xx | Z        |       |

| COMF                  | f, d | Complement f                  | 1        | 00            | 1001 | dfff | ffff | Z        | 2     |

| DECF                  | f, d | Decrement f                   | 1        | 00            | 0011 | dfff |      | Z        | 2     |

| INCF                  | f, d | Increment f                   | 1        | 00            | 1010 | dfff | ffff | Z        | 2     |

| IORWF                 | f, d | Inclusive OR W with f         | 1        | 00            | 0100 | dfff | ffff | Z        | 2     |

| MOVF                  | f, d | Move f                        | 1        | 00            | 1000 | dfff | ffff | Z        | 2     |

| MOVWF                 | f    | Move W to f                   | 1        | 00            | 0000 | lfff | ffff |          | 2     |

| RLF                   | f, d | Rotate Left f through Carry   | 1        | 00            | 1101 | dfff | ffff | С        | 2     |

| RRF                   | f, d | Rotate Right f through Carry  | 1        | 00            | 1100 | dfff | ffff | С        | 2     |

| SUBWF                 | f, d | Subtract W from f             | 1        | 00            | 0010 | dfff | ffff | C, DC, Z | 2     |

| SUBWFB                | f, d | Subtract with Borrow W from f | 1        | 11            | 1011 | dfff | ffff | C, DC, Z | 2     |

| SWAPF                 | f, d | Swap nibbles in f             | 1        | 00            | 1110 | dfff | ffff |          | 2     |

| XORWF                 | f, d | Exclusive OR W with f         | 1        | 00            | 0110 | dfff | ffff | Z        | 2     |

|                       |      | BYTE-ORIENTED SKIF            | OPERATI  | ONS           |      |      |      |          |       |

| DECFSZ                | f, d | Decrement f, Skip if 0        | 1(2)     | 00            | 1011 | dfff | ffff |          | 1, 2  |

| INCFSZ                | f, d | Increment f, Skip if 0        | 1(2)     | 00            | 1111 | dfff | ffff |          | 1, 2  |

|                       |      | BIT-ORIENTED FILE REGIS       |          | RATION        | NS   |      |      | 1        |       |

| BCF                   | f, b | Bit Clear f                   | 1        | 01            | 00bb | bfff | ffff |          | 2     |

| BSF                   | f, b | Bit Set f                     | 1        | 01            | 01bb | bfff | ffff |          | 2     |

|                       |      | BIT-ORIENTED SKIP             | OPERATIO | NS            |      |      |      |          |       |

| BTFSC                 | f, b | Bit Test f, Skip if Clear     | 1 (2)    | 01            | 10bb | bfff | ffff |          | 1, 2  |

| BTFSS                 | f, b | Bit Test f, Skip if Set       | 1 (2)    | 01            | 11bb | bfff | ffff |          | 1, 2  |

| LITERAL               |      |                               |          | 1             |      |      |      | 1        |       |

| ADDLW                 | k    | Add literal and W             | 1        | 11            | 1110 | kkkk |      | C, DC, Z |       |

| ANDLW                 | k    | AND literal with W            | 1        | 11            |      | kkkk |      | Z        |       |

| IORLW                 | k    | Inclusive OR literal with W   | 1        | 11            | 1000 | kkkk |      | Z        |       |

| MOVLB                 | k    | Move literal to BSR           | 1        | 00            | 0000 | 001k |      |          |       |

| MOVLP                 | k    | Move literal to PCLATH        | 1        | 11            | 0001 | 1kkk | kkkk |          |       |

| MOVLW                 | k    | Move literal to W             | 1        | 11            |      | kkkk |      |          |       |

| SUBLW                 | k    | Subtract W from literal       | 1        | 11            | 1100 |      |      | C, DC, Z |       |

| XORLW                 | k    | Exclusive OR literal with W   | 1        | 11            | 1010 | kkkk | kkkk | Z        |       |

## TABLE 24-3: INSTRUCTION SET

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

## 25.5 DC Characteristics: Power-Down Currents (IPD) (Continued)

| PIC16LF1516/7/8/9                           |                        |      |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                |       |            |                          |  |  |

|---------------------------------------------|------------------------|------|------|------------------------------------------------------|----------------|-------|------------|--------------------------|--|--|

| PIC16F1516/7/8/9                            |                        |      |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                |       |            |                          |  |  |

| Param                                       | Device Characteristics | Min. | Тур† | Max.<br>+85°C                                        | Max.<br>+125°C | Units | Conditions |                          |  |  |

| No.                                         |                        |      |      |                                                      |                |       | Vdd        | Note                     |  |  |

| Power-down Currents (IPD) <sup>(2, 4)</sup> |                        |      |      |                                                      |                |       |            |                          |  |  |

| D026A*                                      |                        | _    | 250  | —                                                    | _              | μA    | 1.8        | ADC Current (Note 1, 3), |  |  |

|                                             |                        | _    | 250  |                                                      | _              | μA    | 3.0        | conversion in progress   |  |  |

| D026A*                                      |                        | _    | 280  |                                                      | _              | μA    | 2.3        | ADC Current (Note 1, 3), |  |  |

|                                             |                        | _    | 280  |                                                      | _              | μA    | 3.0        | conversion in progress   |  |  |

|                                             |                        | _    | 280  |                                                      | _              | μA    | 5.0        | ]                        |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral △ current can be determined by subtracting the base IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

3: ADC clock source is FRC.

4: VREGPM = 1, PIC16F1516/7/8/9 only.

## PIC16(L)F1516/7/8/9

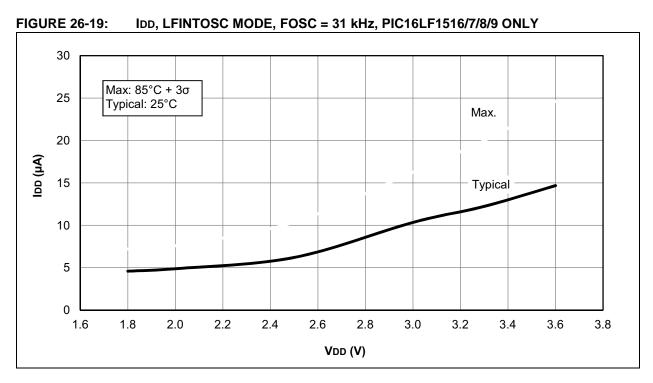

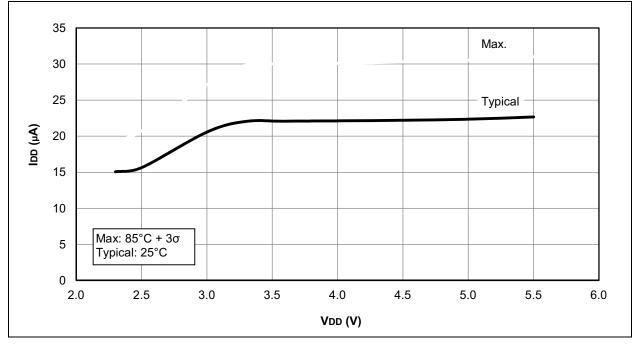

FIGURE 26-20: IDD, LFINTOSC MODE, FOSC = 31 kHz, PIC16F1516/7/8/9 ONLY

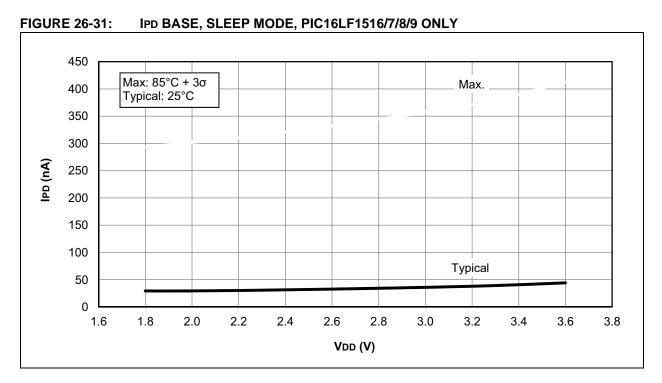

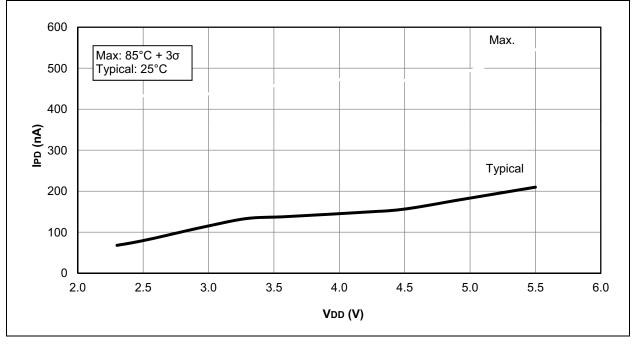

FIGURE 26-32: IPD BASE, LOW-POWER SLEEP MODE (VREGPM = 1), PIC16F1516/7/8/9 ONLY

## PIC16(L)F1516/7/8/9

## 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

Microchip Technology Drawing C04-105C Sheet 1 of 2

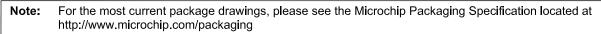

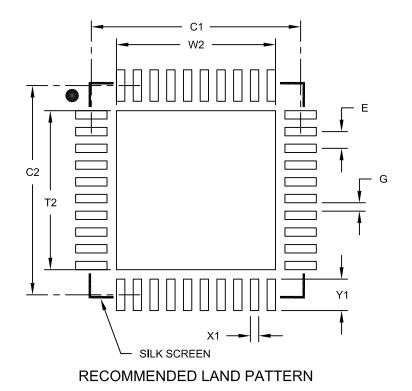

## 40-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) - 5x5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |      |      |      |  |

|----------------------------|-------------|------|------|------|--|

| Dimensio                   | MIN         | NOM  | MAX  |      |  |

| Contact Pitch              | 0.40 BSC    |      |      |      |  |

| Optional Center Pad Width  | W2          |      |      | 3.80 |  |

| Optional Center Pad Length | T2          |      |      | 3.80 |  |

| Contact Pad Spacing        | C1          |      | 5.00 |      |  |

| Contact Pad Spacing        | C2          |      | 5.00 |      |  |

| Contact Pad Width (X40)    | X1          |      |      | 0.20 |  |

| Contact Pad Length (X40)   | Y1          |      |      | 0.75 |  |

| Distance Between Pads      | G           | 0.20 |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2156B