Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 28x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1519-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3-3: PIC16(L)F1516/7 MEMORY MAP (CONTINUED)

|              | Bank 31                               |

|--------------|---------------------------------------|

| F80h         | Core Registers<br>(Table 3-2)         |

| F8Bh<br>F8Ch |                                       |

|              | Unimplemented<br>Read as '0'          |

| FE3h         |                                       |

| FE4h         | STATUS_SHAD                           |

| FE5h         | WREG_SHAD                             |

| FE6h         | BSR_SHAD                              |

| FE7h         | PCLATH_SHAD                           |

| FE8h         | FSR0L_SHAD                            |

| FE9h         | FSR0H_SHAD                            |

| FEAh         | FSR1L_SHAD                            |

| FEBh         | FSR1H_SHAD                            |

| FECh         | —                                     |

| FEDh         | STKPTR                                |

| FEEh         | TOSL                                  |

| FEFh         | TOSH                                  |

| FF0h         | Common RAM<br>(Accesses<br>70h – 7Fh) |

| FFFh         |                                       |

= Unimplemented data memory locations, read as '0',

## 6.13 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON register bits are shown in Register 6-2.

### 6.14 Register Definitions: Power Control

#### REGISTER 6-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q  | R/W/HS-0/q | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|-------------|------------|-----|------------|------------|------------|------------|------------|

| STKOVF      | STKUNF     | —   | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7 bit 0 |            |     |            |            | bit 0      |            |            |

| Legend:                         |                      |                                                       |

|---------------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by hardware |                      | HS = Bit is set by hardware                           |

| R = Readable bit                | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged            | x = Bit is unknown   | -m/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set                | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7 | <ul> <li>STKOVF: Stack Overflow Flag bit</li> <li>1 = A Stack Overflow occurred</li> <li>0 = A Stack Overflow has not occurred or cleared by firmware</li> </ul>                       |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>STKUNF:</b> Stack Underflow Flag bit<br>1 = A Stack Underflow occurred<br>0 = A Stack Underflow has not occurred or cleared by firmware                                             |

| bit 5 | Unimplemented: Read as '0'                                                                                                                                                             |

| bit 4 | <b>RWDT:</b> Watchdog Timer Reset Flag bit<br>1 = A Watchdog Timer Reset has not occurred or set to '1' by firmware<br>0 = A Watchdog Timer Reset has occurred (cleared by hardware)   |

| bit 3 | <b>RMCLR:</b> MCLR Reset Flag bit<br>1 = A MCLR Reset has not occurred or set to '1' by firmware<br>0 = A MCLR Reset has occurred (cleared by hardware)                                |

| bit 2 | <b>RI:</b> RESET Instruction Flag bit<br>1 = A RESET instruction has not been executed or set to '1' by firmware<br>0 = A RESET instruction has been executed (cleared by hardware)    |

| bit 1 | <b>POR</b> : Power-on Reset Status bit<br>1 = No Power-on Reset occurred<br>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                      |

| bit 0 | <b>BOR:</b> Brown-out Reset Status bit<br>1 = No Brown-out Reset occurred<br>0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurs) |

|       |                                                                                                                                                                                        |

| R/W-0/0          | R/W-0/0                                                                                                       | R/W-0/0                            | R/W-0/0       | R/W-0/0         | R/W-0/0          | R/W-0/0  | R/W-0/0     |  |

|------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------|---------------|-----------------|------------------|----------|-------------|--|

| TMR1GIE          | ADIE                                                                                                          | RCIE                               | TXIE          | SSPIE           | CCP1IE           | TMR2IE   | TMR1IE      |  |

| bit 7            |                                                                                                               |                                    |               |                 |                  |          | bit         |  |

| Legend:          |                                                                                                               |                                    |               |                 |                  |          |             |  |

| R = Readable     | bit                                                                                                           | W = Writable                       | bit           | U = Unimpler    | mented bit, read | l as '0' |             |  |

| u = Bit is unch  |                                                                                                               | x = Bit is unkr                    |               | •               | at POR and BO    |          | ther Resets |  |

| '1' = Bit is set | 0.1                                                                                                           | '0' = Bit is clea                  | ared          |                 |                  |          |             |  |

|                  |                                                                                                               |                                    |               |                 |                  |          |             |  |

| bit 7            |                                                                                                               | mer1 Gate Inte                     | •             |                 |                  |          |             |  |

|                  |                                                                                                               | the Timer1 Gate<br>the Timer1 Gat  |               |                 |                  |          |             |  |

| bit 6            | ADIE: Analog                                                                                                  | g-to-Digital Con                   | verter (ADC)  | Interrupt Enabl | le bit           |          |             |  |

|                  |                                                                                                               | 1 = Enables the ADC interrupt      |               |                 |                  |          |             |  |

|                  | 0 = Disables the ADC interrupt                                                                                |                                    |               |                 |                  |          |             |  |

| bit 5            |                                                                                                               | RT Receive Interrupt Enable bit    |               |                 |                  |          |             |  |

|                  | <ul> <li>1 = Enables the USART receive interrupt</li> <li>0 = Disables the USART receive interrupt</li> </ul> |                                    |               |                 |                  |          |             |  |

| bit 4            |                                                                                                               | T Transmit Inter                   |               | it              |                  |          |             |  |

|                  | 1 = Enables the USART transmit interrupt                                                                      |                                    |               |                 |                  |          |             |  |

|                  | 0 = Disables the USART transmit interrupt                                                                     |                                    |               |                 |                  |          |             |  |

| bit 3            |                                                                                                               | hronous Serial                     | . ,           | Interrupt Enabl | le bit           |          |             |  |

|                  | 1 = Enables the MSSP interrupt<br>0 = Disables the MSSP interrupt                                             |                                    |               |                 |                  |          |             |  |

| hit O            |                                                                                                               |                                    |               |                 |                  |          |             |  |

| bit 2            |                                                                                                               | P1 Interrupt En<br>the CCP1 interr |               |                 |                  |          |             |  |

|                  |                                                                                                               | the CCP1 inter                     |               |                 |                  |          |             |  |

| bit 1            |                                                                                                               | R2 to PR2 Mate                     |               | nable bit       |                  |          |             |  |

|                  | 1 = Enables the Timer2 to PR2 match interrupt                                                                 |                                    |               |                 |                  |          |             |  |

|                  | 0 = Disables the Timer2 to PR2 match interrupt                                                                |                                    |               |                 |                  |          |             |  |

| bit 0            |                                                                                                               | er1 Overflow Ir                    |               |                 |                  |          |             |  |

|                  |                                                                                                               | the Timer1 over                    |               |                 |                  |          |             |  |

|                  |                                                                                                               | the Timer1 ove                     | mow interrupt |                 |                  |          |             |  |

| Note: Bit        |                                                                                                               | TCON register                      | must he       |                 |                  |          |             |  |

|                  | to enable any                                                                                                 |                                    |               |                 |                  |          |             |  |

### REGISTER 7-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

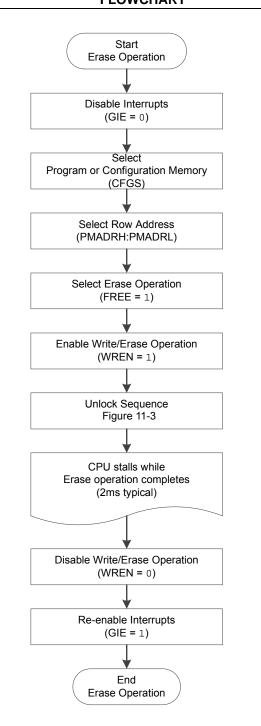

#### 11.2.3 ERASING FLASH PROGRAM MEMORY

While executing code, program memory can only be erased by rows. To erase a row:

- 1. Load the PMADRH:PMADRL register pair with any address within the row to be erased.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Set the FREE and WREN bits of the PMCON1 register.

- 4. Write 55h, then AAh, to PMCON2 (Flash programming unlock sequence).

- 5. Set control bit WR of the PMCON1 register to begin the erase operation.

#### See Example 11-2.

After the "BSF PMCON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions immediately following the WR bit set instruction. The processor will halt internal operations for the typical 2 ms erase time. This is not Sleep mode as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the PMCON1 write instruction.

# FIGURE 11-4: FLAS

#### FLASH PROGRAM MEMORY ERASE FLOWCHART

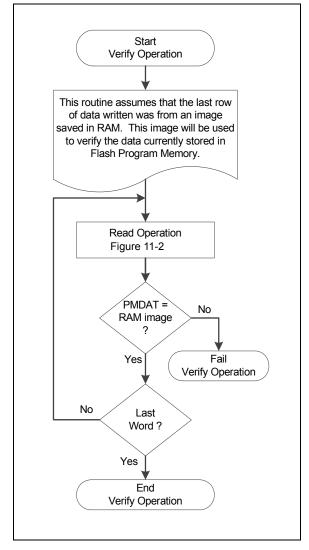

### 11.5 Write Verify

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full page then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

FIGURE 11-8: FLASH PROGRAM MEMORY VERIFY FLOWCHART

### 12.6 PORTE Registers

#### 12.6.1 DATA REGISTER

PORTE is a 4-bit wide, bidirectional port. The corresponding data direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). The exception is RE3, which is input only and its TRIS bit will always read as '1'. Example 12-1 shows how to initialize an I/O port.

Reading the PORTE register (Register 12-19) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATE). RE3 reads '0' when MCLRE = 1.

| Note: | RE<2:0>     | and    | TRISE<2:0>     | pins  | are |

|-------|-------------|--------|----------------|-------|-----|

|       | available o | on PIC | 16(L)F1517/9 c | only. |     |

#### 12.6.2 ANALOG CONTROL

The ANSELE register (Register 12-22) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELE bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELE bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

The TRISE register (Register 12-20) controls the PORTE pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISE register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSELE bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

#### 12.6.3 PORTE FUNCTIONS AND OUTPUT PRIORITIES

PORTE has no peripheral outputs, so the PORTE output has no priority function.

# 19.5 Register Definitions: Timer2 Control

| U-0                  | R/W-0/0                | R/W-0/0                                        | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |  |

|----------------------|------------------------|------------------------------------------------|----------------|----------------|------------------|----------------|--------------|--|

| _                    |                        | T2OUT                                          | PS<3:0>        |                | TMR2ON           | T2CKF          | 'S<1:0>      |  |

| bit 7                |                        |                                                |                |                |                  |                | bit          |  |

|                      |                        |                                                |                |                |                  |                |              |  |

| Legend:              |                        |                                                |                |                |                  |                |              |  |

| R = Readable bit     |                        | W = Writable bit                               |                | -              | mented bit, read |                |              |  |

| u = Bit is unchanged |                        | x = Bit is unkr                                | iown           | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |  |

| '1' = Bit is s       | et                     | '0' = Bit is clea                              | ared           |                |                  |                |              |  |

| bit 7                | Unimpleme              | ented: Read as '                               | 0'             |                |                  |                |              |  |

| bit 6-3              | T2OUTPS<               | 3:0>: Timer2 Ou                                | tput Postscale | er Select bits |                  |                |              |  |

|                      | 1111 <b>= 1:16</b>     | Postscaler                                     |                |                |                  |                |              |  |

|                      | 1110 <b>= 1:15</b>     | 1110 = 1:15 Postscaler                         |                |                |                  |                |              |  |

|                      | 1101 = 1:14 Postscaler |                                                |                |                |                  |                |              |  |

|                      | 1100 = 1:13 Postscaler |                                                |                |                |                  |                |              |  |

|                      | 1011 = 1:12 Postscaler |                                                |                |                |                  |                |              |  |

|                      | 1010 = 1:11 Postscaler |                                                |                |                |                  |                |              |  |

|                      | 1001 = 1:10 Postscaler |                                                |                |                |                  |                |              |  |

|                      | 1000 = 1:9 Postscaler  |                                                |                |                |                  |                |              |  |

|                      |                        | 0111 = 1:8 Postscaler<br>0110 = 1:7 Postscaler |                |                |                  |                |              |  |

|                      |                        | 0110 = 1.7 Postscaler                          |                |                |                  |                |              |  |

|                      | 0100 = 1.5 Postscaler  |                                                |                |                |                  |                |              |  |

|                      | 0011 = 1:4             |                                                |                |                |                  |                |              |  |

|                      | 0010 <b>= 1</b> :3     | Postscaler                                     |                |                |                  |                |              |  |

|                      | 0001 = 1:2             | Postscaler                                     |                |                |                  |                |              |  |

|                      | 0000 = 1:1             | Postscaler                                     |                |                |                  |                |              |  |

| bit 2                | TMR2ON: T              | ïmer2 On bit                                   |                |                |                  |                |              |  |

|                      | 1 = Timer2             | is ON                                          |                |                |                  |                |              |  |

|                      | 0 = Timer2             | is OFF                                         |                |                |                  |                |              |  |

| bit 1-0              | T2CKPS<1:              | <b>0&gt;:</b> Timer2 Cloc                      | k Prescale Se  | elect bits     |                  |                |              |  |

|                      | 11 = Prescaler is 64   |                                                |                |                |                  |                |              |  |

|                      | 10 = Presca            |                                                |                |                |                  |                |              |  |

|                      | 01 = Presca            |                                                |                |                |                  |                |              |  |

|                      | 00 = Presca            |                                                |                |                |                  |                |              |  |

### REGISTER 19-1: T2CON: TIMER2 CONTROL REGISTER

The I<sup>2</sup>C interface supports the following modes and features:

- · Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited Multi-master support

- 7-bit and 10-bit addressing

- · Start and Stop interrupts

- Interrupt masking

- Clock stretching

- · Bus collision detection

- · General call address matching

- Address masking

- · Address Hold and Data Hold modes

- Selectable SDA hold times

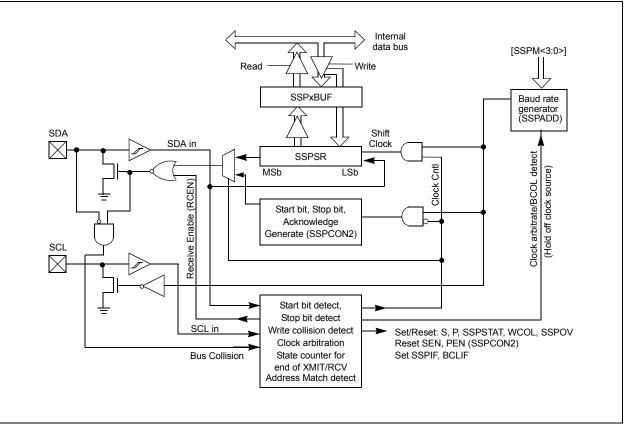

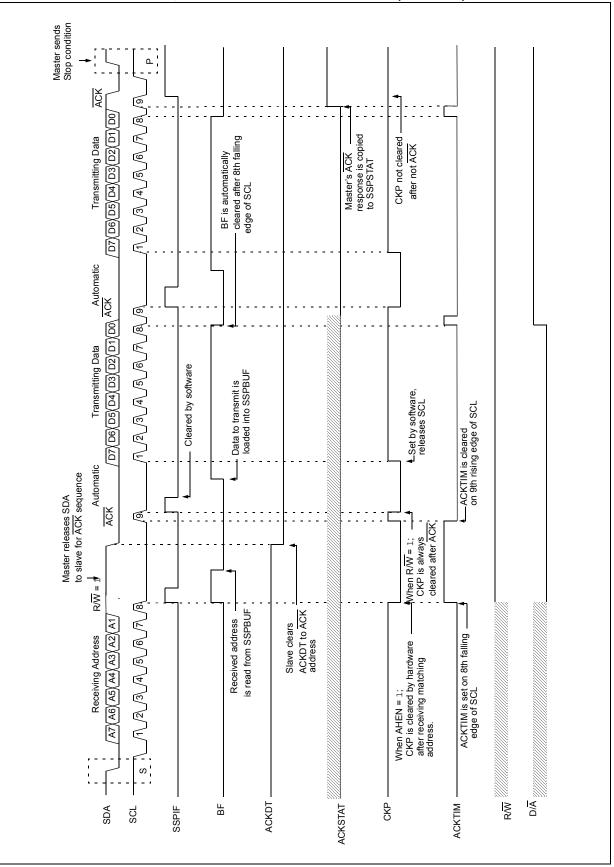

Figure 21-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 21-3 is a diagram of the  $I^2C$  interface module in Slave mode.

### FIGURE 21-2: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

# 24.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- Byte Oriented

- · Bit Oriented

- Literal and Control

The literal and control category contains the most varied instruction word format.

Table lists the instructions recognized by the MPASM<sup>™</sup> assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of four oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

### 24.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

| TABLE 24-1: | OPCODE FIELD |

|-------------|--------------|

|             | DESCRIPTIONS |

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |

| W     | Working register (accumulator)                                                                                                                                                  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |

| k     | Literal field, constant data or label                                                                                                                                           |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                   |

| n     | FSR or INDF number. (0-1)                                                                                                                                                       |

| mm    | Pre-post increment-decrement mode selection                                                                                                                                     |

#### TABLE 24-2: ABBREVIATION DESCRIPTIONS

| Field | Description     |

|-------|-----------------|

| PC    | Program Counter |

| TO    | Time-out bit    |

| С     | Carry bit       |

| DC    | Digit carry bit |

| Z     | Zero bit        |

| PD    | Power-down bit  |

# 25.2 Standard Operating Conditions

| The standard operating co | onditions for any device are defined as:     |        |

|---------------------------|----------------------------------------------|--------|

|                           | $VDDMIN \leq VDD \leq VDDMAX$                |        |

| Operating Temperature:    | — — —                                        |        |

| VDD — Operating Supply    | y Voltage <sup>(1)</sup>                     |        |

| PIC16LF1516/7/8/9         | 9                                            |        |

| Vddmin (F                 | Fosc ≤ 16 MHz)                               |        |

| VDDMIN (1                 | l6 MHz ≤Fosc ≤ 20 MHz)                       | +2.5V  |

| VDDMAX                    |                                              |        |

| PIC16F1516/7/8/9          |                                              |        |

| Vddmin (F                 | Fosc ≤ 16 MHz)                               |        |

| VDDMIN (1                 | l6 MHz ≤Fosc ≤ 20 MHz)                       |        |

| VDDMAX                    |                                              | +5.5V  |

| TA — Operating Ambien     | t Temperature Range                          |        |

| Industrial Temperat       | ture                                         |        |

| TA_MIN                    |                                              | 40°C   |

| Та_мах                    |                                              | +85°C  |

| Extended Tempera          | ture                                         |        |

| TA_MIN                    |                                              | 40°C   |

| Та_мах                    |                                              | +125°C |

| Note 1: See Paramete      | er D001, DC Characteristics: Supply Voltage. |        |

### 25.9 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| 2. Tpp5                               |                                       |     |                |  |  |

|---------------------------------------|---------------------------------------|-----|----------------|--|--|

| Т                                     |                                       |     |                |  |  |

| F                                     | Frequency                             | Т   | Time           |  |  |

| Lowerc                                | case letters (pp) and their meanings: |     |                |  |  |

| рр                                    |                                       |     |                |  |  |

| сс                                    | CCP1                                  | OSC | OSC1           |  |  |

| ck                                    | CLKOUT                                | rd  | RD             |  |  |

| cs                                    | CS                                    | rw  | RD or WR       |  |  |

| di                                    | SDIx                                  | SC  | SCKx           |  |  |

| do                                    | SDO                                   | SS  | SS             |  |  |

| dt                                    | Data in                               | tO  | ТОСКІ          |  |  |

| io                                    | I/O PORT                              | t1  | T1CKI          |  |  |

| mc                                    | MCLR                                  | wr  | WR             |  |  |

| Uppercase letters and their meanings: |                                       |     |                |  |  |

| S                                     |                                       |     |                |  |  |

| F                                     | Fall                                  | Р   | Period         |  |  |

| н                                     | High                                  | R   | Rise           |  |  |

| I                                     | Invalid (High-impedance)              | V   | Valid          |  |  |

| L                                     | Low                                   | Z   | High-impedance |  |  |

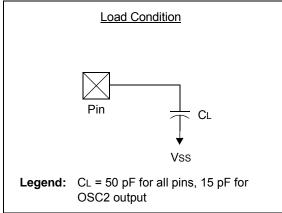

#### FIGURE 25-5: LOAD CONDITIONS

#### **TABLE 25-5**: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

Standard Operating Conditions (unless otherwise stated)

| Param<br>No. | Sym.                     |                                                                                        | Characterist                | ic             | Min.                                      | Тур†   | Max.   | Units | Conditions                         |

|--------------|--------------------------|----------------------------------------------------------------------------------------|-----------------------------|----------------|-------------------------------------------|--------|--------|-------|------------------------------------|

| 40*          | T⊤0H                     | T0CKI High Pulse Width                                                                 |                             | No Prescaler   | 0.5 Tcy + 20                              | —      | _      | ns    |                                    |

|              |                          |                                                                                        | With Presca                 |                | 10                                        |        | _      | ns    |                                    |

| 41* T⊤0L     | T0CKI Low Pulse Width No |                                                                                        | No Prescaler                | 0.5 Tcy + 20   |                                           | _      | ns     |       |                                    |

|              |                          | With Prescaler                                                                         |                             | 10             | —                                         |        | ns     |       |                                    |

| 42*          | Тт0Р                     | T0CKI Period                                                                           |                             |                | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —      | _      | ns    | N = prescale value<br>(2, 4,, 256) |

| 45* T⊤1H     | T⊤1H                     | T1CKI High<br>Time                                                                     | Synchronous,                | No Prescaler   | 0.5 Tcy + 20                              | —      | _      | ns    |                                    |

|              |                          |                                                                                        | Synchronous, with Prescaler |                | 15                                        | —      | _      | ns    |                                    |

|              |                          |                                                                                        | Asynchronous                |                | 30                                        |        | _      | ns    |                                    |

| 46* Tī       | T⊤1L                     | T1CKI Low<br>Time                                                                      | Synchronous,                | No Prescaler   | 0.5 Tcy + 20                              | —      |        | ns    |                                    |

|              |                          |                                                                                        | Synchronous,                | with Prescaler | 15                                        | —      |        | ns    |                                    |

|              |                          |                                                                                        | Asynchronous                |                | 30                                        | —      |        | ns    |                                    |

| 47* T⊤1      | TT1P                     | T1CKI Input<br>Period                                                                  | Synchronous                 |                | Greater of:<br>30 or <u>Tcy + 40</u><br>N | —      | _      | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |                          |                                                                                        | Asynchronous                |                | 60                                        |        | _      | ns    |                                    |

| 48           | FT1                      | Secondary Oscillator Input Frequency Range (oscillator enabled by setting bit T1OSCEN) |                             |                | 32.4                                      | 32.768 | 33.1   | kHz   |                                    |

| 49*          | TCKEZTMR1                | Delay from External Clock Edge to Timer<br>Increment                                   |                             |                | 2 Tosc                                    | —      | 7 Tosc | —     | Timers in Sync<br>mode             |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

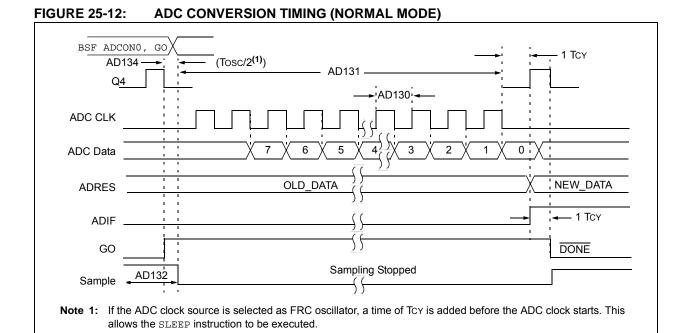

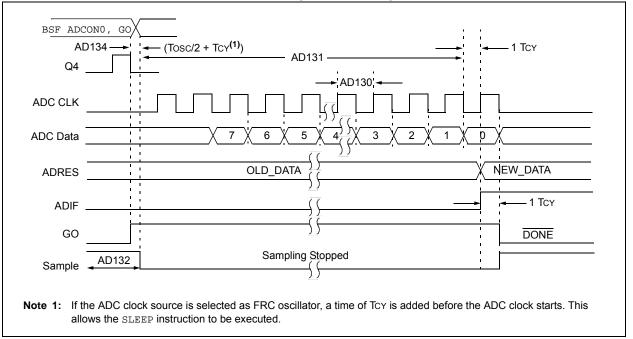

#### FIGURE 25-13: ADC CONVERSION TIMING (SLEEP MODE)

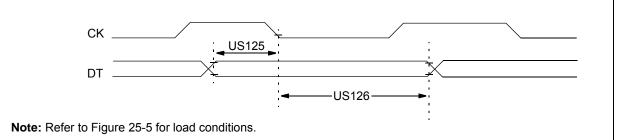

#### FIGURE 25-15: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

### TABLE 25-11: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                                 |    |      |       |            |  |

|----------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------|----|------|-------|------------|--|

| Param.<br>No.                                                                                                        | Symbol   | Symbol Characteristic                           |    | Max. | Units | Conditions |  |

| US125                                                                                                                | TDTV2CKL | SYNC RCV (Master and Slave)                     |    |      |       |            |  |

|                                                                                                                      |          | Data-hold before CK $\downarrow$ (DT hold time) | 10 |      | ns    |            |  |

| US126                                                                                                                | TCKL2DTL | Data-hold after CK $\downarrow$ (DT hold time)  | 15 |      | ns    |            |  |

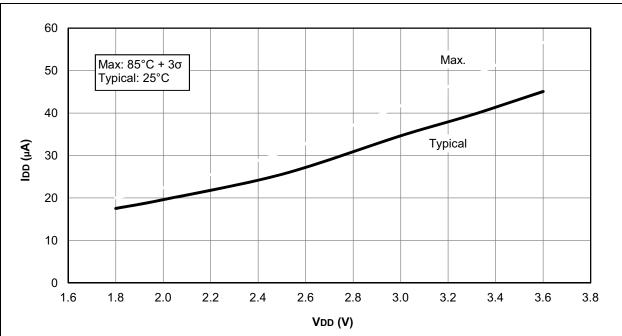

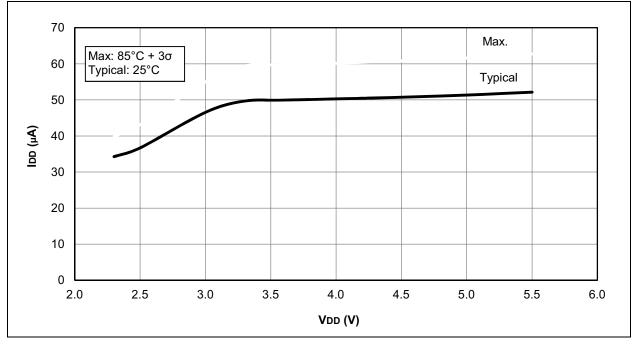

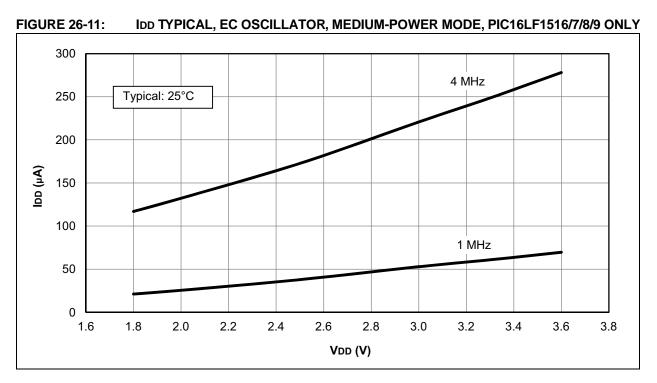

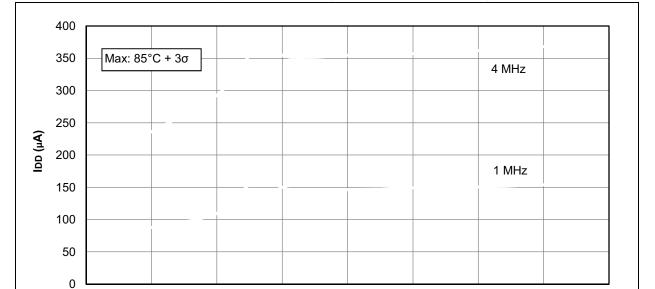

FIGURE 26-10: IDD, EC OSCILLATOR, LOW-POWER MODE, FOSC = 500 kHz, PIC16F1516/7/8/9 ONLY

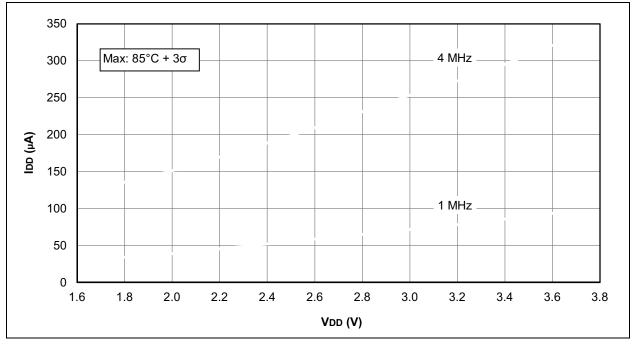

FIGURE 26-12: IDD MAXIMUM, EC OSCILLATOR, MEDIUM-POWER MODE, PIC16LF1516/7/8/9 ONLY

4.0

VDD (V)

4.5

5.0

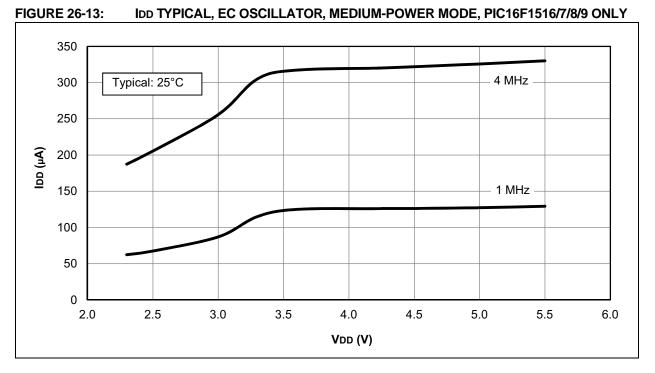

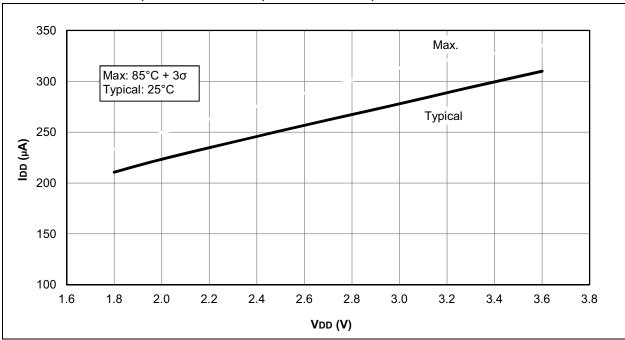

#### FIGURE 26-14: IDD MAXIMUM, EC OSCILLATOR, MEDIUM-POWER MODE, PIC16F1516/7/8/9 ONLY

2.0

2.5

3.0

3.5

5.5

6.0

4.0

VDD (V)

4.5

5.0

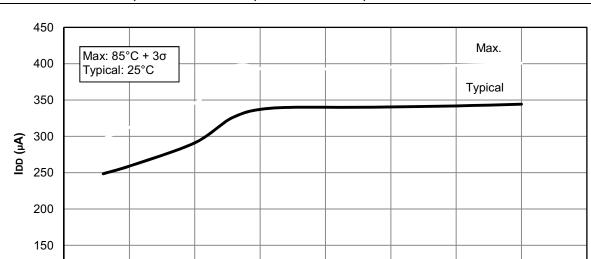

FIGURE 26-22: IDD, MFINTOSC MODE, FOSC = 500 kHz, PIC16F1516/7/8/9 ONLY

3.5

100 L 2.0

2.5

3.0

5.5

6.0