Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

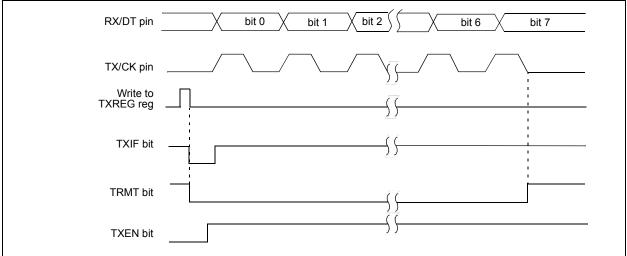

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 28x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1519t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 3-3:** PIC16(L)F1516/7 MEMORY MAP

|      | BANK 0                        |      | BANK 1                        |      | BANK 2                        |      | BANK 3                        |      | BANK 4                        |      | BANK 5                        |      | BANK 6                        |      | BANK 7                        |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| 000h |                               | 080h |                               | 100h |                               | 180h |                               | 200h |                               | 280h |                               | 300h |                               | 380h |                               |

|      | Core Registers<br>(Table 3-2) |

| 00Bh |                               | 08Bh |                               | 10Bh |                               | 18Bh |                               | 20Bh |                               | 28Bh |                               | 30Bh |                               | 38Bh |                               |

| 00Ch | PORTA                         | 08Ch | TRISA                         | 10Ch | LATA                          | 18Ch | ANSELA                        | 20Ch | _                             | 28Ch | _                             | 30Ch | _                             | 38Ch | _                             |

| 00Dh | PORTB                         | 08Dh | TRISB                         | 10Dh | LATB                          | 18Dh | ANSELB                        | 20Dh | WPUB                          | 28Dh | —                             | 30Dh | —                             | 38Dh | —                             |

| 00Eh | PORTC                         | 08Eh | TRISC                         | 10Eh | LATC                          | 18Eh | ANSELC                        | 20Eh | —                             | 28Eh | —                             | 30Eh | —                             | 38Eh | —                             |

| 00Fh | PORTD <sup>(1)</sup>          | 08Fh | TRISD <sup>(1)</sup>          | 10Fh | LATD <sup>(1)</sup>           | 18Fh | ANSELD <sup>(1)</sup>         | 20Fh | _                             | 28Fh | _                             | 30Fh | _                             | 38Fh | _                             |

| 010h | PORTE                         | 090h | TRISE                         | 110h | LATE <sup>(1)</sup>           | 190h | ANSELE <sup>(1)</sup>         | 210h | WPUE                          | 290h | _                             | 310h | _                             | 390h | _                             |

| 011h | PIR1                          | 091h | PIE1                          | 111h | _                             | 191h | PMADRL                        | 211h | SSPBUF                        | 291h | CCPR1L                        | 311h |                               | 391h | _                             |

| 012h | PIR2                          | 092h | PIE2                          | 112h | —                             | 192h | PMADRH                        | 212h | SSPADD                        | 292h | CCPR1H                        | 312h | —                             | 392h | —                             |

| 013h | —                             | 093h | —                             | 113h | _                             | 193h | PMDATL                        | 213h | SSPMSK                        | 293h | CCP1CON                       | 313h | —                             | 393h | —                             |

| 014h | —                             | 094h | _                             | 114h | _                             | 194h | PMDATH                        | 214h | SSPSTAT                       | 294h | —                             | 314h | —                             | 394h | IOCBP                         |

| 015h | TMR0                          | 095h | OPTION_REG                    | 115h | —                             | 195h | PMCON1                        | 215h | SSPCON1                       | 295h | —                             | 315h | —                             | 395h | IOCBN                         |

| 016h | TMR1L                         | 096h | PCON                          | 116h | BORCON                        | 196h | PMCON2                        | 216h | SSPCON2                       | 296h | —                             | 316h | _                             | 396h | IOCBF                         |

| 017h | TMR1H                         | 097h | WDTCON                        | 117h | FVRCON                        | 197h | VREGCON <sup>(2)</sup>        | 217h | SSPCON3                       | 297h | —                             | 317h | _                             | 397h | _                             |

| 018h | T1CON                         | 098h | _                             | 118h | —                             | 198h | _                             | 218h | _                             | 298h | CCPR2L                        | 318h | _                             | 398h | _                             |

| 019h | T1GCON                        | 099h | OSCCON                        | 119h |                               | 199h | RCREG                         | 219h | _                             | 299h | CCPR2H                        | 319h |                               | 399h | _                             |

| 01Ah | TMR2                          | 09Ah | OSCSTAT                       | 11Ah | —                             | 19Ah | TXREG                         | 21Ah | —                             | 29Ah | CCP2CON                       | 31Ah | —                             | 39Ah | —                             |

| 01Bh | PR2                           | 09Bh | ADRESL                        | 11Bh | —                             | 19Bh | SPBRG                         | 21Bh | —                             | 29Bh | —                             | 31Bh | —                             | 39Bh | _                             |

| 01Ch | T2CON                         | 09Ch | ADRESH                        | 11Ch | —                             | 19Ch | SPBRGH                        | 21Ch | _                             | 29Ch | —                             | 31Ch | _                             | 39Ch | _                             |

| 01Dh | _                             | 09Dh | ADCON0                        | 11Dh | APFCON                        | 19Dh | RCSTA                         | 21Dh | _                             | 29Dh | _                             | 31Dh | _                             | 39Dh | _                             |

| 01Eh |                               | 09Eh | ADCON1                        | 11Eh | _                             | 19Eh | TXSTA                         | 21Eh |                               | 29Eh | _                             | 31Eh |                               | 39Eh | _                             |

| 01Fh | —                             | 09Fh | —                             | 11Fh | —                             | 19Fh | BAUDCON                       | 21Fh |                               | 29Fh | —                             | 31Fh | —                             | 39Fh | _                             |

| 020h |                               | 0A0h |                               | 120h |                               | 1A0h |                               | 220h |                               | 2A0h |                               | 320h | General Purpose               | 3A0h |                               |

|      | General                       |      | Register                      |      |                               |

|      | Purpose                       | 32Fh | 16 Bytes                      |      | Unimplemented                 |

|      | Register<br>80 Bytes          | 330h | Unimplemented                 |      | Read as '0'                   |

|      | 00 Dytes                      |      | 00 Dytes                      |      | 00 Dytes                      |      | oo bytes                      |      | 00 Dyies                      |      | oo bytes                      |      | Read as '0'                   |      |                               |

| 06Fh |                               | 0EFh |                               | 16Fh |                               | 1EFh |                               | 26Fh |                               | 2EFh |                               | 36Fh |                               | 3EFh |                               |

| 070h |                               | 0F0h | Common RAM                    | 170h | Common RAM                    | 1F0h | Common RAM                    | 270h | Common RAM                    | 2F0h | Common RAM                    | 370h | Common RAM                    | 3F0h | Common RAM                    |

|      | Common RAM                    |      | (Accesses                     |

| 07Fh |                               | 0FFh | 70h – 7Fh)                    | 17Fh | 70h – 7Fh)                    | 1FFh | 70h – 7Fh)                    | 27Fh | 70h – 7Fh)                    | 2FFh | 70h – 7Fh)                    | 37Fh | 70h – 7Fh)                    | 3FFh | 70h – 7Fh)                    |

| U/Fn |                               | UFFN |                               | 17FN |                               | IFFN |                               | 27FN |                               | ZEEN |                               | SIFN |                               | SEEU |                               |

d: = Unimplemented data memory locations, read as '0'.

1: PIC16F/LF1516/7/8/9 only.

2: PIC16F1516/7 only. Legend: Note 1:

# 3.4.5 CORE FUNCTION REGISTERS SUMMARY

The Core Function registers listed in Table 3-7 can be addressed from any Bank.

| Addr            | Name   | Bit 7               | Bit 6                                                    | Bit 5         | Bit 4        | Bit 3        | Bit 2         | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on all other Resets |

|-----------------|--------|---------------------|----------------------------------------------------------|---------------|--------------|--------------|---------------|-----------|-----------|----------------------|---------------------------|

| Bank (          | 0-31   |                     |                                                          |               |              |              |               |           |           |                      |                           |

| x00h or<br>x80h | INDF0  |                     | this location<br>ical register)                          |               | nts of FSR0H | /FSR0L to ad | ddress data r | memory    |           | xxxx xxxx            | uuuu uuuu                 |

| x01h or<br>x81h | INDF1  |                     | this location<br>ical register)                          |               | nts of FSR1H | /FSR1L to ad | ddress data r | memory    |           | xxxx xxxx            | uuuu uuuu                 |

| x02h or<br>x82h | PCL    | Program Co          | ounter (PC) I                                            | Least Signifi | cant Byte    |              |               |           |           | 0000 0000            | 0000 0000                 |

| x03h or<br>x83h | STATUS |                     | _                                                        | _             | TO           | PD           | Z             | DC        | С         | 1 1000               | q quuu                    |

| x04h or<br>x84h | FSR0L  | Indirect Dat        | Indirect Data Memory Address 0 Low Pointer               |               |              |              |               |           |           | 0000 0000            | uuuu uuuu                 |

| x05h or<br>x85h | FSR0H  | Indirect Dat        | Indirect Data Memory Address 0 High Pointer              |               |              |              |               |           |           | 0000 0000            | 0000 0000                 |

| x06h or<br>x86h | FSR1L  | Indirect Dat        | ndirect Data Memory Address 1 Low Pointer                |               |              |              |               |           | 0000 0000 | uuuu uuuu            |                           |

| x07h or<br>x87h | FSR1H  | Indirect Dat        | Indirect Data Memory Address 1 High Pointer              |               |              |              |               |           | 0000 0000 | 0000 0000            |                           |

| x08h or<br>x88h | BSR    | -                   | -                                                        | -             | BSR4         | BSR3         | BSR2          | BSR1      | BSR0      | 0 0000               | 0 0000                    |

| x09h or<br>x89h | WREG   | EG Working Register |                                                          |               |              |              |               | 0000 0000 | uuuu uuuu |                      |                           |

| x0Ahor<br>x8Ah  | PCLATH | —                   | Write Buffer for the upper 7 bits of the Program Counter |               |              |              |               |           | -000 0000 | -000 0000            |                           |

| x0Bhor<br>x8Bh  | INTCON | GIE                 | PEIE                                                     | TMR0IE        | INTE         | IOCIE        | TMR0IF        | INTF      | IOCIF     | 0000 0000            | 0000 0000                 |

TABLE 3-7: CORE FUNCTION REGISTERS SUMMARY

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

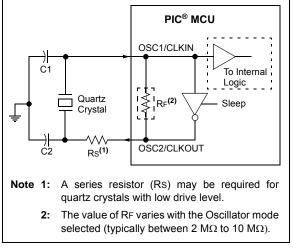

# FIGURE 5-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices (DS00826)

- AN849, Basic PIC<sup>®</sup> Oscillator Design (DS00849)

- AN943, Practical PIC<sup>®</sup> Oscillator Analysis and Design (DS00943)

- AN949, Making Your Oscillator Work (DS00949)

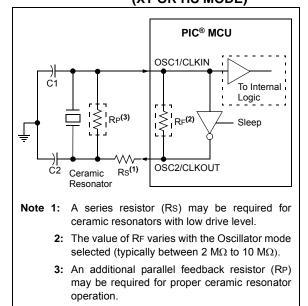

# FIGURE 5-4:

#### CERAMIC RESONATOR OPERATION (XT OR HS MODE)

# 5.2.1.3 Oscillator Start-up Timer (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended, unless either FSCM or Two-Speed Start-up are enabled. In this case, code will continue to execute at the selected INTOSC frequency while the OST is counting. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-Up mode can be selected (see **Section 5.4 "Two-Speed Clock Start-up Mode"**).

## 5.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to the internal oscillator during run time. See **Section 5.3 "Clock Switching**"for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators that provides the internal system clock source.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz.

- 2. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

## 5.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 16 MHz internal clock source.

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). The frequency derived from the HFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.4 "Internal Oscillator Clock Switch Timing"** for more information.

The HFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'.

A fast start-up oscillator allows internal circuits to power-up and stabilize before switching to HFINTOSC.

The High-Frequency Internal Oscillator Ready bit (HFIOFR) of the OSCSTAT register indicates when the HFINTOSC is running.

The High-Frequency Internal Oscillator Stable bit (HFIOFS) of the OSCSTAT register indicates when the HFINTOSC is running within 0.5% of its final value.

# 5.2.2.2 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a multiplexer (see Figure 5-1). Select 31 kHz, via software, using the IRCF<3:0> bits of the OSCCON register. See Section 5.2.2.4 "Internal Oscillator Clock Switch Timing" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<3:0> bits of the OSCCON register = 000) as the system clock source (SCS bits of the OSCCON register = 1x), or when any of the following are enabled:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired LF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to  $`\mathtt{lx}'$

Peripherals that use the LFINTOSC are:

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

The Low-Frequency Internal Oscillator Ready bit (LFIOFR) of the OSCSTAT register indicates when the LFINTOSC is running.

#### 10.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See **Section 25.0 "Electrical Specifications"** for the LFINTOSC tolerances.

#### **10.2 WDT Operating Modes**

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table .

#### 10.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always ON.

WDT protection is active during Sleep.

#### 10.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is ON, except in Sleep.

WDT protection is not active during Sleep.

#### 10.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table for more details.

| WDTE<1:0> | SWDTE<br>N | Device<br>Mode | WDT<br>Mode |

|-----------|------------|----------------|-------------|

| 11        | Х          | Х              | Active      |

| 10        | x          | Awake          | Active      |

| TO        | A          | Sleep          | Disabled    |

| 01        | 1 X        |                | Active      |

| 0         |            | Disabled       |             |

| 00        | Х          | Х              | Disabled    |

#### 10.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

#### 10.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- Oscillator fail

- WDT is disabled

- Oscillator Start-up Timer (OST) is running

See Table 10-2 for more information.

#### 10.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See **Section 5.0** "Oscillator **Module (with Fail-Safe Clock Monitor)**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. The RWDT bit in the PCON register can also be used. See **Section 3.0** "**Memory Organization**" and The STATUS register (Register 3-1) for more information.

#### TABLE 10-2: WDT CLEARING CONDITIONS

| Conditions                                              | WDT                          |  |

|---------------------------------------------------------|------------------------------|--|

| WDTE<1:0> = 00                                          |                              |  |

| WDTE<1:0> = 01 and SWDTEN = 0                           |                              |  |

| WDTE<1:0> = 10 and enter Sleep                          | Cleared                      |  |

| CLRWDT Command                                          | Cleared                      |  |

| Oscillator Fail Detected                                |                              |  |

| Exit Sleep + System Clock = SOSC, EXTRC, INTOSC, EXTCLK |                              |  |

| Exit Sleep + System Clock = XT, HS, LP                  | Cleared until the end of OST |  |

| Change INTOSC divider (IRCF bits)                       | Unaffected                   |  |

© 2010-2016 Microchip Technology Inc.

| U-1          | R/W-0/0            | R/W-0/0                                                                                                                                                                                           | R/W/HC-0/0                                                                                                                | R/W/HC-x/q <sup>(2)</sup> | R/W-0/0            | R/S/HC-0/0           | R/S/HC-0/0     |  |  |  |

|--------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------|----------------------|----------------|--|--|--|

| _(1)         | CFGS               | LWLO                                                                                                                                                                                              | FREE                                                                                                                      | WRERR                     | WREN               | WR                   | RD             |  |  |  |

| bit 7        |                    |                                                                                                                                                                                                   |                                                                                                                           |                           |                    | -<br>-               | bit            |  |  |  |

| Legend:      |                    |                                                                                                                                                                                                   |                                                                                                                           |                           |                    |                      |                |  |  |  |

| R = Reada    | able bit           | W = Writable b                                                                                                                                                                                    | it                                                                                                                        | U = Unimpleme             | ented bit, read as | s 'O'                |                |  |  |  |

| S = Bit car  | n only be set      | x = Bit is unkno                                                                                                                                                                                  | own                                                                                                                       |                           | -                  | Value at all other f | Resets         |  |  |  |

| '1' = Bit is | <b>,</b>           | '0' = Bit is clea                                                                                                                                                                                 | red                                                                                                                       | HC = Bit is clea          | ared by hardware   | 9                    |                |  |  |  |

|              |                    |                                                                                                                                                                                                   |                                                                                                                           |                           |                    |                      |                |  |  |  |

| bit 7        | -                  | ted: Read as '1'                                                                                                                                                                                  |                                                                                                                           |                           |                    |                      |                |  |  |  |

| bit 6        |                    | Juration Select bit                                                                                                                                                                               |                                                                                                                           |                           |                    |                      |                |  |  |  |

|              |                    | Configuration, Use<br>Flash program me                                                                                                                                                            |                                                                                                                           | ID Registers              |                    |                      |                |  |  |  |

| bit 5        |                    | Write Latches On                                                                                                                                                                                  |                                                                                                                           |                           |                    |                      |                |  |  |  |

| bit o        |                    |                                                                                                                                                                                                   | ,                                                                                                                         | e latch is loaded         | updated on the     | next WR comman       | d              |  |  |  |

|              |                    |                                                                                                                                                                                                   |                                                                                                                           |                           |                    | all program mem      |                |  |  |  |

|              | will be in         | itiated on the nex                                                                                                                                                                                | t WR command                                                                                                              |                           |                    |                      |                |  |  |  |

| bit 4        | 0                  | m Flash Erase E                                                                                                                                                                                   |                                                                                                                           |                           |                    |                      |                |  |  |  |

|              |                    |                                                                                                                                                                                                   | In erase operation on the next WR command (hardware cleared upon completion)<br>In write operation on the next WR command |                           |                    |                      |                |  |  |  |

| bit 3        |                    | gram/Erase Error                                                                                                                                                                                  |                                                                                                                           | IX command                |                    |                      |                |  |  |  |

| DIL O        |                    | -                                                                                                                                                                                                 | -                                                                                                                         | or erase sequer           | ice attempt or te  | rmination (bit is s  | et automatical |  |  |  |

|              |                    | et attempt (write '                                                                                                                                                                               |                                                                                                                           |                           |                    |                      |                |  |  |  |

|              | 0 = The prog       | ram or erase ope                                                                                                                                                                                  | ration complete                                                                                                           | d normally.               |                    |                      |                |  |  |  |

| bit 2        | WREN: Progr        | am/Erase Enable                                                                                                                                                                                   | bit                                                                                                                       |                           |                    |                      |                |  |  |  |

|              |                    | rogram/erase cyc                                                                                                                                                                                  |                                                                                                                           | -1                        |                    |                      |                |  |  |  |

| L !! A       |                    | orogramming/eras                                                                                                                                                                                  | ing of program F                                                                                                          | lash                      |                    |                      |                |  |  |  |

| bit 1        | WR: Write Co       | ntrol bit<br>a program Flash p                                                                                                                                                                    | rogram/oraso o                                                                                                            | noration                  |                    |                      |                |  |  |  |

|              |                    | ation is self-timed                                                                                                                                                                               |                                                                                                                           |                           | are once operati   | on is complete.      |                |  |  |  |

|              | •                  | bit can only be se                                                                                                                                                                                |                                                                                                                           | •                         | •                  | ·                    |                |  |  |  |

|              | 0 = Program        | /erase operation f                                                                                                                                                                                | to the Flash is co                                                                                                        | omplete and inac          | ctive.             |                      |                |  |  |  |

| bit 0        | RD: Read Cor       | ntrol bit                                                                                                                                                                                         |                                                                                                                           |                           |                    |                      |                |  |  |  |

|              |                    |                                                                                                                                                                                                   | ead. Read takes                                                                                                           | s one cycle. RD i         | is cleared in hard | ware. The RD bit     | can only be se |  |  |  |

|              | •                  | red) in software.<br>t initiate a prograr                                                                                                                                                         | n Flash read                                                                                                              |                           |                    |                      |                |  |  |  |

| Note 1:      | Unimplemented bit, |                                                                                                                                                                                                   |                                                                                                                           |                           |                    |                      |                |  |  |  |

| 2:           | · · · · · ·        |                                                                                                                                                                                                   | v hardware whe                                                                                                            | en a program me           | mory write or era  | se operation is st   | arted (WR = 1) |  |  |  |

| 3:           |                    | The WRERR bit is automatically set by hardware when a program memory write or erase operation is started (WR = 1).<br>The LWLO bit is ignored during a program memory erase operation (FREE = 1). |                                                                                                                           |                           |                    |                      |                |  |  |  |

#### REGISTER 11-6: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

3: The LWLO bit is ignored during a program memory erase operation (FREE = 1).

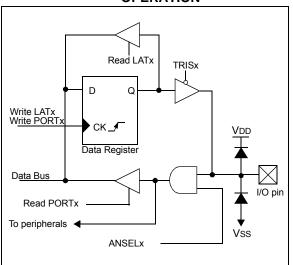

# 12.0 I/O PORTS

Each port has three standard registers for its operation. These registers are:

- TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- ANSELx (analog select)

- WPUx (weak pull-up)

In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

## TABLE 12-1: PORT AVAILABILITY PER DEVICE

| Device          | PORTA | РОКТВ | PORTC | PORTD | PORTE |

|-----------------|-------|-------|-------|-------|-------|

| PIC16(L)F1516/8 | •     | •     | ٠     |       | •     |

| PIC16(L)F1517/9 | •     | •     | •     | •     | •     |

The Data Latch (LATx register) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 12-1.

#### FIGURE 12-1: GENERIC I/O PORT OPERATION

#### 12.2 **PORTA Registers**

#### 12.2.1 DATA REGISTER

PORTA is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 12-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTA register (Register 12-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

#### 12.2.2 DIRECTION CONTROL

The TRISA register (Register 12-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 12.2.3 ANALOG CONTROL

The ANSELA register (Register 12-5) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

The ANSELA bits default to the Analog Note: mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

#### EXAMPLE 12-1: **INITIALIZING PORTA**

| ; | This code example illustrates         |

|---|---------------------------------------|

| ; | initializing the PORTA register. The  |

| ; | other ports are initialized in the sa |

| ; | manner.                               |

same

| BANKSEL | PORTA       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

| BANKSEL | LATA        | ;Data Latch            |

| CLRF    | LATA        | ;                      |

| BANKSEL | ANSELA      | ;                      |

| CLRF    | ANSELA      | ;digital I/O           |

| BANKSEL | TRISA       | ;                      |

| MOVLW   | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF   | TRISA       | ;and set RA<2:0> as    |

|         |             | ;outputs               |

#### 12.2.4 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-2.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown in the priority list.

| TABLE 12-2: | PORTA OUTPUT PRIORITY |

|-------------|-----------------------|

|-------------|-----------------------|

| Pin Name | Function Priority <sup>(1)</sup>    |

|----------|-------------------------------------|

| RA0      | RA0                                 |

| RA1      | RA1                                 |

| RA2      | RA2                                 |

| RA3      | RA3                                 |

| RA4      | RA4                                 |

| RA5      | VCAP (PIC16F1516/7/8/9 only)<br>RA5 |

| RA6      | CLKOUT<br>OSC2<br>RA6               |

| RA7      | RA7                                 |

**Note 1:** Priority listed from highest to lowest.

| Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0   | Register<br>on Page |

|------------|--------|--------|--------|--------|--------|---------|--------|---------|---------------------|

| ANSELA     | —      | —      | ANSA5  | —      | ANSA3  | ANSA2   | ANSA1  | ANSA0   | 108                 |

| APFCON     | _      | _      | _      | _      | _      | —       | SSSEL  | CCP2SEL | 105                 |

| LATA       | LATA7  | LATA6  | LATA5  | LATA4  | LATA3  | LATA2   | LATA1  | LATA0   | 108                 |

| OPTION_REG | WPUEN  | INTEDG | TMR0CS | TMR0SE | PSA    | PS<2:0> |        | 146     |                     |

| PORTA      | RA7    | RA6    | RA5    | RA4    | RA3    | RA2     | RA1    | RA0     | 107                 |

| TRISA      | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2  | TRISA1 | TRISA0  | 107                 |

#### TABLE 12-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

#### TABLE 12-4: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2    | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|-------------|-----------|---------|---------------------|

| CONFIG1 | 13:8 |         |         | FCMEN    | IESO     | CLKOUTEN | BOREN<1:0.> |           | —       | 40                  |

| CONFIGT | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | E<1:0>   |             | FOSC<2:0> |         | 42                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

## 18.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 18-1 displays the Timer1 enable selections.

| TABLE 18-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

## 18.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 18-2 displays the clock source selections.

#### 18.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous source may be used:

Asynchronous event on the T1G pin to Timer1 gate

#### 18.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI. This external clock source can be synchronized to the microcontroller system clock and run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the secondary oscillator circuit.

- **Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- Timer1 enabled after POR

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON =0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

| TABLE 18-2: CLOCK SOURCE SELECTIO | NS |

|-----------------------------------|----|

|-----------------------------------|----|

| TMR1CS1 | TMR1CS0 | T10SCEN | Clock Source                                     |

|---------|---------|---------|--------------------------------------------------|

| 1       | 1       | x       | LFINTOSC                                         |

| 1       | 0       | 1       | Secondary Oscillator Circuit on SOSCI/SOSCO Pins |

| 1       | 0       | 0       | External Clocking on T1CKI Pin                   |

| 0       | 1       | x       | System Clock (FOSC)                              |

| 0       | 0       | x       | Instruction Clock (Fosc/4)                       |

# 20.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral which allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

This family of devices contains two standard Capture/ Compare/PWM modules (CCP1 and CCP2).

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to CCPx module. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

#### TABLE 20-1: PWM RESOURCES

| Device Name         | CCP1         | CCP2         |  |

|---------------------|--------------|--------------|--|

| PIC16(L)F1516/7/8/9 | Standard PWM | Standard PWM |  |

## 20.1 Capture Mode

The Capture mode function described in this section is available and identical for CCP modules CCP1 and CCP2.

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the CCPx pin, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMR1H:TMR1L register pair, respectively. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- · Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

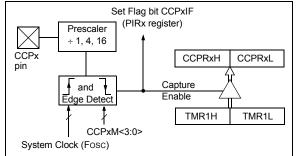

Figure 20-1 shows a simplified diagram of the Capture operation.

#### 20.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Also, the CCP2 pin function can be moved to alternative pins using the APFCON register. Refer to Register 12-1 for more details.

#### FIGURE 20-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

## 20.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 18.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

## 20.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

**Note:** If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

Equation 20-2 is used to calculate the PWM pulse width.

Equation 20-3 is used to calculate the PWM duty cycle ratio.

## EQUATION 20-2: PULSE WIDTH

$Pulse Width = (CCPRxL:CCPxCON < 5:4>) \bullet$

TOSC • (TMR2 Prescale Value)

# EQUATION 20-3: DUTY CYCLE RATIO

$$Duty Cycle Ratio = \frac{(CCPRxL:CCPxCON < 5:4>)}{4(PR2 + 1)}$$

The CCPRxH register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (Fosc), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH and 2-bit latch, then the CCPx pin is cleared (see Figure 20-4).

## 20.3.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 20-4.

# EQUATION 20-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2+1)]}{\log(2)}$$

bits

Note: If the pulse-width value is greater than the period the assigned PWM pin(s) will remain unchanged.

# TABLE 20-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

## TABLE 20-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

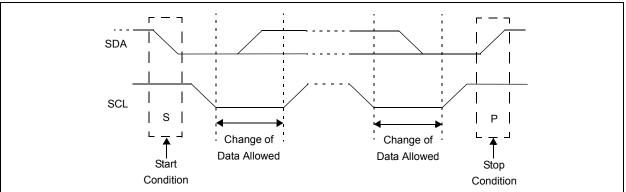

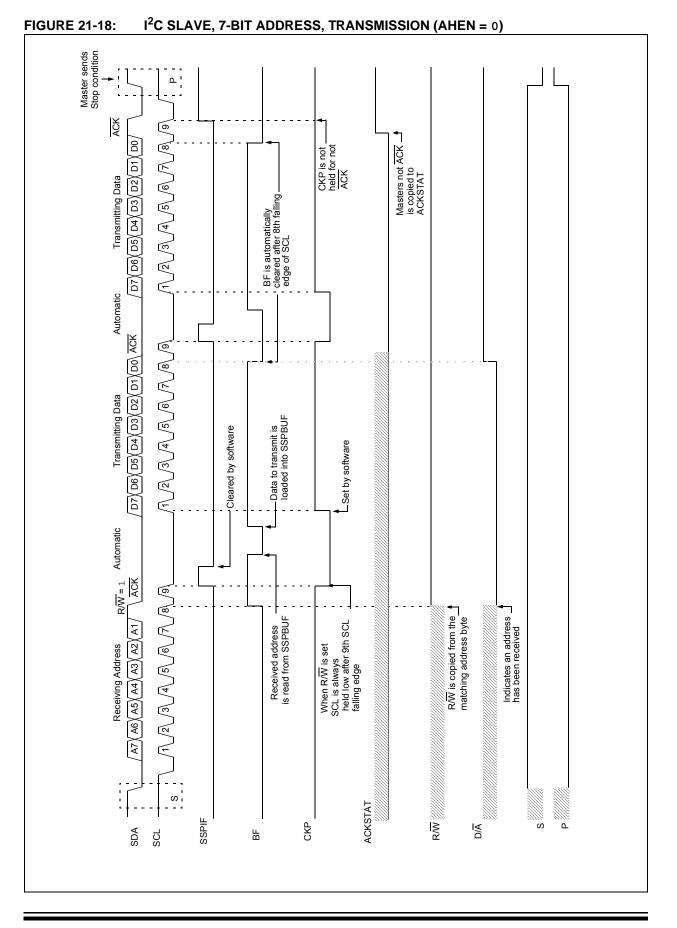

# FIGURE 21-12: I<sup>2</sup>C START AND STOP CONDITIONS

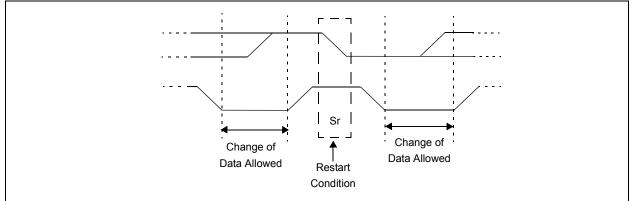

# FIGURE 21-13: I<sup>2</sup>C RESTART CONDITION

# 21.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicated to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{\text{ACK}}$  is placed in the ACKSTAT bit of the SSPCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the  $\overline{ACK}$  value sent back to the transmitter. The ACKDT bit of the SSPCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPCON3 register are clear.

There are certain conditions where an  $\overline{ACK}$  will not be sent by the slave. If the BF bit of the SSPSTAT register or the SSPOV bit of the SSPCON1 register are set when a byte is received. When the module is addressed, after the 8th falling edge of SCL on the bus, the ACKTIM bit of the SSPCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

#### 21.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 10-bit Addressing mode.

Figure 21-20 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish  $I^2C$  communication.

- 1. Bus starts Idle.

- 2. Master sends Start condition; S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- 3. Master sends matching high address with  $R/\overline{W}$  bit clear; UA bit of the SSPSTAT register is set.

- 4. Slave sends ACK and SSPIF is set.

- 5. Software clears the SSPIF bit.

- 6. Software reads received address from SSPBUF clearing the BF flag.

- 7. Slave loads low address into SSPADD, releasing SCL.

- 8. Master sends matching low address byte to the slave; UA bit is set.

**Note:** Updates to the SSPADD register are not allowed until after the ACK sequence.

9. Slave sends ACK and SSPIF is set.

**Note:** If the low address does not match, SSPIF and UA are still set so that the slave software can set SSPADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSPIF.

- 11. Slave reads the received matching address from SSPBUF clearing BF.

- 12. Slave loads high address into SSPADD.

- 13. Master clocks a data byte to the slave and clocks out the slaves ACK on the 9th SCL pulse; SSPIF is set.

- 14. If SEN bit of SSPCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSPIF.

- 16. Slave reads the received byte from SSPBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCL.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

## 21.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCL line is held low are the same. Figure 21-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 21-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

| R-0/0                   | R/W-0/0                        | R/W-0/0                               | R/W-0/0                       | R/W-0/0                     | R/W-0/0                       | R/W-0/0           | R/W-0/0         |

|-------------------------|--------------------------------|---------------------------------------|-------------------------------|-----------------------------|-------------------------------|-------------------|-----------------|

| ACKTIM                  | PCIE                           | SCIE                                  | BOEN                          | SDAHT                       | SBCDE                         | AHEN              | DHEN            |

| bit 7                   | •                              | •                                     | •                             | •                           | •                             |                   | bit (           |

| Logondi                 |                                |                                       |                               |                             |                               |                   |                 |

| Legend:<br>R = Readable | , bit                          | W = Writable                          | hit                           | II – Unimploi               | mented bit, read              | 1 22 (0)          |                 |

| u = Bit is uncl         |                                | x = Bit is unk                        |                               | -                           | at POR and BO                 |                   | ther Resets     |

| '1' = Bit is set        | 0                              | '0' = Bit is cle                      |                               |                             |                               |                   |                 |

|                         |                                |                                       | arcu                          |                             |                               |                   |                 |

| bit 7                   | ACKTIM: Ac                     | knowledge Tim                         | ne Status bit (l <sup>2</sup> | C mode only)                | (3)                           |                   |                 |

|                         |                                | -                                     |                               | • •                         | e, set on 8 <sup>⊺H</sup> fal | ling edge of SC   | CL clock        |

|                         |                                |                                       |                               |                             | g edge of SCL c               |                   |                 |

| bit 6                   | PCIE: Stop C                   | Condition Interre                     | upt Enable bit (              | (I <sup>2</sup> C mode only | ()                            |                   |                 |

|                         |                                | nterrupt on dete                      |                               |                             |                               |                   |                 |

|                         |                                | ection interrupt                      |                               |                             |                               |                   |                 |

| bit 5                   |                                | Condition Interr                      | •                             | · ·                         | , ,                           |                   |                 |

|                         |                                | nterrupt on dete<br>ection interrupt  |                               |                             | ditions                       |                   |                 |

| bit 4                   |                                | ection interrupt                      |                               | -                           |                               |                   |                 |

|                         | In SPI Slave                   |                                       |                               |                             |                               |                   |                 |

|                         |                                |                                       | every time that               | a new data by               | te is shifted in i            | gnoring the BF    | bit             |

|                         |                                |                                       |                               |                             | STAT register a               | Iready set, SSI   | POV bit of the  |

|                         |                                | CON1 register<br>r mode and SP        |                               |                             | pdated                        |                   |                 |

|                         |                                | is ignored.                           | Tiviaster moue                | <u>.</u>                    |                               |                   |                 |

|                         | <u>In I<sup>2</sup>C Slave</u> | mode:                                 |                               |                             |                               |                   |                 |

|                         |                                |                                       |                               |                             | eceived addres                | s/data byte, ign  | oring the state |

|                         |                                | e SSPOV bit o<br>BUF is only up       |                               |                             |                               |                   |                 |

| bit 3                   |                                | A Hold Time Se                        |                               |                             |                               |                   |                 |

| bit 0                   |                                | n of 300 ns hold                      |                               |                             | a edge of SCI                 |                   |                 |

|                         |                                | n of 100 ns hold                      |                               |                             |                               |                   |                 |

| bit 2                   | SBCDE: Sla                     | ve Mode Bus C                         | Collision Detect              | Enable bit (I <sup>2</sup>  | C Slave mode o                | only)             |                 |

|                         | If on the risin                | g edge of SCL,                        | SDA is sample                 | d low when the              | e module is outp              | outting a high st | ate, the BCLI   |

|                         | bit of the PIR                 | R2 register is se                     | t, and bus goe                | s idle                      |                               |                   |                 |

|                         |                                | lave bus collisi                      |                               |                             |                               |                   |                 |

|                         |                                | is collision inter                    | -                             |                             |                               |                   |                 |

| bit 1                   |                                | ess Hold Enabl                        | •                             | • •                         |                               |                   |                 |

|                         |                                |                                       |                               |                             | received addre                | ss byte; CKP b    | oit of the SSP  |

|                         |                                | egister will be c<br>holding is disal |                               | SCL will be h               | eid iow.                      |                   |                 |

| bit 0                   |                                | Hold Enable b                         |                               | ode only)                   |                               |                   |                 |

|                         |                                |                                       | -                             | • •                         | data byte; slave              | hardware clea     | irs the CKP b   |

|                         | of the S                       | SPCON1 regist                         | ter and SCL is                |                             | ,, <u>.</u>                   |                   |                 |

|                         | 0 = Data hole                  | ding is disabled                      | l                             |                             |                               |                   |                 |

| Note 1: Fo              | r daisy-chained                | I SPI operation;                      | allows the use                | er to ignore all            | but the last rece             | vived byte. SSP   | OV is still set |

|                         |                                |                                       |                               |                             | ues to write the              |                   |                 |

| о т.                    | in hit has see all             | fact in Clave me                      | adaa that Ctart               | and Chan age                | ditions data ations           |                   |                 |

#### REGISTER 21-6: SSPCON3: SSP CONTROL REGISTER 3

2: This bit has no effect in Slave modes that Start and Stop condition detection is explicitly listed as enabled.

**3:** The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is set.

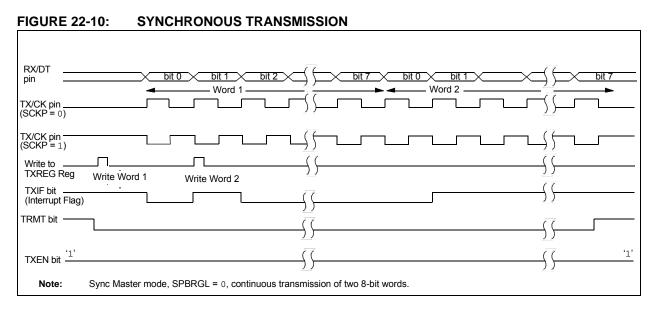

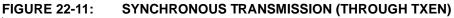

# TABLE 22-5:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>TRANSMISSION

| Name    | Bit 7                         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                        | RCIDL  | —      | SCKP   | BRG16  | —      | WUE    | ABDEN  | 232                 |

| INTCON  | GIE                           | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 74                  |

| PIE1    | TMR1GIE                       | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 75                  |

| PIR1    | TMR1GIF                       | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 77                  |

| RCSTA   | SPEN                          | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 231                 |

| SPBRGL  |                               |        |        | BRG    | <7:0>  |        |        |        | 233*                |

| SPBRGH  |                               |        |        | BRG<   | :15:8> |        |        |        | 233*                |

| TRISC   | TRISC7                        | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 114                 |

| TXREG   | EUSART Transmit Data Register |        |        |        |        |        |        |        | 222*                |

| TXSTA   | CSRC                          | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 230                 |

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

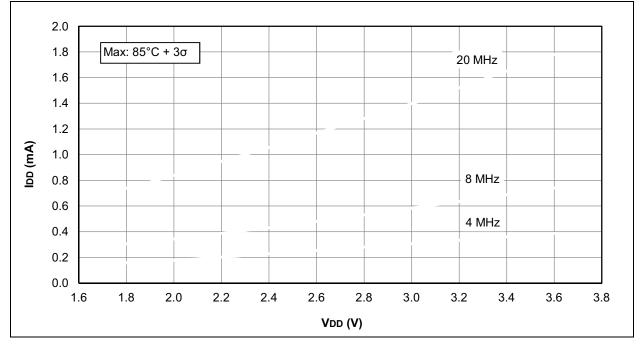

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |      |      |

|--------------------------|-------------|----------|------|------|

| Dimension                | MIN         | NOM      | MAX  |      |

| Contact Pitch            | E           | 0.65 BSC |      |      |

| Contact Pad Spacing      | С           |          | 7.20 |      |

| Contact Pad Width (X28)  | X1          |          |      | 0.45 |

| Contact Pad Length (X28) | Y1          |          |      | 1.75 |

| Distance Between Pads    | G           | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

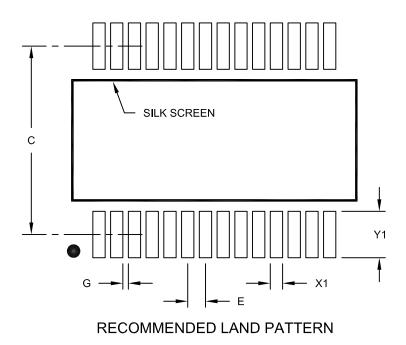

## 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | MILLIMETERS |      |      |

|-------------------------|--------|-------------|------|------|

| Dimensior               | Limits | MIN         | NOM  | MAX  |

| Number of Pins          | N      | 28          |      |      |

| Pitch                   | е      | 0.65 BSC    |      |      |

| Overall Height          | A      | 0.80        | 0.90 | 1.00 |

| Standoff                | A1     | 0.00        | 0.02 | 0.05 |

| Terminal Thickness      | A3     | 0.20 REF    |      |      |

| Overall Width           | E      | 6.00 BSC    |      |      |

| Exposed Pad Width       | E2     | 3.65        | 3.70 | 4.20 |

| Overall Length          | D      | 6.00 BSC    |      |      |

| Exposed Pad Length      | D2     | 3.65        | 3.70 | 4.20 |

| Terminal Width          | b      | 0.23        | 0.30 | 0.35 |

| Terminal Length         | L      | 0.50        | 0.55 | 0.70 |

| Terminal-to-Exposed Pad | K      | 0.20        | -    | -    |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M.