Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 28x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1519t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 3-3:** PIC16(L)F1516/7 MEMORY MAP

|      | BANK 0                        |      | BANK 1                        |      | BANK 2                        |      | BANK 3                        |      | BANK 4                        |      | BANK 5                        |      | BANK 6                        |      | BANK 7                        |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| 000h |                               | 080h |                               | 100h |                               | 180h |                               | 200h |                               | 280h |                               | 300h |                               | 380h |                               |

|      | Core Registers<br>(Table 3-2) |

| 00Bh |                               | 08Bh |                               | 10Bh |                               | 18Bh |                               | 20Bh |                               | 28Bh |                               | 30Bh |                               | 38Bh |                               |

| 00Ch | PORTA                         | 08Ch | TRISA                         | 10Ch | LATA                          | 18Ch | ANSELA                        | 20Ch | _                             | 28Ch | _                             | 30Ch | _                             | 38Ch | _                             |

| 00Dh | PORTB                         | 08Dh | TRISB                         | 10Dh | LATB                          | 18Dh | ANSELB                        | 20Dh | WPUB                          | 28Dh | —                             | 30Dh | —                             | 38Dh | —                             |

| 00Eh | PORTC                         | 08Eh | TRISC                         | 10Eh | LATC                          | 18Eh | ANSELC                        | 20Eh | —                             | 28Eh | —                             | 30Eh | —                             | 38Eh | —                             |

| 00Fh | PORTD <sup>(1)</sup>          | 08Fh | TRISD <sup>(1)</sup>          | 10Fh | LATD <sup>(1)</sup>           | 18Fh | ANSELD <sup>(1)</sup>         | 20Fh | _                             | 28Fh | _                             | 30Fh | _                             | 38Fh | _                             |

| 010h | PORTE                         | 090h | TRISE                         | 110h | LATE <sup>(1)</sup>           | 190h | ANSELE <sup>(1)</sup>         | 210h | WPUE                          | 290h | _                             | 310h | _                             | 390h | _                             |

| 011h | PIR1                          | 091h | PIE1                          | 111h | _                             | 191h | PMADRL                        | 211h | SSPBUF                        | 291h | CCPR1L                        | 311h |                               | 391h | _                             |

| 012h | PIR2                          | 092h | PIE2                          | 112h | —                             | 192h | PMADRH                        | 212h | SSPADD                        | 292h | CCPR1H                        | 312h | —                             | 392h | —                             |

| 013h | —                             | 093h | —                             | 113h | _                             | 193h | PMDATL                        | 213h | SSPMSK                        | 293h | CCP1CON                       | 313h | —                             | 393h | —                             |

| 014h | —                             | 094h | _                             | 114h | _                             | 194h | PMDATH                        | 214h | SSPSTAT                       | 294h | —                             | 314h | —                             | 394h | IOCBP                         |

| 015h | TMR0                          | 095h | OPTION_REG                    | 115h | —                             | 195h | PMCON1                        | 215h | SSPCON1                       | 295h | —                             | 315h | —                             | 395h | IOCBN                         |

| 016h | TMR1L                         | 096h | PCON                          | 116h | BORCON                        | 196h | PMCON2                        | 216h | SSPCON2                       | 296h | —                             | 316h | _                             | 396h | IOCBF                         |

| 017h | TMR1H                         | 097h | WDTCON                        | 117h | FVRCON                        | 197h | VREGCON <sup>(2)</sup>        | 217h | SSPCON3                       | 297h | —                             | 317h | _                             | 397h | _                             |

| 018h | T1CON                         | 098h | _                             | 118h | —                             | 198h | _                             | 218h | _                             | 298h | CCPR2L                        | 318h | _                             | 398h | _                             |

| 019h | T1GCON                        | 099h | OSCCON                        | 119h |                               | 199h | RCREG                         | 219h | _                             | 299h | CCPR2H                        | 319h |                               | 399h | _                             |

| 01Ah | TMR2                          | 09Ah | OSCSTAT                       | 11Ah | —                             | 19Ah | TXREG                         | 21Ah | —                             | 29Ah | CCP2CON                       | 31Ah | —                             | 39Ah | —                             |

| 01Bh | PR2                           | 09Bh | ADRESL                        | 11Bh | —                             | 19Bh | SPBRG                         | 21Bh | —                             | 29Bh | —                             | 31Bh | —                             | 39Bh | _                             |

| 01Ch | T2CON                         | 09Ch | ADRESH                        | 11Ch | —                             | 19Ch | SPBRGH                        | 21Ch | _                             | 29Ch | —                             | 31Ch | _                             | 39Ch | _                             |

| 01Dh | _                             | 09Dh | ADCON0                        | 11Dh | APFCON                        | 19Dh | RCSTA                         | 21Dh | _                             | 29Dh | _                             | 31Dh | _                             | 39Dh | _                             |

| 01Eh |                               | 09Eh | ADCON1                        | 11Eh | _                             | 19Eh | TXSTA                         | 21Eh |                               | 29Eh | _                             | 31Eh |                               | 39Eh | _                             |

| 01Fh | —                             | 09Fh | —                             | 11Fh | —                             | 19Fh | BAUDCON                       | 21Fh |                               | 29Fh | —                             | 31Fh | _                             | 39Fh | _                             |

| 020h |                               | 0A0h |                               | 120h |                               | 1A0h |                               | 220h |                               | 2A0h |                               | 320h | General Purpose               | 3A0h |                               |

|      | General                       |      | Register                      |      |                               |

|      | Purpose                       | 32Fh | 16 Bytes                      |      | Unimplemented                 |

|      | Register<br>80 Bytes          | 330h | Unimplemented                 |      | Read as '0'                   |

|      | 00 Dytes                      |      | 00 Dytes                      |      | 00 Dytes                      |      | oo bytes                      |      | 00 Dyies                      |      | oo bytes                      |      | Read as '0'                   |      |                               |

| 06Fh |                               | 0EFh |                               | 16Fh |                               | 1EFh |                               | 26Fh |                               | 2EFh |                               | 36Fh |                               | 3EFh |                               |

| 070h |                               | 0F0h | Common RAM                    | 170h | Common RAM                    | 1F0h | Common RAM                    | 270h | Common RAM                    | 2F0h | Common RAM                    | 370h | Common RAM                    | 3F0h | Common RAM                    |

|      | Common RAM                    |      | (Accesses                     |

| 07Fh |                               | 0FFh | 70h – 7Fh)                    | 17Fh | 70h – 7Fh)                    | 1FFh | 70h – 7Fh)                    | 27Fh | 70h – 7Fh)                    | 2FFh | 70h – 7Fh)                    | 37Fh | 70h – 7Fh)                    | 3FFh | 70h – 7Fh)                    |

| U/Fn |                               | UFFN |                               | 17FN |                               | IFFN |                               | 27FN |                               | ZEEU |                               | SIFN |                               | SEEU |                               |

d: = Unimplemented data memory locations, read as '0'.

1: PIC16F/LF1516/7/8/9 only.

2: PIC16F1516/7 only. Legend: Note 1:

### 3.4.5 CORE FUNCTION REGISTERS SUMMARY

The Core Function registers listed in Table 3-7 can be addressed from any Bank.

| Addr            | Name      | Bit 7                                      | Bit 6                                           | Bit 5         | Bit 4            | Bit 3        | Bit 2         | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on all other Resets |  |  |

|-----------------|-----------|--------------------------------------------|-------------------------------------------------|---------------|------------------|--------------|---------------|--------|--------|----------------------|---------------------------|--|--|

| Bank (          | Bank 0-31 |                                            |                                                 |               |                  |              |               |        |        |                      |                           |  |  |

| x00h or<br>x80h | INDF0     |                                            | this location<br>ical register)                 |               | xxxx xxxx        | uuuu uuuu    |               |        |        |                      |                           |  |  |

| x01h or<br>x81h | INDF1     |                                            | this location<br>ical register)                 |               | nts of FSR1H     | /FSR1L to ad | ddress data r | memory |        | xxxx xxxx            | uuuu uuuu                 |  |  |

| x02h or<br>x82h | PCL       | Program Co                                 | ounter (PC) I                                   | Least Signifi | cant Byte        |              |               |        |        | 0000 0000            | 0000 0000                 |  |  |

| x03h or<br>x83h | STATUS    |                                            | <u>TO</u> <u>PD</u> <u>Z</u> <u>DC</u> <u>C</u> |               |                  |              |               |        | 1 1000 | q quuu               |                           |  |  |

| x04h or<br>x84h | FSR0L     | Indirect Data Memory Address 0 Low Pointer |                                                 |               |                  |              |               |        |        | 0000 0000            | uuuu uuuu                 |  |  |

| x05h or<br>x85h | FSR0H     | Indirect Dat                               | Indirect Data Memory Address 0 High Pointer     |               |                  |              |               |        |        |                      | 0000 0000                 |  |  |

| x06h or<br>x86h | FSR1L     | Indirect Dat                               | ta Memory A                                     | ddress 1 Lo   | w Pointer        |              |               |        |        | 0000 0000            | uuuu uuuu                 |  |  |

| x07h or<br>x87h | FSR1H     | Indirect Dat                               | ta Memory A                                     | ddress 1 Hig  | gh Pointer       |              |               |        |        | 0000 0000            | 0000 0000                 |  |  |

| x08h or<br>x88h | BSR       | -                                          | -                                               | -             | BSR4             | BSR3         | BSR2          | BSR1   | BSR0   | 0 0000               | 0 0000                    |  |  |

| x09h or<br>x89h | WREG      | Working Register                           |                                                 |               |                  |              |               |        |        |                      | uuuu uuuu                 |  |  |

| x0Ahor<br>x8Ah  | PCLATH    | —                                          | Write Buffer                                    | for the uppe  | er 7 bits of the | e Program Co | ounter        |        |        | -000 0000            | -000 0000                 |  |  |

| x0Bhor<br>x8Bh  | INTCON    | GIE                                        | PEIE                                            | TMR0IE        | INTE             | IOCIE        | TMR0IF        | INTF   | IOCIF  | 0000 0000            | 0000 0000                 |  |  |

TABLE 3-7: CORE FUNCTION REGISTERS SUMMARY

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

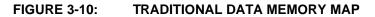

#### FIGURE 3-9: INDIRECT ADDRESSING

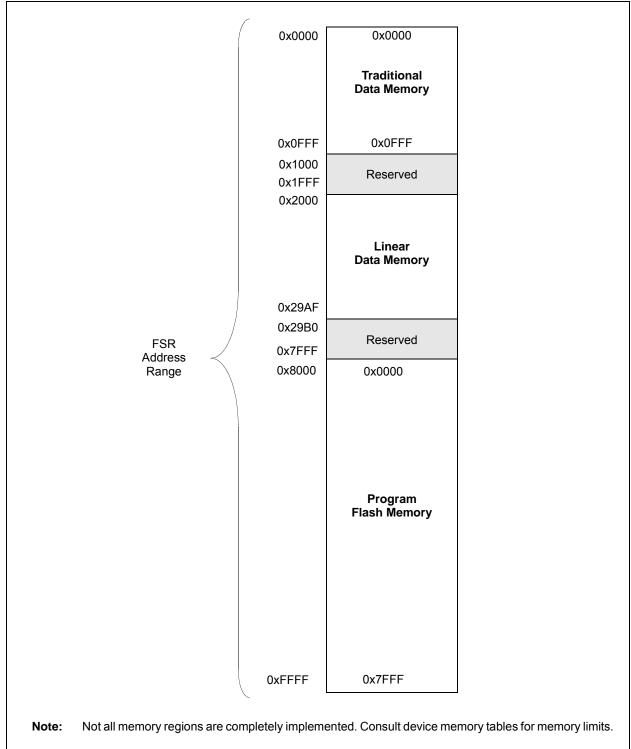

#### 3.7.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

### 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

#### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

| U-0                  | U-0       | U-0                          | U-0  | R-x/u                                                 | R/W-x/u            | R/W-x/u            | R/W-x/u            |  |  |  |  |

|----------------------|-----------|------------------------------|------|-------------------------------------------------------|--------------------|--------------------|--------------------|--|--|--|--|

| _                    | _         | _                            | —    | RE3                                                   | RE2 <sup>(1)</sup> | RE1 <sup>(1)</sup> | RE0 <sup>(1)</sup> |  |  |  |  |

| bit 7                |           |                              |      |                                                       |                    |                    | bit (              |  |  |  |  |

| Legend:              |           |                              |      |                                                       |                    |                    |                    |  |  |  |  |

| R = Readab           | ole bit   | W = Writable I               | bit  | U = Unimplemented bit, read as '0'                    |                    |                    |                    |  |  |  |  |

| u = Bit is unchanged |           | x = Bit is unkn              | own  | -n/n = Value at POR and BOR/Value at all other Resets |                    |                    |                    |  |  |  |  |

| '1' = Bit is se      | et        | '0' = Bit is clea            | ared |                                                       |                    |                    |                    |  |  |  |  |

| bit 7-4              | Unimpleme | nted: Read as 'o             | )'   |                                                       |                    |                    |                    |  |  |  |  |

| bit 3-0              | -         | ORTE I/O Pin bit<br>is > Viн |      |                                                       |                    |                    |                    |  |  |  |  |

**Note 1:** RE<2:0> are not implemented on the PIC16(L)F1516/8. Read as '0'. Writes to RE<2:0> are actually written to corresponding LATE register. Reads from PORTE register is the return of actual I/O pin values.

#### REGISTER 12-20: TRISE: PORTE TRI-STATE REGISTER

| U-0   | U-0 | U-0 | U-0 | U-1 <sup>(2)</sup> | R/W-1                 | R/W-1                 | R/W-1                 |

|-------|-----|-----|-----|--------------------|-----------------------|-----------------------|-----------------------|

| _     | _   | _   | -   | _                  | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> |

| bit 7 |     |     |     |                    |                       |                       | bit 0                 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

bit 3 Unimplemented: Read as '1'

bit 2-0 TRISE<2:0>: RE<2:0> Tri-State Control bits<sup>(1)</sup>

- 1 = PORTE pin configured as an input (tri-stated)

- 0 = PORTE pin configured as an output

Note 1: TRISE<2:0> are not implemented on the PIC16(L)F1517/9. Read as '0'.

2: Unimplemented, read as '1'.

#### **REGISTER 12-21:** LATE: PORTE DATA LATCH REGISTER<sup>(2)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | _   | _   | _   | _   | LATE2   | LATE1   | LATE0   |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-3 | Unimplemented: | Read as '0' |

|---------|----------------|-------------|

|         |                |             |

bit 2-0 LATE<2:0>: PORTE Output Latch Value bits<sup>(1)</sup>

- **Note 1:** Writes to PORTE are actually written to corresponding LATE register. Reads from PORTE register is the return of actual I/O pin values.

- 2: PIC16(L)F1517/9 only.

#### REGISTER 12-22: ANSELE: PORTE ANALOG SELECT REGISTER<sup>(2)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-----|-----|-------|-------|-------|

|       | _   | _   | _   | _   | ANSE2 | ANSE1 | ANSE0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 ANSE<2:0>: Analog Select between Analog or Digital Function on pins RE<2:0>, respectively

- 0 = Digital I/O. Pin is assigned to port or digital special function.

- 1 =Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

- **Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

- 2: PIC16(L)F1517/9 only.

#### TABLE 18-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                      |

|-------|---------------------------------------------------------|

| 00    | Timer1 Gate Pin                                         |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h) |

| 10    | Timer2 match PR2                                        |

| 11    | Reserved                                                |

#### 18.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 18.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 18.6.2.3 Timer2 Match PR2 Operation

When Timer2 increments and matches PR2, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 18.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single-level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 18-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |

|-------|---------------------------------------------|

|       | as changing the gate polarity may result in |

|       | indeterminate operation.                    |

#### 18.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single-pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 18-5 for timing details.

If the Single-Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 18-6 for timing details.

#### 18.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

#### 18.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

| FIGURE 18-6:           | TIMER1 GATE SINGLE                                            | -PULSE AND TOGGLE COMBIN                     | ED MODE                                       |

|------------------------|---------------------------------------------------------------|----------------------------------------------|-----------------------------------------------|

| TMR1GE                 |                                                               |                                              |                                               |

| T1GPOL                 |                                                               |                                              |                                               |

| T1GSPM                 |                                                               |                                              |                                               |

| T1GTM                  |                                                               |                                              |                                               |

| T1GG <u>O/</u><br>DONE | ✓ Set by software<br>Counting enabled o<br>rising edge of T1G | n<br>S                                       | Cleared by hardware on falling edge of T1GVAL |

| T1G_IN                 |                                                               |                                              |                                               |

| т1СКІ                  |                                                               |                                              |                                               |

| T1GVAL                 |                                                               |                                              |                                               |

| Timer1                 | Ν                                                             | <u>N+1</u> <u>N+2</u> <u>N+3</u> <u>N+4</u>  |                                               |

| TMR1GIF                | Cleared by software                                           | Set by hardware on falling edge of T1GVAL —▶ | Cleared by software                           |

#### 20.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPx module does not assert control of the CCPx pin (see the CCPxCON register).

#### 20.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is chosen (CCPxM<3:0> = 1011), the CCPx module does the following:

- Resets Timer1

- Starts an ADC conversion if ADC is enabled

The CCPx module does not assert control of the CCPx pin in this mode.

The Special Event Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPRxH, CCPRxL register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. The Special Event Trigger output starts an ADC conversion (if the ADC module is enabled). This allows the CCPRxH, CCPRxL register pair to effectively provide a 16-bit programmable period register for Timer1.

#### TABLE 20-2: SPECIAL EVENT TRIGGER

| Device              | CCPx |

|---------------------|------|

| PIC16(L)F1516/7/8/9 | CCP2 |

Refer to **Section 16.2.5 "Special Event Trigger"** for more information.

- Note 1: The Special Event Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

- 2: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Special Event Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

#### 20.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

#### 20.2.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function**" for more information.

#### 20.3 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 20-3 shows a typical waveform of the PWM signal.

#### 20.3.1 STANDARD PWM OPERATION

The standard PWM function described in this section is available and identical for all CCP modules.

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to 10 bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PR2 registers

- T2CON registers

- CCPRxL registers

- CCPxCON registers

Figure 20-4 shows a simplified block diagram of PWM operation.

Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

2: Clearing the CCPxCON register will relinquish control of the CCPx pin.

#### 21.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK line. The master determines when the slave (Processor 2, Figure 21-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and Status bits appropriately set). The clock polarity is selected by appropriately programming the CKP bit of the SSPCON1 register and the CKE bit of the SSPSTAT register. This then, would give waveforms for SPI communication as shown in Figure 21-6, Figure 21-8, Figure 21-9 and Figure 21-10, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- · Timer2 output/2

- Fosc/(4 \* (SSPADD + 1))

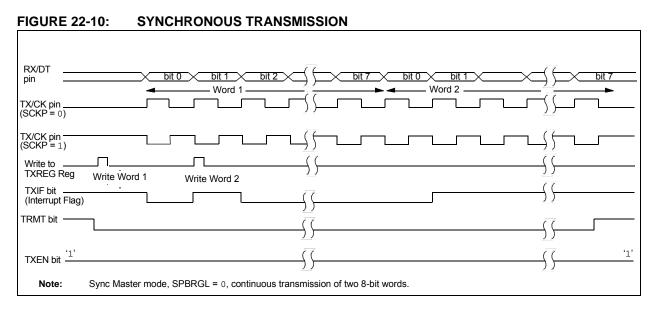

Figure 21-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

Write to SSPBUF SCK (CKP = 0  $\dot{C}KE = 0$ ) SCK (CKP = 1  $\dot{C}KE = 0$ ) 4 Clock Modes SCK (CKP = 0 CKE = 1) SCK (CKP = 1 CKE = 1) bit 6 bit 2 SDO bit 7 bit 5 bit 4 bit 3 bit 1 bit 0 (CKE = 0) bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 SDO (CKE = 1) SDI (SMP = 0)bit 7 bit 0 Input Sample (SMP = 0)SDI (SMP = 1) bit 7 hi 0 Input Sample (SMP = 1)1 SSPIF SSPSR to SSPBUF

FIGURE 21-6: SPI MODE WAVEFORM (MASTER MODE)

#### 21.6.13.3 Bus Collision During a Stop Condition

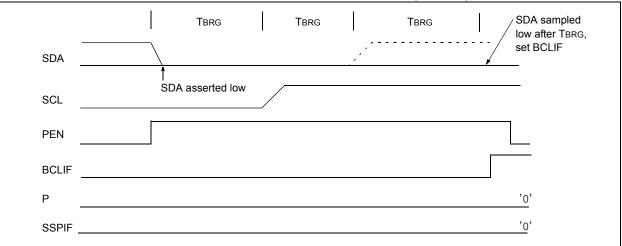

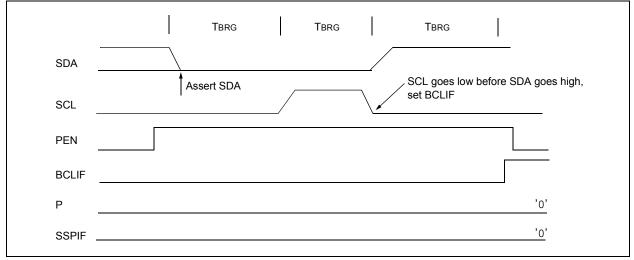

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out (Case 1).

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high (Case 2).

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 21-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 21-39).

#### FIGURE 21-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 21-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

| WCOL         SSPOV         SSPEN         CKP         SSPM<3:0>           bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/C/HS-0/0         | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0/0                                     | R/W-0/0                            | R/W-0/0                              | R/W-0/0              | R/W-0/0                 | R/W-0/0                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------|--------------------------------------|----------------------|-------------------------|-------------------------------------------|

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Resets         '1' = Bit is set       '0' = Bit is cleared       HS = Bit is set by hardware       C = User cleared         bit 7       WCOL: Write Collision Detect bit       Master mode:       1       - A write to the SSPBUF register was attempted while the I <sup>2</sup> C conditions were not valid for a transmission to be started 0 = No collision         Slave mode:       1 = A write to the SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)       0 = No collision         bit 6       SSPOV: Receive Overflow Indicator bit <sup>(1)</sup> In SPI mode:       1         1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is Overflow can only occur in Slave mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing the SSPBUF register (must be cleared in software).       0 = No overflow         0 = No overflow       In a A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit r (must be cleared in software).       0 = No overflow         0 = No overflow       In 2 A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit r (must be cleared in software).       0 = No overflow <tr< td=""><td>WCOL</td><td>SSPOV</td><td>SSPEN</td><td>CKP</td><td></td><td>SSF</td><td>M&lt;3:0&gt;</td><td></td></tr<>                                                            | WCOL               | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SSPEN                                       | CKP                                |                                      | SSF                  | M<3:0>                  |                                           |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Resets         '1' = Bit is set       '0' = Bit is cleared       HS = Bit is set by hardware       C = User cleared         bit 7       WCOL: Write Collision Detect bit       Master mode:       I = A write to the SSPBUF register was attempted while the I <sup>2</sup> C conditions were not valid for a transmission to be started 0 = No collision         Slave mode:       I = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)       0 = No collision         bit 6       SSPOV: Receive Overflow Indicator bit <sup>(1)</sup> In SPI mode:       I = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is Overflow. In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to SSPBUF register (must be cleared in software).       0 = No overflow.         In PC mode:       I = A byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is Overflow under the software).       0 = No overflow.         In PC mode:       I = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit r (must be cleared in software).       0 = No overflow         In PC mode:       I = A byte is received while the SSPBUF register is still holding the previous byte.                                                                                                                                     | bit 7              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                             |                                    |                                      |                      |                         | bit (                                     |

| u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Resets         '1' = Bit is set       '0' = Bit is cleared       HS = Bit is set by hardware       C = User cleared         bit 7       WCOL: Write Collision Detect bit<br>Master mode:       I = A write to the SSPBUF register was attempted while the I <sup>2</sup> C conditions were not valid for a transmission to be started<br>0 = No collision         Slave mode:       I = A write to the SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)       0 = No collision         bit 6       SSPOV: Receive Overflow Indicator bit <sup>(1)</sup><br>InSPI mode:       I = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is<br>Overflow can only occur in Slave mode. In Slave mode, the user must read the SSPBUF, even if only transmitting data, to av<br>setting overflow. In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to<br>SSPBUF register (must be cleared in software).         0 = No overflow       I = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit r<br>(must be cleared in software).         0 = No overflow       I = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit r<br>(must be cleared in software).         0 = No overflow       I = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit r<br>(must be cleared in software).         0 =                                      | Legend:            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                             |                                    |                                      |                      |                         |                                           |

| 1'1 = Bit is set       '0' = Bit is cleared       HS = Bit is set by hardware       C = User cleared         bit 7       WCOL: Write Collision Detect bit<br>Master mode:<br>1 = A write to the SSPBUF register was attempted while the 1 <sup>2</sup> C conditions were not valid for a transmission to be started<br>0 = No collision<br>Slave mode:<br>1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)<br>0 = No collision         bit 6       SSPOV: Receive Overflow Indicator bit <sup>(1)</sup><br>InSPI mode:<br>1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is<br>Overflow can only occur in Slave mode. In Slave mode, the user must read the SSPBUF, even if only transmitting data, to av<br>setting overflow. In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to<br>SSPBUF register (must be cleared in software).<br>0 = No overflow<br>In I <sup>2</sup> C mode:<br>1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit r<br>(must be cleared in software).<br>0 = No overflow<br>bit 5         bit 5       SSPEN: Synchronous Serial Port Enable bit<br>In both modes, when enabled, these pins must be properly configured as input or output<br>In <u>SPI mode:</u><br>1 = Enables serial port and configures SCK, SDO, SDI and <u>SS</u> as the source of the serial port pins <sup>(2)</sup><br>0 = Disables serial port and configures these pins as I/O port pins<br>In <sup>2</sup> C mode:<br>1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins <sup>(3)</sup> | R = Readable bit   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W = Writable bit                            |                                    | U = Unimplemente                     | ed bit, read as '0'  |                         |                                           |

| <ul> <li>bit 7 WCOL: Write Collision Detect bit<br/><u>Master mode:</u> <ol> <li>A write to the SSPBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started<br/>0 = No collision<br/><u>Slave mode:</u> </li> <li>The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)<br/>0 = No collision</li> </ol> </li> <li>bit 6 SSPOV: Receive Overflow Indicator bit<sup>(1)</sup><br/>In <u>SPI mode:</u> <ol> <li>A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is<br/>Overflow can only occur in Slave mode. In Slave mode, the user must read the SSPBUF, even if only transmitting data, to av<br/>setting overflow. In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to<br/>SSPBUF register (must be cleared in software).</li> <li>No overflow</li> <li>A hyte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit r<br/>(must be cleared in software).</li> <li>No overflow</li> </ol> </li> <li>bit 5 SSPEN: Synchronous Serial Port Enable bit<br/>In both modes, when enabled, these pins must be properly configured as input or output<br/>In <u>SPI mode:</u> <ol> <li>E nables serial port and configures SCK, SDO, SDI and <u>SS</u> as the source of the serial port pins<sup>(2)</sup></li> <li>D = Disables serial port and configures these pins as I/O port pins<br/>In <sup>2</sup>C mode:</li> </ol> </li> </ul>                                                                                                                                                                                 | u = Bit is unchang | ed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | x = Bit is unknow                           | า                                  | -n/n = Value at PO                   | R and BOR/Valu       | e at all other Resets   |                                           |

| Master mode:         1 = A write to the SSPBUF register was attempted while the I <sup>2</sup> C conditions were not valid for a transmission to be started<br>0 = No collision         Slave mode:         1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)         0 = No collision         Blave mode:         1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)         0 = No collision         bit 6         SSPOV: Receive Overflow Indicator bit <sup>(1)</sup><br>In SPI mode:         1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is<br>Overflow can only occur in Slave mode. In Slave mode, the user must read the SSPBUF, even if only transmitting data, to av<br>setting overflow. In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing the<br>SSPBUF register (must be cleared in software).         0 = No overflow         0 = No overflow         1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit r<br>(must be cleared in software).         0 = No overflow         bit 5       SSPEN: Synchronous Serial Port Enable bit<br>In both modes, when enabled, these pins must be properly configured as input or output<br>In SPI mode:         1 = Enables serial port and configures SCK, SDO, SDI and SS as the source of the serial port pins <sup>(2)</sup> 0 = Disables serial port and con                                                                                                                                                           | '1' = Bit is set   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | '0' = Bit is cleared                        | l                                  | HS = Bit is set by h                 | nardware             | C = User cleared        |                                           |

| <ul> <li>In SPI mode:         <ul> <li>A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is Overflow can only occur in Slave mode. In Slave mode, the user must read the SSPBUF, even if only transmitting data, to ave setting overflow. In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing the SSPBUF register (must be cleared in software).</li> <li>No overflow</li> <li>No overflow</li> <li>In 1<sup>2</sup>C mode:</li> <li>A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit r (must be cleared in software).</li> <li>No overflow</li> <li>No overflow</li> <li>SSPEN: Synchronous Serial Port Enable bit in both modes, when enabled, these pins must be properly configured as input or output In SPI mode:</li> <li>E Enables serial port and configures SCK, SDO, SDI and SS as the source of the serial port pins<sup>(2)</sup></li> <li>Disables serial port and configures these pins as I/O port pins In 1<sup>2</sup>C mode:</li> <li>E nables the serial port and configures the SDA and SCL pins as the source of the serial port pins<sup>(3)</sup></li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>1</b>           | 1 = The SSPBU<br>0 = No collision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                           |                                    | mitting the previous wo              | ord (must be clear   | ed in software)         |                                           |

| <ul> <li>bit 5</li> <li>SSPEN: Synchronous Serial Port Enable bit<br/>In both modes, when enabled, these pins must be properly configured as input or output<br/>In SPI mode:</li> <li>1 = Enables serial port and configures SCK, SDO, SDI and SS as the source of the serial port pins<sup>(2)</sup></li> <li>0 = Disables serial port and configures these pins as I/O port pins<br/>In I<sup>2</sup>C mode:</li> <li>1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins<sup>(3)</sup></li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit 6              | <ul> <li>SSPOV: Receive Overflow Indicator bit<sup>(1)</sup></li> <li>In SPI mode:         <ol> <li>A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSI Overflow can only occur in Slave mode. In Slave mode, the user must read the SSPBUF, even if only transmitting data, to setting overflow. In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writin SSPBUF register (must be cleared in software).</li> <li>No overflow</li> </ol> </li> </ul> |                                             |                                    |                                      |                      |                         | ng data, to avoid<br>ed by writing to the |

| In both modes, when enabled, these pins must be properly configured as input or output<br>In SPI mode:<br>$I = Enables$ serial port and configures SCK, SDO, SDI and $\overline{SS}$ as the source of the serial port pins<br>I = Disables serial port and configures these pins as I/O port pins<br>In I <sup>2</sup> C mode:<br>I = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins<br>I = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins<br>I = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins<br>I = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    | 0 = No overflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ,                                           | abla bit                           |                                      |                      |                         |                                           |

| 1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | υπο                | In both modes, w<br>In SPI mode:<br>1 = Enables ser<br>0 = Disables se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | hen enabled, these<br>ial port and configur | pins must be pr<br>es SCK, SDO, SI | DI and $\overline{SS}$ as the source |                      | t pins <sup>(2)</sup>   |                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    | 1 = Enables the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                             |                                    |                                      | irce of the serial p | ort pins <sup>(3)</sup> |                                           |

CKP: Clock Polarity Select bit bit 4 <u>In SPI mode:</u> 1 = Idle state for clock is a high level 0 = Idle state for clock is a low level In I<sup>2</sup>C Slave mode: SCL release control 1 = Enable clock

- 0 = Holds clock low (clock stretch). (Used to ensure data setup time.)

- In I<sup>2</sup>C Master mode: Unused in this mode

- bit 3-0 SSPM<3:0>: Synchronous Serial Port Mode Select bits

- 1111 = I<sup>2</sup>C Slave mode, 10-bit address with Start and Stop bit interrupts enabled

- 1110 =  $I^2C$  Slave mode, 7-bit address with Start and Stop bit interrupts enabled

- 1101 = Reserved

- 1100 = Reserved 1011 =  $I^2C$  firmware controlled Master mode (slave idle)

- 1010 = SPI Master mode, clock = Fosc/(4 \* (SSPADD+1))<sup>(5)</sup>

- 1001 = Reserved

- 1000 =  $I^2C$  Master mode, clock = Fosc / (4 \* (SSPADD+1))<sup>(4)</sup>

- 0111 = I<sup>2</sup>C Slave mode, 10-bit address

- $0110 = I^2C$  Slave mode, 7-bit address

- 0101 = SPI Slave mode, clock = SCK pin, <u>SS</u> pin control disabled, <u>SS</u> can be used as I/O pin 0100 = SPI Slave mode, clock = SCK pin, <u>SS</u> pin control enabled

- 0011 = SPI Master mode, clock = TMR2 output/2

- 0010 = SPI Master mode, clock = Fosc/64

- 0001 = SPI Master mode, clock = Fosc/16

- 0000 = SPI Master mode, clock = Fosc/4

- Note 1: In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register.

- When enabled, these pins must be properly configured as input or output. 2:

- 3: When enabled, the SDA and SCL pins must be configured as inputs.

- 4: SSPADD values of 0, 1 or 2 are not supported for I<sup>2</sup>C mode.

- SSPADD value of '0' is not supported. Use SSPM = 0000 instead. 5:

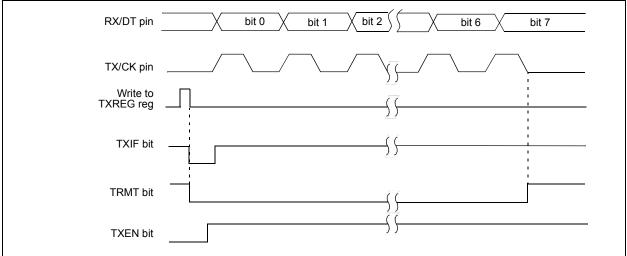

#### 22.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 22-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 22.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

**Note 1:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

#### 22.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 22.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

| Note: | If the receive FIFO is overrun, no additional |

|-------|-----------------------------------------------|

|       | characters will be received until the overrun |

|       | condition is cleared. See Section 22.1.2.5    |

|       | "Receive Overrun Error" for more              |

|       | information on overrun errors.                |

#### 22.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE, Interrupt Enable bit of the PIE1 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

|         |            | -        |        |               |             |              |        |        |                     |

|---------|------------|----------|--------|---------------|-------------|--------------|--------|--------|---------------------|

| Name    | Bit 7      | Bit 6    | Bit 5  | Bit 4         | Bit 3       | Bit 2        | Bit 1  | Bit 0  | Register<br>on Page |

| BAUDCON | ABDOVF     | RCIDL    | _      | SCKP          | BRG16       | —            | WUE    | ABDEN  | 232                 |

| INTCON  | GIE        | PEIE     | TMR0IE | INTE          | IOCIE       | TMR0IF       | INTF   | IOCIF  | 74                  |

| PIE1    | TMR1GIE    | ADIE     | RCIE   | TXIE          | SSPIE       | CCP1IE       | TMR2IE | TMR1IE | 75                  |

| PIR1    | TMR1GIF    | ADIF     | RCIF   | TXIF          | SSPIF       | CCP1IF       | TMR2IF | TMR1IF | 77                  |

| RCREG   |            |          | EUS    | ART Receiv    | ve Data Reg | gister       |        |        | 225*                |

| RCSTA   | SPEN       | RX9      | SREN   | CREN          | ADDEN       | FERR         | OERR   | RX9D   | 231                 |

| SPBRGL  |            | BRG<7:0> |        |               |             |              | 233*   |        |                     |

| SPBRGH  |            |          |        | BRG<          | :15:8>      |              |        |        | 233*                |

| TRISC   | TRISC7     | TRISC6   | TRISC5 | TRISC4        | TRISC3      | TRISC2       | TRISC1 | TRISC0 | 114                 |

| TXSTA   | CSRC       | TX9      | TXEN   | SYNC          | SENDB       | BRGH         | TRMT   | TX9D   | 230                 |

| Logondy | – unimplom |          |        | ممامم ممالم م |             | for one work |        | ntinn  |                     |