Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$\times$  FI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, UART/USART                                               |

| Peripherals                | LVD, POR, WDT                                                                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 3K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                     |

| Data Converters            | A/D 12x8/12b                                                                    |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 32-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 32-HVQFN (5x5)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f117bcgna-40 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin<br>count | Package                                                   | Ordering Part Number                                                                              |

|--------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 20 pins      | 20-pin plastic LSSOP (4.4 $\times$ 6.5 mm, 0.65 mm pitch) | R5F11768GSP#30, R5F1176AGSP#30,<br>R5F11768GSP#50, R5F1176AGSP#50                                 |

| 24 pins      | 24-pin plastic HWQFN<br>(4 × 4 mm, 0.5 mm pitch)          | R5F11778GNA#U0, R5F1177AGNA#U0,<br>R5F11778GNA#W0, R5F1177AGNA#W0                                 |

| 30 pins      | 30-pin plastic LSSOP<br>(7.62 mm (300), 0.65 mm pitch)    | R5F117A8GSP#30, R5F117AAGSP#30, R5F117ACGSP#30,<br>R5F117A8GSP#50, R5F117AAGSP#50, R5F117ACGSP#50 |

| 32 pins      | 32-pin plastic HVQFN (5 $\times$ 5 mm, 0.5 mm pitch)      | R5F117BAGNA#20, R5F117BCGNA#20,<br>R5F117BAGNA#40, R5F117BCGNA#40                                 |

|              | 32-pin plastic LQFP<br>(7 × 7 mm, 0.8 mm pitch)           | R5F117BAGFP#30, R5F117BCGFP#30,<br>R5F117BAGFP#50, R5F117BCGFP#50                                 |

| 48 pins      | 48-pin plastic LFQFP<br>(7 × 7 mm, 0.5 mm pitch)          | R5F117GAGFB#30, R5F117GCGFB#30,<br>R5F117GAGFB#50, R5F117GCGFB#50                                 |

Caution The ordering part numbers represent the numbers at the time of publication. For the latest ordering part numbers, refer to the target product page of the Renesas Electronics website.

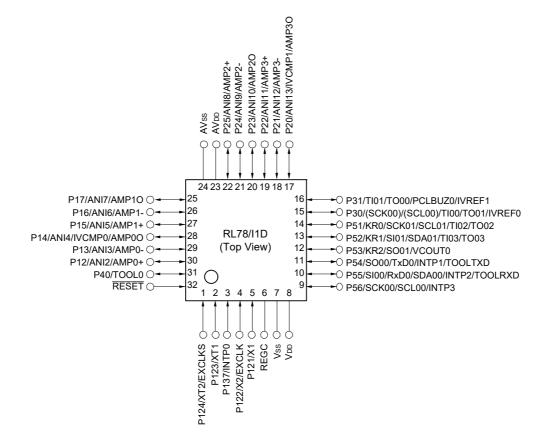

• 32-pin plastic LQFP (7 × 7 mm, 0.8 mm pitch)

- Caution 1. Connect the REGC pin to Vss pin via a capacitor (0.47 to 1  $\mu\text{F}).$

- Caution 2. Make AVss pin the same potential as Vss pin.

- Caution 3. Make AVDD pin the same potential as VDD pin.

- Remark 1. For pin identification, see 1.4 Pin Identification.

- **Remark 2.** Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register 0 (PIOR0).

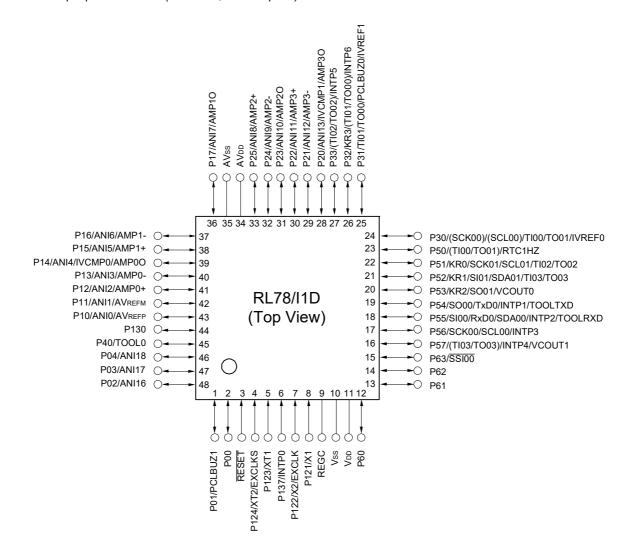

### 1.3.5 48-pin products

<R>

• 48-pin plastic LFQFP ( $7 \times 7$  mm, 0.5 mm pitch)

- Caution 1. Connect the REGC pin to Vss pin via a capacitor (0.47 to 1  $\mu\text{F}).$

- Caution 2. Make AVss pin the same potential as Vss pin.

- Caution 3. Make AV  $\ensuremath{\mathsf{DD}}$  pin the same potential as  $\ensuremath{\mathsf{VDD}}$  pin.

- Remark 1. For pin identification, see 1.4 Pin Identification.

- Remark 2. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register 0 (PIOR0).

(2/2)

|                       |               |                                                                                                                                                         | <del>.</del>                                                                                                                                                                                                                                         | ;                                                                  |                                               | (2)                                           |  |  |  |  |

|-----------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|--|--|--|--|

|                       |               | 20-pin                                                                                                                                                  | 24-pin                                                                                                                                                                                                                                               | 30-pin                                                             | 32-pin                                        | 48-pin                                        |  |  |  |  |

| lter                  | n             | R5F1176x<br>(x = 8, A)                                                                                                                                  | R5F1177x<br>(x = 8, A)                                                                                                                                                                                                                               | R5F117Ax<br>(x = 8, A, C)                                          | R5F117Bx<br>(x = A, C)                        | R5F117Gx<br>(x = A, C)                        |  |  |  |  |

| Clock output/buzzer   | output        | 1                                                                                                                                                       | 1                                                                                                                                                                                                                                                    | 1                                                                  | 1                                             | 2                                             |  |  |  |  |

|                       |               | (Main system clock<br>[30-pin, 32-pin, 48-p<br>• 2.44 kHz, 4.88 kHz<br>(Main system clock<br>• 256 Hz, 512 Hz, 1.                                       | z, 9.76 kHz, 1.25 MHz<br>k: fmain = 20 MHz ope<br>in products]<br>z, 9.76 kHz, 1.25 MHz<br>k: fmain = 20 MHz ope                                                                                                                                     | ration)<br>, 2.5 MHz, 5 MHz, 10<br>ration)<br>4.096 kHz, 8.192 kHz | MHz<br>, 16.384 kHz, 32.768 l                 | kHz                                           |  |  |  |  |

| 12-bit resolution A/D | converter     | 6 channels                                                                                                                                              | 6 channels                                                                                                                                                                                                                                           | 12 channels                                                        | 12 channels                                   | 17 channels                                   |  |  |  |  |

| Comparator (Windov    | v Comparator) | 2 channels                                                                                                                                              |                                                                                                                                                                                                                                                      |                                                                    |                                               |                                               |  |  |  |  |

| Operational amplifier |               | 2 channels                                                                                                                                              |                                                                                                                                                                                                                                                      | 4 channels                                                         |                                               |                                               |  |  |  |  |

| Data Operation Circu  | uit (DOC)     | Comparison, addition                                                                                                                                    | n, and subtraction of 1                                                                                                                                                                                                                              | 6-bit data                                                         |                                               |                                               |  |  |  |  |

| Serial interface      |               | • CSI: 1 channel/UA<br>[24-pin, 32-pin, 48-p                                                                                                            | <ul> <li>[20-pin, 30-pin products]</li> <li>CSI: 1 channel/UART: 1 channel/simplified l<sup>2</sup>C: 1 channel</li> <li>[24-pin, 32-pin, 48-pin products]</li> <li>CSI: 2 channels/UART: 1 channel/simplified l<sup>2</sup>C: 2 channels</li> </ul> |                                                                    |                                               |                                               |  |  |  |  |

| Data transfer control | ler (DTC)     | 16 sources                                                                                                                                              | 20 sources                                                                                                                                                                                                                                           | 19 sources                                                         | 20 sources                                    | 22 sources                                    |  |  |  |  |

| Event link controller | (ELC)         | Event input: 15<br>Event trigger<br>output: 5                                                                                                           | Event input: 17<br>Event trigger<br>output: 5                                                                                                                                                                                                        | Event input: 17<br>Event trigger<br>output: 7                      | Event input: 17<br>Event trigger<br>output: 7 | Event input: 20<br>Event trigger<br>output: 7 |  |  |  |  |

| Vectored interrupt    | Internal      | 22                                                                                                                                                      | 22                                                                                                                                                                                                                                                   | 24                                                                 | 24                                            | 24                                            |  |  |  |  |

| sources               | External      | 3                                                                                                                                                       | 5                                                                                                                                                                                                                                                    | 5                                                                  | 5                                             | 8                                             |  |  |  |  |

| Key interrupt         |               | —                                                                                                                                                       | 3                                                                                                                                                                                                                                                    | —                                                                  | 3                                             | 4                                             |  |  |  |  |

| Reset                 |               | Internal reset by R                                                                                                                                     | atchdog timer<br>ower-on-reset<br>oltage detector<br>egal instruction execu                                                                                                                                                                          | tion Note                                                          |                                               |                                               |  |  |  |  |

| Power-on-reset circu  | it            | <ul> <li>Power-on-reset: 1.51 ± 0.04V (T<sub>A</sub> = -40 to +85°C)</li> <li>Power-down-reset: 1.50 ± 0.04 V (T<sub>A</sub> = -40 to +85°C)</li> </ul> |                                                                                                                                                                                                                                                      |                                                                    |                                               |                                               |  |  |  |  |

| Voltage detector      | Power on      | 1.67 V to 3.13 V (12                                                                                                                                    | stages)                                                                                                                                                                                                                                              |                                                                    |                                               |                                               |  |  |  |  |

|                       | Power down    | 1.63 V to 3.06 V (12                                                                                                                                    | stages)                                                                                                                                                                                                                                              |                                                                    |                                               |                                               |  |  |  |  |

| On-chip debug funct   | ion           | Provided (Enable to                                                                                                                                     | tracing)                                                                                                                                                                                                                                             |                                                                    |                                               |                                               |  |  |  |  |

| Power supply voltage  | e             | V <sub>DD</sub> = 1.6 to 3.6 V                                                                                                                          |                                                                                                                                                                                                                                                      |                                                                    |                                               |                                               |  |  |  |  |

| Operating ambient te  | emperature    | T <sub>A</sub> = -40 to +105°C                                                                                                                          |                                                                                                                                                                                                                                                      |                                                                    |                                               |                                               |  |  |  |  |

The illegal instruction is generated when instruction code FFH is executed.

Reset by the illegal instruction execution is not issued by emulation with the in-circuit emulator or on-chip debug emulator.

| Items                          | Symbol | Con                                                                   | ditions      |                                       | MIN. | TYP. | MAX. | Unit |

|--------------------------------|--------|-----------------------------------------------------------------------|--------------|---------------------------------------|------|------|------|------|

| Input leakage<br>current, high |        |                                                                       |              |                                       |      | 1    | μA   |      |

|                                | ILIH2  | RESET                                                                 | VI = VDD     |                                       |      |      | 1    | μA   |

|                                | Ілнз   | P121 to P124 (X1, X2, EXCLK,<br>XT1, XT2, EXCLKS)                     | VI = VDD     | In input port or external clock input |      |      | 1    | μA   |

|                                |        |                                                                       |              | In resonator connection               |      |      | 10   | μA   |

|                                | ILIH4  | P10 to P17, P20 to P25                                                | VI = AVDD    |                                       |      |      | 1    | μA   |

| Input leakage<br>current, low  | ILIL1  | P00 to P04, P30 to P33, P40,<br>P50 to P57, P60 to P63, P130,<br>P137 | VI = Vss     |                                       |      |      | -1   | μA   |

|                                | ILIL2  | RESET                                                                 | VI = Vss     |                                       |      |      | -1   | μA   |

|                                | Ilil3  | P121 to P124 (X1, X2, EXCLK,<br>XT1, XT2, EXCLKS)                     | VI = Vss     | In input port or external clock input |      |      | -1   | μA   |

|                                |        |                                                                       |              | In resonator connection               |      |      | -10  | μΑ   |

|                                | ILIL4  | P10 to P17, P20 to P25                                                | VI = AVss    |                                       |      |      | -1   | μA   |

| On-chip pull-up<br>resistance  | Ru     | P00 to P04, P30 to P33, P40,<br>P50 to P57, P130                      | Vı = Vss, In | input port                            | 10   | 20   | 100  | kΩ   |

# $(TA = -40 \text{ to } +85^{\circ}C, \ 1.6 \text{ V} \le \text{AVDD} = \text{VDD} \le 3.6 \text{ V}, \ \text{Vss} = \text{AVss} = 0 \text{ V} ) \\ (TA = +85 \text{ to } +105^{\circ}C, \ 2.4 \text{ V} \le \text{AVDD} = \text{VDD} \le 3.6 \text{ V}, \ \text{Vss} = \text{AVss} = 0 \text{ V} ) \\$

(5/5)

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

#### (TA = -40 to +85°C, 1.6 V $\leq$ AVDD = VDD $\leq$ 3.6 V, Vss = AVss = 0 V) (TA = +85 to +105°C, 2.4 V $\leq$ AVDD = VDD $\leq$ 3.6 V, Vss = AVss = 0 V)

| (TA = +85 to +10 | 05°C, 2.4 | $V \leq AVDD = VD$ | D ≤ 3.6 V, Vss = AVss = 0 V) |      |      |       | (4/4) |

|------------------|-----------|--------------------|------------------------------|------|------|-------|-------|

| Parameter        | Symbol    |                    | Conditions                   | MIN. | TYP. | MAX.  | Unit  |

| Supply current   | IDD3      | STOP mode          | TA = -40°C                   |      | 0.16 | 0.51  | μA    |

| Note 1           | Note 2    | Note 3             | TA = +25°C                   |      | 0.22 | 0.51  |       |

|                  |           |                    | TA = +50°C                   |      | 0.27 | 1.10  |       |

|                  |           |                    | TA = +70°C                   |      | 0.37 | 1.90  |       |

|                  |           |                    | TA = +85°C                   |      | 0.60 | 3.30  |       |

|                  |           |                    | TA = +105°C                  |      | 1.50 | 17.00 |       |

#### <R>

Note 1. Total current flowing into VDD, including the input leakage current flowing when the level of the input pin is fixed to VDD or Vss. The MAX values include the peripheral operating current. However, these values do not include the current flowing into the A/D converter, operational amplifier, comparator, LVD circuit, I/O ports, and on-chip pull-up/pull-down resistors, and the current flowing during data flash rewrite.

Note 2. The values do not include the current flowing into the real-time clock, 12-bit interval timer, and watchdog timer.

**Note 3.** For the setting of the current values when operating the subsystem clock in STOP mode, see the current values when operating the subsystem clock in HALT mode.

## 2.5 Peripheral Functions Characteristics

AC Timing Test Points

Viн/Voн VIH/VOH Test points VIL/VOL VIL/VOL .

## 2.5.1 Serial array unit

#### (1) During communication at same potential (UART mode)

#### (TA = -40 to +85°C, 1.6 V $\leq$ AVDD = VDD $\leq$ 3.6 V, VSS = AVSS = 0 V)

| Parameter     | Symbol | Conditions                                                                |      | speed main)<br>ode                                                        | · ·  | oeed main)<br>ode | · ·  | ower main)<br>ode | -    | ltage main)<br>ode | Unit |     |      |

|---------------|--------|---------------------------------------------------------------------------|------|---------------------------------------------------------------------------|------|-------------------|------|-------------------|------|--------------------|------|-----|------|

|               |        |                                                                           | MIN. | MAX.                                                                      | MIN. | MAX.              | MIN. | MAX.              | MIN. | MAX.               |      |     |      |

| Transfer rate |        | $2.4~V \leq V_{DD} \leq 3.6~V$                                            |      | fмск/6                                                                    |      | fмск/6            |      | fмск/6            |      | fмск/6             | bps  |     |      |

| Note 1        |        | Theoretical value of the maximum transfer rate $f_{MCK} = f_{CLK} Note 2$ |      | 4.0                                                                       |      | 1.3               |      | 0.1               |      | 0.6                | Mbps |     |      |

|               |        | $1.8 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$              |      | _                                                                         |      | fмск/6            |      | fмск/6            |      | fмск/6             | bps  |     |      |

|               |        |                                                                           |      | Theoretical value of the maximum transfer rate $f_{MCK} = f_{CLK}$ Note 2 |      | _                 |      | 1.3               |      | 0.1                |      | 0.6 | Mbps |

|               |        | $1.7~V \leq V_{DD} \leq 3.6~V$                                            |      | _                                                                         | -    | _                 | -    | _                 |      | fмск/6             | bps  |     |      |

|               |        | Theoretical value of the maximum transfer rate $f_{MCK} = f_{CLK}$ Note 2 |      |                                                                           | -    | _                 | -    | _                 |      | 0.6                | Mbps |     |      |

|               |        | $1.6~V \leq V_{DD} \leq 3.6~V$                                            |      | _                                                                         | -    | _                 | -    | _                 |      | fмск/6             | bps  |     |      |

|               |        | Theoretical value of the maximum transfer rate $f_{MCK} = f_{CLK} Note 2$ |      | _                                                                         | -    | _                 | -    | _                 |      | 0.6                | Mbps |     |      |

Note 1. Transfer rate in the SNOOZE mode is 4800 bps only.

Note 2.The maximum operating frequencies of the CPU/peripheral hardware clock (fcLK) are:<br/>HS (high-speed main) mode: $24 \text{ MHz} (2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V})$ <br/> $16 \text{ MHz} (2.4 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V})$ <br/>LS (low-speed main) mode: $8 \text{ MHz} (1.8 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V})$ <br/>LP (low-power main) mode: $1 \text{ MHz} (1.8 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V})$ <br/>LV (low-voltage main) mode: $4 \text{ MHz} (1.6 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V})$

# Caution Select the normal input buffer for the RxDq pin and the normal output mode for the TxDq pin by using port input mode register g (PIMg) and port output mode register g (POMg).

#### (TA = +85 to +105°C, 2.4 V $\leq$ AVDD = VDD $\leq$ 3.6 V, Vss = AVss = 0 V)

| Parameter            | Symbol | Conditions                                                                | HS (high-spee | HS (high-speed main) Mode |      |  |

|----------------------|--------|---------------------------------------------------------------------------|---------------|---------------------------|------|--|

| Falanielei           | Symbol | Conditions                                                                | MIN.          | MAX.                      | Unit |  |

| Transfer rate Note 1 |        | $2.4 \text{ V} \leq \text{Vdd} \leq 3.6 \text{ V}$                        |               | fмск/12                   | bps  |  |

|                      |        | Theoretical value of the maximum transfer rate $f_{MCK} = f_{CLK} Note 2$ |               | 2.0                       | Mbps |  |

Note 1. Transfer rate in the SNOOZE mode is 4800 bps only.

Note 2. The maximum operating frequencies of the CPU/peripheral hardware clock (fcLK) are:

HS (high-speed main) mode: 24 MHz (2.7 V  $\leq$  VDD  $\leq$  3.6 V)

16 MHz (2.4 V  $\leq$  VDD  $\leq$  3.6 V)

Caution Select the normal input buffer for the RxDq pin and the normal output mode for the TxDq pin by using port input mode register g (PIMg) and port output mode register g (POMg).

#### (4) During communication at same potential (CSI mode) (slave mode, SCKp... external clock input)

|                 | ,-     |           | ,                                                         |                 |                   | -,              |                   |                 |                   |                               |      | (   |

|-----------------|--------|-----------|-----------------------------------------------------------|-----------------|-------------------|-----------------|-------------------|-----------------|-------------------|-------------------------------|------|-----|

| Parameter       | Symbol |           | Conditions                                                |                 | peed main)<br>ode | • •             | beed main)<br>bde | • •             | ower main)<br>ode | LV (low-voltage main)<br>Mode |      | Uni |

|                 |        |           |                                                           | MIN.            | MAX.              | MIN.            | MAX.              | MIN.            | MAX.              | MIN.                          | MAX. |     |

| SI00 setup time | tssik  | DAPmn = 0 | $2.7~V \leq V_{\text{DD}} \leq 3.6~V$                     | 120             |                   | 120             |                   | 120             |                   | 120                           |      | ns  |

|                 |        |           | $2.4~\text{V} \leq \text{V}_\text{DD} < 2.7~\text{V}$     | 200             |                   | 200             |                   | 200             |                   | 200                           |      |     |

|                 |        |           | $1.8 \text{ V} \leq V_{\text{DD}} < 2.4 \text{ V}$        | -               |                   |                 |                   |                 |                   |                               |      |     |

|                 |        |           | $1.6~\text{V} \leq \text{V}_\text{DD} < 1.8~\text{V}$     | -               |                   | _               |                   | _               |                   | 400                           |      |     |

|                 |        | DAPmn = 1 | $2.7~V \leq V_{\text{DD}} \leq 3.6~V$                     | 1/fмск          |                   | 1/fмск          |                   | 1/fмск          |                   | 1/fмск                        |      | n   |

|                 |        |           |                                                           | + 120           |                   | + 120           |                   | + 120           |                   | + 120                         |      |     |

|                 |        |           | $2.4 \text{ V} \leq \text{V}_{\text{DD}} < 2.7 \text{ V}$ | 1/fмск<br>+ 200 |                   | 1/fмск<br>+ 200 |                   | 1/fмск<br>+ 200 |                   | 1/fмск<br>+ 200               |      |     |

|                 |        |           | $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 2.4 \text{ V}$ | -               |                   |                 |                   |                 |                   |                               |      |     |

|                 |        |           | $1.6 \text{ V} \le \text{V}_{\text{DD}} < 1.8 \text{ V}$  | -               |                   | —               |                   | —               |                   | 1/fмск<br>+ 400               |      |     |

| SI00 hold time  | tĸssi  | DAPmn = 0 | $2.7~V \leq V_{\text{DD}} \leq 3.6~V$                     | 1/fмск<br>+ 120 |                   | 1/fмск<br>+ 120 |                   | 1/fмск<br>+ 120 |                   | 1/fмск<br>+ 120               |      | n   |

|                 |        |           | $2.4 \text{ V} \leq \text{V}_{\text{DD}} < 2.7 \text{ V}$ | 1/fмск<br>+ 200 |                   | 1/fмск<br>+ 200 |                   | 1/fмск<br>+ 200 |                   | 1/fмск<br>+ 200               |      |     |

|                 |        |           | $1.8 \text{ V} \le \text{V}_{\text{DD}} < 2.4 \text{ V}$  | _               |                   |                 |                   |                 |                   |                               |      |     |

|                 |        |           | $1.6 \text{ V} \le \text{V}_{\text{DD}} < 1.8 \text{ V}$  | -               |                   | —               |                   | —               |                   | 1/fмск<br>+ 400               |      |     |

|                 |        | DAPmn = 1 | $2.7~V \leq V_{\text{DD}} \leq 3.6~V$                     | 120             |                   | 120             |                   | 120             |                   | 120                           |      | n   |

|                 |        |           | $2.4~\text{V} \leq \text{V}_\text{DD} < 2.7~\text{V}$     | 200             |                   | 200             |                   | 200             |                   | 200                           |      | 1   |

|                 |        |           | $1.8~V \leq V_{\text{DD}} < 2.4~V$                        | -               |                   |                 |                   |                 |                   |                               |      |     |

|                 | 1      |           | $1.6 \text{ V} \le \text{V}_{\text{DD}} < 1.8 \text{ V}$  | _               |                   | _               |                   | _               |                   | 400                           |      | 1   |

### (TA = -40 to +85°C, 1.6 V $\leq$ AVDD = VDD $\leq$ 3.6 V, Vss = AVss = 0 V)

(2/2)

Caution Select the normal input buffer for the SIp pin and SCKp pin and the normal output mode for the SOp pin by using port input mode register g (PIMg) and port output mode register g (POMg).

Remark p: CSI number (p = 00), m: Unit number (m = 0), n: Channel number (n = 0), g: PIM and POM numbers (g = 5)

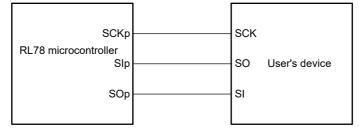

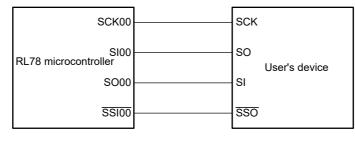

#### CSI mode connection diagram (during communication at same potential)

CSI mode connection diagram (during communication at same potential) (Slave Transmission of slave select input function (CSI00))

**Remark 1.** p: CSI number (p = 00, 01)

**Remark 2.** m: Unit number, n: Channel number (mn = 00, 01)

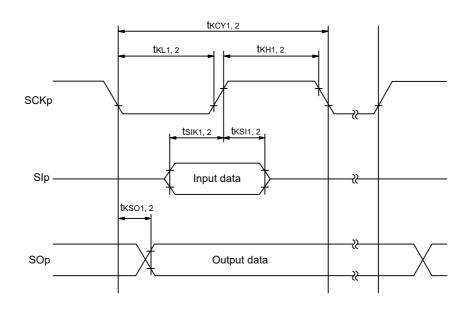

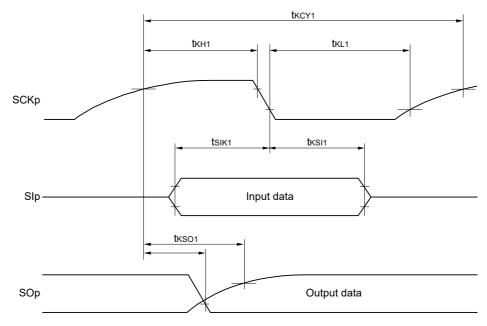

## CSI mode serial transfer timing (during communication at same potential) (When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.)

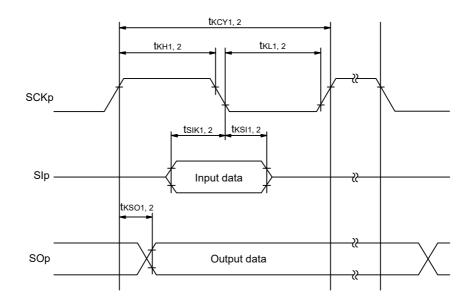

CSI mode serial transfer timing (during communication at same potential) (When DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.)

Remark 1. p: CSI number (p = 00, 01) Remark 2. m: Unit number, n: Channel number (mn = 00, 01)

### (5) During communication at same potential (simplified I<sup>2</sup>C mode)

| Parameter                        | Symbol   | Conditions                                                                                                                                                                               |                          | peed main)<br>ode |                           | peed main)<br>ode | -                         | w-power<br>mode |                           | -voltage<br>Mode | Unit |

|----------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------|---------------------------|-------------------|---------------------------|-----------------|---------------------------|------------------|------|

|                                  |          |                                                                                                                                                                                          | MIN.                     | MAX.              | MIN.                      | MAX.              | MIN.                      | MAX.            | MIN.                      | MAX.             |      |

| SCLr clock frequency             | fscL     | $\begin{array}{l} 2.7 \ \text{V} \leq \text{V}_{\text{DD}} \leq 3.6 \ \text{V}, \\ C_{\text{b}} = 50 \ \text{pF}, \ \text{R}_{\text{b}} = 2.7 \ \text{k}\Omega \end{array}$              |                          | 1000<br>Note 1    |                           | 400<br>Note 1     |                           | 250<br>Note 1   |                           | 400<br>Note 1    | kHz  |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{V}_{\mbox{DD}} \leq 3.6 \mbox{ V}, \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 3  k\Omega \end{array}$                              |                          | _                 |                           |                   |                           |                 |                           |                  |      |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{V}_{DD} < 2.7 \mbox{ V}, \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 5 \mbox{ k}\Omega \end{array}$                                 |                          | _                 |                           | 300<br>Note 1     |                           | 250<br>Note 1   |                           | 300<br>Note 1    |      |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.7 \mbox{ V} \leq \mbox{V}_{DD} < 1.8 \mbox{ V}, \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 5 \mbox{ k}\Omega \end{array}$                                 |                          | -                 |                           |                   |                           | -               |                           | 250<br>Note 1    |      |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.6 \mbox{ V} \leq \mbox{V}_{DD} < 1.8 \mbox{ V}, \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 5 \mbox{ k}\Omega \end{array}$                                 |                          | -                 |                           | -                 |                           | -               |                           |                  |      |

| Hold time<br>when SCLr = "L"     | t∟ow     | $\begin{array}{l} 2.7 \; V \leq V_{\text{DD}} \leq 3.6 \; \text{V}, \\ C_{\text{b}} = 50 \; \text{pF}, \; \text{R}_{\text{b}} = 2.7 \; \text{k}\Omega \end{array}$                       | 475                      |                   | 1150                      |                   | 1150                      |                 | 1150                      |                  | ns   |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{V}_{\mbox{DD}} \leq 3.6 \mbox{ V}, \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 3  k\Omega \end{array}$                              | -                        |                   |                           |                   |                           |                 |                           |                  |      |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{V}_{DD} < 2.7 \mbox{ V}, \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 5 \mbox{ k}\Omega \end{array}$                                 | -                        |                   | 1550                      |                   | 1550                      |                 | 1550                      |                  |      |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.7 \mbox{ V} \leq \mbox{V}_{DD} < 1.8 \mbox{ V}, \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 5  k\Omega \end{array}$                                        | _                        |                   | —                         |                   | —                         |                 | 1850                      |                  |      |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.6 \mbox{ V} \leq \mbox{V}_{DD} < 1.8 \mbox{ V}, \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 5 \mbox{ k}\Omega \end{array}$                                 | -                        |                   | _                         |                   | _                         |                 |                           |                  |      |

| Hold time<br>when SCLr = "H"     | tніgн    | $\begin{array}{l} 2.7 \; V \leq V_{DD} \leq 3.6 \; V, \\ C_{b} = 50 \; pF, \; R_{b} = 2.7 \; k\Omega \end{array}$                                                                        | 475                      |                   | 1150                      |                   | 1150                      |                 | 1150                      |                  | ns   |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{V}_{\mbox{DD}} \leq 3.6 \mbox{ V}, \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 3  k\Omega \end{array}$                              | -                        |                   |                           |                   |                           |                 |                           |                  |      |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{ V}_{\mbox{DD}} < 2.7 \mbox{ V}, \\ C_{\mbox{b}} = 100 \mbox{ pF}, \mbox{ R}_{\mbox{b}} = 5  k\Omega \end{array}$              | -                        |                   | 1550                      |                   | 1550                      |                 | 1550                      |                  |      |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.7 \mbox{ V} \leq \mbox{ V}_{\mbox{DD}} < 1.8 \mbox{ V}, \\ C_{\mbox{b}} = 100 \mbox{ pF}, \mbox{ R}_{\mbox{b}} = 5  k\Omega \end{array}$              | -                        |                   | -                         |                   | _                         |                 | 1850                      |                  |      |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.6 \mbox{ V} \leq \mbox{V}_{DD} < 1.8 \mbox{ V}, \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 5 \mbox{ k}\Omega \end{array}$                                 | -                        |                   | -                         |                   | _                         |                 |                           |                  |      |

| Data setup time<br>(reception)   | tsu: dat | $\begin{array}{l} 2.7 \ \text{V} \leq \text{V}_{\text{DD}} \leq 3.6 \ \text{V}, \\ C_{\text{b}} = 50 \ \text{pF}, \ \text{R}_{\text{b}} = 2.7 \ \text{k}\Omega \end{array}$              | 1/fмск<br>+ 85<br>Note 2 |                   | 1/fмск<br>+ 145<br>Note 2 |                   | 1/fмск<br>+ 145<br>Note 2 |                 | 1/fмск<br>+ 145<br>Note 2 |                  | ns   |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{V}_{\mbox{DD}} \leq 3.6 \mbox{ V}, \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 3  k\Omega \end{array}$                              | -                        |                   |                           |                   |                           |                 |                           |                  |      |

|                                  |          | $\label{eq:def-loss} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{V}_{DD} < 2.7 \mbox{ V}, \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 5  k\Omega \end{array}$                                   | -                        |                   | 1/fмск<br>+ 230<br>Note 2 |                   | 1/fмск<br>+ 230<br>Note 2 |                 | 1/fмск<br>+ 230<br>Note 2 |                  |      |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.7 \mbox{ V} \leq \mbox{V}_{DD} < 1.8 \mbox{ V}, \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 5 \mbox{ k}\Omega \end{array}$                                 | -                        |                   | -                         |                   | _                         |                 | 1/fмск<br>+ 290           |                  |      |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.6 \mbox{ V} \leq \mbox{V}_{DD} < 1.8 \mbox{ V}, \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 5 \mbox{ k}\Omega \end{array}$                                 | -                        |                   | -                         |                   | -                         |                 | Note 2                    |                  |      |

| Data hold time<br>(transmission) | thd: dat | $\label{eq:VDD} \begin{array}{l} 2.7 \mbox{ V} \leq \mbox{V}_{DD} \leq 3.6 \mbox{ V}, \\ C_b = 50 \mbox{ pF}, \mbox{ R}_b = 2.7 \mbox{ k}\Omega \end{array}$                             | 0                        | 305               | 0                         | 305               | 0                         | 305             | 0                         | 305              | ns   |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{V}_{DD} \leq 3.6 \mbox{ V}, \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 3  k\Omega \end{array}$                                     | -                        | -                 |                           | 355               |                           | 355             |                           | 355              |      |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.8 \mbox{ V} \leq \mbox{V}_{DD} < 2.7 \mbox{ V}, \\ C_b = 100 \mbox{ pF}, \mbox{ R}_b = 5 \mbox{ k}\Omega \end{array}$                                 | -                        | -                 |                           |                   |                           |                 |                           |                  |      |

|                                  |          | eq:def-def-def-def-def-def-def-def-def-def-                                                                                                                                              | —                        | _                 | -                         | _                 | —                         | -               |                           | 405              |      |

|                                  |          | $\label{eq:VDD} \begin{array}{l} 1.6 \text{ V} \leq \text{V}_{\text{DD}} < 1.8 \text{ V}, \\ \text{C}_{\text{b}} = 100 \text{ pF}, \text{ R}_{\text{b}} = 5 \text{ k}\Omega \end{array}$ | _                        | _                 | _                         | -                 | —                         | —               |                           |                  |      |

## (TA = -40 to +85°C, 1.6 V $\leq$ AVDD = VDD $\leq$ 3.6 V, Vss = AVss = 0 V)

(Notes and Caution are listed on the next page.)

#### (5) During communication at same potential (simplified I<sup>2</sup>C mode)

| Devenuenten                   | Or mark at | Que ditions                                                                                                                                               | HS (high-speed      | main) Mode | 1.1    |

|-------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|--------|

| Parameter                     | Symbol     | Conditions                                                                                                                                                | MIN.                | MAX.       | - Unit |

| SCLr clock frequency          | fscL       | $\label{eq:VDD} \begin{array}{l} 2.7 \mbox{ V} \leq \mbox{Vdd} \leq 3.6 \mbox{ V}, \\ C_b = 50 \mbox{ pF}, \mbox{ Rb} = 2.7 \mbox{ k}\Omega \end{array}$  |                     | 400 Note 1 | kHz    |

|                               |            | $\label{eq:VDD} \begin{array}{l} 2.4 \ V \leq V_{DD} \leq 3.6 \ V, \\ C_b = 100 \ pF, \ R_b = 3 \ k\Omega \end{array}$                                    |                     | 100 Note 1 | kHz    |

| Hold time when SCLr = "L"     | tLOW       | $\label{eq:VDD} \begin{array}{l} 2.7 \mbox{ V} \leq \mbox{Vdd} \leq 3.6 \mbox{ V}, \\ C_b = 50 \mbox{ pF}, \mbox{ Rb} = 2.7 \mbox{ k}\Omega \end{array}$  | 1200                |            | ns     |

|                               |            | $\label{eq:VDD} \begin{array}{l} 2.4 \ V \leq V_{DD} \leq 3.6 \ V, \\ C_b = 100 \ pF, \ R_b = 3 \ k\Omega \end{array}$                                    | 4600                |            | ns     |

| Hold time when SCLr = "H"     | tнigн      | $\label{eq:VDD} \begin{array}{l} 2.7 \mbox{ V} \leq \mbox{Vdd} \leq 3.6 \mbox{ V}, \\ C_b = 50 \mbox{ pF}, \mbox{ Rb} = 2.7 \mbox{ k}\Omega \end{array}$  | 1200                |            | ns     |

|                               |            | $\label{eq:VDD} \begin{array}{l} 2.4 \ V \leq V_{DD} \leq 3.6 \ V, \\ C_b = 100 \ pF, \ R_b = 3 \ k\Omega \end{array}$                                    | 4600                |            | ns     |

| Data setup time (reception)   | tsu: dat   | $\label{eq:VDD} \begin{array}{l} 2.7 \mbox{ V} \leq \mbox{Vdd} \leq 3.6 \mbox{ V}, \\ C_b = 50 \mbox{ pF}, \mbox{ Rb} = 2.7 \mbox{ k}\Omega \end{array}$  | 1/fмск + 220 Note 2 |            | ns     |

|                               |            | $\label{eq:VDD} \begin{array}{l} 2.4 \ V \leq V_{DD} \leq 3.6 \ V, \\ C_b = 100 \ pF, \ R_b = 3 \ k\Omega \end{array}$                                    | 1/fмск + 580 Note 2 |            | ns     |

| Data hold time (transmission) | thd: dat   | $\label{eq:VDD} \begin{array}{l} 2.7 \mbox{ V} \leq \mbox{Vdd} \leq 3.6 \mbox{ V}, \\ C_b = 50 \mbox{ pF}, \mbox{ R}_b = 2.7 \mbox{ k}\Omega \end{array}$ | 0                   | 770        | ns     |

|                               |            | $\label{eq:VDD} \begin{array}{l} 2.4 \ V \leq V_{DD} \leq 3.6 \ V, \\ C_b = 100 \ pF, \ R_b = 3 \ k\Omega \end{array}$                                    | 0                   | 1420       | ns     |

### (TA = +85 to +105°C, 2.4 V $\leq$ AVDD = VDD $\leq$ 3.6 V, Vss = AVss = 0 V)

**Note 1.** The value must also be equal to or less than fMCK/4.

**Note 2.** Set the fMCK value to keep the hold time of SCLr = "L" and SCLr = "H".

Caution Select the normal input buffer and the N-ch open drain output (VDD tolerance) mode for the SDAr pin and the normal output mode for the SCLr pin by using port input mode register g (PIMg) and port output mode register h (POMh).

#### (6) Communication at different potential (1.8 V, 2.5 V) (UART mode) (dedicated baud rate generator output)

| Parameter Symb   |  |           | Conditions                                                                                         |  | HS (high-speed main) Mode |      | LS (low-speed main) Mode |      | w-power<br>) mode    | LV (low-voltage<br>main) Mode |                      | Unit |

|------------------|--|-----------|----------------------------------------------------------------------------------------------------|--|---------------------------|------|--------------------------|------|----------------------|-------------------------------|----------------------|------|

|                  |  |           |                                                                                                    |  | MAX.                      | MIN. | MAX.                     | MIN. | MAX.                 | MIN.                          | MAX.                 |      |

| Transfer<br>rate |  | reception | $\begin{array}{l} 2.7 \ V \leq V_{DD} \leq 3.6 \ V, \\ 2.3 \ V \leq V_b \leq 2.7 \ V \end{array}$  |  | fмск/6<br>Note 1          |      | fмск/6<br>Note 1         |      | fмск/6<br>Note 1     |                               | fмск/6<br>Note 1     | bps  |

| Notes 1, 2       |  |           | Theoretical value of<br>the maximum transfer<br>rate<br>f <sub>MCK</sub> = f <sub>CLK</sub> Note 3 |  | 4.0                       |      | 1.3                      |      | 0.1                  |                               | 0.6                  | Mbps |

|                  |  |           | $\begin{array}{l} 1.8 \ V \leq V_{DD} < 3.3 \ V, \\ 1.6 \ V \leq V_b \leq 2.0 \ V \end{array}$     |  | fмск/6<br>Notes 1, 2      |      | fмск/6<br>Notes 1, 2     |      | fмск/6<br>Notes 1, 2 |                               | fмск/6<br>Notes 1, 2 | bps  |

|                  |  |           | Theoretical value of<br>the maximum transfer<br>rate<br>fMCK = fCLK Note 3                         |  | 4.0                       |      | 1.3                      |      | 0.1                  |                               | 0.6                  | Mbps |

#### (TA = -40 to +85°C, 1.8 V $\leq$ AVDD = VDD $\leq$ 3.6 V, VSS = AVSS = 0 V)

(1/2)

Note 1. Transfer rate in the SNOOZE mode is 4,800 bps only.

Note 2. Use it with  $V_{DD} \ge Vb$ .

$\label{eq:Note 3.} \qquad \mbox{The maximum operating frequencies of the CPU/peripheral hardware clock (fcLK) are:}$

$\begin{array}{ll} \text{HS (high-speed main) mode:} & 24 \ \text{MHz} \ (2.7 \ \text{V} \leq \text{V}\text{DD} \leq 3.6 \ \text{V}) \\ & 16 \ \text{MHz} \ (2.4 \ \text{V} \leq \text{V}\text{DD} \leq 3.6 \ \text{V}) \\ \text{LS (low-speed main) mode:} & 8 \ \text{MHz} \ (1.8 \ \text{V} \leq \text{V}\text{DD} \leq 3.6 \ \text{V}) \\ \text{LP (low-power main) mode:} & 1 \ \text{MHz} \ (1.8 \ \text{V} \leq \text{V}\text{DD} \leq 3.6 \ \text{V}) \\ \text{LV (low-voltage main) mode:} & 4 \ \text{MHz} \ (1.6 \ \text{V} \leq \text{V}\text{DD} \leq 3.6 \ \text{V}) \\ \end{array}$

Caution Select the TTL input buffer for the RxDq pin and the N-ch open drain output (VDD tolerance) mode for the TxDq pin by using port input mode register g (PIMg) and port output mode register g (POMg). For VIH and VIL, see the DC characteristics with TTL input buffer selected.

Remark 1. Vb[V]: Communication line voltage

- **Remark 2.** q: UART number (q = 0), g: PIM and POM number (g = 5)

- Remark 3. fMCK: Serial array unit operation clock frequency

(Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number,

n: Channel number (mn = 00, 01)

#### (6) Communication at different potential (1.8 V, 2.5 V) (UART mode) (dedicated baud rate generator output)

| Parameter                | Symbol |           | Conditions                                                                                  | HS (high- | HS (high-speed main) Mode |      |  |

|--------------------------|--------|-----------|---------------------------------------------------------------------------------------------|-----------|---------------------------|------|--|

| i didineter              | Gymbol |           | Conditions                                                                                  | MIN.      | MAX.                      | Unit |  |

| Transfer rate Notes 1, 2 |        | Reception | $ \begin{array}{l} V \leq V_{DD} \leq 3.6 \; V, \\ V \leq V_{b} \leq 2.7 \; V \end{array} $ |           | fмск/12 Note 1            | bps  |  |

|                          |        |           | Theoretical value of the maximum transfer rate $f_{MCK}$ = $f_{CLK}$ $^{Note\ 3}$           |           | 2.0                       | Mbps |  |

|                          |        |           | $ V \leq V_{DD} < 3.3 \text{ V}, \\ V \leq V_b \leq 2.0 \text{ V}  $                        |           | fMCK/12 Notes 1, 2        | bps  |  |

|                          |        |           | Theoretical value of the maximum transfer rate $f_{MCK}$ = $f_{CLK}$ $^{Note\;3}$           |           | 0.66                      | Mbps |  |

#### (TA = +85 to +105°C, 2.4 V $\leq$ AVDD = VDD $\leq$ 3.6 V, VSS = AVSS = 0 V)

(1/2)

Note 1. Transfer rate in the SNOOZE mode is 4,800 bps only.

**Note 2.** Use it with  $VDD \ge Vb$ .

$\label{eq:Note 3.} \qquad \mbox{The maximum operating frequencies of the CPU/peripheral hardware clock (fclk) are:}$

HS (high-speed main) mode: 24 MHz (2.7 V  $\leq$  VDD  $\leq$  3.6 V)

16 MHz (2.4 V  $\leq$  VDD  $\leq$  3.6 V)

- Caution Select the TTL input buffer for the RxDq pin and the N-ch open drain output (VDD tolerance) mode for the TxDq pin by using port input mode register g (PIMg) and port output mode register g (POMg). For VIH and VIL, see the DC characteristics with TTL input buffer selected.

- Remark 1. Vb[V]: Communication line voltage

- **Remark 2.** q: UART number (q = 0), g: PIM and POM numbers (g = 5)

- Remark 3. fMCK: Serial array unit operation clock frequency

(Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number, n: Channel number (mn = 00, 01)

(2/2)

# (8) Communication at different potential (1.8 V, 2.5 V) (CSI mode) (master mode, SCKp... internal clock output)

| Parameter Sym<br>bol               |       | Conditions                                                                                                                                                                                                                   |      | h-speed<br>Mode |      | v-speed<br>Mode | LP (Low-power<br>main) mode |      | LV (low-voltage main) Mode |      | Unit |

|------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|------|-----------------|-----------------------------|------|----------------------------|------|------|

|                                    |       |                                                                                                                                                                                                                              | MIN. | MAX.            | MIN. | MAX.            | MIN.                        | MAX. | MIN.                       | MAX. |      |

| SIp setup<br>time                  | tsıĸı | $\begin{array}{l} 2.7 \ V \leq V_{DD} \leq 3.6 \ V, \ 2.3 \ V \leq V_b \leq 2.7 \ V, \\ C_b = 30 \ pF, \ R_b = 2.7 \ k\Omega \end{array}$                                                                                    | 177  |                 | 479  |                 | 479                         |      | 479                        |      | ns   |

| (to SCKp↑)<br><sub>Note 1</sub>    |       | $\begin{array}{l} 1.8 \ V \leq V_{DD} < 3.3 \ V, \ 1.6 \ V \leq V_b \leq 2.0 \ V \ ^{Note \ 3}, \\ C_b = 30 \ pF, \ R_b = 5.5 \ k\Omega \end{array}$                                                                         | 479  |                 | 479  |                 | 479                         |      | 479                        |      | ns   |

| SIp hold time<br>(from SCKp↑)      | tksi1 | $\begin{array}{l} 2.7 \ V \leq V_{DD} \leq 3.6 \ V, \ 2.3 \ V \leq V_b \leq 2.7 \ V, \\ C_b = 30 \ pF, \ R_b = 2.7 \ k\Omega \end{array}$                                                                                    | 19   |                 | 19   |                 | 19                          |      | 19                         |      | ns   |

| Note 1                             |       | $\begin{array}{l} 1.8 \ V \leq V_{DD} < 3.3 \ V, \ 1.6 \ V \leq V_b \leq 2.0 \ V \ ^{Note \ 3}, \\ C_b = 30 \ pF, \ R_b = 5.5 \ k\Omega \end{array}$                                                                         | 19   |                 | 19   |                 | 19                          |      | 19                         |      | ns   |

| Delay time<br>from SCKp↓           | tkso1 | $\begin{array}{l} 2.7 \ V \leq V_{DD} \leq 3.6 \ V, \ 2.3 \ V \leq V_b \leq 2.7 \ V, \\ C_b = 30 \ pF, \ R_b = 2.7 \ k\Omega \end{array}$                                                                                    |      | 195             |      | 195             |                             | 195  |                            | 195  | ns   |

| to SOp<br>output <sup>Note 1</sup> |       | $\begin{array}{l} 1.8 \ V \leq V_{DD} < 3.3 \ V, \ 1.6 \ V \leq V_b \leq 2.0 \ V \ ^{Note \ 3}, \\ C_b = 30 \ pF, \ R_b = 5.5 \ k\Omega \end{array}$                                                                         |      | 483             |      | 483             |                             | 483  |                            | 483  | ns   |

| SIp setup<br>time                  | tsıĸı | $\begin{array}{l} 2.7 \ V \leq V_{DD} \leq 3.6 \ V, \ 2.3 \ V \leq V_b \leq 2.7 \ V, \\ C_b = 30 \ pF, \ R_b = 2.7 \ k\Omega \end{array}$                                                                                    | 44   |                 | 110  |                 | 110                         |      | 110                        |      | ns   |

| (to SCKp↓)<br>Note 2               |       | $\begin{array}{l} 1.8 \ V \leq V_{DD} < 3.3 \ V, \ 1.6 \ V \leq V_b \leq 2.0 \ V \ ^{Note \ 3}, \\ C_b = 30 \ pF, \ R_b = 5.5 \ k\Omega \end{array}$                                                                         | 110  |                 | 110  |                 | 110                         |      | 110                        |      | ns   |

| SIp hold time<br>(from SCKp↓)      | tksi1 | $\begin{array}{l} 2.7 \ V \leq V_{DD} \leq 3.6 \ V, \ 2.3 \ V \leq V_b \leq 2.7 \ V, \\ C_b = 30 \ pF, \ R_b = 2.7 \ k\Omega \end{array}$                                                                                    | 19   |                 | 19   |                 | 19                          |      | 19                         |      | ns   |

| Note 2                             |       | $\begin{array}{l} 1.8 \mbox{ V} \leq \mbox{V}_{DD} \mbox{ < } 3.3 \mbox{ V}, \ 1.6 \mbox{ V} \leq \mbox{V}_b \leq 2.0 \mbox{ V} \mbox{ Note } 3, \\ C_b \mbox{ = } 30 \mbox{ pF}, \ R_b \mbox{ = } 5.5   \Omega \end{array}$ | 19   |                 | 19   |                 | 19                          |      | 19                         |      | ns   |

| Delay time<br>from SCKp↑           | tkso1 | $\begin{array}{l} 2.7 \ V \leq V_{DD} \leq 3.6 \ V, \ 2.3 \ V \leq V_{b} \leq 2.7 \ V, \\ C_{b} = 30 \ pF, \ R_{b} = 2.7 \ k\Omega \end{array}$                                                                              |      | 25              |      | 25              |                             | 25   |                            | 25   | ns   |

| to SOp<br>output <sup>Note 2</sup> |       | $\begin{array}{l} 1.8 \ V \leq V_{DD} < 3.3 \ V, \ 1.6 \ V \leq V_b \leq 2.0 \ V \ \mbox{Note 3}, \\ C_b = 30 \ \mbox{pF}, \ R_b = 5.5 \ \mbox{k}\Omega \end{array}$                                                         |      | 25              |      | 25              |                             | 25   |                            | 25   | ns   |

#### (TA = -40 to +85°C, 1.8 V $\leq$ AVDD = VDD $\leq$ 3.6 V, Vss = AVss = 0 V)

Note 1. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.

**Note 2.** When DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

Note 3. Use it with  $V_{DD} \ge V_b$ .

Caution Select the TTL input buffer for the SIp pin and the N-ch open drain output (VDD tolerance) mode for the SOp pin and SCKp pin by using port input mode register g (PIMg) and port output mode register g (POMg). For VIH and VIL, see the DC characteristics with TTL input buffer selected.

(**Remarks** are listed on the next page.)

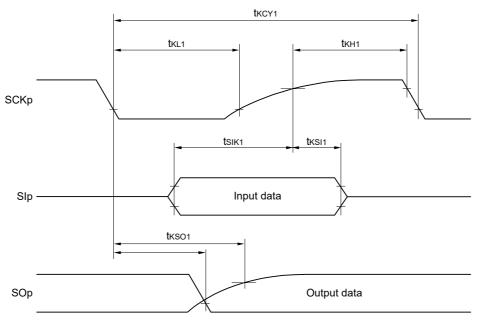

### CSI mode serial transfer timing (master mode) (during communication at different potential) (When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.)

CSI mode serial transfer timing (master mode) (during communication at different potential) (When DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.)

(7) When reference voltage (+) = AVDD (ADREFP1 = 0, ADREFP0 = 0), reference voltage (-) = AVss (ADREFM = 0), conversion target: ANI0 to ANI13

# (TA = +85 to +105°C, 2.4 V $\leq$ AVDD = VDD $\leq$ 3.6 V, Vss = 0 V, AVss = 0 V, Reference voltage (+) = AVDD, Reference voltage (-) = AVss = 0 V)

| Parameter                         | Symbol        | Conditions                      |                                                             | MIN.  | TYP. | MAX. | Unit |

|-----------------------------------|---------------|---------------------------------|-------------------------------------------------------------|-------|------|------|------|

| Resolution                        | Res           |                                 | $2.4~V \leq AV \text{DD} \leq 3.6~V$                        | 8     |      | 12   | bit  |

| Overall error Note                | AINL          | 12-bit resolution               | $2.4~\text{V} \leq \text{AV}\text{DD} \leq 3.6~\text{V}$    |       |      | ±7.5 | LSB  |

| Conversion time                   | <b>t</b> CONV | ADTYP = 0,<br>12-bit resolution | $2.4 \text{ V} \le \text{AV}_{\text{DD}} \le 3.6 \text{ V}$ | 3.375 |      |      | μs   |

| Zero-scale error Note             | Ezs           | 12-bit resolution               | $2.4~\text{V} \leq \text{AV}\text{DD} \leq 3.6~\text{V}$    |       |      | ±6.0 | LSB  |

| Full-scale error Note             | Efs           | 12-bit resolution               | $2.4~\text{V} \leq \text{AV}\text{DD} \leq 3.6~\text{V}$    |       |      | ±6.0 | LSB  |

| Integral linearity error Note     | ILE           | 12-bit resolution               | $2.4~\text{V} \leq \text{AV}\text{DD} \leq 3.6~\text{V}$    |       |      | ±3.0 | LSB  |

| Differential linearity error Note | DLE           | 12-bit resolution               | $2.4~\text{V} \leq \text{AV}\text{DD} \leq 3.6~\text{V}$    |       |      | ±2.0 | LSB  |

| Analog input voltage              | VAIN          |                                 | ÷                                                           | 0     |      | AVdd | V    |

**Note** Excludes quantization error ( $\pm 1/2$  LSB).

Caution Always use AVDD pin with the same potential as the VDD pin.

# (10) When reference voltage (+) = Internal reference voltage (1.45 V) (ADREFP1 = 1, ADREFP0 = 0), reference voltage (-) = AVss (ADREFM = 0), conversion target: ANI0 to ANI13, ANI16 to ANI18

(TA = +85 to +105°C, 2.4 V  $\leq$  VDD, 2.4 V  $\leq$  AVDD = VDD  $\leq$  3.6 V, Vss = 0 V, AVss = 0 V, Reference voltage (+) = internal reference voltage, Reference voltage (-) = AVss = 0 V)

| Parameter                         | Symbol | Conditions       | MIN. | TYP. | MAX. | Unit |

|-----------------------------------|--------|------------------|------|------|------|------|

| Resolution                        | Res    |                  |      | 8    |      | bit  |

| Conversion time                   | tCONV  | 8-bit resolution | 16.0 |      |      | μs   |

| Zero-scale error Note             | Ezs    | 8-bit resolution |      |      | ±4.0 | LSB  |

| Integral linearity error Note     | ILE    | 8-bit resolution |      |      | ±2.0 | LSB  |

| Differential linearity error Note | DLE    | 8-bit resolution |      |      | ±2.5 | LSB  |

| Analog input voltage              | Vain   |                  | 0    |      | Vbgr | V    |

**Note** Excludes quantization error (±1/2 LSB).

Caution Always use AVDD pin with the same potential as the VDD pin.

## 2.6.2 Temperature sensor, internal reference voltage output characteristics

| (TA = -40 to 85°C, 1.8 V $\leq$ AVDD = VDD $\leq$ 3.6 V, Vss = AVss = 0 V)  |

|-----------------------------------------------------------------------------|

| (TA = +85 to 105°C, 2.4 V $\leq$ AVDD = VDD $\leq$ 3.6 V, Vss = AVss = 0 V) |

| Parameter                         | Symbol  | conditions                                                        |      | TYP. | MAX. | Unit  |

|-----------------------------------|---------|-------------------------------------------------------------------|------|------|------|-------|

| Temperature sensor output voltage | VTMPS25 | Setting ADS register = 80H, TA = +25°C                            |      | 1.05 |      | V     |

| Internal reference voltage        | Vbgr    | Setting ADS register = 81H                                        | 1.38 | 1.45 | 1.50 | V     |

| Temperature coefficient           | FVTMPS  | Temperature sensor output voltage that depends on the temperature |      | -3.6 |      | mV/°C |

| Operation stabilization wait time | tamp    | $2.4 \text{ V} \leq \text{Vdd} \leq 3.6 \text{ V}$                | 5    |      |      | μs    |

|                                   |         | $1.8 \text{ V} \le \text{V}_{DD} \le 2.4 \text{ V}$               | 10   |      |      |       |

## 2.9 Dedicated Flash Memory Programmer Communication (UART)

(Ta = -40 to +85°C, 1.8 V  $\leq$  AVDD = VDD  $\leq$  3.6 V, Vss = AVss = 0 V)

| (TA = +85 to +105°C, 2.4 V $\leq$ AVDD = VDD $\leq$ 3.6 V, Vss = AVss = 0 V) |        |            |     |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------|--------|------------|-----|--|--|--|--|--|--|--|

| Paramotor                                                                    | Symbol | Conditions | MIN |  |  |  |  |  |  |  |

| Parameter     | Symbol | Conditions                | MIN.    | TYP. | MAX.      | Unit |

|---------------|--------|---------------------------|---------|------|-----------|------|

| Transfer rate |        | During serial programming | 115,200 |      | 1,000,000 | bps  |

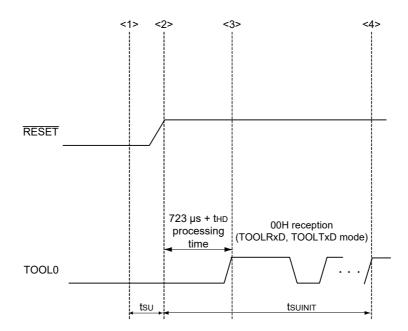

## 2.10 Timing of Entry to Flash Memory Programming Modes

(TA = -40 to +85°C, 1.8 V  $\leq$  AVDD = VDD  $\leq$  3.6 V, Vss = AVss = 0 V)

(TA = +85 to +105°C, 2.4 V  $\leq$  AVDD = VDD  $\leq$  3.6 V, Vss = AVss = 0 V)

| Parameter                                                                                                                                                                                    | Symbol  | Conditions                                                    | MIN. | TYP. | MAX. | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------|------|------|------|------|

| How long from when an external reset ends until the                                                                                                                                          | tsuinit | POR and LVD reset must end<br>before the external reset ends. |      |      | 100  | ms   |

| initial communication settings are specified Note 1                                                                                                                                          | tou     | POR and LVD reset must end                                    | 10   |      |      |      |

| How long from when the TOOL0 pin is placed at the low level until an external reset ends <sup>Note 1</sup>                                                                                   | tsu     | before the external reset ends.                               | 10   |      |      | μs   |

| How long the TOOL0 pin must be kept at the low<br>level after an external reset ends<br>(excluding the processing time of the firmware to<br>control the flash memory) <sup>Notes 1, 2</sup> | thd     | POR and LVD reset must end before the external reset ends.    | 1    |      |      | ms   |

Note 1. Deassertion of the POR and LVD reset signals must precede deassertion of the pin reset signal.

Note 2. This excludes the flash firmware processing time (723  $\mu$ s).

<1> The low level is input to the TOOL0 pin.

<2> The external reset ends (POR and LVD reset must end before the external reset ends).

<3> The TOOL0 pin is set to the high level.

<4> Setting of the flash memory programming mode by UART reception and complete the baud rate setting.

**Remark** tsuinit. The segment shows that it is necessary to finish specifying the initial communication settings within 100 ms from when the external resets end.

- tsu: How long from when the TOOL0 pin is placed at the low level until a pin reset ends

- tHD: How long to keep the TOOL0 pin at the low level from when the external resets end (excluding the processing time of the firmware to control the flash memory)

RENESAS

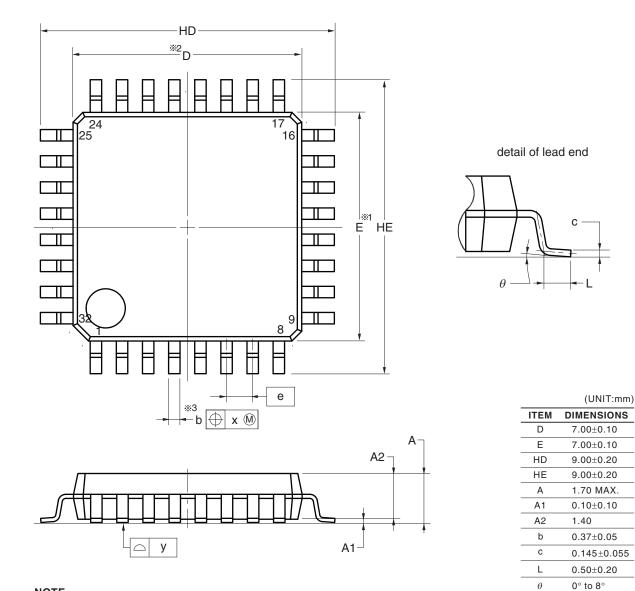

#### R5F117BAGFP, R5F117BCGFP

| JEITA Package Code | RENESAS Code | Previous Code  | MASS (TYP.) [g] |

|--------------------|--------------|----------------|-----------------|

| P-LQFP32-7x7-0.80  | PLQP0032GB-A | P32GA-80-GBT-1 | 0.2             |

#### NOTE

1.Dimensions "%1" and "%2" do not include mold flash.

2.Dimension "%3" does not include trim offset.

0.80

0.20

0.10

е

х

у