#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 2K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 20x10b; D/A 3x8b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 20-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/attiny3216-snr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# ATtiny3216 / ATtiny1616 Memories

#### 6.10.2.1 Device ID n

| Name:     | DEVICEIDn            |

|-----------|----------------------|

| Offset:   | 0x00 + n*0x01 [n=02] |

| Reset:    | [Device ID]          |

| Property: | -                    |

Each device has a device ID identifying the device and its properties; such as memory sizes, pin count, and die revision. This can be used to identify a device and hence, the available features by software. The Device ID consists of three bytes: SIGROW.DEVICEID[2:0].

| Bit    | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|---------------|---|---|---|---|---|---|---|

|        | DEVICEID[7:0] |   |   |   |   |   |   |   |

| Access | R             | R | R | R | R | R | R | R |

| Reset  | x             | x | x | x | x | x | x | x |

Bits 7:0 - DEVICEID[7:0] Byte n of the Device ID

# 7. Peripherals and Architecture

# 7.1 Peripheral Module Address Map

The address map shows the base address for each peripheral. For complete register description and summary for each peripheral module, refer to the respective module chapters.

| Base Address | Name    | Description                            |  |  |  |

|--------------|---------|----------------------------------------|--|--|--|

| 0x0000       | VPORTA  | Virtual Port A                         |  |  |  |

| 0x0004       | VPORTB  | Virtual Port B                         |  |  |  |

| 0x0008       | VPORTC  | Virtual Port C                         |  |  |  |

| 0x001C       | GPIO    | General Purpose I/O registers          |  |  |  |

| 0x0030       | CPU     | CPU                                    |  |  |  |

| 0x0040       | RSTCTRL | Reset Controller                       |  |  |  |

| 0x0050       | SLPCTRL | Sleep Controller                       |  |  |  |

| 0x0060       | CLKCTRL | Clock Controller                       |  |  |  |

| 0x0080       | BOD     | Brown-Out Detector                     |  |  |  |

| 0x00A0       | VREF    | Voltage Reference                      |  |  |  |

| 0x0100       | WDT     | Watchdog Timer                         |  |  |  |

| 0x0110       | CPUINT  | Interrupt Controller                   |  |  |  |

| 0x0120       | CRCSCAN | Cyclic Redundancy Check Memory Scan    |  |  |  |

| 0x0140       | RTC     | Real-Time Counter                      |  |  |  |

| 0x0180       | EVSYS   | Event System                           |  |  |  |

| 0x01C0       | CCL     | Configurable Custom Logic              |  |  |  |

| 0x0200       | PORTMUX | Port Multiplexer                       |  |  |  |

| 0x0400       | PORTA   | Port A Configuration                   |  |  |  |

| 0x0420       | PORTB   | Port B Configuration                   |  |  |  |

| 0x0440       | PORTC   | Port C Configuration                   |  |  |  |

| 0x0600       | ADC0    | Analog-to-Digital Converter            |  |  |  |

| 0x0640       | ADC1    | Analog-to-Digital Converter instance 1 |  |  |  |

| 0x0680       | AC0     | Analog Comparator 0                    |  |  |  |

| 0x0688       | AC1     | Analog Comparator 1                    |  |  |  |

| 0x0690       | AC2     | Analog Comparator 2                    |  |  |  |

Table 7-1. Peripheral Module Address Map

#### 9.5.2 Control B

|        | Name:<br>Offset:<br>Reset:<br>Property: | CTRLB<br>0x01<br>0x00<br>- |   |   |   |   |          |       |

|--------|-----------------------------------------|----------------------------|---|---|---|---|----------|-------|

| Bit    | 7                                       | 6                          | 5 | 4 | 3 | 2 | 1        | 0     |

|        |                                         |                            |   |   |   |   | BOOTLOCK | APCWP |

| Access |                                         |                            |   |   |   |   | R/W      | R/W   |

| Reset  |                                         |                            |   |   |   |   | 0        | 0     |

#### Bit 1 – BOOTLOCK Boot Section Lock

Writing a '1' to this bit locks the boot section from read and instruction fetch.

If this bit is '1', a read from the boot section will return '0'. A fetch from the boot section will also return '0' as instruction.

This bit can be written from the boot section only. It can only be cleared to '0' by a Reset.

This bit will take effect only when the boot section is left the first time after the bit is written.

Bit 0 – APCWP Application Code Section Write Protection

Writing a '1' to this bit protects the application code section from further writes.

This bit can only be written to '1'. It is cleared to '0' only by Reset.

#### 10.5.8 32 KHz Oscillator Control A

Name:OSC32KCTRLAOffset:0x18Reset:0x00Property:Configuration Change Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1        | 0 |

|--------|---|---|---|---|---|---|----------|---|

|        |   |   |   |   |   |   | RUNSTDBY |   |

| Access |   |   |   |   |   |   | R/W      |   |

| Reset  |   |   |   |   |   |   | 0        |   |

#### Bit 1 – RUNSTDBY Run Standby

This bit forces the oscillator ON in all modes, even when unused by the system. In Standby Sleep mode this can be used to ensure immediate wake-up and not waiting for the oscillator start-up time.

When not requested by peripherals, no oscillator output is provided.

It takes four oscillator cycles to open the clock gate after a request but the oscillator analog start-up time will be removed when this bit is set.

0

0

#### 16.5.9 Input Value

|        | Name:<br>Offset:<br>Reset:<br>Property: | IN<br>0x08<br>0x00<br>- |     |     |      |     |     |     |   |

|--------|-----------------------------------------|-------------------------|-----|-----|------|-----|-----|-----|---|

| Bit    | 7                                       | 6                       | 5   | 4   | 3    | 2   | 1   | 0   | _ |

|        |                                         |                         |     | IN[ | 7:0] |     |     |     |   |

| Access | R/W                                     | R/W                     | R/W | R/W | R/W  | R/W | R/W | R/W | _ |

#### Bits 7:0 – IN[7:0] Input Value

0

0

Reset

This register shows the value present on the pins if the digital input driver is enabled. IN[n] shows the value of pin n of the port. The input is not sampled and cannot be read if the digital input buffers are disabled.

0

0

0

Writing to a bit of PORT.IN will toggle the corresponding bit in PORT.OUT.

0

R/W

0

R/W

0

#### 16.5.10 Interrupt Flags

R/W

0

Access Reset

| Of<br>Re | me:<br>fset:<br>set:<br>operty: | INTFLAGS<br>0x09<br>0x00<br>- |   |     |       |   |   |   |

|----------|---------------------------------|-------------------------------|---|-----|-------|---|---|---|

| Bit      | 7                               | 6                             | 5 | 4   | 3     | 2 | 1 | 0 |

|          |                                 |                               |   | INT | [7:0] |   |   |   |

R/W

0

R/W

0

#### Bits 7:0 - INT[7:0] Interrupt Pin Flag

R/W

0

R/W

0

The INT Flag is set when a pin change/state matches the pin's input sense configuration. Writing a '1' to a flag's bit location will clear the flag.

R/W

0

For enabling and executing the interrupt, refer to ISC bit description in PORT.PINnCTRL.

When the Synchronize Update bit (SYNCUPD) in the Control A register (TCBn.CTRLA) is written to '1', the TCB counter will restart when the TCA counter restarts.

#### **Related Links**

21.2.1 Block Diagram

#### 21.3.4 Events

The TCB is an event generator. Any condition that causes the CAPT flag in TCBn.INTFLAGS to be set will also generate a one-cycle strobe on the event channel output.

The peripheral accepts one event input. If the Capture Event Input Enable bit (CAPTEI) in the Event Control register (TCBn.EVCTRL) is written to '1', incoming events will result in an event action as defined by the Event Edge bit (EDGE) in TCBn.EVCTRL. The event needs to last for at least one CLK\_PER cycle to ensure that it is recognized.

If the Asynchronous mode is enabled for Single-Shot mode, the event is edge triggered and will capture changes on the event input shorter than one system clock cycle.

#### **Related Links**

21.5.3 EVCTRL 14. EVSYS - Event System

#### 21.3.5 Interrupts

#### Table 21-4. Available Interrupt Vectors and Sources

| Offset | Name | Vector Description | Conditions                                                           |

|--------|------|--------------------|----------------------------------------------------------------------|

| 0x00   | CAPT | TCB interrupt      | Depending on operating mode. See description of CAPT in TCB.INTFLAG. |

When an interrupt condition occurs, the corresponding interrupt flag is set in the Interrupt Flags register of the peripheral (*peripheral*.INTFLAGS).

An interrupt source is enabled or disabled by writing to the corresponding enable bit in the peripheral's Interrupt Control register (*peripheral*.INTCTRL).

An interrupt request is generated when the corresponding interrupt source is enabled and the interrupt flag is set. The interrupt request remains active until the interrupt flag is cleared. See the peripheral's INTFLAGS register for details on how to clear interrupt flags.

#### **Related Links**

13. CPUINT - CPU Interrupt Controller 21.5.5 INTFLAGS

#### 21.3.6 Sleep Mode Operation

TCB will halt operation in the Power-Down Sleep mode. Standby sleep operation is dependent on the Run in Standby bit (RUNSTDBY) in the Control A register (TCB.CTRLA).

#### 21.3.7 Synchronization

Not applicable.

#### 21.3.8 Configuration Change Protection

Not applicable.

# ATtiny3216 / ATtiny1616

# TCD - 12-Bit Timer/Counter Type D

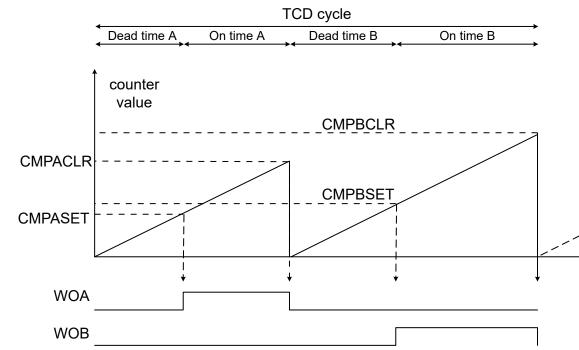

In the figure above, *CMPASET < CMPACLR and CMPBSET < CMPBCLR*. This causes the outputs to go high. There are no restrictions on the CMPASET/CLR compared to the CMPBSET/CLR values.

In Two Ramp mode, it is not possible to get overlapping outputs.

#### 22.3.2.3.3 Four Ramp Mode

In Four Ramp mode the TCD cycle is following this pattern:

- 1. A TCD cycle begins with the TCD counter counting up from zero until it reaches the CMPASET value, and resets to zero.

- 2. The Counter counts up from zero until it reaches the CMPACLR value, and resets to zero.

- 3. The Counter counts up from zero until it reaches the CMPBSET value, and resets to zero.

- 4. The Counter counts up from zero until it reaches the CMPBCLR value, and ends the TCD cycle by resetting to zero.

The TCD cycle period is given by:

Figure 22-5. Two Ramp Mode

$T_{\text{TCD}\_\text{cycle}} = \frac{(\text{CMPASET} + 1 + \text{CMPACLR} + 1 + \text{CMPBSET} + 1 + \text{CMPBCLR} + 1)}{f_{\text{CLK}\_\text{TCD}\_\text{CNT}}}$

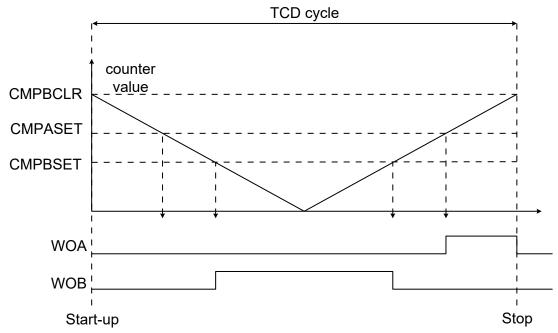

CMPACLR is not used in Dual Slope mode. Writing a value to CMPACLR has no effect.

When starting the TCD in Dual Slope mode, the TCD counter starts at the CMPBCLR value and counts down. The WOA will not be set before the end of the first TCD cycle.

Figure 22-8. Dual Slope Mode Starting and Stopping

### 22.3.2.4 TCD Inputs

The TCD has two inputs that are connected to the Event System, Input A and Input B. Each input has functionality that is connected to the corresponding output (WOA and WOB). That functionality is controlled by the Event Control x registers (TCDn.EVCTRLA and TCDn.EVCTRLB) and the Input Control x registers (TCDn.INPUTACTRL and TCDn.INPUTBCTRL).

To enable the input Events, write a '1' to the Trigger Event Input Enable bit (TRIGEI) in the Event Control register (TCDn.EVCTRLx). The inputs will be used as a fault detect and/or capture trigger. To enable capture trigger, write a '1' to the ACTION bit in Event Control register (TCDn.EVCTRLx).

There are ten different input modes for the fault detection. The two inputs have the same functionality, except for input blanking which is only supported by input A. Input blanking is configured by the Delay Control and Delay Value registers (TCDn.DLYCTRL and TCDn.DLYVAL).

The inputs are connected to the Event System. The connections between the event source and the TCD input must be configured in the Event System.

An overview of the input system is shown below.

# ATtiny3216 / ATtiny1616

## **USART - Universal Synchronous and Asynchrono...**

| Symbol            | Meaning                                                                                                |

|-------------------|--------------------------------------------------------------------------------------------------------|

| D                 | Sum of character size and parity size (D = 5 to 10 bit)                                                |

| R <sub>slow</sub> | The ratio of the slowest incoming data rate that can be accepted in relation to the receiver baud rate |

| R <sub>fast</sub> | The ratio of the fastest incoming data rate that can be accepted in relation to the receiver baud rate |

#### Table 24-5. Formula Nomenclature

The following tables list the maximum receiver baud rate error that can be tolerated. Normal Speed mode has higher toleration of baud rate variations.

# Table 24-6. Recommended Maximum Receiver Baud Rate Error for Normal Speed Mode (CLK2X =0)

| D #(Data + Parity Bit) | R <sub>slow</sub> [%] | R <sub>fast</sub> [%] | Maximum Total Error [%] | Receiver Max. Receiver<br>Error [%] |

|------------------------|-----------------------|-----------------------|-------------------------|-------------------------------------|

| 5                      | 93.20                 | 106.67                | +6.67/-6.80             | ±3.0                                |

| 6                      | 94.12                 | 105.79                | +5.79/-5.88             | ±2.5                                |

| 7                      | 94.81                 | 105.11                | +5.11/-5.19             | ±2.0                                |

| 8                      | 95.36                 | 104.58                | +4.58/-4.54             | ±2.0                                |

| 9                      | 95.81                 | 104.14                | +4.14/-4.19             | ±1.5                                |

| 10                     | 96.17                 | 103.78                | +3.78/-3.83             | ±1.5                                |

# Table 24-7. Recommended Maximum Receiver Baud Rate Error for Double Speed Mode (CLK2X =1)

| D #(Data + Parity Bit) | R <sub>slow</sub> [%] | R <sub>fast</sub> [%] | Maximum Total Error [%] | Receiver Max. Receiver<br>Error [%] |

|------------------------|-----------------------|-----------------------|-------------------------|-------------------------------------|

| 5                      | 94.12                 | 105.66                | +5.66/-5.88             | ±2.5                                |

| 6                      | 94.92                 | 104.92                | +4.92/-5.08             | ±2.0                                |

| 7                      | 95.52                 | 104.35                | +4.35/-4.48             | ±1.5                                |

| 8                      | 96.00                 | 103.90                | +3.90/-4.00             | ±1.5                                |

| 9                      | 96.39                 | 103.53                | +3.53/-3.61             | ±1.5                                |

| 10                     | 96.70                 | 103.23                | +3.23/-3.30             | ±1.0                                |

The recommendations of the maximum receiver baud rate error were made under the assumption that the receiver and transmitter equally divide the maximum total error.

#### 24.3.2.5 USART in Master SPI mode

Using the USART in Master SPI mode requires the transmitter to be enabled. The receiver can optionally be enabled to serve as the serial input. The XCK pin will be used as the transfer clock.

As for the USART, a data transfer is initiated by writing to the USARTn.DATA register. This is the case for both sending and receiving data since the transmitter controls the transfer clock. The data written to

#### 26.5.8 Master DATA

| Name:     | MDATA |

|-----------|-------|

| Offset:   | 0x08  |

| Reset:    | 0x00  |

| Property: | -     |

| Bit    | 7         | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|--------|-----------|-----|-----|-----|-----|-----|-----|-----|--|--|

|        | DATA[7:0] |     |     |     |     |     |     |     |  |  |

| Access | R/W       | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Reset  | 0         | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

#### Bits 7:0 – DATA[7:0] Data

The bit field gives direct access to the master's physical Shift register which is used both to shift data out onto the bus (write) and to shift in data received from the bus (read).

The direct access implies that the Data register cannot be accessed during byte transmissions. Built-in logic prevents any write access to this register during the shift operations. Reading valid data or writing data to be transmitted can only be successfully done when the bus clock (SCL) is held low by the master (i.e., when the CLKHOLD bit in the Master Status register (TWIn.MSTATUS) is set). However, it is not necessary to check the CLKHOLD bit in software before accessing this register if the software keeps track of the present protocol state by using interrupts or observing the interrupt flags.

Accessing this register assumes that the master clock hold is active, auto-triggers bus operations dependent of the state of the Acknowledge Action Command bit (ACKACT) in TWIn.MSTATUS and type of register access (read or write).

A write access to this register will, independent of ACKACT in TWIn.MSTATUS, command the master to perform a byte transmit operation on the bus directly followed by receiving the Acknowledge bit from the slave. When the Acknowledge bit is received, the Master Write Interrupt Flag (WIF) in TWIn.MSTATUS is set regardless of any bus errors or arbitration. If operating in a multi-master environment, the interrupt handler or application software must check the Arbitration Lost Status Flag (ARBLOST) in TWIn.MSTATUS before continuing from this point. If the arbitration was lost, the application software must decide to either abort or to resend the packet by rewriting this register. The entire operation is performed (i.e., all bits are clocked), regardless of winning or losing arbitration before the write interrupt flag is set. When arbitration is lost, only '1's are transmitted for the remainder of the operation, followed by a write interrupt with ARBLOST flag set.

Both TWI Master Interrupt Flags are cleared automatically when this register is written. However, the Master Arbitration Lost and Bus Error flags are left unchanged.

Reading this register triggers a bus operation, dependent on the setting of the Acknowledge Action Command bit (ACKACT) in TWIn.MSTATUS. Normally the ACKACT bit is preset to either ACK or NACK before the register read operation. If ACK or NACK action is selected, the transmission of the acknowledge bit precedes the release of the clock hold. The clock is released for one byte, allowing the slave to put one byte of data on the bus. The Master Read Interrupt flag RIF in TWIn.MSTATUS is then set if the procedure was successfully executed. However, if arbitration was lost when sending NACK, or a bus error occurred during the time of operation, the Master Write Interrupt flag (WIF) is set instead. Observe that the two Master Interrupt Flags are mutually exclusive (i.e., both flags will not be set simultaneously).

#### 28.2.3.1 Clocks

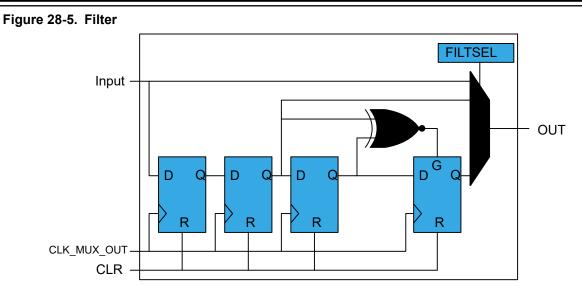

By default, the CCL is using the peripheral clock of the device (CLK\_PER).

Alternatively, the CCL can be clocked by a peripheral input that is available on LUT n input line 2 (LUTn\_IN[2]). This is configured by writing a '1' to the Clock Source Selection bit (CLKSRC) in the LUT n Control A register (CCL.LUTnCTRLA). The sequential block is clocked by the same clock as that of the even LUT in the LUT pair (SEQn.clk = LUT2n.clk). It is advised to disable the peripheral by writing a '0' to the Enable bit (ENABLE) in the Control A register (CCL.CTRLA) before configuring the CLKSRC bit in CCL.LUTnCTRLA.

Alternatively, the input line 2 (IN[2]) of an LUT can be used to clock the LUT and the corresponding Sequential block. This is enabled by writing a '1' to the Clock Source Selection bit (CLKSRC) in the LUT n Control A register (CCL.LUTnCTRLA).

The CCL must be disabled before changing the LUT clock source: write a '0' to the Enable bit (ENABLE) in Control A register (CCL.CTRLA).

#### **Related Links**

10. CLKCTRL - Clock Controller

#### 28.2.3.2 I/O Lines

The CCL can take inputs and generate output through I/O pins. For this to function properly, the I/O pins must be configured to be used by a Look Up Table (LUT).

#### **Related Links**

16. PORT - I/O Pin Configuration

#### 28.2.3.3 Interrupts

Using the interrupts of this peripheral requires the interrupt controller to be configured first.

#### 28.2.3.4 Debug Operation

When the CPU is halted in Debug mode the CCL continues normal operation. However, the CCL cannot be halted when the CPU is halted in Debug mode. If the CCL is configured in a way that requires it to be periodically serviced by the CPU, improper operation or data loss may result during debugging.

## 28.3 Functional Description

#### 28.3.1 Initialization

The following bits are enable-protected, meaning that they can only be written when the corresponding even LUT is disabled (ENABLE=0 in CCL.LUT0CTRLA):

• Sequential Selection (SEQSEL) in Sequential Control 0 register (CCL.SEQCTRL0)

The following registers are enable-protected, meaning that they can only be written when the corresponding LUT is disabled (ENABLE=0 in CCL.LUT0CTRLA):

• LUT n Control x register, except ENABLE bit (CCL.LUTnCTRLx)

Enable-protected bits in the CCL.LUTnCTRLx registers can be written at the same time as ENABLE in CCL.LUTnCTRLx is written to '1', but not at the same time as ENABLE is written to '0'.

Enable-protection is denoted by the enable-protected property in the register description.

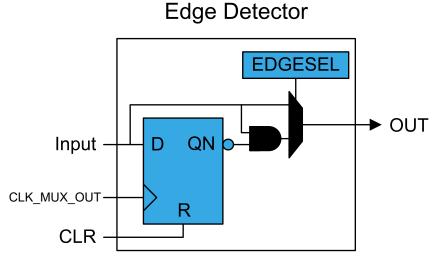

#### 28.3.2.5 Edge Detector

The edge detector can be used to generate a pulse when detecting a rising edge on its input. To detect a falling edge, the TRUTH table should be programmed to provide inverted output.

The edge detector is enabled by writing '1' to the Edge Selection bit (EDGEDET) in the LUT n Control A register (CCL.LUTnCTRLA). In order to avoid unpredictable behavior, a valid filter option must be enabled as well.

Edge detection is disabled by writing a '0' to EDGEDET in CCL.LUTnCTRLA. After disabling an LUT, the corresponding internal Edge Detector logic is cleared one clock cycle later.

#### Figure 28-6. Edge Detector

#### 28.3.2.6 Sequential Logic

Each LUT pair can be connected to an internal Sequential block. A Sequential block can function as either D flip-flop, JK flip-flop, gated D-latch, or RS-latch. The function is selected by writing the Sequential Selection bits (SEQSEL) in the Sequential Control register (CCL.SEQCTRLn).

The Sequential block receives its input from either LUT, filter, or edge detector, depending on the configuration.

#### 29.2.3.2 I/O Lines and Connections

I/O pins AINN0-AINN1 and AINP0- AINP3 are all analog inputs to the AC.

For correct operation, the pins must be configured in the port and port multiplexing peripherals.

It is recommended to disable the GPIO input when using the AC.

#### 29.2.3.3 Interrupts

Using the interrupts of this peripheral requires the interrupt controller to be configured first.

#### 29.2.3.4 Events

The events of this peripheral are connected to the Event System.

#### 29.2.3.5 Debug Operation

This peripheral is unaffected by entering Debug mode.

If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during halted debugging.

### 29.3 Functional Description

#### 29.3.1 Initialization

For basic operation, follow these steps:

- Configure the desired input pins in the port peripheral

- Select the positive and negative input sources by writing the Positive and Negative Input MUX Selection bit fields (MUXPOS and MUXNEG) in the MUX Control A register (AC.MUXCTRLA)

- Optional: Enable the output to pin by writing a '1' to the Output Pad Enable bit (OUTEN) in the Control A register (AC.CTRLA)

- Enable the AC by writing a '1' to the ENABLE bit in AC.CTRLA

During the start-up time after enabling the AC, the output of the AC may be invalid.

The start-up time of the AC by itself is at most 2.5 µs. If an internal reference is used, the reference startup time is normally longer than the AC start-up time. The VREF start-up time is 60 µs at most.

#### 29.3.2 Operation

#### 29.3.2.1 Input Hysteresis

Applying an input hysteresis helps to prevent constant toggling of the output when the noise-afflicted input signals are close to each other.

The input hysteresis can either be disabled or have one of three levels. The hysteresis is configured by writing to the Hysteresis Mode Select bit field (HYSMODE) in the Control A register (ACn.CTRLA).

#### 29.3.2.2 Input Sources

The AC has one positive and one negative input. The inputs can be pins and internal sources, such as a voltage reference.

Each input is selected by writing to the Positive and Negative Input MUX Selection bit field (MUXPOS and MUXNEG) in the MUX Control A register (AC.MUXTRLA).

#### 29.3.2.2.1 Pin Inputs

The following Analog input pins on the port can be selected as input to the analog comparator:

AINN0

#### 30.5.14 Result

| Name:     | RES  |

|-----------|------|

| Offset:   | 0x10 |

| Reset:    | 0x00 |

| Property: | -    |

The ADCn.RESL and ADCn.RESH register pair represents the 16-bit value, ADCn.RES. The low byte [7:0] (suffix L) is accessible at the original offset. The high byte [15:8] (suffix H) can be accessed at offset + 0x01.

If the analog input is higher than the reference level of the ADC, the 10-bit ADC result will be equal the maximum value of 0x3FF. Likewise, if the input is below 0V, the ADC result will be 0x000. As the ADC cannot produce a result above 0x3FF values, the accumulated value will never exceed 0xFFC0 even after the maximum allowed 64 accumulations.

| Bit    | 15        | 14 | 13 | 12 | 11 | 10 | 9 | 8 |  |  |  |

|--------|-----------|----|----|----|----|----|---|---|--|--|--|

|        | RES[15:8] |    |    |    |    |    |   |   |  |  |  |

| Access | R         | R  | R  | R  | R  | R  | R | R |  |  |  |

| Reset  | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0 |  |  |  |

|        |           |    |    |    |    |    |   |   |  |  |  |

| Bit    | 7         | 6  | 5  | 4  | 3  | 2  | 1 | 0 |  |  |  |

|        | RES[7:0]  |    |    |    |    |    |   |   |  |  |  |

| Access | R         | R  | R  | R  | R  | R  | R | R |  |  |  |

| Reset  | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0 |  |  |  |

|        |           |    |    |    |    |    |   |   |  |  |  |

#### Bits 15:8 - RES[15:8] Result high byte

These bits constitute the MSB of the ADCn.RES register, where the MSb is RES[15]. The ADC itself has a 10-bit output, ADC[9:0], where the MSb is ADC[9]. The data format in ADC and Digital Accumulation is 1's complement, where 0x0000 represents the '0' and 0xFFFF represents the largest number (full scale).

#### Bits 7:0 – RES[7:0] Result low byte

These bits constitute the LSB of ADC/Accumulator Result, (ADCn.RES) register. The data format in ADC and Digital Accumulation is 1's complement, where 0x0000 represents the '0' and 0xFFFF represents the largest number (full scale).

# 31.4 Register Summary - DAC

| Offset | Name  | Bit Pos. |           |       |  |  |  |  |        |

|--------|-------|----------|-----------|-------|--|--|--|--|--------|

| 0x00   | CTRLA | 7:0      | RUNSTDBY  | OUTEN |  |  |  |  | ENABLE |

| 0x01   | DATA  | 7:0      | DATA[7:0] |       |  |  |  |  |        |

# 31.5 Register Description

# 32. Peripheral Touch Controller (PTC)

## 32.1 Overview

The Peripheral Touch Controller (PTC) acquires signals in order to detect a touch on the capacitive sensors. The external capacitive touch sensor is typically formed on a PCB, and the sensor electrodes are connected to the analog front end of the PTC through the I/O pins in the device. The PTC supports both self and mutual capacitance sensors.

In the Mutual Capacitance mode, sensing is done using capacitive touch matrices in various X-Y configurations, including indium tin oxide (ITO) sensor grids. The PTC requires one pin per X-line and one pin per Y-line.

In the Self Capacitance mode, the PTC requires only one pin (Y-line) for each touch sensor.

The number of available pins and the assignment of X- and Y-lines is depending on both package type and device configuration. Refer to the Configuration Summary and I/O Multiplexing table for details.

#### **Related Links**

1.1 Configuration Summary

5. I/O Multiplexing and Considerations

## 32.2 Features

- Low-Power, High-Sensitivity, Environmentally Robust Capacitive Touch Buttons, Sliders, and Wheels

- Supports Wake-up on Touch from power-save Sleep mode

- Supports Mutual Capacitance and Self Capacitance Sensing

- Mix-and-Match Mutual and Self Capacitance Sensors

- One Pin per Electrode No External Components

- Load Compensating Charge Sensing

- Parasitic capacitance compensation and adjustable gain for superior sensitivity

- Zero Drift Over the Temperature and V<sub>DD</sub> Range

- Auto calibration and recalibration of sensors

- Single-shot and free-running Charge Measurement

- Hardware Noise Filtering and Noise Signal Desynchronization for High Conducted Immunity

- Driven Shield for Better Noise Immunity and Moisture Tolerance

- Any PTC X/Y line can be used for the driven shield

- All enabled sensors will be driven at the same potential as the sensor scanned

- Selectable channel change delay allows choosing the settling time on a new channel, as required

- Acquisition-start triggered by command or through auto-triggering feature

- Low CPU utilization through interrupt on acquisition-complete

- Using ADC peripheral for signal conversion and acquisition

#### **Related Links**

- 1.1 Configuration Summary

- 5. I/O Multiplexing and Considerations

#### 33.3.1.1 UPDI UART

All transmission and reception of serial data on the UPDI is achieved using the UPDI frames presented in Figure 33-3. Communication is initiated from the master (debugger) side, and every transmission must start with a SYNCH character upon which the UPDI can recover the transmission baud rate, and store this setting for the coming data. The baud rate set by the SYNCH character will be used for both reception and transmission for the instruction byte received after the SYNCH. See 33.3.3 UPDI Instruction Set for details on when the next SYNCH character is expected in the instruction stream.

There is no writable baud rate register in the UPDI, so the baud rate sampled from the SYNCH character is used for data recovery by sampling the Start bit, and performing a majority vote on the middle samples. This process is repeated for all bits in the frame, including the parity bit and two Stop bits. The baud generator uses 16 samples, and the majority voting is done on sample 7, 8, and 9. **Figure 33-4. UPDI UART Start Bit and Data/Parity/Stop Bit Sampling**

RxD

IDLE

START

BIT 0

Sample

$\uparrow$   $\uparrow$  <th

The transmission baud rate must be set up in relation to the selected UPDI clock, which can be adjusted by UPDICLKSEL in UPDI.ASI\_CTRLA. See Table 33-2 for recommended maximum and minimum baud rate settings.

#### Table 33-2. Recommended UART Baud Rate Based on UPDICLKSEL Setting

| UPDICLKSEL[1:0]       | MAX Recommended Baud Rate | MIN Recommended Baud Rate |

|-----------------------|---------------------------|---------------------------|

| 0x1 (16 MHz)          | 0.9 Mbps                  | 0.300 kbps                |

| 0x2 (8 MHz)           | 450 kbps                  | 0.150 kbps                |

| 0x3 (4 MHz) - Default | 225 kbps                  | 0.075 kbps                |

The UPDI Baud Rate Generator utilizes fractional baud counting to minimize the transmission error. With the fixed frame format used by the UPDI, the maximum and recommended receiver transmission error limits can be seen in the following table:

#### Table 33-3. Receiver Baud Rate Error

| Data + Parity Bits | R <sub>slow</sub> | R <sub>fast</sub> |             | Recommended<br>Max. RX Error [%] |

|--------------------|-------------------|-------------------|-------------|----------------------------------|

| 9                  | 96.39             | 104.76            | +4.76/-3.61 | +1.5/-1.5                        |

### 33.3.1.2 BREAK Character

The BREAK character is used to reset the internal state of the UPDI to the default setting. This is useful if the UPDI enters an error state due to a communication error, or when the synchronization between the debugger and the UPDI is lost.

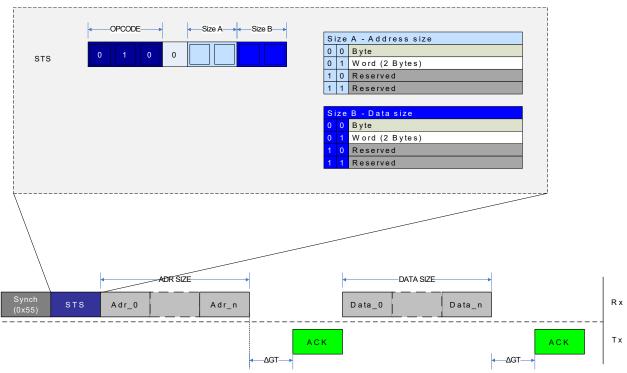

#### Figure 33-10. STS Instruction Operation

The transfer protocol for an STS instruction is depicted in the figure as well, following this sequence:

- 1. The address is sent.

- 2. An Acknowledge (ACK) is sent back from the UPDI if the transfer was successful.

- 3. The number of bytes as specified in the STS instruction is sent.

- 4. A new ACK is received after the data has been successfully transferred.

#### 33.3.3.3 LD - Load Data from Data Space Using Indirect Addressing

The LD instruction is used to load data from the bus matrix and into the serial shift register for serial readout. The LD instruction is based on indirect addressing, which means that the Address Pointer in the UPDI needs to be written prior to bus matrix access. Automatic pointer post-increment operation is supported and is useful when the LD instruction is used with REPEAT. It is also possible to do an LD of the UPDI Pointer register. The maximum supported size for address and data load is 16 bits.

#### 33.5.1 Status A

| Name:     | STATUSA |

|-----------|---------|

| Offset:   | 0x00    |

| Reset:    | 0x10    |

| Property: | -       |

| Bit    | 7 | 6      | 5       | 4 | 3 | 2 | 1 | 0 |

|--------|---|--------|---------|---|---|---|---|---|

|        |   | UPDIRI | EV[3:0] |   |   |   |   |   |

| Access | R | R      | R       | R |   |   |   |   |

| Reset  | 0 | 0      | 0       | 1 |   |   |   |   |

## Bits 7:4 - UPDIREV[3:0] UPDI Revision

These bits are read-only and contain the revision of the current UPDI implementation.