#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HC08                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | SCI, SPI                                                                |

| Peripherals                | LVD, POR, PWM                                                           |

| Number of I/O              | 21                                                                      |

| Program Memory Size        | 7.5KB (7.5K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 384 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 6x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-LQFP                                                                 |

| Supplier Device Package    | 32-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchc908gr8amfae |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Chapter 1 General Description

## 1.1 Introduction

The MC68HC908GR8A is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

This document also describes the MC68HC908GR4A. The MC68HC908GR4A is a device identical to the MC68HC908GR8A except that it has less FLASH memory. Only when there are differences from the MC68HC908GR8A is the MC68HC908GR4A specifically mentioned in the text.

## 1.2 Features

For convenience, features have been organized to reflect:

- Standard features

- Features of the CPU08

### 1.2.1 Standard Features

Features include:

- High-performance M68HC08 architecture optimized for C-compilers

- Fully upward-compatible object code with M6805, M146805, and M68HC05 Families

- 8-MHz internal bus frequency

- Clock generation module supporting 1-MHz to 8-MHz crystals

- FLASH program memory security<sup>(1)</sup>

- On-chip programming firmware for use with host personal computer which does not require high voltage for entry

- In-system programming (ISP)

- System protection features:

- Optional computer operating properly (COP) reset

- Low-voltage detection with optional reset and selectable trip points for 3.0-V and 5.0-V operation

- Illegal opcode detection with reset

- Illegal address detection with reset

- Low-power design; fully static with stop and wait modes

- Standard low-power modes of operation:

- Wait mode

- Stop mode

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

General Description

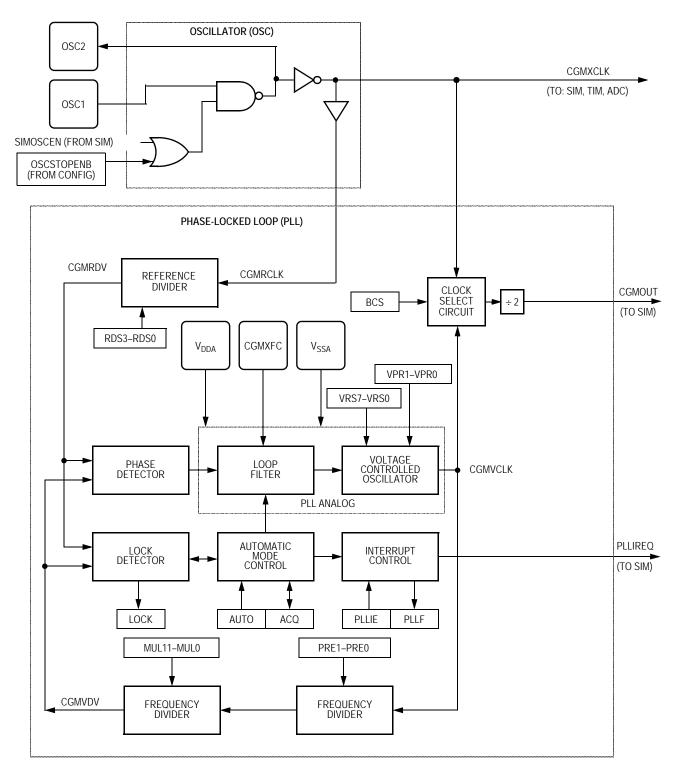

## 1.5.5 CGM Power Supply Pins ( $V_{DDA}$ and $V_{SSA}$ )

$V_{DDA}$  and  $V_{SSA}$  are the power supply pins for the analog portion of the clock generator module (CGM). Decoupling of these pins should be as per the digital supply. See Chapter 4 Clock Generator Module (CGM).

## 1.5.6 External Filter Capacitor Pin (V<sub>CGMXFC</sub>)

CGMXFC is an external filter capacitor connection for the CGM. See Chapter 4 Clock Generator Module (CGM).

## 1.5.7 ADC Power Supply/Reference Pins ( $V_{DDAD}/V_{REFH}$ and $V_{SSAD}/V_{REFL}$ )

$V_{DDAD}$  and  $V_{SSAD}$  are the power supply pins to the analog-to-digital converter (ADC).  $V_{REFH}$  and  $V_{REFL}$  are the reference voltage pins for the ADC.  $V_{REFH}$  is the high reference supply for the ADC, and by default the  $V_{DDAD}/V_{REFH}$  pin should be externally filtered and connected to the same voltage potential as  $V_{DD}$ .  $V_{REFL}$  is the low reference supply for the ADC, and by default the  $V_{SSAD}/V_{REFL}$  pin should be connected to the same voltage potential as  $V_{SS}$ . See Chapter 3 Analog-to-Digital Converter (ADC).

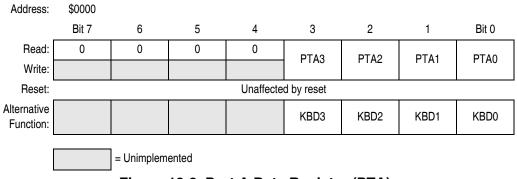

## 1.5.8 Port A Input/Output (I/O) Pins (PTA3/KBD3–PTA0/KBD0)

PTA3–PTA0 are special-function, bidirectional I/O port pins. Any or all of the port A pins can be programmed to serve as keyboard interrupt pins. See Chapter 12 Input/Output (I/O) Ports and Chapter 9 Keyboard Interrupt Module (KBI).

These port pins also have selectable pullups when configured for input mode. The pullups are disengaged when configured for output mode. The pullups are selectable on an individual port bit basis.

## 1.5.9 Port B I/O Pins (PTB5/AD5-PTB0/AD0)

PTB5–PTB0 are special-function, bidirectional I/O port pins that can also be used for analog-to-digital converter (ADC) inputs. See Chapter 12 Input/Output (I/O) Ports and Chapter 3 Analog-to-Digital Converter (ADC).

## 1.5.10 Port C I/O Pins (PTC1 and PTC0)

PTC1 and PTC0 are general-purpose, bidirectional I/O port pins. PTC1–PTC0 are only available on the 32-pin LQFP package. See Chapter 12 Input/Output (I/O) Ports.

These port pins also have selectable pullups when configured for input mode. The pullups are disengaged when configured for output mode. The pullups are selectable on an individual port bit basis.

## 1.5.11 Port D I/O Pins (PTD6/T2CH0-PTD0/SS)

PTD6–PTD0 are special-function, bidirectional I/O port pins. PTD3–PTD0 can be programmed to be serial peripheral interface (SPI) pins, while PTD6–PTD4 can be individually programmed to be timer interface module (TIM1 and TIM2) pins. See Chapter 17 Timer Interface Module (TIM1 and TIM2), Chapter 15 Serial Peripheral Interface (SPI) Module, and Chapter 12 Input/Output (I/O) Ports.

These port pins also have selectable pullups when configured for input mode. The pullups are disengaged when configured for output mode. The pullups are selectable on an individual port bit basis.

### 1.5.12 Port E I/O Pins (PTE1/RxD and PTE0/TxD)

PTE1 and PTE0 are special-function, bidirectional I/O port pins. These pins can also be programmed to be serial communications interface (SCI) pins. See Chapter 13 Serial Communications Interface (SCI) Module and Chapter 12 Input/Output (I/O) Ports.

### NOTE

Any unused inputs and I/O ports should be tied to an appropriate logic level (either  $V_{DD}$  or  $V_{SS}$ ). Although the I/O ports of the MC68HC908GR8A do not require termination, termination is recommended to reduce the possibility of static damage.

NP,

Memory

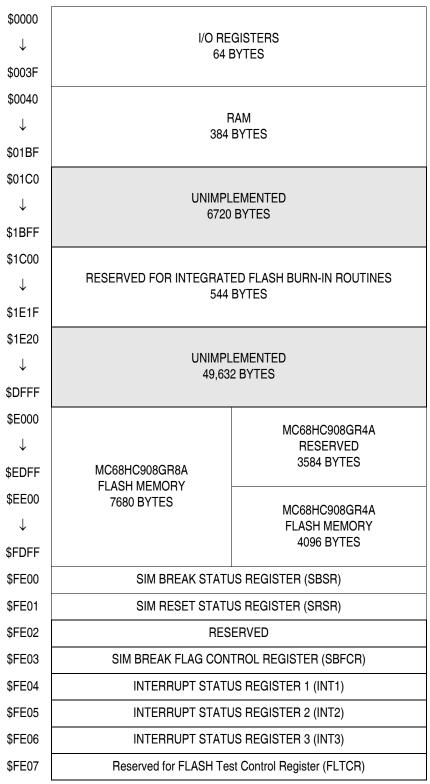

Figure 2-1. Memory Map

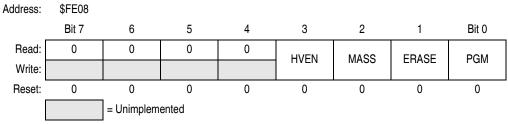

### 2.6.2 FLASH Control Register

The FLASH control register (FLCR) controls FLASH program and erase operations.

Figure 2-3. FLASH Control Register (FLCR)

#### HVEN — High-Voltage Enable Bit

This read/write bit enables the charge pump to drive high voltages for program and erase operations in the array. HVEN can only be set if either PGM = 1 or ERASE = 1 and the proper sequence for program or erase is followed.

1 = High voltage enabled to array and charge pump on

0 = High voltage disabled to array and charge pump off

#### MASS — Mass Erase Control Bit

Setting this read/write bit configures the FLASH array for mass erase operation.

1 = MASS erase operation selected

0 = PAGE erase operation selected

#### **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Erase operation selected

- 0 = Erase operation unselected

#### PGM — Program Control Bit

This read/write bit configures the memory for program operation. PGM is interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Program operation selected

- 0 = Program operation unselected

#### Analog-to-Digital Converter (ADC)

1. Ports are software configurable with pullup device if input port.

2. Higher current drive port pins

3. Pin contains integrated pullup device

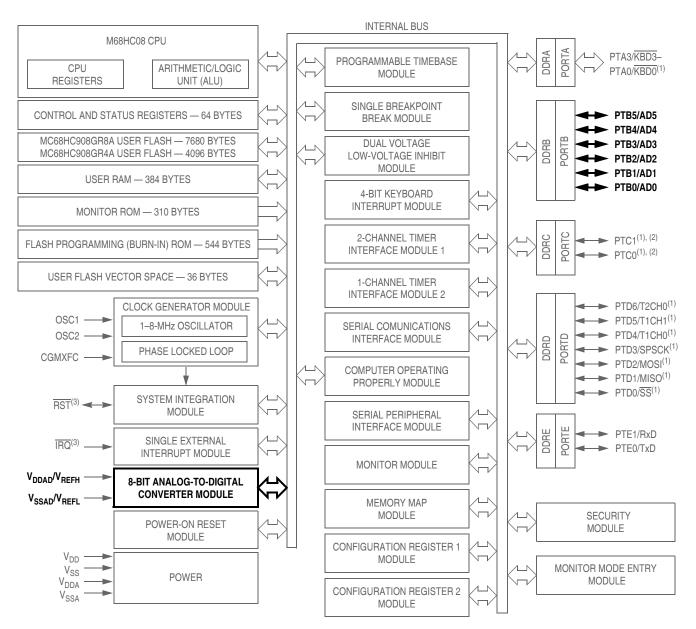

### Figure 3-1. Block Diagram Highlighting ADC Block and Pins

#### **Clock Generator Module (CGM)**

Figure 4-1. CGM Block Diagram

# 8.4 IRQ Pin

A falling edge on the IRQ pin can latch an interrupt request into the IRQ latch. A vector fetch, software clear, or reset clears the IRQ latch.

If the MODE bit is set, the IRQ pin is both falling-edge-sensitive and low-level sensitive. With MODE set, both of the following actions must occur to clear IRQ:

- Vector fetch or software clear A vector fetch generates an interrupt acknowledge signal to clear the latch. Software may generate the interrupt acknowledge signal by writing a 1 to the ACK bit in the interrupt status and control register (INTSCR). The ACK bit is useful in applications that poll the IRQ pin and require software to clear the IRQ latch. Writing to the ACK bit prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACK does not affect subsequent transitions on the IRQ pin. A falling edge that occurs after writing to the ACK bit latches another interrupt request. If the IRQ mask bit, IMASK, is clear, the CPU loads the program counter with the vector address at locations \$FFFA and \$FFFB.

- Return of the  $\overline{IRQ}$  pin to a high level As long as the  $\overline{IRQ}$  pin is low, IRQ remains active.

The vector fetch or software clear and the return of the IRQ pin to a high level may occur in any order. The interrupt request remains pending as long as the IRQ pin is low. A reset will clear the latch and the MODE control bit, thereby clearing the interrupt even if the pin stays low.

If the MODE bit is clear, the IRQ pin is falling-edge-sensitive only. With MODE clear, a vector fetch or software clear immediately clears the IRQ latch.

The IRQF bit in the INTSCR register can be used to check for pending interrupts. The IRQF bit is not affected by the IMASK bit, which makes it useful in applications where polling is preferred.

Use the BIH or BIL instruction to read the logic level on the  $\overline{IRQ}$  pin.

NOTE

When using the level-sensitive interrupt trigger, avoid false interrupts by masking interrupt requests in the interrupt routine.

## 8.5 IRQ Module During Break Interrupts

The BCFE bit in the SIM break flag control register (SBFCR) enables software to clear the latch during the break state. See Chapter 18 Development Support.

To allow software to clear the IRQ latch during a break interrupt, write a 1 to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect CPU interrupt flags during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), writing to the ACK bit in the IRQ status and control register during the break state has no effect on the IRQ interrupt flags.

| Port Bit DDR Module Control Pin |   |       |               |             |            |         |

|---------------------------------|---|-------|---------------|-------------|------------|---------|

| FUIL                            |   |       |               |             |            |         |

|                                 | 0 | DDRA0 | KBD           | KBIE0       | PTA0/KBD0  |         |

| А                               | 1 | DDRA1 |               | KBIE1       | PTA1/KBD1  |         |

|                                 | 2 | DDRA2 |               | KBIE2       | PTA2/KBD2  |         |

|                                 | 3 | DDRA3 |               | KBIE3       | PTA3/KBD3  |         |

|                                 | 0 | DDRB0 |               | ADCH4:0     | PTB0/AD0   |         |

|                                 | 1 | DDRB1 |               | ADCH4:0     | PTB1/AD1   |         |

| В                               | 2 | DDRB2 | ADC           | ADCH4:0     | PTB2/AD2   |         |

| D                               | 3 | DDRB3 | ADO           | ADCH4:0     | PTB3/AD3   |         |

|                                 | 4 | DDRB4 |               | ADCH4:0     | PTB4/AD4   |         |

|                                 | 5 | DDRB5 |               | ADCH4:0     | PTB5/AD5   |         |

| С                               | 0 | DDRC0 |               |             | PTC0       |         |

| C                               | 1 | DDRC1 |               |             | PTC1       |         |

|                                 | 0 | DDRD0 | SPI           |             |            | PTD0/SS |

|                                 | 1 | DDRD1 |               | SPE         | PTD1/MISO  |         |

|                                 | 2 | DDRD2 |               |             | PTD2/MOSI  |         |

| D                               | 3 | DDRD3 |               |             | PTD3/SPSCK |         |

|                                 | 4 | DDRD4 | <b>TIN 44</b> | ELS0B:ELS0A | PTD4/T1CH0 |         |

| -                               | 5 | DDRD5 | TIM1          | ELS1B:ELS1A | PTD5/T1CH1 |         |

|                                 | 6 | DDRD6 | TIM2          | ELS0B:ELS0A | PTD6/T2CH0 |         |

| Е                               | 0 | DDRE0 |               |             | PTE0/TxD   |         |

| E                               | 1 | DDRE1 | SCI           | ENSCI       | PTE1/RxD   |         |

Table 12-1. Port Control Register Bits Summary

## 12.2 Port A

Port A is an 4-bit special-function port that shares all four of its pins with the keyboard interrupt (KBI) module. Port A also has software configurable pullup devices if configured as an input port.

### 12.2.1 Port A Data Register

The port A data register (PTA) contains a data latch for each of the four port A pins.

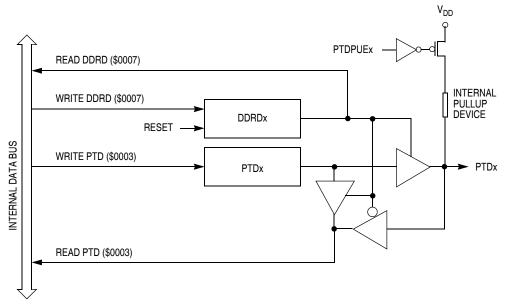

Figure 12-15 shows the port D I/O logic.

When bit DDRDx is a 1, reading address \$0003 reads the PTDx data latch. When bit DDRDx is a 0, reading address \$0003 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 12-5 summarizes the operation of the port D pins.

| Table | 12-5. | Port D | Pin | Functions |

|-------|-------|--------|-----|-----------|

|-------|-------|--------|-----|-----------|

| PTDPUE | DDRD<br>Bit | PTD              | I/O Pin                               | Accesses to DDRD | Access    | es to PTD                |

|--------|-------------|------------------|---------------------------------------|------------------|-----------|--------------------------|

| Bit    |             | Bit              | Mode                                  | Read/Write       | Read      | Write                    |

| 1      | 0           | X <sup>(1)</sup> | Input, V <sub>DD</sub> <sup>(2)</sup> | DDRD6-DDRD0      | Pin       | PTD6–PTD0 <sup>(3)</sup> |

| 0      | 0           | Х                | Input, Hi-Z <sup>(4)</sup>            | DDRD6-DDRD0      | Pin       | PTD6–PTD0 <sup>(3)</sup> |

| Х      | 1           | Х                | Output                                | DDRD6-DDRD0      | PTD6–PTD0 | PTD6–PTD0                |

1. X = Don't care

2. I/O pin pulled up to  $V_{DD}$  by internal pullup device. 3. Writing affects data register, but does not affect input.

4. Hi-Z = High impedance

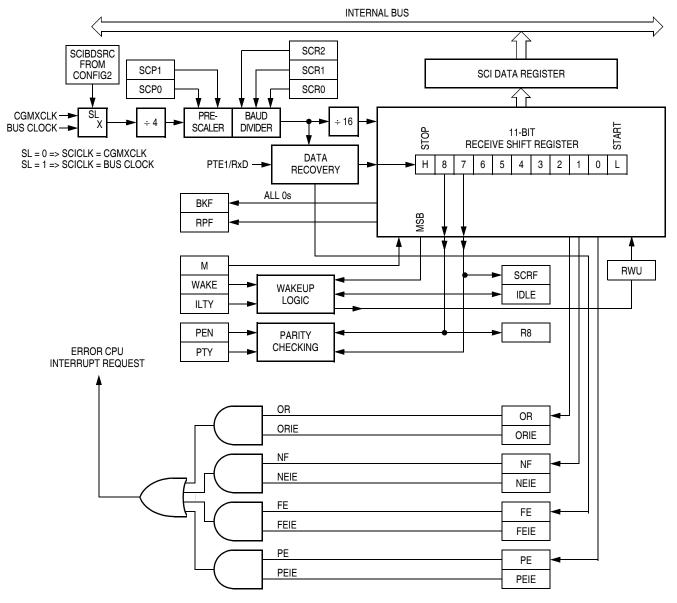

#### **Functional Description**

Figure 13-6. SCI Receiver Block Diagram

To determine the value of a data bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 13-3 summarizes the results of the data bit samples.

| RT8, RT9, and RT10<br>Samples | Data Bit<br>Determination | Noise Flag |  |  |  |

|-------------------------------|---------------------------|------------|--|--|--|

| 000                           | 0                         | 0          |  |  |  |

| 001                           | 0                         | 1          |  |  |  |

| 010                           | 0                         | 1          |  |  |  |

| 011                           | 1                         | 1          |  |  |  |

| 100                           | 0                         | 1          |  |  |  |

| 101                           | 1                         | 1          |  |  |  |

| 110                           | 1                         | 1          |  |  |  |

| 111                           | 1                         | 0          |  |  |  |

### NOTE

The RT8, RT9, and RT10 samples do not affect start bit verification. If any or all of the RT8, RT9, and RT10 start bit samples are 1s following a successful start bit verification, the noise flag (NF) is set and the receiver assumes that the bit is a start bit.

To verify a stop bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 13-4 summarizes the results of the stop bit samples.

| RT8, RT9, and RT10<br>Samples | Framing<br>Error Flag | Noise Flag |  |

|-------------------------------|-----------------------|------------|--|

| 000                           | 1                     | 0          |  |

| 001                           | 1                     | 1          |  |

| 010                           | 1                     | 1          |  |

| 011                           | 0                     | 1          |  |

| 100                           | 1                     | 1          |  |

| 101                           | 0                     | 1          |  |

| 110                           | 0                     | 1          |  |

| 111                           | 0                     | 0          |  |

#### Table 13-4. Stop Bit Recovery

### 13.4.3.4 Framing Errors

If the data recovery logic does not detect a 1 where the stop bit should be in an incoming character, it sets the framing error bit, FE, in SCS1. A break character also sets the FE bit because a break character has no stop bit. The FE bit is set at the same time that the SCRF bit is set.

#### Serial Communications Interface (SCI) Module

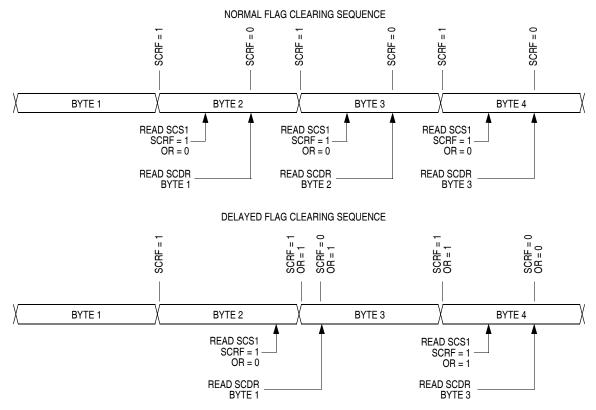

Software latency may allow an overrun to occur between reads of SCS1 and SCDR in the flag-clearing sequence. Figure 13-14 shows the normal flag-clearing sequence and an example of an overrun caused by a delayed flag-clearing sequence. The delayed read of SCDR does not clear the OR bit because OR was not set when SCS1 was read. Byte 2 caused the overrun and is lost. The next flag-clearing sequence reads byte 3 in the SCDR instead of byte 2.

In applications that are subject to software latency or in which it is important to know which byte is lost due to an overrun, the flag-clearing routine can check the OR bit in a second read of SCS1 after reading the data register.

Figure 13-14. Flag Clearing Sequence

### NF — Receiver Noise Flag Bit

This clearable, read-only bit is set when the SCI detects noise on the PTE1/RxD pin. NF generates an SCI error CPU interrupt request if the NEIE bit in SCC3 is also set. Clear the NF bit by reading SCS1 and then reading the SCDR. Reset clears the NF bit.

1 = Noise detected

0 = No noise detected

#### FE — Receiver Framing Error Bit

This clearable, read-only bit is set when a 0 is accepted as the stop bit. FE generates an SCI error CPU interrupt request if the FEIE bit in SCC3 also is set. Clear the FE bit by reading SCS1 with FE set and then reading the SCDR. Reset clears the FE bit.

1 = Framing error detected

0 = No framing error detected

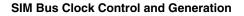

## 14.2 SIM Bus Clock Control and Generation

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, CGMOUT, as shown in Figure 14-3. This clock originates from either an external oscillator or from the on-chip PLL.

### 14.2.1 Bus Timing

In user mode, the internal bus frequency is either the crystal oscillator output (CGMXCLK) divided by four or the PLL output (CGMVCLK) divided by four.

### 14.2.2 Clock Startup from POR or LVI Reset

When the power-on reset module or the low-voltage inhibit module generates a reset, the clocks to the CPU and peripherals are inactive and held in an inactive phase until after the 4096 CGMXCLK cycle POR timeout has completed. The RST pin is driven low by the SIM during this entire period. The bus clocks start upon completion of the timeout.

Figure 14-3. System Clock Signals

### 14.2.3 Clocks in Stop Mode and Wait Mode

Upon exit from stop mode by an interrupt or reset, the SIM allows CGMXCLK to clock the SIM counter. The CPU and peripheral clocks do not become active until after the stop delay timeout. This timeout is selectable as 4096 or 32 CGMXCLK cycles. See 14.6.2 Stop Mode.

In wait mode, the CPU clocks are inactive. The SIM also produces two sets of clocks for other modules. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

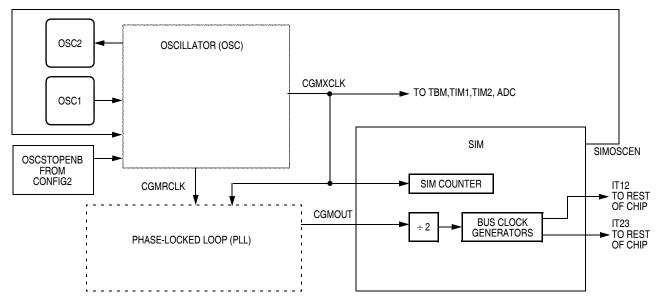

Interrupts are latched, and arbitration is performed in the SIM at the start of interrupt processing. The arbitration result is a constant that the CPU uses to determine which vector to fetch. Once an interrupt is latched by the SIM, no other interrupt can take precedence, regardless of priority, until the latched interrupt is serviced (or the I bit is cleared). See Figure 14-10.

Figure 14-10. Interrupt Processing

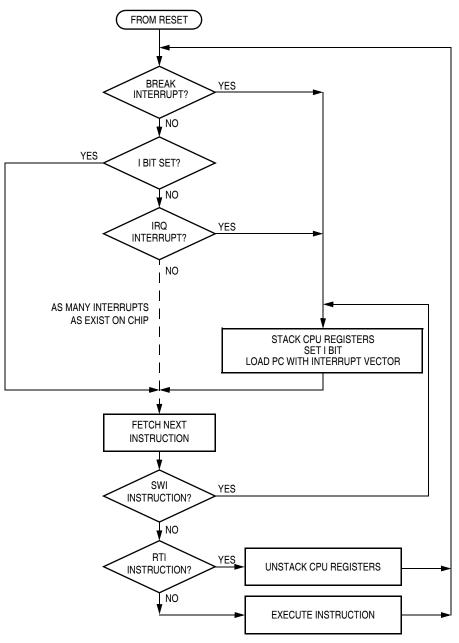

## 15.12 I/O Registers

Three registers control and monitor SPI operation:

- SPI control register (SPCR)

- SPI status and control register (SPSCR)

- SPI data register (SPDR)

### 15.12.1 SPI Control Register

The SPI control register:

- Enables SPI module interrupt requests

- · Configures the SPI module as master or slave

- Selects serial clock polarity and phase

- · Configures the SPSCK, MOSI, and MISO pins as open-drain outputs

- Enables the SPI module

### Figure 15-14. SPI Control Register (SPCR)

### SPRIE — SPI Receiver Interrupt Enable Bit

This read/write bit enables CPU interrupt requests generated by the SPRF bit. The SPRF bit is set when a byte transfers from the shift register to the receive data register. Reset clears the SPRIE bit.

1 = SPRF CPU interrupt requests enabled

0 = SPRF CPU interrupt requests disabled

#### SPMSTR — SPI Master Bit

This read/write bit selects master mode operation or slave mode operation. Reset sets the SPMSTR bit.

1 = Master mode

0 = Slave mode

### **CPOL** — Clock Polarity Bit

This read/write bit determines the logic state of the SPSCK pin between transmissions. (See Figure 15-5 and Figure 15-7.) To transmit data between SPI modules, the SPI modules must have identical CPOL values. Reset clears the CPOL bit.

#### CPHA — Clock Phase Bit

This read/write bit controls the timing relationship between the serial clock and SPI data. (See Figure 15-5 and Figure 15-7.) To transmit data between SPI modules, the SPI modules must have identical CPHA values. When CPHA = 0, the  $\overline{SS}$  pin of the slave SPI module must be high between bytes. (See Figure 15-13.) Reset sets the CPHA bit.

### SPWOM — SPI Wired-OR Mode Bit

This read/write bit disables the pullup devices on pins SPSCK, MOSI, and MISO so that those pins become open-drain outputs.

1 = Wired-OR SPSCK, MOSI, and MISO pins

0 = Normal push-pull SPSCK, MOSI, and MISO pins

#### **OVRF** — Overflow Bit

This clearable, read-only flag is set if software does not read the byte in the receive data register before the next full byte enters the shift register. In an overflow condition, the byte already in the receive data register is unaffected, and the byte that shifted in last is lost. Clear the OVRF bit by reading the SPI status and control register with OVRF set and then reading the receive data register. Reset clears the OVRF bit.

- 1 = Overflow

- 0 = No overflow

#### MODF — Mode Fault Bit

This clearable, read-only flag is set in a slave SPI if the SS pin goes high during a transmission with MODFEN set. In a master SPI, the MODF flag is set if the SS pin goes low at any time with the MODFEN bit set. Clear MODF by reading the SPI status and control register (SPSCR) with MODF set and then writing to the SPI control register (SPCR). Reset clears the MODF bit.

- $1 = \overline{SS}$  pin at inappropriate logic level

- $0 = \overline{SS}$  pin at appropriate logic level

#### SPTE — SPI Transmitter Empty Bit

This clearable, read-only flag is set each time the transmit data register transfers a byte into the shift register. SPTE generates an SPTE CPU interrupt request if SPTIE in the SPI control register is set also.

#### NOTE

Do not write to the SPI data register unless SPTE is high.

During an SPTE CPU interrupt, the CPU clears SPTE bit writing to the transmit data register. Reset sets the SPTE bit.

1 = Transmit data register empty

0 = Transmit data register not empty

#### MODFEN — Mode Fault Enable Bit

This read/write bit, when set, allows the MODF flag to be set. If the MODF flag is set, clearing MODFEN does not clear the MODF flag. If the SPI is enabled as a master and the MODFEN bit is 0, then the  $\overline{SS}$  pin is available as a general-purpose I/O.

If the MODFEN bit is 1, then the  $\overline{SS}$  is not available as a general-purpose I/O. When the SPI is enabled as a slave, the  $\overline{SS}$  pin is not available as a general-purpose I/O regardless of the value of MODFEN. See 15.11.4 SS (Slave Select).

If the MODFEN bit is 0, the level of the  $\overline{SS}$  pin does not affect the operation of an enabled SPI configured as a master. For an enabled SPI configured as a slave, having MODFEN low only prevents the MODF flag from being set. It does not affect any other part of SPI operation. See 15.6.2 Mode Fault Error.

#### SPR1 and SPR0 — SPI Baud Rate Select Bits

In master mode, these read/write bits select one of four baud rates as shown in Table 15-3. SPR1 and SPR0 have no effect in slave mode. Reset clears SPR1 and SPR0.

| SPR1 and SPR0 | Baud Rate Divisor (BD) |

|---------------|------------------------|

| 00            | 2                      |

| 01            | 8                      |

| 10            | 32                     |

| 11            | 128                    |

#### Table 15-3. SPI Master Baud Rate Selection

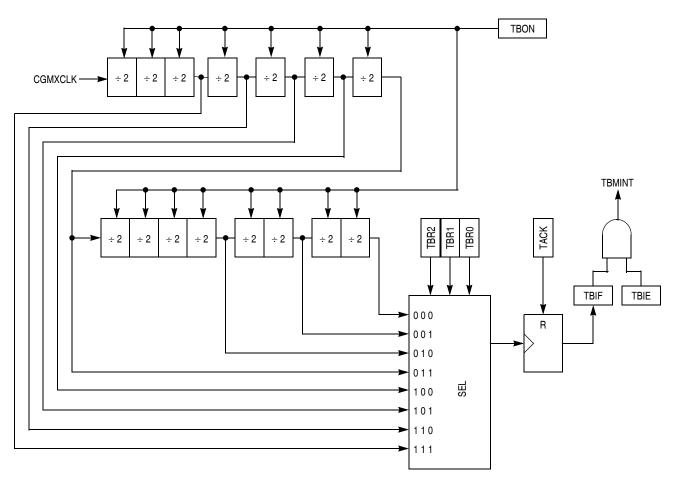

Timebase Module (TBM)

Figure 16-1. Timebase Block Diagram

## 16.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

### 16.5.1 Wait Mode

The timebase module remains active after execution of the WAIT instruction. In wait mode the timebase register is not accessible by the CPU.

If the timebase functions are not required during wait mode, reduce the power consumption by stopping the timebase before executing the WAIT instruction.

### 16.5.2 Stop Mode

The timebase module may remain active after execution of the STOP instruction if the internal clock generator has been enabled to operate during stop mode through the OSCSTOPENB bit in the configuration register. The timebase module can be used in this mode to generate a periodic wakeup from stop mode.

If the internal clock generator has not been enabled to operate in stop mode, the timebase module will not be active during stop mode. In stop mode, the timebase register is not accessible by the CPU.

# Chapter 18 Development Support

## **18.1 Introduction**

This section describes the break module, the monitor module (MON), and the monitor mode entry methods.

## 18.2 Break Module (BRK)

The break module can generate a break interrupt that stops normal program flow at a defined address to enter a background program.

Features of the break module include:

- Accessible input/output (I/O) registers during the break Interrupt

- Central processor unit (CPU) generated break interrupts

- Software-generated break interrupts

- Computer operating properly (COP) disabling during break interrupts

### 18.2.1 Functional Description

When the internal address bus matches the value written in the break address registers, the break module issues a breakpoint signal (BKPT) to the system integration module (SIM). The SIM then causes the CPU to load the instruction register with a software interrupt instruction (SWI). The program counter vectors to \$FFFC and \$FFFD (\$FEFC and \$FEFD in monitor mode).

The following events can cause a break interrupt to occur:

- A CPU generated address (the address in the program counter) matches the contents of the break address registers.

- Software writes a 1 to the BRKA bit in the break status and control register.

When a CPU generated address matches the contents of the break address registers, the break interrupt is generated. A return-from-interrupt instruction (RTI) in the break routine ends the break interrupt and returns the microcontroller unit (MCU) to normal operation.

Figure 18-2 shows the structure of the break module.

Figure 18-3 provides a summary of the I/O registers.

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- A. THIS DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

- 4. 751F-01 THRU -04 OBSOLETE. NEW STANDARD: 751F-05

- A. THIS DIMENSION DOES NOT INCLUDE DAM BAR PROTRUSION ALLOWABLE DAM BAR PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF THIS DIMENSION AT MAXIMUM MATERIAL CONDITION.

| © FREESCALE SEMICONDUCTOR, INC.<br>All rights reserved.      |  | OUTLINE                         | PRINT VERSION NO | DT TO SCALE |

|--------------------------------------------------------------|--|---------------------------------|------------------|-------------|

| <sup>title:</sup> Soic, Wide Body,<br>28 Lead<br>caseoutline |  | DOCUMENT NO                     | : 98ASB42345B    | REV: G      |

|                                                              |  | CASE NUMBER: 751F-05 10 MAR 200 |                  | 10 MAR 2005 |

|                                                              |  | STANDARD: MS-013AE              |                  |             |