Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | HC08                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | SCI, SPI                                                                 |

| Peripherals                | LVD, POR, PWM                                                            |

| Number of I/O              | 21                                                                       |

| Program Memory Size        | 7.5KB (7.5K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 384 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 6x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-LQFP                                                                  |

| Supplier Device Package    | 32-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchc908gr8amfaer |

|                            |                                                                          |

## **List of Chapters**

| Chapter 1 General Description                                 | 19  |

|---------------------------------------------------------------|-----|

| Chapter 2 Memory                                              |     |

| Chapter 3 Analog-to-Digital Converter (ADC)                   | 47  |

| Chapter 4 Clock Generator Module (CGM)                        | 55  |

| Chapter 5 Configuration Register (CONFIG)                     |     |

| Chapter 6 Computer Operating Properly (COP) Module            | 79  |

| Chapter 7 Central Processor Unit (CPU)                        | 83  |

| Chapter 8 External Interrupt (IRQ)                            |     |

| Chapter 9 Keyboard Interrupt Module (KBI)                     |     |

| Chapter 10 Low-Power Modes                                    | 105 |

| Chapter 11 Low-Voltage Inhibit (LVI)                          | 111 |

| Chapter 12 Input/Output (I/O) Ports                           |     |

| Chapter 13 Serial Communications Interface (SCI) Module       |     |

| Chapter 14 System Integration Module (SIM)                    | 157 |

| Chapter 15 Serial Peripheral Interface (SPI) Module           | 175 |

| Chapter 16 Timebase Module (TBM)                              | 195 |

| Chapter 17 Timer Interface Module (TIM1 and TIM2)             | 199 |

| Chapter 18 Development Support                                | 215 |

| Chapter 19 Electrical Specifications                          | 231 |

| Chapter 20 Ordering Information and Mechanical Specifications | 249 |

### **Table of Contents**

## Chapter 3 Analog-to-Digital Converter (ADC)

| 3.1               | Introduction                                                                                  | 47  |

|-------------------|-----------------------------------------------------------------------------------------------|-----|

| 3.2               | Features                                                                                      | 47  |

| 3.3               | Functional Description                                                                        | 47  |

| 3.3.1             | ADC Port I/O Pins                                                                             | 47  |

| 3.3.2             | Voltage Conversion                                                                            | 49  |

| 3.3.3             | Conversion Time                                                                               | 50  |

| 3.3.4             | Conversion                                                                                    | 50  |

| 3.3.5             | Accuracy and Precision                                                                        | 50  |

| 3.4               | Interrupts                                                                                    | 50  |

| 3.5               | Low-Power Modes                                                                               | 50  |

| 3.5.1             | Wait Mode                                                                                     | 50  |

| 3.5.2             | Stop Mode                                                                                     | 50  |

| 3.6               | I/O Signals                                                                                   | 51  |

| 3.6.1             | ADC Analog Ground Pin (V <sub>SSAD</sub> )/ADC Voltage Reference Low Pin (V <sub>REFL</sub> ) |     |

| 3.6.2             | ADC Analog Power Pin (V <sub>DDAD</sub> )/ADC Voltage Reference High Pin (V <sub>REFH</sub> ) |     |

| 3.6.3             | ADC Voltage In (V <sub>ADIN</sub> )                                                           |     |

| 3.7               | I/O Registers                                                                                 | 51  |

| 3.7.1             | ADC Status and Control Register                                                               |     |

| 3.7.2             | ADC Data Register                                                                             | 53  |

| 3.7.3             | ADC Clock Register                                                                            | 53  |

|                   | Chapter 4                                                                                     |     |

|                   | Chapter 4 Clock Generator Module (CGM)                                                        |     |

| 4.1               | Introduction                                                                                  | E 6 |

| 4. i<br>4.2       |                                                                                               |     |

|                   | Features                                                                                      |     |

| 4.3<br>4.3.1      | Functional Description                                                                        |     |

| 4.3.1<br>4.3.2    | Crystal Oscillator Circuit                                                                    |     |

| 4.3.2<br>4.3.3    | PLL Circuits                                                                                  |     |

| 4.3.4<br>4.3.4    | Acquisition and Tracking Modes                                                                |     |

| 4.3. <del>4</del> | Manual and Automatic PLL Bandwidth Modes                                                      |     |

| 4.3.6             | Programming the PLL                                                                           |     |

| 4.3.7             | Special Programming Exceptions                                                                |     |

| 4.3.8             | Base Clock Selector Circuit                                                                   |     |

| 4.3.9             | CGM External Connections                                                                      |     |

| 4.4               | I/O Signals                                                                                   |     |

| 4.4.1             | Crystal Amplifier Input Pin (OSC1).                                                           | 63  |

| 4.4.2             | Crystal Amplifier Output Pin (OSC2)                                                           | 63  |

| 4.4.3             | External Filter Capacitor Pin (CGMXFC)                                                        |     |

| 4.4.4             | PLL Analog Power Pin (V <sub>DDA</sub> )                                                      |     |

| 4.4.5             | PLL Analog Ground Pin (V <sub>SSA</sub> )                                                     |     |

| 4.4.6             | Oscillator Enable Signal (SIMOSCEN)                                                           |     |

| 4.4.7             | Oscillator Stop Mode Enable Bit (OSCSTOPENB)                                                  | 64  |

| 4.4.8             | Crystal Output Frequency Signal (CGMXCLK)                                                     |     |

| 4.4.9             | CGM Base Clock Output (CGMOUT)                                                                |     |

| 4.4.10            | CGM CPU Interrupt (CGMINT)                                                                    |     |

|                   |                                                                                               |     |

MC68HC908GR8A • MC68HC908GR4A Data Sheet, Rev. 5

| Addr.                                         | Register Name                                                                                                                                                                                                                                           |                                                                                                              | Bit 7                                                | 6                    | 5                                | 4                                          | 3                                           | 2                              | 1                            | Bit 0                       |  |  |  |  |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------|----------------------------------|--------------------------------------------|---------------------------------------------|--------------------------------|------------------------------|-----------------------------|--|--|--|--|

|                                               | Timer 1 Counter                                                                                                                                                                                                                                         | Read:                                                                                                        | Bit 7                                                | 6                    | 5                                | 4                                          | 3                                           | 2                              | 1                            | Bit 0                       |  |  |  |  |

| \$0022                                        | Register Low (T1CNTL)                                                                                                                                                                                                                                   | Write:                                                                                                       |                                                      |                      |                                  |                                            |                                             |                                |                              |                             |  |  |  |  |

|                                               | See page 210.                                                                                                                                                                                                                                           | Reset:                                                                                                       | 0                                                    | 0                    | 0                                | 0                                          | 0                                           | 0                              | 0                            | 0                           |  |  |  |  |

|                                               | Timer 1 Counter Modulo                                                                                                                                                                                                                                  |                                                                                                              | Dia 45                                               | 4.4                  | 10                               | 10                                         | 44                                          | 10                             | 0                            | D:+ 0                       |  |  |  |  |

| \$0023                                        | Register High (T1MODH)                                                                                                                                                                                                                                  | Write:                                                                                                       | Bit 15                                               | 14                   | 13                               | 12                                         | 11                                          | 10                             | 9                            | Bit 8                       |  |  |  |  |

|                                               | See page 211.                                                                                                                                                                                                                                           | Reset:                                                                                                       | 1                                                    | 1                    | 1                                | 1                                          | 1                                           | 1                              | 1                            | 1                           |  |  |  |  |

|                                               | Timer 1 Counter Modulo<br>\$0024 Register Low (T1MODL)                                                                                                                                                                                                  |                                                                                                              | Bit 7                                                | 6                    | 5                                | 4                                          | 3                                           | 2                              | 1                            | Bit 0                       |  |  |  |  |

| \$0024                                        |                                                                                                                                                                                                                                                         |                                                                                                              | DIL 7                                                | 0                    | 3                                | 4                                          | 3                                           | 2                              | -                            | DIL U                       |  |  |  |  |

|                                               | See page 211.                                                                                                                                                                                                                                           | Reset:                                                                                                       | 1                                                    | 1                    | 1                                | 1                                          | 1                                           | 1                              | 1                            | 1                           |  |  |  |  |

|                                               | Timer 1 Channel 0 Status and                                                                                                                                                                                                                            | Read:                                                                                                        | CH0F                                                 | CH0IE                | MS0B                             | MS0A                                       | ELS0B                                       | ELS0A                          | TOV0                         | CHOMAX                      |  |  |  |  |

| \$0025                                        | Control Register (T1SC0)                                                                                                                                                                                                                                | Write:                                                                                                       | 0                                                    | OFIOIL               | WOOD                             | WOOA                                       | LLOOD                                       | LLOOK                          | 1000                         | OTIONIPOX                   |  |  |  |  |

|                                               | See page 214.                                                                                                                                                                                                                                           | Reset:                                                                                                       | 0                                                    | 0                    | 0                                | 0                                          | 0                                           | 0                              | 0                            | 0                           |  |  |  |  |

|                                               | Timer 1 Channel 0                                                                                                                                                                                                                                       | Read:                                                                                                        | Bit 15                                               | 14                   | 13                               | 12                                         | 11                                          | 10                             | 9                            | Bit 8                       |  |  |  |  |

| \$0026                                        | Register High (T1CH0H)                                                                                                                                                                                                                                  | Write:                                                                                                       | <b>D</b> it 10                                       |                      |                                  |                                            |                                             | .0                             | ŭ                            | Dit 0                       |  |  |  |  |

|                                               | See page 214.                                                                                                                                                                                                                                           | Reset:                                                                                                       |                                                      |                      |                                  | Indetermina                                | te after reset                              |                                |                              |                             |  |  |  |  |

|                                               | Timer 1 Channel 0                                                                                                                                                                                                                                       | Read:                                                                                                        | Bit 7                                                | 6                    | 5                                | 4                                          | 3                                           | 2                              | 1                            | Bit 0                       |  |  |  |  |

| \$0027 Register Low (T1CH0L)<br>See page 214. |                                                                                                                                                                                                                                                         | Write:                                                                                                       |                                                      |                      |                                  |                                            |                                             | _                              |                              | 20                          |  |  |  |  |

|                                               | 3ee page 214.                                                                                                                                                                                                                                           | Reset:                                                                                                       |                                                      | 1                    | T                                | : Indeterminate after reset                |                                             |                                |                              |                             |  |  |  |  |

|                                               |                                                                                                                                                                                                                                                         |                                                                                                              |                                                      |                      |                                  |                                            |                                             |                                |                              |                             |  |  |  |  |

|                                               | Timer 1 Channel 1 Status and                                                                                                                                                                                                                            | Read:                                                                                                        | CH1F                                                 | CH1IE                | 0                                | MS1A                                       | ELS1B                                       | ELS1A                          | TOV1                         | CH1MAX                      |  |  |  |  |

| \$0028                                        | Control Register (T1SC1)                                                                                                                                                                                                                                | Write:                                                                                                       | 0                                                    | CH1IE                |                                  |                                            | ELS1B                                       | ELS1A                          | TOV1                         | CH1MAX                      |  |  |  |  |

| \$0028                                        |                                                                                                                                                                                                                                                         | Write:                                                                                                       |                                                      | CH1IE<br>0           | 0                                | MS1A<br>0                                  | ELS1B<br>0                                  | ELS1A<br>0                     | TOV1                         | CH1MAX<br>0                 |  |  |  |  |

|                                               | Control Register (T1SC1) See page 214. Timer 1 Channel 1                                                                                                                                                                                                | Write:<br>Reset:<br>Read:                                                                                    | 0                                                    |                      |                                  |                                            |                                             |                                | 0                            |                             |  |  |  |  |

| \$0028<br>\$0029                              | Control Register (T1SC1) See page 214.  Timer 1 Channel 1 Register High (T1CH1H)                                                                                                                                                                        | Write: Reset: Read: Write:                                                                                   | 0                                                    | 0                    | 0                                | 0 12                                       | 0 11                                        | 0                              |                              | 0                           |  |  |  |  |

|                                               | Control Register (T1SC1) See page 214. Timer 1 Channel 1                                                                                                                                                                                                | Write: Reset: Read: Write: Reset:                                                                            | 0                                                    | 0                    | 0                                | 0 12                                       | 0                                           | 0                              | 0                            | 0                           |  |  |  |  |

| \$0029                                        | Control Register (T1SC1) See page 214.  Timer 1 Channel 1 Register High (T1CH1H) See page 214.  Timer 1 Channel 1                                                                                                                                       | Write: Reset: Read: Write: Reset: Read:                                                                      | 0                                                    | 0                    | 0                                | 0 12                                       | 0 11                                        | 0                              | 0                            | 0                           |  |  |  |  |

|                                               | Control Register (T1SC1) See page 214.  Timer 1 Channel 1 Register High (T1CH1H) See page 214.  Timer 1 Channel 1 Register Low (T1CH1L)                                                                                                                 | Write: Reset: Read: Write: Reset: Read: Write:                                                               | 0<br>0<br>Bit 15                                     | 0 14                 | 0 13                             | 0<br>12<br>Indetermina<br>4                | 0<br>11<br>te after reset                   | 0 10                           | 9                            | 0<br>Bit 8                  |  |  |  |  |

| \$0029                                        | Control Register (T1SC1) See page 214.  Timer 1 Channel 1 Register High (T1CH1H) See page 214.  Timer 1 Channel 1                                                                                                                                       | Write: Reset: Read: Write: Reset: Read: Write: Reset: Reset:                                                 | 0<br>0<br>Bit 15                                     | 0 14                 | 0 13                             | 0 12 Indetermina 4 Indetermina             | 0 11 te after reset 3                       | 0 10                           | 9                            | 0<br>Bit 8                  |  |  |  |  |

| \$0029<br>\$002A                              | Control Register (T1SC1) See page 214.  Timer 1 Channel 1 Register High (T1CH1H) See page 214.  Timer 1 Channel 1 Register Low (T1CH1L) See page 214.                                                                                                   | Write: Reset: Read: Write: Reset: Read: Write: Read: Reset: Reset: Reset:                                    | 0<br>0<br>Bit 15<br>Bit 7                            | 0 14                 | 0 13                             | 0 12 Indetermina 4 Indetermina 0           | 0<br>11<br>te after reset                   | 0 10                           | 9                            | 0<br>Bit 8                  |  |  |  |  |

| \$0029                                        | Control Register (T1SC1) See page 214.  Timer 1 Channel 1 Register High (T1CH1H) See page 214.  Timer 1 Channel 1 Register Low (T1CH1L) See page 214.  Timer 2 Status and Control Register (T2SC)                                                       | Write: Reset: Read: Write: Reset: Read: Write: Reset: Reset: Write: Write:                                   | 0<br>0<br>Bit 15<br>Bit 7                            | 0<br>14<br>6<br>TOIE | 0<br>13<br>5                     | 0 12 Indetermina 4 Indetermina 0 TRST      | 0 11 te after reset 3 te after reset 0      | 0<br>10<br>2<br>PS2            | 0<br>9<br>1                  | 0 Bit 8 Bit 0               |  |  |  |  |

| \$0029<br>\$002A                              | Control Register (T1SC1) See page 214.  Timer 1 Channel 1 Register High (T1CH1H) See page 214.  Timer 1 Channel 1 Register Low (T1CH1L) See page 214.                                                                                                   | Write: Reset: Read: Write: Reset: Read: Write: Reset: Reset: Reset: Reset: Reset:                            | 0<br>0<br>Bit 15<br>Bit 7<br>TOF<br>0                | 0 14 6 TOIE 0        | 0<br>13<br>5<br>TSTOP            | 0 12 Indetermina 4 Indetermina 0 TRST 0    | 0 11 te after reset 3 te after reset 0      | 0<br>10<br>2<br>PS2<br>0       | 0<br>9<br>1<br>PS1           | O Bit 8 Bit 0 PS0 O         |  |  |  |  |

| \$0029<br>\$002A<br>\$002B                    | Control Register (T1SC1) See page 214.  Timer 1 Channel 1 Register High (T1CH1H) See page 214.  Timer 1 Channel 1 Register Low (T1CH1L) See page 214.  Timer 2 Status and Control Register (T2SC) See page 211.  Timer 2 Counter                        | Write: Reset: Read: Write: Reset: Read: Write: Reset: Read: Write: Reset: Read: Write: Reset: Reset:         | 0<br>0<br>Bit 15<br>Bit 7                            | 0<br>14<br>6<br>TOIE | 0<br>13<br>5                     | 0 12 Indetermina 4 Indetermina 0 TRST      | 0 11 te after reset 3 te after reset 0      | 0<br>10<br>2<br>PS2            | 0<br>9<br>1                  | 0 Bit 8 Bit 0               |  |  |  |  |

| \$0029<br>\$002A                              | Control Register (T1SC1) See page 214.  Timer 1 Channel 1 Register High (T1CH1H) See page 214.  Timer 1 Channel 1 Register Low (T1CH1L) See page 214.  Timer 2 Status and Control Register (T2SC) See page 211.  Timer 2 Counter Register High (T2CNTH) | Write: Reset: Read: Write: Reset: Read: Write: Reset: Read: Write: Reset: Reset: Reset: Reset: Reset: Reset: | 0<br>0<br>Bit 15<br>Bit 7<br>TOF<br>0<br>0<br>Bit 15 | 0 14 6 TOIE 0 14     | 0<br>13<br>5<br>TSTOP<br>1<br>13 | 0 12 Indetermina 4 Indetermina 0 TRST 0 12 | 0 11 te after reset 3 te after reset 0 0 11 | 0<br>10<br>2<br>PS2<br>0<br>10 | 0<br>9<br>1<br>PS1<br>0<br>9 | O Bit 8  Bit 0  PS0 O Bit 8 |  |  |  |  |

| \$0029<br>\$002A<br>\$002B                    | Control Register (T1SC1) See page 214.  Timer 1 Channel 1 Register High (T1CH1H) See page 214.  Timer 1 Channel 1 Register Low (T1CH1L) See page 214.  Timer 2 Status and Control Register (T2SC) See page 211.  Timer 2 Counter                        | Write: Reset: Read: Write: Reset: Read: Write: Reset: Read: Write: Reset: Read: Write: Reset: Reset:         | 0<br>0<br>Bit 15<br>Bit 7<br>TOF<br>0                | 0 14 6 TOIE 0        | 0<br>13<br>5<br>TSTOP            | 0 12 Indetermina 4 Indetermina 0 TRST 0    | 0 11 te after reset 3 te after reset 0      | 0<br>10<br>2<br>PS2<br>0       | 0<br>9<br>1<br>PS1           | O Bit 8 Bit 0 PS0 O         |  |  |  |  |

| \$0029<br>\$002A<br>\$002B                    | Control Register (T1SC1) See page 214.  Timer 1 Channel 1 Register High (T1CH1H) See page 214.  Timer 1 Channel 1 Register Low (T1CH1L) See page 214.  Timer 2 Status and Control Register (T2SC) See page 211.  Timer 2 Counter Register High (T2CNTH) | Write: Reset: Read: Write: Reset: Read: Write: Reset: Read: Write: Reset: Reset: Reset: Reset: Reset: Reset: | 0<br>0<br>Bit 15<br>Bit 7<br>TOF<br>0<br>0<br>Bit 15 | 0 14 6 TOIE 0 14     | 0<br>13<br>5<br>TSTOP<br>1<br>13 | 0 12 Indetermina 4 Indetermina 0 TRST 0 12 | 0 11 te after reset 3 te after reset 0 0 11 | 0<br>10<br>2<br>PS2<br>0<br>10 | 0<br>9<br>1<br>PS1<br>0<br>9 | O Bit 8  Bit 0  PS0 O Bit 8 |  |  |  |  |

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 7)

MC68HC908GR8A • MC68HC908GR4A Data Sheet, Rev. 5

**Table 2-1. Vector Addresses**

| Vector Priority | Vector | Address | Vector                                |

|-----------------|--------|---------|---------------------------------------|

| Lowest          | IF16   | \$FFDC  | Timebase Vector (High)                |

| A               | IFIO   | \$FFDD  | Timebase Vector (Low)                 |

|                 | 1515   | \$FFDE  | ADC Conversion Complete Vector (High) |

|                 | IF15   | \$FFDF  | ADC Conversion Complete Vector (Low)  |

|                 | 154.4  | \$FFE0  | Keyboard Vector (High)                |

|                 | IF14   | \$FFE1  | Keyboard Vector (Low)                 |

|                 | 1510   | \$FFE2  | SCI Transmit Vector (High)            |

|                 | IF13   | \$FFE3  | SCI Transmit Vector (Low)             |

|                 | 1510   | \$FFE4  | SCI Receive Vector (High)             |

|                 | IF12   | \$FFE5  | SCI Receive Vector (Low)              |

|                 | 1544   | \$FFE6  | SCI Error Vector (High)               |

|                 | IF11   | \$FFE7  | SCI Error Vector (Low)                |

|                 | 1510   | \$FFE8  | SPI Transmit Vector (High)            |

|                 | IF10   | \$FFE9  | SPI Transmit Vector (Low)             |

|                 | IFO    | \$FFEA  | SPI Receive Vector (High)             |

|                 | IF9    | \$FFEB  | SPI Receive Vector (Low)              |

|                 | IEO    | \$FFEC  | TIM2 Overflow Vector (High)           |

|                 | IF8    | \$FFED  | TIM2 Overflow Vector (Low)            |

|                 | IF7    | \$FFEE  | Reserved                              |

|                 | IF/    | \$FFEF  | Reserved                              |

|                 | IF6    | \$FFF0  | TIM2 Channel 0 Vector (High)          |

|                 | IFO    | \$FFF1  | TIM2 Channel 0 Vector (Low)           |

|                 | ICC    | \$FFF2  | TIM1 Overflow Vector (High)           |

|                 | IF5    | \$FFF3  | TIM1 Overflow Vector (Low)            |

|                 | IF4    | \$FFF4  | TIM1 Channel 1 Vector (High)          |

|                 | 1174   | \$FFF5  | TIM1 Channel 1 Vector (Low)           |

|                 | IF3    | \$FFF6  | TIM1 Channel 0 Vector (High)          |

|                 | IF3    | \$FFF7  | TIM1 Channel 0 Vector (Low)           |

|                 | IFO    | \$FFF8  | PLL Vector (High)                     |

|                 | IF2    | \$FFF9  | PLL Vector (Low)                      |

|                 | IE1    | \$FFFA  | IRQ Vector (High)                     |

|                 | IF1    | \$FFFB  | IRQ Vector (Low)                      |

|                 |        | \$FFFC  | SWI Vector (High)                     |

|                 |        | \$FFFD  | SWI Vector (Low)                      |

| <b>*</b>        |        | \$FFFE  | Reset Vector (High)                   |

| Highest         |        | \$FFFF  | Reset Vector (Low)                    |

Memory

## 2.5 Random-Access Memory (RAM)

Addresses \$0040 through \$01BF are RAM locations. The location of the stack RAM is programmable. The 16-bit stack pointer allows the stack to be anywhere in the 64-Kbyte memory space.

### NOTE

For correct operation, the stack pointer must point only to RAM locations.

Within page zero are 192 bytes of RAM. Because the location of the stack RAM is programmable, all page zero RAM locations can be used for I/O control and user data or code. When the stack pointer is moved from its reset location at \$00FF out of page zero, direct addressing mode instructions can efficiently access all page zero RAM locations. Page zero RAM, therefore, provides ideal locations for frequently accessed global variables.

Before processing an interrupt, the CPU uses five bytes of the stack to save the contents of the CPU registers.

### NOTE

For M6805 compatibility, the H register is not stacked.

During a subroutine call, the CPU uses two bytes of the stack to store the return address. The stack pointer decrements during pushes and increments during pulls.

#### NOTE

Be careful when using nested subroutines. The CPU may overwrite data in the RAM during a subroutine or during the interrupt stacking operation.

## 2.6 FLASH Memory (FLASH)

This subsection describes the operation of the embedded FLASH memory. This memory can be read, programmed, and erased from a single external supply. The program, erase, and read operations are enabled through the use of an internal charge pump.

### 2.6.1 Functional Description

The FLASH memory is an array of 7,680 bytes for the MC68HC908GR8A or 4,096 bytes for the MC68HC908GR4A with an additional 36 bytes of user vectors and one byte of block protection. *An erased bit reads as 1 and a programmed bit reads as a 0.* Memory in the FLASH array is organized into two rows per page basis. The page size is 64 bytes per page and the row size is 32 bytes per row. Hence the minimum erase page size is 64 bytes and the minimum program row size is 32 bytes. Program and erase operation operations are facilitated through control bits in FLASH control register (FLCR). Details for these operations appear later in this section.

The address ranges for the user memory and vectors are:

- \$E000-\$FDFF; user memory for the MC68HC908GR8A

\$EE00-\$FDFF; user memory for the MC68HC908GR4A

- \$FE08; FLASH control register

- \$FF7E; FLASH block protect register

- \$FFDC-\$FFFF; these locations are reserved for user-defined interrupt and reset vectors

### NOTE

A security feature prevents viewing of the FLASH contents. (1)

MC68HC908GR8A • MC68HC908GR4A Data Sheet, Rev. 5

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

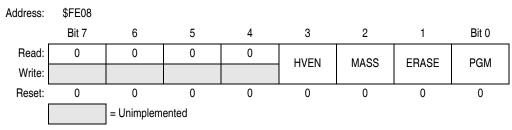

### 2.6.2 FLASH Control Register

The FLASH control register (FLCR) controls FLASH program and erase operations.

Figure 2-3. FLASH Control Register (FLCR)

### **HVEN** — High-Voltage Enable Bit

This read/write bit enables the charge pump to drive high voltages for program and erase operations in the array. HVEN can only be set if either PGM = 1 or ERASE = 1 and the proper sequence for program or erase is followed.

- 1 = High voltage enabled to array and charge pump on

- 0 = High voltage disabled to array and charge pump off

### MASS — Mass Erase Control Bit

Setting this read/write bit configures the FLASH array for mass erase operation.

- 1 = MASS erase operation selected

- 0 = PAGE erase operation selected

### **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Erase operation selected

- 0 = Erase operation unselected

### **PGM** — Program Control Bit

This read/write bit configures the memory for program operation. PGM is interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Program operation selected

- 0 = Program operation unselected

Memory

MC68HC908GR8A • MC68HC908GR4A Data Sheet, Rev. 5

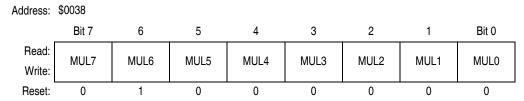

### 4.5.4 PLL Multiplier Select Register Low

The PLL multiplier select register low (PMSL) contains the programming information for the low byte of the modulo feedback divider.

Figure 4-7. PLL Multiplier Select Register Low (PMSL)

### NOTE

For applications using 1–8 MHz reference frequencies, this register must be reprogrammed before enabling the PLL. The reset value of this register will cause applications using 1–8 MHz reference frequencies to become unstable if the PLL is enabled without programming an appropriate value. The programmed value must not allow the VCO clock to exceed 32 MHz. See 4.3.6 Programming the PLL for detailed instructions on choosing the proper value for PMSL.

### MUL7-MUL0 — Multiplier Select Bits

These read/write bits control the low byte of the modulo feedback divider that selects the VCO frequency multiplier, N. (See 4.3.3 PLL Circuits and 4.3.6 Programming the PLL.) MUL7–MUL0 cannot be written when the PLLON bit in the PCTL is set. A value of \$0000 in the multiplier select registers configures the modulo feedback divider the same as a value of \$0001. Reset initializes the register to \$40 for a default multiply value of 64.

### NOTE

The multiplier select bits have built-in protection such that they cannot be written when the PLL is on (PLLON = 1).

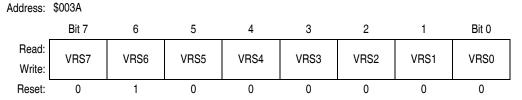

### 4.5.5 PLL VCO Range Select Register

The PLL VCO range select register (PMRS) contains the programming information required for the hardware configuration of the VCO.

Figure 4-8. PLL VCO Range Select Register (PMRS)

### VRS7-VRS0 — VCO Range Select Bits

These read/write bits control the hardware center-of-range linear multiplier L which, in conjunction with E (see 4.3.3 PLL Circuits, 4.3.6 Programming the PLL, and 4.5.1 PLL Control Register), controls the hardware center-of-range frequency, f<sub>VRS</sub>. VRS7–VRS0 cannot be written when the PLLON bit in the PCTL is set. (See 4.3.7 Special Programming Exceptions.) A value of \$00 in the VCO range select

### 6.3.6 COPD (COP Disable)

The COPD signal reflects the state of the COP disable bit (COPD) in the configuration register. See Chapter 5 Configuration Register (CONFIG).

### 6.3.7 COPRS (COP Rate Select)

The COPRS signal reflects the state of the COP rate select bit (COPRS) in the configuration register. See Chapter 5 Configuration Register (CONFIG).

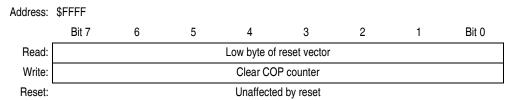

## 6.4 COP Control Register

The COP control register (COPCTL) is located at address \$FFFF and overlaps the reset vector. Writing any value to \$FFFF clears the COP counter and starts a new timeout period. Reading location \$FFFF returns the low byte of the reset vector.

Figure 6-2. COP Control Register (COPCTL)

## 6.5 Interrupts

The COP does not generate central processor unit (CPU) interrupt requests.

### 6.6 Monitor Mode

When monitor mode is entered with  $V_{TST}$  on the IRQ pin, the COP is disabled as long as  $V_{TST}$  remains on the IRQ pin or the RST pin. When monitor mode is entered by having blank reset vectors and not having  $V_{TST}$  on the IRQ pin, the COP is automatically disabled until a POR occurs.

### 6.7 Low-Power Modes

The WAIT and STOP instructions put the microcontroller unit (MCU) in low power-consumption standby modes.

### 6.7.1 Wait Mode

The COP remains active during wait mode. If COP is enabled, a reset will occur at COP timeout.

### 6.7.2 Stop Mode

Stop mode turns off the CGMXCLK input to the COP and clears the COP prescaler. Service the COP immediately before entering or after exiting stop mode to ensure a full COP timeout period after entering or exiting stop mode.

## Table 7-1. Instruction Set Summary (Sheet 4 of 6)

| Source                                                                                         | Operation                           | Description                                                                                                                                                                                           | Eff<br>on ( |   |   |   |          |   | Address<br>Mode                                     | Opcode                                           | Operand                                         | les                                  |

|------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---|---|---|----------|---|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                           |                                     |                                                                                                                                                                                                       | ٧           | Н | ı | N | Z        | С | Add                                                 | Opc                                              | Ope                                             | Cycles                               |

| JMP opr<br>JMP opr<br>JMP opr,X<br>JMP opr,X<br>JMP ,X                                         | Jump                                | PC ← Jump Address                                                                                                                                                                                     | _           | _ | _ | - | -        | - | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BC<br>CC<br>DC<br>EC<br>FC                       | dd<br>hh II<br>ee ff<br>ff                      | 2<br>3<br>4<br>3<br>2                |

| JSR opr<br>JSR opr<br>JSR opr,X<br>JSR opr,X<br>JSR ,X                                         | Jump to Subroutine                  | $PC \leftarrow (PC) + n (n = 1, 2, \text{ or } 3)$<br>$Push (PCL); SP \leftarrow (SP) - 1$<br>$PC \leftarrow Unconditional Address$                                                                   | _           | _ | _ | _ | _        | _ | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BD<br>CD<br>DD<br>ED<br>FD                       | dd<br>hh II<br>ee ff<br>ff                      | 4<br>5<br>6<br>5<br>4                |

| LDA #opr<br>LDA opr<br>LDA opr<br>LDA opr,X<br>LDA opr,X<br>LDA, X<br>LDA opr,SP<br>LDA opr,SP | Load A from M                       | A ← (M)                                                                                                                                                                                               | 0           | 1 | _ | ţ | ‡        | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A6<br>B6<br>C6<br>D6<br>E6<br>F6<br>9EE6<br>9ED6 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| LDHX #opr<br>LDHX opr                                                                          | Load H:X from M                     | H:X ← (M:M + 1)                                                                                                                                                                                       | 0           | _ | - | 1 | 1        | - | IMM<br>DIR                                          | 45<br>55                                         | ii jj<br>dd                                     | 3 4                                  |

| LDX #opr<br>LDX opr<br>LDX opr,<br>LDX opr,X<br>LDX opr,X<br>LDX,X<br>LDX opr,SP<br>LDX opr,SP | Load X from M                       | X ← (M)                                                                                                                                                                                               | 0           | _ | _ | 1 | <b>‡</b> | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | AE<br>BE<br>CE<br>DE<br>EE<br>FE<br>9EEE<br>9EDE | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff       | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| LSL opr<br>LSLA<br>LSLX<br>LSL opr,X<br>LSL ,X<br>LSL opr,SP                                   | Logical Shift Left<br>(Same as ASL) | © <b>-</b>                                                                                                                                                                                            | 1           | - | _ | 1 | 1        | ‡ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| LSR opr<br>LSRA<br>LSRX<br>LSR opr,X<br>LSR ,X<br>LSR opr,SP                                   | Logical Shift Right                 | 0 - C b7 b0                                                                                                                                                                                           | t           | _ | - | 0 | 1        | 1 | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 34<br>44<br>54<br>64<br>74<br>9E64               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| MOV opr,opr<br>MOV opr,X+<br>MOV #opr,opr<br>MOV X+,opr                                        | Move                                | $(M)_{Destination} \leftarrow (M)_{Source}$ $H:X \leftarrow (H:X) + 1 (IX+D, DIX+)$                                                                                                                   | 0           | _ | - | ‡ | ‡        | - | DD<br>DIX+<br>IMD<br>IX+D                           | 4E<br>5E<br>6E<br>7E                             | dd dd<br>dd<br>ii dd<br>dd                      | 5<br>4<br>4<br>4                     |

| MUL                                                                                            | Unsigned multiply                   | $X:A \leftarrow (X) \times (A)$                                                                                                                                                                       | -           | 0 | - | - | _        | 0 | INH                                                 | 42                                               |                                                 | 5                                    |

| NEG opr<br>NEGA<br>NEGX<br>NEG opr,X<br>NEG ,X<br>NEG opr,SP                                   | Negate (Two's Complement)           | $\begin{array}{l} M \leftarrow -(M) = \$00 - (M) \\ A \leftarrow -(A) = \$00 - (A) \\ X \leftarrow -(X) = \$00 - (X) \\ M \leftarrow -(M) = \$00 - (M) \\ M \leftarrow -(M) = \$00 - (M) \end{array}$ | 1           | - | _ | 1 | 1        | 1 | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 30<br>40<br>50<br>60<br>70<br>9E60               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| NOP                                                                                            | No Operation                        | None                                                                                                                                                                                                  | -           | _ | - | - | -        | - | INH                                                 | 9D                                               |                                                 | 1                                    |

| NSA                                                                                            | Nibble Swap A                       | A ← (A[3:0]:A[7:4])                                                                                                                                                                                   | -           | _ | - | _ | _        | _ | INH                                                 | 62                                               |                                                 | 3                                    |

| ORA #opr<br>ORA opr<br>ORA opr<br>ORA opr,X<br>ORA opr,X<br>ORA,X<br>ORA opr,SP<br>ORA opr,SP  | Inclusive OR A and M                | A ← (A)   (M)                                                                                                                                                                                         | 0           | _ | _ | 1 | 1        | - | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | AA<br>BA<br>CA<br>DA<br>EA<br>FA<br>9EEA<br>9EDA |                                                 | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| PSHA                                                                                           | Push A onto Stack                   | Push (A); SP ← (SP) – 1                                                                                                                                                                               | _           | _ | _ | _ | _        | _ | INH                                                 | 87                                               |                                                 | 2                                    |

| PSHH                                                                                           | Push H onto Stack                   | Push (H); SP ← (SP) – 1                                                                                                                                                                               | -           | _ | - | _ | -        | _ | INH                                                 | 8B                                               |                                                 | 2                                    |

| PSHX                                                                                           | Push X onto Stack                   | Push (X); SP $\leftarrow$ (SP) – 1                                                                                                                                                                    | -           | _ | _ | _ | _        | - | INH                                                 | 89                                               |                                                 | 2                                    |

### MC68HC908GR8A • MC68HC908GR4A Data Sheet, Rev. 5

# **Chapter 9 Keyboard Interrupt Module (KBI)**

### 9.1 Introduction

The keyboard interrupt module (KBI) provides four independently maskable external interrupts which are accessible via PTA0-PTA3. When a port pin is enabled for keyboard interrupt function, an internal pullup device is also enabled on the pin.

### 9.2 Features

Features include:

- Four keyboard interrupt pins with separate keyboard interrupt enable bits and one keyboard interrupt mask

- Hysteresis buffers

- Programmable edge-only or edge- and level- interrupt sensitivity

- Exit from low-power modes

- I/O (input/output) port bit(s) software configurable with pullup device(s) if configured as input port bit(s)

## 9.3 Functional Description

Writing to the KBIE3–KBIE0 bits in the keyboard interrupt enable register independently enables or disables each port A pin as a keyboard interrupt pin. Enabling a keyboard interrupt pin also enables its internal pullup device. A low level applied to an enabled keyboard interrupt pin latches a keyboard interrupt request.

A keyboard interrupt is latched when one or more keyboard pins goes low after all were high. The MODEK bit in the keyboard status and control register controls the triggering mode of the keyboard interrupt.

- If the keyboard interrupt is edge-sensitive only, a falling edge on a keyboard pin does not latch an interrupt request if another keyboard pin is already low. To prevent losing an interrupt request on one pin because another pin is still low, software can disable the latter pin while it is low.

- If the keyboard interrupt is falling edge- and low-level sensitive, an interrupt request is present as long as any keyboard interrupt pin is low and the pin is keyboard interrupt enabled.

99

## Chapter 11 Low-Voltage Inhibit (LVI)

### 11.1 Introduction

This section describes the low-voltage inhibit (LVI) module, which monitors the voltage on the  $V_{DD}$  pin and can force a reset when the  $V_{DD}$  voltage falls below the LVI trip falling voltage,  $V_{TRIPF}$ .

### 11.2 Features

Features of the LVI module include:

- Programmable LVI reset

- Selectable LVI trip voltage

- Programmable stop mode operation

## 11.3 Functional Description

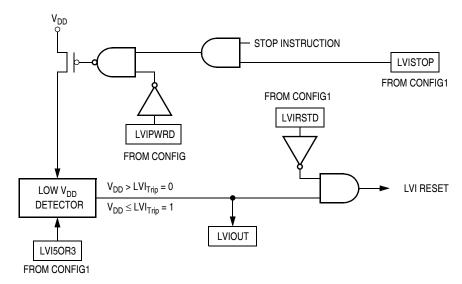

Figure 11-1 shows the structure of the LVI module. The LVI is enabled out of reset. The LVI module contains a bandgap reference circuit and comparator. Clearing the LVI power disable bit, LVIPWRD, enables the LVI to monitor  $V_{DD}$  voltage. Clearing the LVI reset disable bit, LVIRSTD, enables the LVI module to generate a reset when  $V_{DD}$  falls below a voltage,  $V_{TRIPF}$ . Setting the LVI enable in stop mode bit, LVISTOP, enables the LVI to operate in stop mode. Setting the LVI 5-V or 3-V trip point bit, LVI5OR3, enables the trip point voltage,  $V_{TRIPF}$ , to be configured for 5-V operation. Clearing the LVI5OR3 bit enables the trip point voltage,  $V_{TRIPF}$ , to be configured for 3-V operation. The actual trip points are shown in Chapter 19 Electrical Specifications.

### **NOTE**

After a power-on reset (POR) the LVI's default mode of operation is 3 V. If a 5-V system is used, the user must set the LVI5OR3 bit to raise the trip point to 5-V operation. Note that this must be done after every power-on reset since the default will revert back to 3-V mode after each power-on reset. If the  $V_{DD}$  supply is below the 5-V mode trip voltage but above the 3-V mode trip voltage when POR is released, the part will operate because  $V_{TRIPF}$  defaults to 3-V mode after a POR. So, in a 5-V system care must be taken to ensure that  $V_{DD}$  is above the 5-V mode trip voltage after POR is released.

If the user requires 5-V mode and sets the LVI5OR3 bit after a power-on reset while the  $V_{DD}$  supply is not above the  $V_{TRIPR}$  for 5-V mode, the microcontroller unit (MCU) will immediately go into reset. The LVI in this case will hold the part in reset until either  $V_{DD}$  goes above the rising 5-V trip point,  $V_{TRIPR}$ , which will release reset or  $V_{DD}$  decreases to approximately 0 V which will re-trigger the power-on reset and reset the trip point to 3-V operation.

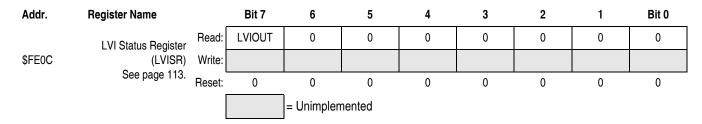

### Low-Voltage Inhibit (LVI)

LVISTOP, LVIPWRD, LVI5OR3, and LVIRSTD are in the configuration register (CONFIG1). See Figure 5-2. Configuration Register 1 (CONFIG1) for details of the LVI's configuration bits. Once an LVI reset occurs, the MCU remains in reset until  $V_{DD}$  rises above a voltage,  $V_{TRIPR}$ , which causes the MCU to exit reset. See 14.3.2.5 Low-Voltage Inhibit (LVI) Reset for details of the interaction between the SIM and the LVI. The output of the comparator controls the state of the LVIOUT flag in the LVI status register (LVISR).

An LVI reset also drives the RST pin low to provide low-voltage protection to external peripheral devices.

Figure 11-1. LVI Module Block Diagram

Figure 11-2. LVI I/O Register Summary

### 11.3.1 Polled LVI Operation

In applications that can operate at  $V_{DD}$  levels below the  $V_{TRIPF}$  level, software can monitor  $V_{DD}$  by polling the LVIOUT bit. In the configuration register, the LVIPWRD bit must be 0 to enable the LVI module, and the LVIRSTD bit must be at 1 to disable LVI resets.

### 11.3.2 Forced Reset Operation

In applications that require  $V_{DD}$  to remain above the  $V_{TRIPF}$  level, enabling LVI resets allows the LVI module to reset the MCU when  $V_{DD}$  falls below the  $V_{TRIPF}$  level. In the configuration register, the LVIPWRD and LVIRSTD bits must be cleared to enable the LVI module and to enable LVI resets.

MC68HC908GR8A • MC68HC908GR4A Data Sheet, Rev. 5

Low-Voltage Inhibit (LVI)

### **11.6.1 Wait Mode**

If enabled, the LVI module remains active in wait mode. If enabled to generate resets, the LVI module can generate a reset and bring the MCU out of wait mode.

## 11.6.2 Stop Mode

If enabled in stop mode (LVISTOP bit in the configuration register is set), the LVI module remains active in stop mode. If enabled to generate resets, the LVI module can generate a reset and bring the MCU out of stop mode.

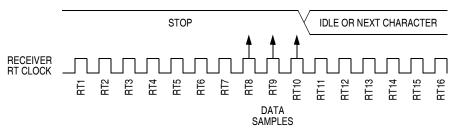

### **Fast Data Tolerance**

Figure 13-9 shows how much a fast received character can be misaligned without causing a noise error or a framing error. The fast stop bit ends at RT10 instead of RT16 but is still there for the stop bit data samples at RT8, RT9, and RT10.

Figure 13-9. Fast Data

For an 8-bit character, data sampling of the stop bit takes the receiver 9 bit times  $\times$  16 RT cycles + 10 RT cycles = 154 RT cycles.

With the misaligned character shown in Figure 13-9, the receiver counts 154 RT cycles at the point when the count of the transmitting device is 10 bit times  $\times$  16 RT cycles = 160 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 8-bit character with no errors is

$$\left| \frac{154 - 160}{154} \right| \times 100 = 3.90\%$$

For a 9-bit character, data sampling of the stop bit takes the receiver 10 bit times  $\times$  16 RT cycles + 10 RT cycles = 170 RT cycles.

With the misaligned character shown in Figure 13-9, the receiver counts 170 RT cycles at the point when the count of the transmitting device is 11 bit times  $\times$  16 RT cycles = 176 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 9-bit character with no errors is

$$\left| \frac{170 - 176}{170} \right| \times 100 = 3.53\%$$

### 13.4.3.6 Receiver Wakeup

So that the MCU can ignore transmissions intended only for other receivers in multiple-receiver systems, the receiver can be put into a standby state. Setting the receiver wakeup bit, RWU, in SCC2 puts the receiver into a standby state during which receiver interrupts are disabled.

Depending on the state of the WAKE bit in SCC1, either of two conditions on the PTE1/RxD pin can bring the receiver out of the standby state:

• Address mark — An address mark is a 1 in the most significant bit position of a received character. When the WAKE bit is set, an address mark wakes the receiver from the standby state by clearing the RWU bit. The address mark also sets the SCI receiver full bit, SCRF. Software can then compare the character containing the address mark to the user-defined address of the receiver. If they are the same, the receiver remains awake and processes the characters that follow. If they are not the same, software can set the RWU bit and put the receiver back into the standby state.

### Serial Peripheral Interface (SPI) Module

In a master SPI with the mode fault enable bit (MODFEN) set, the mode fault flag (MODF) is set if SS goes low. A mode fault in a master SPI causes the following events to occur:

- If ERRIE = 1, the SPI generates an SPI receiver/error CPU interrupt request.

- The SPE bit is cleared.

- The SPTE bit is set.

- The SPI state counter is cleared.

- The data direction register of the shared I/O port regains control of port drivers.

### NOTE

To prevent bus contention with another master SPI after a mode fault error, clear all SPI bits of the data direction register of the shared I/O port before enabling the SPI.

When configured as a slave (SPMSTR = 0), the MODF flag is set if  $\overline{SS}$  goes high during a transmission. When CPHA = 0, a transmission begins when  $\overline{SS}$  goes low and ends once the incoming SPSCK goes back to its idle level following the shift of the eighth data bit. When CPHA = 1, the transmission begins when the SPSCK leaves its idle level and  $\overline{SS}$  is already low. The transmission continues until the SPSCK returns to its idle level following the shift of the last data bit. See 15.4 Transmission Formats.

### NOTE

Setting the MODF flag does not clear the SPMSTR bit. SPMSTR has no function when SPE = 0. Reading SPMSTR when MODF = 1 shows the difference between a MODF occurring when the SPI is a master and when it is a slave.

### NOTE

When CPHA = 0, a MODF occurs if a slave is selected  $(\overline{SS})$  is low) and later unselected  $(\overline{SS})$  is high) even if no SPSCK is sent to that slave. This happens because  $\overline{SS}$  low indicates the start of the transmission (MISO driven out with the value of MSB) for CPHA = 0. When CPHA = 1, a slave can be selected and then later unselected with no transmission occurring. Therefore, MODF does not occur since a transmission was never begun.

In a slave SPI (MSTR = 0), MODF generates an SPI receiver/error CPU interrupt request if the ERRIE bit is set. The MODF bit does not clear the SPE bit or reset the SPI in any way. Software can abort the SPI transmission by clearing the SPE bit of the slave.

### NOTE

A high on the  $\overline{SS}$  pin of a slave SPI puts the MISO pin in a high impedance state. Also, the slave SPI ignores all incoming SPSCK clocks, even if it was already in the middle of a transmission.

To clear the MODF flag, read the SPSCR with the MODF bit set and then write to the SPCR register. This entire clearing mechanism must occur with no MODF condition existing or else the flag is not cleared.

## 15.7 Interrupts

Four SPI status flags can be enabled to generate CPU interrupt requests. See Table 15-1.

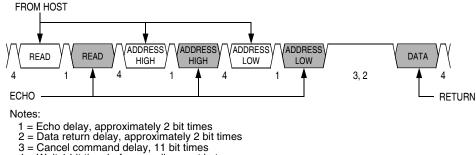

- 4 = Wait 1 bit time before sending next byte.

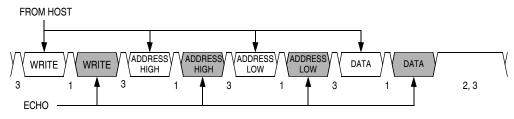

Figure 18-14. Read Transaction

- Notes

- 1 = Echo delay, approximately 2 bit times 2 = Cancel command delay, 11 bit times

- 3 = Wait 1 bit time before sending next byte.

Figure 18-15. Write Transaction

A brief description of each monitor mode command is given in Table 18-3 through Table 18-8.

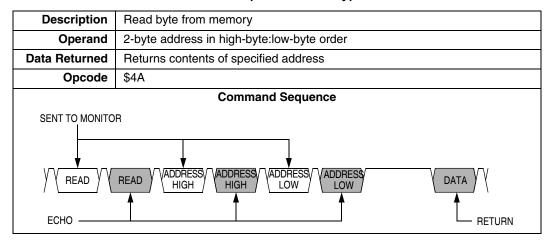

Table 18-3. READ (Read Memory) Command

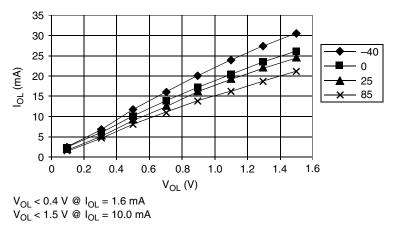

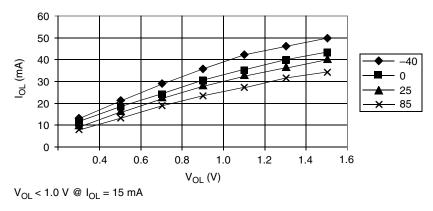

## 19.10 Output Low-Voltage Characteristics

Figure 19-7. Typical Low-Side Driver Characteristics — Port PTA3–PTA0 (V<sub>DD</sub> = 5.5 Vdc)

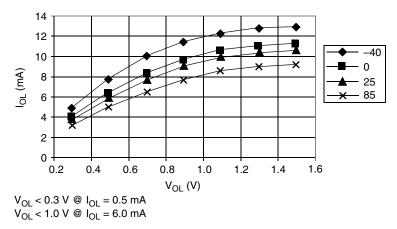

Figure 19-8. Typical Low-Side Driver Characteristics — Port PTA3–PTA0 (V<sub>DD</sub> = 2.7 Vdc)

Figure 19-9. Typical Low-Side Driver Characteristics — Port PTC1–PTC0 ( $V_{DD} = 4.5 \text{ Vdc}$ )

## 19.15 Clock Generation Module Characteristics

## 19.15.1 CGM Component Specifications

| Characteristic                             | Symbol         | Min | Тур            | Max | Unit |

|--------------------------------------------|----------------|-----|----------------|-----|------|

| Crystal reference frequency <sup>(1)</sup> | fXCLK          | 1   | 4              | 8   | MHz  |

| Crystal load capacitance <sup>(2)</sup>    | CL             | _   | 20             | _   | pF   |

| Crystal fixed capacitance <sup>(2)</sup>   | C <sub>1</sub> | _   | $2 \times C_L$ | _   | pF   |

| Crystal tuning capacitance <sup>(2)</sup>  | C <sub>2</sub> | _   | $2 \times C_L$ | _   | pF   |

| Feedback bias resistor                     | R <sub>B</sub> | 0.5 | 1              | 10  | ΜΩ   |

| Series resistor                            | R <sub>S</sub> | _   | 0              | _   | Ω    |

<sup>1.</sup> Fundamental mode crystals only

## 19.15.2 CGM Electrical Specifications

| Description                                 | Symbol            | Min | Тур  | Max                                                   | Unit |

|---------------------------------------------|-------------------|-----|------|-------------------------------------------------------|------|

| Operating voltage                           | V <sub>DD</sub>   | 2.7 | _    | 5.5                                                   | V    |

| Operating temperature                       | T <sub>A</sub>    | -40 | 25   | 125                                                   | °C   |

| Crystal reference frequency                 | f <sub>RCLK</sub> | 1   | 4    | 8                                                     | MHz  |

| Range nominal multiplier                    | f <sub>NOM</sub>  | _   | 38.4 | _                                                     | kHz  |

| VCO center-of-range frequency               | f <sub>VRS</sub>  | 4   | _    | 40                                                    | MHz  |

| VCO range linear range multiplier           | L                 | 1   | _    | 255                                                   |      |

| VCO power-of-two range multiplier           | 2 <sup>E</sup>    | 1   | _    | 4                                                     |      |

| VCO multiply factor                         | N                 | 1   | _    | 4095                                                  |      |

| VCO prescale multiplier                     | 2 <sup>P</sup>    | 1   | 1    | 8                                                     |      |

| Reference divider factor                    | R                 | 1   | 1    | 15                                                    |      |

| VCO operating frequency                     | f <sub>VCLK</sub> | 4   | _    | 40                                                    | MHz  |

| Bus operating frequency (5-V operation)     | f <sub>BUS</sub>  | _   | _    | 8.2                                                   | MHz  |

| Bus frequency (3-V operation)               | f <sub>BUS</sub>  | _   | _    | 4.1                                                   | MHz  |

| Manual acquisition time                     | t <sub>Lock</sub> | _   | _    | 5                                                     | ms   |

| Automatic lock time                         | t <sub>Lock</sub> | _   | _    | 5                                                     | ms   |

| PLL jitter <sup>(1)</sup>                   | fJ                | 0   | _    | f <sub>RCLK</sub> x<br>0.025% x<br>2 <sup>P</sup> N/4 | Hz   |

| External clock input frequency PLL disabled | fosc              | dc  | _    | 32.8 M                                                | Hz   |

| External clock input frequency PLL enabled  | fosc              | 1   | 4    | 8                                                     | MHz  |

<sup>1.</sup> Deviation of average bus frequency over 2 ms. N = VCO multiplier.

<sup>2.</sup> Consult crystal manufacturer's data.