#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 4MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 12                                                                      |

| Program Memory Size        | 768B (512 x 12)                                                         |

| Program Memory Type        | ОТР                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 25 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6.25V                                                              |

| Data Converters            | -                                                                       |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 18-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c54-xt-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

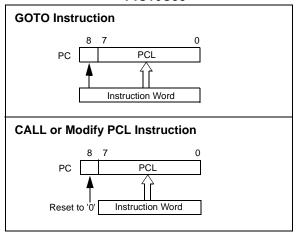

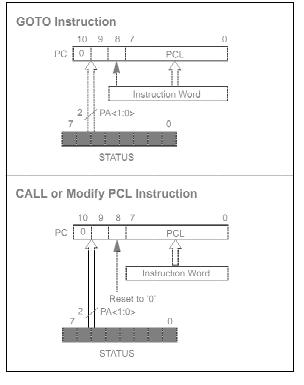

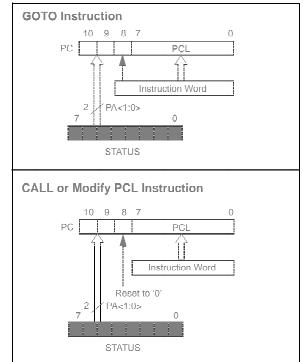

# 6.5 Program Counter

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one, every instruction cycle, unless an instruction changes the PC.

For a GOTO instruction, bits 8:0 of the PC are provided by the GOTO instruction word. The PC Latch (PCL) is mapped to PC<7:0> (Figure 6-7, Figure 6-8 and Figure 6-9).

For the PIC16C56, PIC16CR56, PIC16C57, PIC16CR57, PIC16C757, PIC16C58 and PIC16CR58, a page number must be supplied as well. Bit5 and bit6 of the STA-TUS Register provide page information to bit9 and bit10 of the PC (Figure 6-8 and Figure 6-9).

For a CALL instruction, or any instruction where the PCL is the destination, bits 7:0 of the PC again are provided by the instruction word. However, PC<8> does not come from the instruction word, but is always cleared (Figure 6-7 and Figure 6-8).

Instructions where the PCL is the destination, or modify PCL instructions, include MOVWF PCL, ADDWF PCL, and BSF PCL, 5.

For the PIC16C56, PIC16CR56, PIC16C57, PIC16CR57, PIC16C58 and PIC16CR58, a page number again must be supplied. Bit5 and bit6 of the STA-TUS Register provide page information to bit9 and bit10 of the PC (Figure 6-8 and Figure 6-9).

| Note: | Because PC<8> is cleared in the CALL           |

|-------|------------------------------------------------|

|       | instruction, or any modify PCL instruction,    |

|       | all subroutine calls or computed jumps are     |

|       | limited to the first 256 locations of any pro- |

|       | gram memory page (512 words long).             |

### FIGURE 6-7: LOADING OF PC BRANCH INSTRUCTIONS - PIC16C54, PIC16CR54, PIC16C55

### FIGURE 6-8:

### LOADING OF PC BRANCH INSTRUCTIONS - PIC16C56/PIC16CR56

FIGURE 6-9:

LOADING OF PC BRANCH INSTRUCTIONS - PIC16C57/PIC16CR57, AND PIC16C58/ PIC16CR58

NOTES:

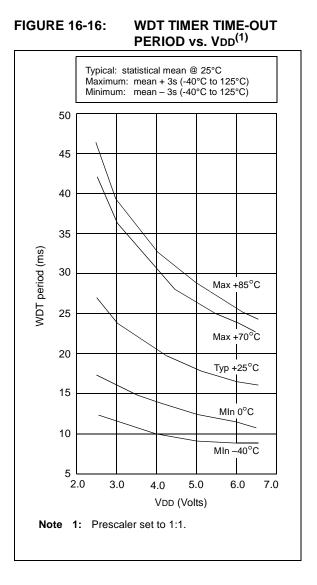

### 8.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer (WDT), respectively (Section 9.2.1). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT, but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the WDT, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a RESET, the prescaler contains all '0's.

### 8.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 8-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

### EXAMPLE 8-1: CHANGING PRESCALER (TIMER0→WDT)

| CLRWDT            | ;Clear WDT              |

|-------------------|-------------------------|

| CLRF TMR0         | Clear TMR0 & Prescaler  |

| MOVLW B'00xx1111' | ;Last 3 instructions in |

|                   | this example            |

| OPTION            | ;are required only if   |

|                   | ;desired                |

| CLRWDT            | ;PS<2:0> are 000 or     |

|                   | ;001                    |

| MOVLW B'00xx1xxx' | ;Set Prescaler to       |

| OPTION            | ;desired WDT rate       |

|                   |                         |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 8-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

# EXAMPLE 8-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| MOVLW  | B'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

|        |             | ;clock source       |

OPTION

### 9.1 Configuration Bits

Configuration bits can be programmed to select various device configurations. Two bits are for the selection of the oscillator type and one bit is the Watchdog Timer enable bit. Nine bits are code protection bits for the PIC16C54A, PIC16CR54A, PIC16C55A, PIC16C56A, PIC16CR56A, PIC16CR57C, PIC16CR57C, PIC16CR57C,

PIC16C58B, and PIC16CR58B devices (Register 9-1). One bit is for code protection for the PIC16C54, PIC16C55, PIC16C56 and PIC16C57 devices (Register 9-2).

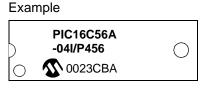

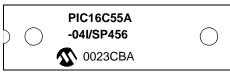

QTP or ROM devices have the oscillator configuration programmed at the factory and these parts are tested accordingly (see "Product Identification System" diagrams in the back of this data sheet).

### REGISTER 9-1: CONFIGURATION WORD FOR PIC16C54A/CR54A/C54C/CR54C/C55A/C56A/ CR56A/C57C/CR57C/C58B/CR58B

| CP     | CP | CP | CP | CP | CP | CP | CP | CP | WDTE | FOSC1 | FOSC0 |

|--------|----|----|----|----|----|----|----|----|------|-------|-------|

| bit 11 |    |    |    |    |    |    |    |    |      |       | bit 0 |

bit 11-3: CP: Code Protection Bit

- 1 = Code protection off

- 0 =Code protection on

- bit 2: WDTE: Watchdog timer enable bit

- 1 = WDT enabled

- 0 = WDT disabled

### bit 1-0: FOSC1:FOSC0: Oscillator Selection Bit

- 00 = LP oscillator

- 01 = XT oscillator

- 10 = HS oscillator

- 11 = RC oscillator

# **Note 1:** Refer to the PIC16C5X Programming Specification (Literature Number DS30190) to determine how to access the configuration word.

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared        | x = bit is unknown |

| BSF                                                        | Bit Set f                                                          |              |         |  |  |

|------------------------------------------------------------|--------------------------------------------------------------------|--------------|---------|--|--|

| Syntax:                                                    | [ label ]                                                          | BSF f,b      |         |  |  |

| Operands:                                                  | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |              |         |  |  |

| Operation:                                                 | $1 \rightarrow (f < b$                                             | >)           |         |  |  |

| Status Affected:                                           | None                                                               |              |         |  |  |

| Encoding:                                                  | 0101                                                               | bbbf         | ffff    |  |  |

| Description:                                               | Bit 'b' in ı                                                       | register 'f' | is set. |  |  |

| Words:                                                     | 1                                                                  |              |         |  |  |

| Cycles:                                                    | 1                                                                  |              |         |  |  |

| Example: BSF FLAG_REG, 7                                   |                                                                    |              |         |  |  |

| Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction |                                                                    |              |         |  |  |

| FLAG_F                                                     | REG = 0                                                            | IXOA         |         |  |  |

| BTFSC                                                  | Bit Test f, Skip if Clear                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                                | [label] BTFSC f,b                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Operands:                                              | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                                   |  |  |  |  |  |  |

| Operation:                                             | skip if $(f < b >) = 0$                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Status Affected:                                       | None                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Encoding:                                              | 0110 bbbf ffff                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Description:                                           | If bit 'b' in register 'f' is 0 then the<br>next instruction is skipped.<br>If bit 'b' is 0 then the next instruc-<br>tion fetched during the current<br>instruction execution is discarded,<br>and a NOP is executed instead,<br>making this a 2-cycle instruction. |  |  |  |  |  |  |

| Words:                                                 | 1                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Cycles:                                                | 1(2)                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Example:                                               | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                                                                                                                                                                                                          |  |  |  |  |  |  |

| Before Instru                                          | uction                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| PC<br>After Instruct<br>if FLAG<br>PC<br>if FLAG<br>PC | <pre>&lt;1&gt; = 0,<br/>= address (TRUE);</pre>                                                                                                                                                                                                                      |  |  |  |  |  |  |

| BTFSS                                    | Bit Test f, Skip if Set                                                                                                                                                                                                                                                   |                    |             |  |  |  |  |  |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|--|--|--|--|--|

| Syntax:                                  | [label]                                                                                                                                                                                                                                                                   | BTFSS f            | ,b          |  |  |  |  |  |

| Operands:                                |                                                                                                                                                                                                                                                                           | $0 \le f \le 31$   |             |  |  |  |  |  |

|                                          | 0 ≤ b < 7                                                                                                                                                                                                                                                                 |                    |             |  |  |  |  |  |

| Operation:                               | skip if (f<                                                                                                                                                                                                                                                               | :b>) = 1           |             |  |  |  |  |  |

| Status Affected:                         | None                                                                                                                                                                                                                                                                      |                    |             |  |  |  |  |  |

| Encoding:                                | 0111                                                                                                                                                                                                                                                                      | bbbf               | ffff        |  |  |  |  |  |

| Description:                             | If bit 'b' in register 'f' is '1' then the<br>next instruction is skipped.<br>If bit 'b' is '1', then the next instruc-<br>tion fetched during the current<br>instruction execution, is discarded<br>and a NOP is executed instead,<br>making this a 2-cycle instruction. |                    |             |  |  |  |  |  |

| Words:                                   | 1                                                                                                                                                                                                                                                                         |                    |             |  |  |  |  |  |

| Cycles:                                  | 1(2)                                                                                                                                                                                                                                                                      |                    |             |  |  |  |  |  |

| Example:                                 | HERE BTFSS FLAG,1<br>FALSE GOTO PROCESS_CO<br>TRUE •<br>•                                                                                                                                                                                                                 |                    |             |  |  |  |  |  |

| Before Instruction                       |                                                                                                                                                                                                                                                                           |                    |             |  |  |  |  |  |

| PC<br>After Instru                       | =                                                                                                                                                                                                                                                                         | addres             | SS (HERE)   |  |  |  |  |  |

| After Instru<br>If FLAG<br>PC<br>if FLAG | <1> =                                                                                                                                                                                                                                                                     | 0,<br>addres<br>1, | SS (FALSE); |  |  |  |  |  |

| PC                                       | =                                                                                                                                                                                                                                                                         | addres             | SS (TRUE)   |  |  |  |  |  |

### 11.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can also link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian is a librarian for precompiled code to be used with the MPLINK object linker. When a routine from a library is called from another source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. The MPLIB object librarian manages the creation and modification of library files.

The MPLINK object linker features include:

- Integration with MPASM assembler and MPLAB C17 and MPLAB C18 C compilers.

- Allows all memory areas to be defined as sections to provide link-time flexibility.

The MPLIB object librarian features include:

- Easier linking because single libraries can be included instead of many smaller files.

- Helps keep code maintainable by grouping related modules together.

- Allows libraries to be created and modules to be added, listed, replaced, deleted or extracted.

# 11.5 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC-hosted environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user-defined key press, to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and the MPLAB C18 C compilers and the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent multiproject software development tool.

## 11.6 MPLAB ICE High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB ICE universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers (MCUs). Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE in-circuit emulator system has been designed as a real-time emulation system, with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows environment were chosen to best make these features available to you, the end user.

# 11.7 ICEPIC In-Circuit Emulator

The ICEPIC low cost, in-circuit emulator is a solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X and PIC16CXXX families of 8-bit One-Time-Programmable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules, or daughter boards. The emulator is capable of emulating without target application circuitry being present.

### 12.1 DC Characteristics: PIC16C54/55/56/57-RC, XT, 10, HS, LP (Commercial)

| PIC16C54/55/56/57-RC, XT, 10, HS, LP<br>(Commercial) |        | Standard Operating Conditions (unless otherwise specified Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial    |                                 |                                       |                                    |                            |                                                                                                                                                                                                          |

|------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------|------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                                         | Symbol | Characteristic/Device                                                                                                                  | Min                             | Тур†                                  | Max                                | Units                      | Conditions                                                                                                                                                                                               |

| D001                                                 | Vdd    | Supply Voltage<br>PIC16C5X-RC<br>PIC16C5X-XT<br>PIC16C5X-10<br>PIC16C5X-HS<br>PIC16C5X-LP                                              | 3.0<br>3.0<br>4.5<br>4.5<br>2.5 |                                       | 6.25<br>6.25<br>5.5<br>5.5<br>6.25 | V<br>V<br>V<br>V           |                                                                                                                                                                                                          |

| D002                                                 | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>                                                                                              | _                               | 1.5*                                  | _                                  | V                          | Device in SLEEP Mode                                                                                                                                                                                     |

| D003                                                 | VPOR   | VDD Start Voltage to ensure<br>Power-on Reset                                                                                          |                                 | Vss                                   | —                                  | V                          | See Section 5.1 for details on<br>Power-on Reset                                                                                                                                                         |

| D004                                                 | SVDD   | VDD Rise Rate to ensure<br>Power-on Reset                                                                                              | 0.05*                           |                                       | —                                  | V/ms                       | See Section 5.1 for details on<br>Power-on Reset                                                                                                                                                         |

| D010                                                 | IDD    | Supply Current <sup>(2)</sup><br>PIC16C5X-RC <sup>(3)</sup><br>PIC16C5X-XT<br>PIC16C5X-10<br>PIC16C5X-HS<br>PIC16C5X-HS<br>PIC16C5X-LP | <br>                            | 1.8<br>1.8<br>4.8<br>4.8<br>9.0<br>15 | 3.3<br>3.3<br>10<br>10<br>20<br>32 | mA<br>mA<br>mA<br>mA<br>μA | Fosc = 4 MHz, VDD = $5.5V$<br>Fosc = 4 MHz, VDD = $5.5V$<br>Fosc = 10 MHz, VDD = $5.5V$<br>Fosc = 10 MHz, VDD = $5.5V$<br>Fosc = 20 MHz, VDD = $5.5V$<br>Fosc = $32$ kHz, VDD = $3.0V$ ,<br>WDT disabled |

| D020                                                 | Ipd    | Power-down Current <sup>(2)</sup>                                                                                                      | _                               | 4.0<br>0.6                            | 12<br>9                            | μΑ<br>μΑ                   | VDD = 3.0V, WDT enabled<br>VDD = 3.0V, WDT disabled                                                                                                                                                      |

\* These parameters are characterized but not tested.

† Data in "Typ" column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

**Note 1:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- **3:** Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

# 13.5 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. Tp | ρS                                      |                    |

|-------|-----------------------------------------|--------------------|

| Т     |                                         |                    |

| F     | Frequency                               | T Time             |

| Lowe  | ercase letters (pp) and their meanings: |                    |

| рр    |                                         |                    |

| 2     | to                                      | mc MCLR            |

| ck    | CLKOUT                                  | osc oscillator     |

| су    | cycle time                              | os OSC1            |

| drt   | device reset timer                      | t0 T0CKI           |

| io    | I/O port                                | wdt watchdog timer |

| Uppe  | ercase letters and their meanings:      |                    |

| S     |                                         |                    |

| F     | Fall                                    | P Period           |

| н     | High                                    | R Rise             |

| T     | Invalid (Hi-impedance)                  | V Valid            |

| L     | Low                                     | Z Hi-impedance     |

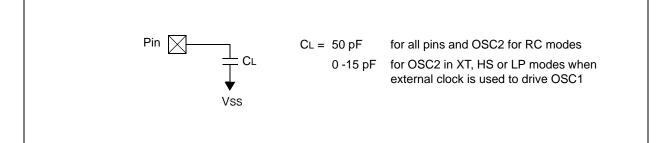

### FIGURE 13-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS - PIC16CR54A

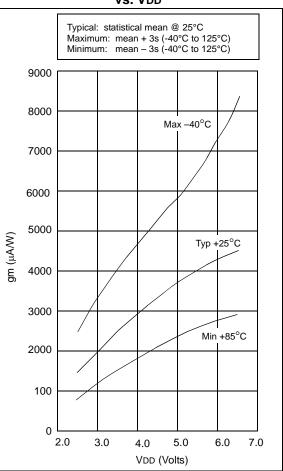

### FIGURE 16-17: TRANSCONDUCTANCE (gm) OF HS OSCILLATOR vs. VDD

TABLE 16-2:INPUT CAPACITANCE FOR<br/>PIC16C54A/C58A

| Pin         | Typical Capacitance (pF) |          |  |  |

|-------------|--------------------------|----------|--|--|

| FIII        | 18L PDIP                 | 18L SOIC |  |  |

| RA port     | 5.0                      | 4.3      |  |  |

| RB port     | 5.0                      | 4.3      |  |  |

| MCLR        | 17.0                     | 17.0     |  |  |

| OSC1        | 4.0                      | 3.5      |  |  |

| OSC2/CLKOUT | 4.3                      | 3.5      |  |  |

| TOCKI       | 3.2                      | 2.8      |  |  |

All capacitance values are typical at 25°C. A part-to-part variation of  $\pm 25\%$  (three standard deviations) should be taken into account.

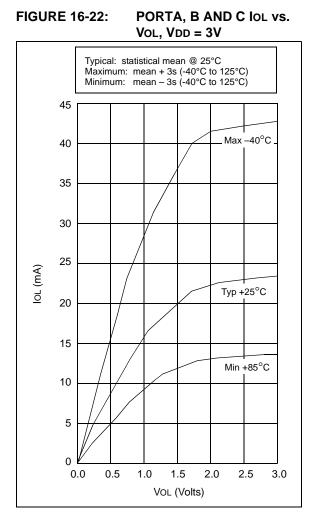

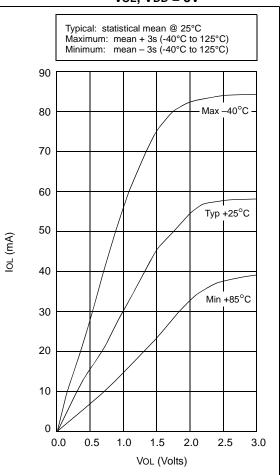

### FIGURE 16-23: PORTA, B AND C IOL vs. VoL, VDD = 5V

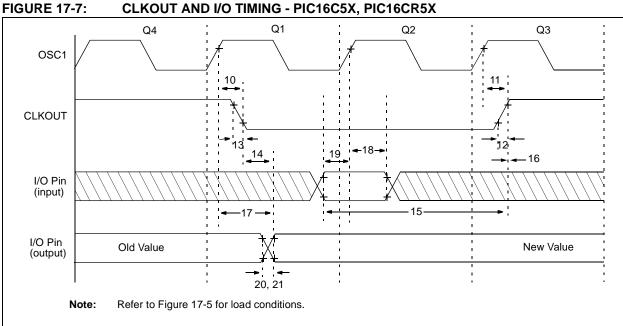

| AC Chara     | acteristics | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \\ \end{array} $ |              |      |      |       |  |  |  |

|--------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|-------|--|--|--|

| Param<br>No. | Symbol      | Characteristic                                                                                                                                                                                                                                                                                                                        | Min          | Тур† | Max  | Units |  |  |  |

| 10           | TosH2ckL    | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                                                                                                                                                                                                                                                                                                       | _            | 15   | 30** | ns    |  |  |  |

| 11           | TosH2ckH    | OSC1↑ to CLKOUT↑ <sup>(1)</sup>                                                                                                                                                                                                                                                                                                       | _            | 15   | 30** | ns    |  |  |  |

| 12           | TckR        | CLKOUT rise time <sup>(1)</sup>                                                                                                                                                                                                                                                                                                       | —            | 5.0  | 15** | ns    |  |  |  |

| 13           | TckF        | CLKOUT fall time <sup>(1)</sup>                                                                                                                                                                                                                                                                                                       | —            | 5.0  | 15** | ns    |  |  |  |

| 14           | TckL2ioV    | CLKOUT↓ to Port out valid <sup>(1)</sup>                                                                                                                                                                                                                                                                                              | —            |      | 40** | ns    |  |  |  |

| 15           | TioV2ckH    | Port in valid before CLKOUT <sup>(1)</sup>                                                                                                                                                                                                                                                                                            | 0.25 TCY+30* |      | _    | ns    |  |  |  |

| 16           | TckH2iol    | Port in hold after CLKOUT <sup>(1)</sup>                                                                                                                                                                                                                                                                                              | 0*           |      | _    | ns    |  |  |  |

| 17           | TosH2ioV    | OSC1↑ (Q1 cycle) to Port out valid <sup>(2)</sup>                                                                                                                                                                                                                                                                                     | —            |      | 100* | ns    |  |  |  |

| 18           | TosH2iol    | OSC1↑ (Q2 cycle) to Port input invalid<br>(I/O in hold time)                                                                                                                                                                                                                                                                          | TBD          | —    | —    | ns    |  |  |  |

| 19           | TioV2osH    | Port input valid to OSC1↑<br>(I/O in setup time)                                                                                                                                                                                                                                                                                      | TBD          |      | _    | ns    |  |  |  |

| 20           | TioR        | Port output rise time <sup>(2)</sup>                                                                                                                                                                                                                                                                                                  | _            | 10   | 25** | ns    |  |  |  |

| 21           | TioF        | Port output fall time <sup>(2)</sup>                                                                                                                                                                                                                                                                                                  | —            | 10   | 25** | ns    |  |  |  |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested. No characterization data available at this time.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

**2:** Refer to Figure 17-5 for load conditions.

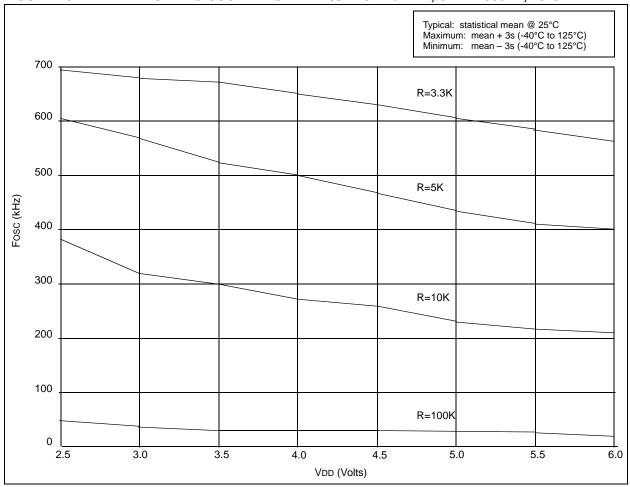

FIGURE 18-4: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD, CEXT = 300 PF, 25°C

© 1997-2013 Microchip Technology Inc.

# 19.1 DC Characteristics:PIC16C54C/C55A/C56A/C57C/C58B-40 (Commercial)<sup>(1)</sup>

| PIC16C54C/C55A/C56A/C57C/C58B-40<br>(Commercial) |                       |                                               |       | ard Ope<br>ing Tem | -          |          | itions (unless otherwise specified) $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |  |  |

|--------------------------------------------------|-----------------------|-----------------------------------------------|-------|--------------------|------------|----------|-----------------------------------------------------------------------------------------|--|--|

| Param<br>No.                                     | Sympol Characteristic |                                               | Min   | Тур†               | Max        | Units    | Conditions                                                                              |  |  |

| D001                                             | Vdd                   | Supply Voltage                                | 4.5   | -                  | 5.5        | V        | HS mode from 20 - 40 MHz                                                                |  |  |

| D002                                             | Vdr                   | RAM Data Retention Voltage <sup>(2)</sup>     |       | 1.5*               | —          | V        | Device in SLEEP mode                                                                    |  |  |

| D003                                             | VPOR                  | VDD Start Voltage to ensure<br>Power-on Reset | —     | Vss                | —          | V        | See Section 5.1 for details on<br>Power-on Reset                                        |  |  |

| D004                                             | SVDD                  | VDD Rise Rate to ensure Power-<br>on Reset    | 0.05* | _                  | —          | V/ms     | See Section 5.1 for details on<br>Power-on Reset                                        |  |  |

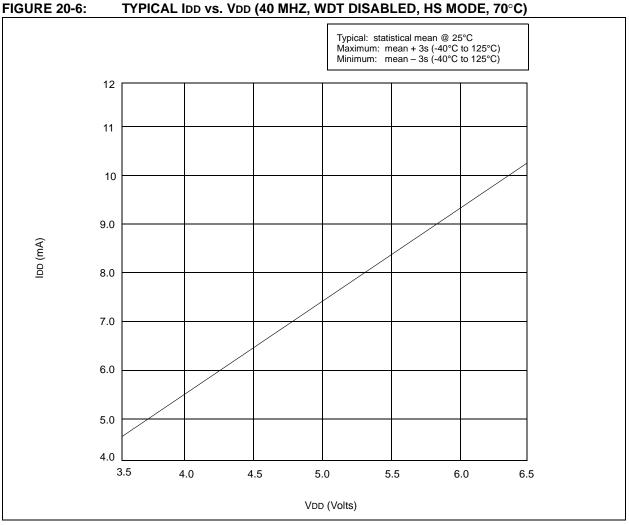

| D010                                             | Idd                   | Supply Current <sup>(3)</sup>                 | _     | 5.2<br>6.8         | 12.3<br>16 | mA<br>mA | Fosc = 40 MHz, VDD = $4.5V$ , HS mode<br>Fosc = 40 MHz, VDD = $5.5V$ , HS mode          |  |  |

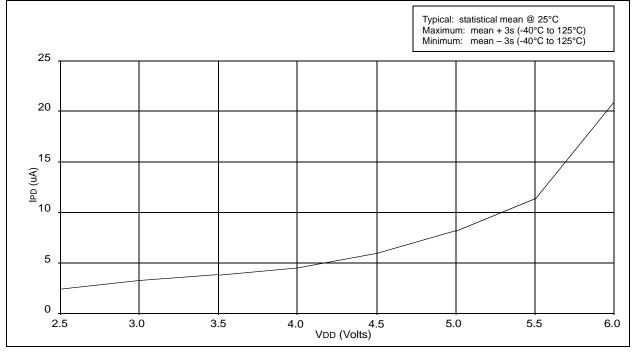

| D020                                             | IPD                   | Power-down Current <sup>(3)</sup>             | _     | 1.8<br>9.8         | 7.0<br>27* | μΑ<br>μΑ | VDD = 5.5V, WDT disabled, Commercial<br>VDD = 5.5V, WDT enabled, Commercial             |  |  |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** Device operation between 20 MHz to 40 MHz requires the following: VDD between 4.5V to 5.5V, OSC1 pin externally driven, OSC2 pin not connected, HS oscillator mode and commercial temperatures. For operation between DC and 20 MHz, See Section 19.1.

- **2:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

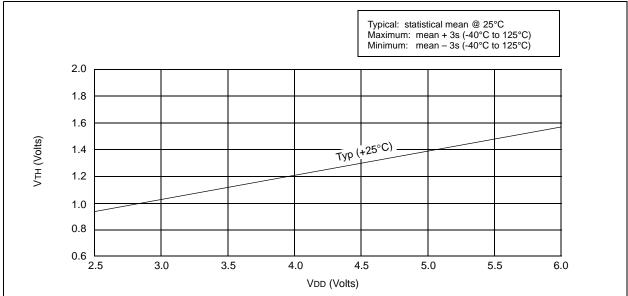

FIGURE 20-4: VTH (INPUT THRESHOLD TRIP POINT VOLTAGE) OF I/O PINS vs. VDD

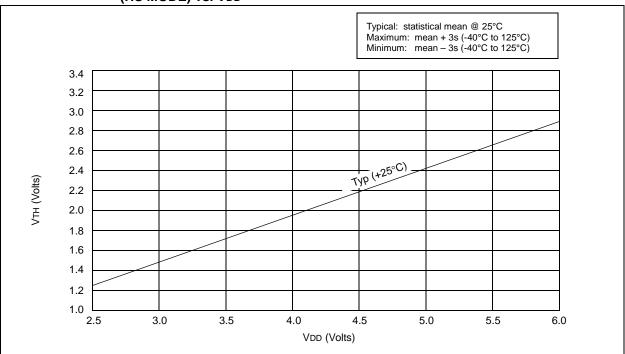

FIGURE 20-5: VTH (INPUT THRESHOLD TRIP POINT VOLTAGE) OF OSC1 INPUT (HS MODE) vs. VDD

# PIC16C5X

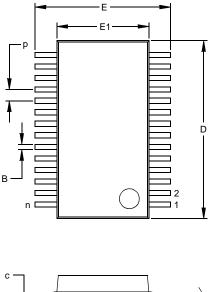

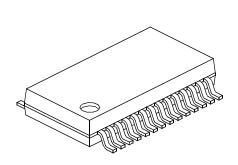

# 21.0 PACKAGING INFORMATION

# 21.1 Package Marketing Information

### 18-Lead PDIP

### 28-Lead Skinny PDIP (.300")

### 28-Lead PDIP (.600")

### 18-Lead SOIC

### 28-Lead SOIC

### 20-Lead SSOP

### 28-Lead SSOP

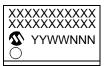

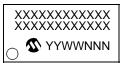

### Example

### Example

# Example

# Example

### Example

### Example

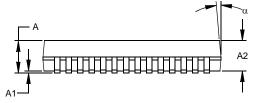

### 28-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    | INCHES |      |      | MILLIMETERS* |        |        |  |

|--------------------------|----------|--------|------|------|--------------|--------|--------|--|

| Dimensio                 | n Limits | MIN    | NOM  | MAX  | MIN          | NOM    | MAX    |  |

| Number of Pins           | n        |        | 28   |      |              | 28     |        |  |

| Pitch                    | р        |        | .026 |      |              | 0.65   |        |  |

| Overall Height           | А        | .068   | .073 | .078 | 1.73         | 1.85   | 1.98   |  |

| Molded Package Thickness | A2       | .064   | .068 | .072 | 1.63         | 1.73   | 1.83   |  |

| Standoff §               | A1       | .002   | .006 | .010 | 0.05         | 0.15   | 0.25   |  |

| Overall Width            | Е        | .299   | .309 | .319 | 7.59         | 7.85   | 8.10   |  |

| Molded Package Width     | E1       | .201   | .207 | .212 | 5.11         | 5.25   | 5.38   |  |

| Overall Length           | D        | .396   | .402 | .407 | 10.06        | 10.20  | 10.34  |  |

| Foot Length              | L        | .022   | .030 | .037 | 0.56         | 0.75   | 0.94   |  |

| Lead Thickness           | С        | .004   | .007 | .010 | 0.10         | 0.18   | 0.25   |  |

| Foot Angle               | ¢        | 0      | 4    | 8    | 0.00         | 101.60 | 203.20 |  |

| Lead Width               | В        | .010   | .013 | .015 | 0.25         | 0.32   | 0.38   |  |

| Mold Draft Angle Top     | α        | 0      | 5    | 10   | 0            | 5      | 10     |  |

| Mold Draft Angle Bottom  | β        | 0      | 5    | 10   | 0            | 5      | 10     |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-150 Drawing No. C04-073

# w

| W Register                 |        |

|----------------------------|--------|

| Value on reset             | 20     |

| Wake-up from SLEEP         | 19, 47 |

| Watchdog Timer (WDT)       | 43, 46 |

| Period                     |        |

| Programming Considerations |        |

| Register values on reset   |        |

| WWW, On-Line Support       |        |

| X                          |        |

| XORLW                      | 60     |

| XORWF                      |        |

| Z                          |        |

| Zero (Z) bit               | 9, 29  |

NOTES:

# **ON-LINE SUPPORT**

Microchip provides on-line support on the Microchip World Wide Web (WWW) site.

The web site is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

### Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

### ftp://ftp.microchip.com

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- Latest Microchip Press Releases

- Technical Support Section with Frequently Asked Questions

- Design Tips

- Device Errata

- Job Postings

- Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

- Conferences for products, Development Systems, technical information and more

- Listing of seminars and events