Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 768B (512 x 12)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 25 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c54a-04-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 4.0   |                                                                                        | -    |

|-------|----------------------------------------------------------------------------------------|------|

| 1.0   | General Description                                                                    |      |

| 2.0   | PIC16C5X Device Varieties                                                              |      |

| 3.0   | Architectural Overview                                                                 |      |

| 4.0   | Oscillator Configurations                                                              | . 15 |

| 5.0   | Reset                                                                                  | . 19 |

| 6.0   | Memory Organization                                                                    | . 25 |

| 7.0   | I/O Ports                                                                              | . 35 |

| 8.0   | Timer0 Module and TMR0 Register                                                        | . 37 |

| 9.0   | Special Features of the CPU                                                            | . 43 |

| 10.0  | Instruction Set Summary                                                                | . 49 |

| 11.0  | Development Support                                                                    | . 61 |

| 12.0  | Electrical Characteristics - PIC16C54/55/56/57                                         | . 67 |

| 13.0  | Electrical Characteristics - PIC16CR54A                                                |      |

| 14.0  | Device Characterization - PIC16C54/55/56/57/CR54A                                      | . 91 |

| 15.0  | Electrical Characteristics - PIC16C54A                                                 | 103  |

| 16.0  | Device Characterization - PIC16C54A                                                    | 117  |

| 17.0  | Electrical Characteristics - PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/C58B/CR58B     | 131  |

| 18.0  | Device Characterization - PIC16C54C/CR54C/C55A/C56A/CR56A/CR56A/CR57C/CR57C/C58B/CR58B | 145  |

| 19.0  | Electrical Characteristics - PIC16C54C/C55A/C56A/C57C/C58B 40MHz                       | 155  |

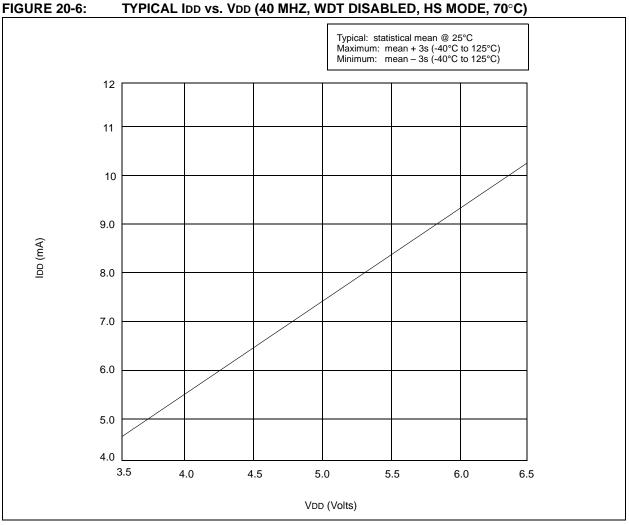

| 20.0  | Device Characterization - PIC16C54C/C55A/C56A/C57C/C58B 40MHz                          | 165  |

| 21.0  | Packaging Information                                                                  | 171  |

| Appe  | ndix A: Compatibility                                                                  | 182  |

| On-L  | ne Support                                                                             | 187  |

| Read  | er Response                                                                            | 188  |

| Produ | uct Identification System                                                              | 189  |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

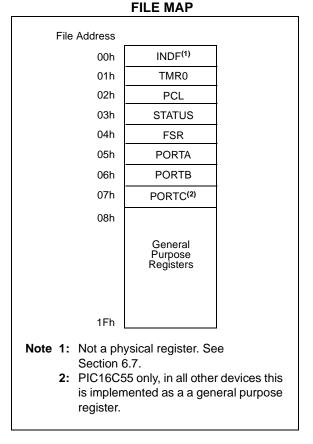

### 6.2 Data Memory Organization

Data memory is composed of registers, or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: Special Function Registers and General Purpose Registers.

The Special Function Registers include the TMR0 register, the Program Counter (PC), the Status Register, the I/O registers (ports) and the File Select Register (FSR). In addition, Special Purpose Registers are used to control the I/O port configuration and prescaler options.

The General Purpose Registers are used for data and control information under command of the instructions.

For the PIC16C54, PIC16CR54, PIC16C56 and PIC16CR56, the register file is composed of 7 Special Function Registers and 25 General Purpose Registers (Figure 6-4).

For the PIC16C55, the register file is composed of 8 Special Function Registers and 24 General Purpose Registers.

For the PIC16C57 and PIC16CR57, the register file is composed of 8 Special Function Registers, 24 General Purpose Registers and up to 48 additional General Purpose Registers that may be addressed using a banking scheme (Figure 6-5).

For the PIC16C58 and PIC16CR58, the register file is composed of 7 Special Function Registers, 25 General Purpose Registers and up to 48 additional General Purpose Registers that may be addressed using a banking scheme (Figure 6-6).

### 6.2.1 GENERAL PURPOSE REGISTER FILE

The register file is accessed either directly or indirectly through the File Select Register (FSR). The FSR Register is described in Section 6.7.

### FIGURE 6-4: PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56 REGISTER

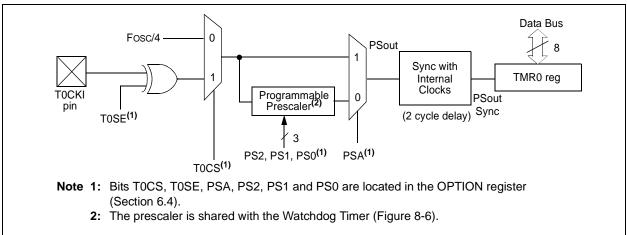

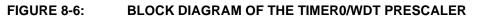

### 8.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Edge select for external clock

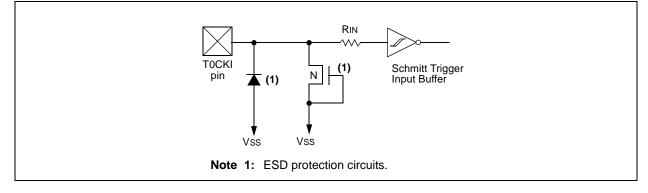

Figure 8-1 is a simplified block diagram of the Timer0 module, while Figure 8-2 shows the electrical structure of the Timer0 input.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 8-3 and Figure 8-4). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The incrementing edge is determined by the source edge select bit T0SE (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 8.1.

Note: The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both.

The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. Section 8.2 details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 8-1.

### FIGURE 8-2: ELECTRICAL STRUCTURE OF TOCKI PIN

#### CONFIGURATION WORD FOR PIC16C54/C55/C56/C57 **REGISTER 9-2:**

|           |            |             | İ            |            |                     |             | İ         | СР      | WDTE        | FOSC1      | FOSC0   |

|-----------|------------|-------------|--------------|------------|---------------------|-------------|-----------|---------|-------------|------------|---------|

|           |            | _           | _            | _          |                     |             |           | CP      | WDIE        | FUSCI      |         |

| bit 11    |            |             |              |            |                     |             |           |         |             |            | bit 0   |

|           |            |             |              |            |                     |             |           |         |             |            |         |

| bit 11-4: | Unimple    | mented      | Read as '    | 0'         |                     |             |           |         |             |            |         |

| bit 3:    | CP: Cod    | e protecti  | on bit.      |            |                     |             |           |         |             |            |         |

|           |            | e protecti  |              |            |                     |             |           |         |             |            |         |

|           | 0 = Code   | e protectio | on on        |            |                     |             |           |         |             |            |         |

| bit 2:    | WDTE: \    | Vatchdog    | timer ena    | ble bit    |                     |             |           |         |             |            |         |

|           | 1 = WDT    | enabled     |              |            |                     |             |           |         |             |            |         |

|           | 0 = WDT    | disabled    |              |            |                     |             |           |         |             |            |         |

| bit 1-0:  | FOSC1:I    | FOSC0: (    | Oscillator s | election b | oits <sup>(2)</sup> |             |           |         |             |            |         |

|           | 00 = LF    | oscillato   | or           |            |                     |             |           |         |             |            |         |

|           | 01 = X     | T oscillato | or           |            |                     |             |           |         |             |            |         |

|           |            | S oscillato |              |            |                     |             |           |         |             |            |         |

|           | 11 = R     | C oscillate | or           |            |                     |             |           |         |             |            |         |

| Note 1.   | Refer to t | ha PIC16    | C5X Prog     | rammina    | Specificat          | ions (Liter | atura Num | her DS3 | 190) to d   | otormino l | now to  |

|           |            |             | iration wor  | 0          | opeemear            |             |           |         | , 100) to u |            | 1011 10 |

| 2:        |            | •           | orts XT, R   |            | oscillator          | onlv.       |           |         |             |            |         |

|           |            |             |              |            |                     | - 1         |           |         |             |            |         |

| Legend:   |            |             |              |            |                     |             |           |         |             |            |         |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared                 | x = bit is unknown |  |

### 9.3 Power-Down Mode (SLEEP)

A device may be powered down (SLEEP) and later powered up (Wake-up from SLEEP).

### 9.3.1 SLEEP

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the TO bit (STATUS<4>) is set, the PD bit (STATUS<3>) is cleared and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, driving low, or hi-impedance).

It should be noted that a RESET generated by a WDT time-out does not drive the MCLR/VPP pin low.

For lowest current consumption while powered down, the T0CKI input should be at VDD or Vss and the  $\overline{\text{MCLR}}/\text{VPP}$  pin must be at a logic high level ( $\overline{\text{MCLR}} = \text{VIH}$ ).

### 9.3.2 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. An external RESET input on MCLR/VPP pin.

- 2. A Watchdog Timer Time-out Reset (if WDT was enabled).

Both of these events cause a device RESET. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits can be used to determine the cause of device RESET. The  $\overline{\text{TO}}$  bit is cleared if a WDT timeout occurred (and caused wake-up). The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked.

The WDT is cleared when the device wakes from SLEEP, regardless of the wake-up source.

### 9.4 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

### 9.5 ID Locations

Four memory locations are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify.

Use only the lower 4 bits of the ID locations and always program the upper 8 bits as '1's.

**Note:** Microchip will assign a unique pattern number for QTP and SQTP requests and for ROM devices. This pattern number will be unique and traceable to the submitted code.

# PIC16C5X

| IORLW                                               | Inclusive OR literal with W                                                                                                 |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                             | [ <i>label</i> ] IORLW k                                                                                                    |

| Operands:                                           | $0 \leq k \leq 255$                                                                                                         |

| Operation:                                          | (W) .OR. (k) $\rightarrow$ (W)                                                                                              |

| Status Affected:                                    | Z                                                                                                                           |

| Encoding:                                           | 1101 kkkk kkkk                                                                                                              |

| Description:                                        | The contents of the W register are<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W regis-<br>ter. |

| Words:                                              | 1                                                                                                                           |

| Cycles:                                             | 1                                                                                                                           |

| Example:                                            | IORLW 0x35                                                                                                                  |

| Before Instru<br>W =<br>After Instruc<br>W =<br>Z = | 0x9A<br>tion                                                                                                                |

| IORWF                                                            | Inclusive OR W with f                                                                                                                                                 |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                          | [ <i>label</i> ] IORWF f,d                                                                                                                                            |

| Operands:                                                        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                            |

| Operation:                                                       | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                                      |

| Status Affected:                                                 | Z                                                                                                                                                                     |

| Encoding:                                                        | 0001 00df ffff                                                                                                                                                        |

| Description:                                                     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |

| Words:                                                           | 1                                                                                                                                                                     |

| Cycles:                                                          | 1                                                                                                                                                                     |

| Example:                                                         | IORWF RESULT, 0                                                                                                                                                       |

| Before Instru<br>RESUL<br>W<br>After Instruct<br>RESUL<br>W<br>Z | Γ = 0x13<br>= 0x91<br>tion                                                                                                                                            |

| MOVF                  | Move f                                                                                                                                                                                                                                                 |  |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:               | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                              |  |  |  |  |

| Operands:             | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                                                                                         |  |  |  |  |

| Operation:            | $(f) \rightarrow (dest)$                                                                                                                                                                                                                               |  |  |  |  |

| Status Affected:      | Z                                                                                                                                                                                                                                                      |  |  |  |  |

| Encoding:             | 0010 00df ffff                                                                                                                                                                                                                                         |  |  |  |  |

| Description:          | The contents of register 'f' is<br>moved to destination 'd'. If 'd' is 0,<br>destination is the W register. If 'd'<br>is 1, the destination is file<br>register 'f'. 'd' is 1 is useful to test a<br>file register since status flag Z is<br>affected. |  |  |  |  |

| Words:                | 1                                                                                                                                                                                                                                                      |  |  |  |  |

| Cycles:               | 1                                                                                                                                                                                                                                                      |  |  |  |  |

| Example:              | MOVF FSR, 0                                                                                                                                                                                                                                            |  |  |  |  |

| After Instruct<br>W = | tion<br>- value in FSR register                                                                                                                                                                                                                        |  |  |  |  |

| MOVLW                         | Move Lit             | teral to W | I             |        |

|-------------------------------|----------------------|------------|---------------|--------|

| Syntax:                       | [ label ]            | MOVLW      | k             |        |

| Operands:                     | $0 \leq k \leq 2$    | 55         |               |        |

| Operation:                    | $k \rightarrow (W)$  |            |               |        |

| Status Affected:              | None                 |            |               |        |

| Encoding:                     | 1100                 | kkkk       | kkkk          |        |

| Description:                  | The eigh<br>the W re |            | 'k' is loaded | d into |

| Words:                        | 1                    |            |               |        |

| Cycles:                       | 1                    |            |               |        |

| Example:                      | MOVLW                | 0x5A       |               |        |

| After Instruction<br>W = 0x5A |                      |            |               |        |

# PIC16C5X

| XORLW                                         | Exclusiv        | e OR lite     | eral with                                 | w         |

|-----------------------------------------------|-----------------|---------------|-------------------------------------------|-----------|

| Syntax:                                       | [label]         | XORLW         | k                                         |           |

| Operands:                                     | $0 \le k \le 2$ | 55            |                                           |           |

| Operation:                                    | (W) .XOF        | $R. k \to (W$ | /)                                        |           |

| Status Affected:                              | Z               |               |                                           |           |

| Encoding:                                     | 1111            | kkkk          | kkkk                                      |           |

| Description:                                  | XOR'ed          | with the e    | e W regis<br>eight bit lit<br>ed in the V | eral 'k'. |

| Words:                                        | 1               |               |                                           |           |

| Cycles:                                       | 1               |               |                                           |           |

| Example:                                      | XORLW           | 0xAF          |                                           |           |

| Before Instru<br>W =<br>After Instruct<br>W = | 0xB5            |               |                                           |           |

| Exclusive OR W with f                                                                                                                                        |                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| [ label ] XORWF f,d                                                                                                                                          | -                                   |

| $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                   |                                     |

| (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                           |                                     |

| ted: Z                                                                                                                                                       |                                     |

| 0001 10df ffff                                                                                                                                               |                                     |

| W register with register 'f'. If 'd' is 0<br>the result is stored in the W regis-<br>ter. If 'd' is 1 the result is stored<br>back in register 'f'.          |                                     |

| 1                                                                                                                                                            |                                     |

| 1                                                                                                                                                            |                                     |

| XORWF REG,1                                                                                                                                                  |                                     |

| Instruction<br>G = 0xAF<br>= 0xB5<br>struction<br>G = 0x1A<br>= 0xB5                                                                                         |                                     |

| the result is stored in t<br>ter. If 'd' is 1 the result<br>back in register 'f'.<br>1<br>1<br>XORWF REG, 1<br>nstruction<br>G = 0xAF<br>= 0xB5<br>struction | er 'f'. If 'd' is 0<br>the W regis- |

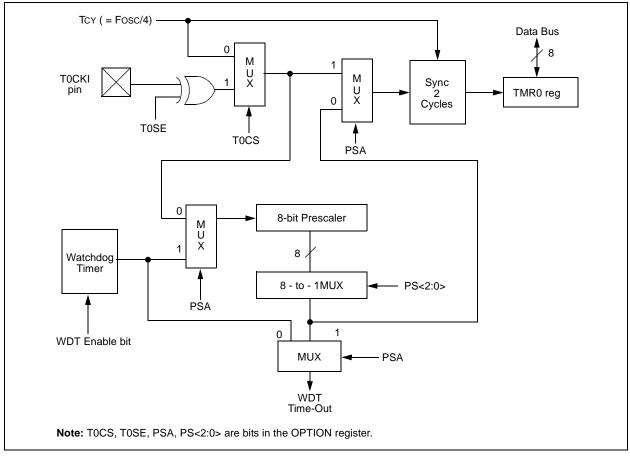

### TABLE 12-2: CLKOUT AND I/O TIMING REQUIREMENTS - PIC16C54/55/56/57

| AC Char      | acteristics | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |              |      |      |       |

|--------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|-------|

| Param<br>No. | Symbol      | Characteristic                                                                                                                                                                                                                                                                                                                   | Min          | Тур† | Max  | Units |

| 10           | TosH2ckL    | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                                                                                                                                                                                                                                                                                                  | _            | 15   | 30** | ns    |

| 11           | TosH2ckH    | OSC1↑ to CLKOUT↑ <sup>(1)</sup>                                                                                                                                                                                                                                                                                                  | _            | 15   | 30** | ns    |

| 12           | TckR        | CLKOUT rise time <sup>(1)</sup>                                                                                                                                                                                                                                                                                                  |              | 5.0  | 15** | ns    |

| 13           | TckF        | CLKOUT fall time <sup>(1)</sup>                                                                                                                                                                                                                                                                                                  | —            | 5.0  | 15** | ns    |

| 14           | TckL2ioV    | CLKOUT↓ to Port out valid <sup>(1)</sup>                                                                                                                                                                                                                                                                                         |              |      | 40** | ns    |

| 15           | TioV2ckH    | Port in valid before CLKOUT <sup>(1)</sup>                                                                                                                                                                                                                                                                                       | 0.25 TCY+30* | _    | _    | ns    |

| 16           | TckH2iol    | Port in hold after CLKOUT <sup>(1)</sup>                                                                                                                                                                                                                                                                                         | 0*           | _    | _    | ns    |

| 17           | TosH2ioV    | OSC1↑ (Q1 cycle) to Port out valid <sup>(2)</sup>                                                                                                                                                                                                                                                                                | _            |      | 100* | ns    |

| 18           | TosH2iol    | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid<br>(I/O in hold time)                                                                                                                                                                                                                                                         | TBD          | —    |      | ns    |

| 19           | TioV2osH    | Port input valid to OSC1↑<br>(I/O in setup time)                                                                                                                                                                                                                                                                                 | TBD          | —    | —    | ns    |

| 20           | TioR        | Port output rise time <sup>(2)</sup>                                                                                                                                                                                                                                                                                             | —            | 10   | 25** | ns    |

| 21           | TioF        | Port output fall time <sup>(2)</sup>                                                                                                                                                                                                                                                                                             | —            | 10   | 25** | ns    |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested. No characterization data available at this time.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

2: Please refer to Figure 12-1 for load conditions.

## 13.5 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. TppS |                                         |                    |  |  |  |  |  |

|---------|-----------------------------------------|--------------------|--|--|--|--|--|

| Т       |                                         |                    |  |  |  |  |  |

| F       | Frequency                               | T Time             |  |  |  |  |  |

| Lowe    | ercase letters (pp) and their meanings: |                    |  |  |  |  |  |

| рр      |                                         |                    |  |  |  |  |  |

| 2       | to                                      | mc MCLR            |  |  |  |  |  |

| ck      | CLKOUT                                  | osc oscillator     |  |  |  |  |  |

| су      | cycle time                              | os OSC1            |  |  |  |  |  |

| drt     | device reset timer                      | t0 T0CKI           |  |  |  |  |  |

| io      | I/O port                                | wdt watchdog timer |  |  |  |  |  |

| Uppe    | ercase letters and their meanings:      |                    |  |  |  |  |  |

| S       |                                         |                    |  |  |  |  |  |

| F       | Fall                                    | P Period           |  |  |  |  |  |

| н       | High                                    | R Rise             |  |  |  |  |  |

| I       | Invalid (Hi-impedance)                  | V Valid            |  |  |  |  |  |

| L       | Low                                     | Z Hi-impedance     |  |  |  |  |  |

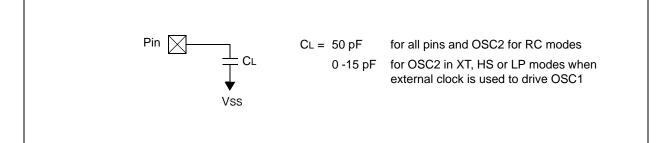

### FIGURE 13-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS - PIC16CR54A

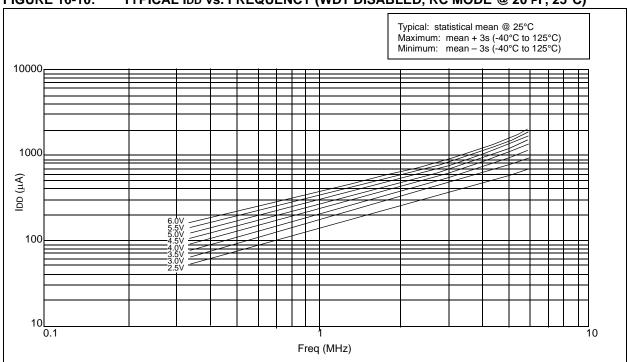

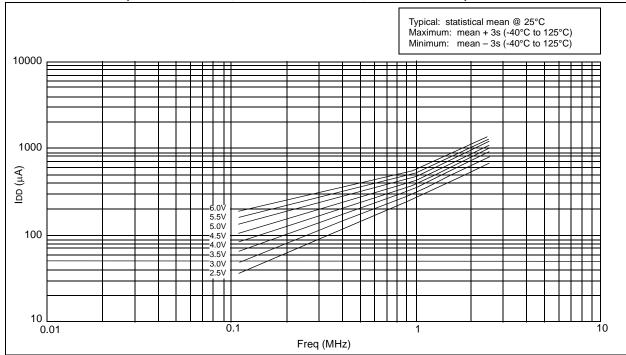

FIGURE 16-10: TYPICAL IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 20 PF, 25°C)

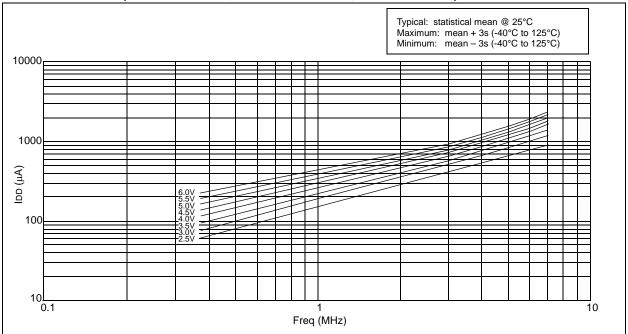

FIGURE 16-11: MAXIMUM IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 20 PF, -40°C to +85°C)

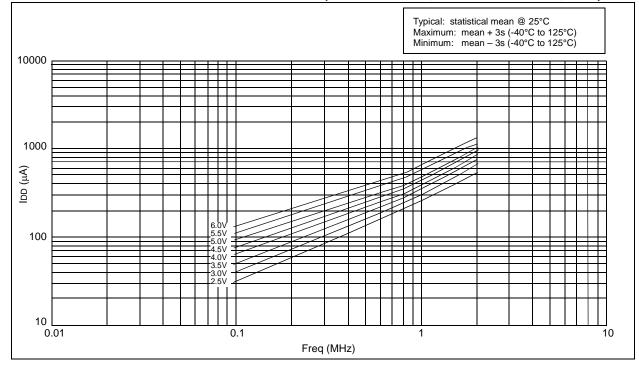

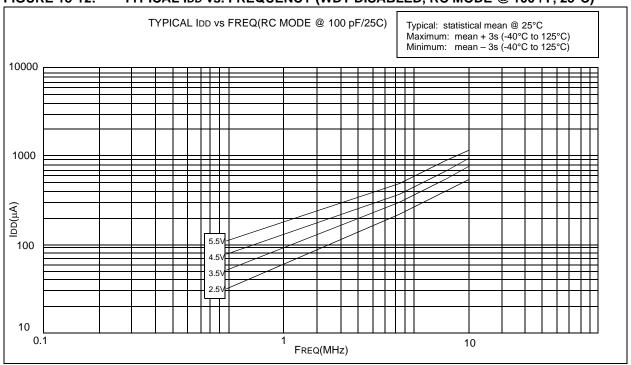

### FIGURE 16-12: TYPICAL IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 100 PF, 25°C)

FIGURE 16-13: MAXIMUM IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 100 PF, -40°C to +85°C)

### 17.1 DC Characteristics:PIC16C54C/C55A/C56A/C57C/C58B-04, 20 (Commercial, Industrial) PIC16LC54C/LC55A/LC56A/LC57C/LC58B-04 (Commercial, Industrial) PIC16CR54C/CR56A/CR57C/CR58B-04, 20 (Commercial, Industrial) PIC16LCR54C/LCR56A/LCR57C/LCR58B-04 (Commercial, Industrial)

| PIC16LC5X<br>PIC16LCR5X<br>(Commercial, Industrial)<br>PIC16C5X<br>PIC16CR5X<br>(Commercial, Industrial) |        |                                                | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrialStandard Operating Conditions (unless otherwise specified) |      |                   |             |                                                                                                                                                                                      |  |  |

|----------------------------------------------------------------------------------------------------------|--------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                          |        |                                                | Operating Temperature                                                                                                                                                                                                                               |      |                   |             | $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial<br>-40°C $\le TA \le +85^{\circ}C$ for industrial                                                                                |  |  |

| Param<br>No.                                                                                             | Symbol | Characteristic/Device                          | Min                                                                                                                                                                                                                                                 | Тур† | Max               | Units       | Conditions                                                                                                                                                                           |  |  |

|                                                                                                          | Vdd    | Supply Voltage                                 |                                                                                                                                                                                                                                                     |      |                   |             |                                                                                                                                                                                      |  |  |

| D001                                                                                                     |        | PIC16LC5X                                      | 2.5<br>2.7<br>2.5                                                                                                                                                                                                                                   |      | 5.5<br>5.5<br>5.5 | V<br>V<br>V | $\begin{array}{l} -40^{\circ}C \leq TA \leq +\ 85^{\circ}C,\ 16LCR5X \\ -40^{\circ}C \leq TA \leq 0^{\circ}C,\ 16LC5X \\ 0^{\circ}C \leq TA \leq +\ 85^{\circ}C\ 16LC5X \end{array}$ |  |  |

| D001A                                                                                                    |        | PIC16C5X                                       | 3.0<br>4.5                                                                                                                                                                                                                                          | _    | 5.5<br>5.5        | V<br>V      | RC, XT, LP and HS mode<br>from 0 - 10 MHz<br>from 10 - 20 MHz                                                                                                                        |  |  |

| D002                                                                                                     | Vdr    | RAM Data Retention Volt-<br>age <sup>(1)</sup> | —                                                                                                                                                                                                                                                   | 1.5* | —                 | V           | Device in SLEEP mode                                                                                                                                                                 |  |  |

| D003                                                                                                     | VPOR   | VDD Start Voltage to ensure<br>Power-on Reset  | —                                                                                                                                                                                                                                                   | Vss  | —                 | V           | See Section 5.1 for details on<br>Power-on Reset                                                                                                                                     |  |  |

| D004                                                                                                     | SVDD   | VDD Rise Rate to ensure<br>Power-on Reset      | 0.05*                                                                                                                                                                                                                                               | —    | —                 | V/ms        | See Section 5.1 for details on<br>Power-on Reset                                                                                                                                     |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

\* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- **3:** Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

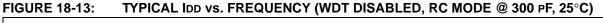

# 18.0 DEVICE CHARACTERIZATION - PIC16LC54A

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

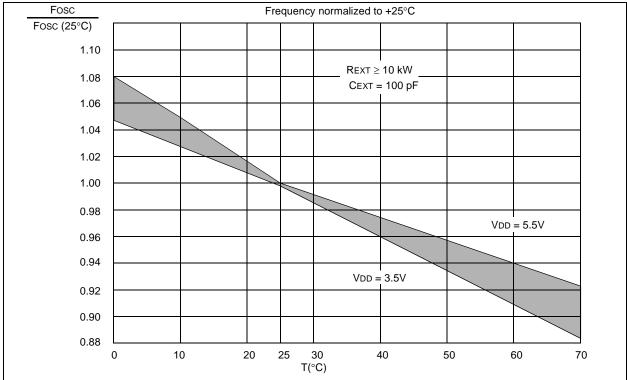

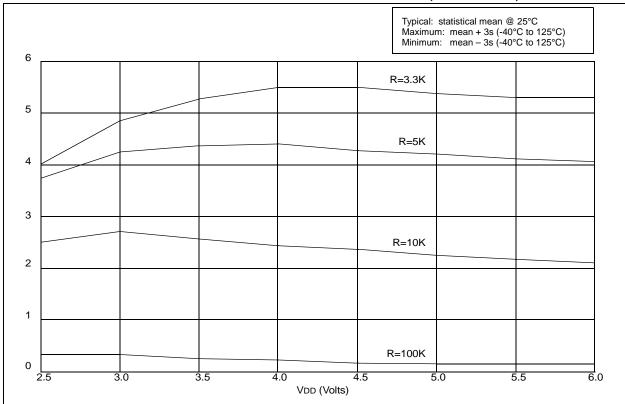

FIGURE 18-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

### TABLE 18-1: RC OSCILLATOR FREQUENCIES

| Сехт   | Rext |          | rage<br>5V, 25°C |

|--------|------|----------|------------------|

| 20 pF  | 3.3K | 5 MHz    | ± 27%            |

|        | 5K   | 3.8 MHz  | ± 21%            |

|        | 10K  | 2.2 MHz  | ± 21%            |

|        | 100K | 262 kHz  | ± 31%            |

| 100 pF | 3.3K | 1.63 MHz | ± 13%            |

|        | 5K   | 1.2 MHz  | ± 13%            |

|        | 10K  | 684 kHz  | ± 18%            |

|        | 100K | 71 kHz   | ± 25%            |

| 300 pF | 3.3K | 660 kHz  | ± 10%            |

|        | 5.0K | 484 kHz  | ± 14%            |

|        | 10K  | 267 kHz  | ± 15%            |

|        | 100K | 29 kHz   | ± 19%            |

The frequencies are measured on DIP packages.

The percentage variation indicated here is part-to-part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviation from average value for VDD = 5V.

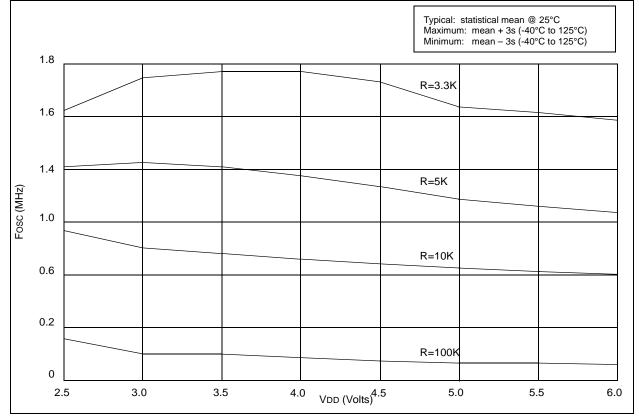

### FIGURE 18-2: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD, CEXT = 20 PF, 25°C

### FIGURE 18-12: TYPICAL IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 100 PF, 25°C)

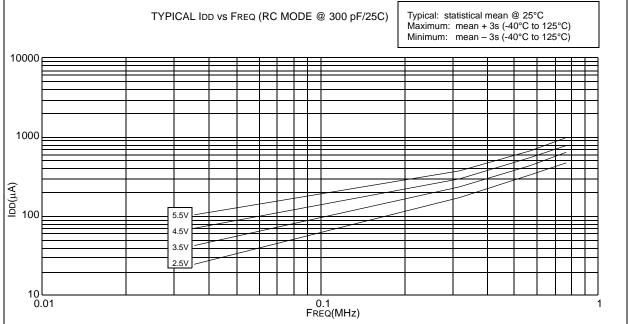

### FIGURE 19-5: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16C5X-40

### TABLE 19-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16C5X-40

| AC Characteristics  |      | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercial)Operating Voltage VDD range is described in Section 19.1. |       |      |       |       |                   |  |

|---------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|-------------------|--|

| Param<br>No. Symbol |      | Characteristic                                                                                                                                                                             | Min   | Тур† | Max   | Units | Conditions        |  |

| 30                  | TmcL | MCLR Pulse Width (low)                                                                                                                                                                     | 1000* | _    | _     | ns    | VDD = 5.0V        |  |

| 31                  | Twdt | Watchdog Timer Time-out Period<br>(No Prescaler)                                                                                                                                           | 9.0*  | 18*  | 30*   | ms    | VDD = 5.0V (Comm) |  |

| 32                  | Tdrt | Device Reset Timer Period                                                                                                                                                                  | 9.0*  | 18*  | 30*   | ms    | VDD = 5.0V (Comm) |  |

| 34                  | Tioz | I/O Hi-impedance from MCLR Low                                                                                                                                                             | 100*  | 300* | 1000* | ns    |                   |  |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

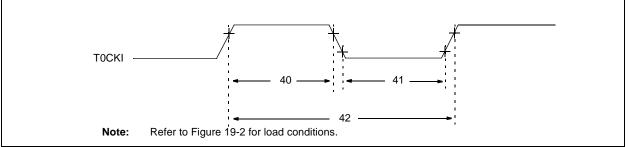

### FIGURE 19-6: TIMER0 CLOCK TIMINGS - PIC16C5X-40

### TABLE 19-4: TIMER0 CLOCK REQUIREMENTS PIC16C5X-40

| A            | AC Charac | toristics              | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |      |     |       |                                                                |  |

|--------------|-----------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|----------------------------------------------------------------|--|

| Param<br>No. | Symbol    | Characteristic         | Min                                                                                                                                 | Тур† | Max | Units | Conditions                                                     |  |

| 40           | Tt0H      | T0CKI High Pulse Width |                                                                                                                                     |      |     |       |                                                                |  |

|              |           | - No Prescaler         | 0.5 Tcy + 20*                                                                                                                       | —    |     | ns    |                                                                |  |

|              |           | - With Prescaler       | 10*                                                                                                                                 |      | —   | ns    |                                                                |  |

| 41           | Tt0L      | T0CKI Low Pulse Width  |                                                                                                                                     |      |     |       |                                                                |  |

|              |           | - No Prescaler         | 0.5 TCY + 20*                                                                                                                       | —    |     | ns    |                                                                |  |

|              |           | - With Prescaler       | 10*                                                                                                                                 | _    | —   | ns    |                                                                |  |

| 42           | Tt0P      | T0CKI Period           | 20 or <u>Tcy + 40</u> *<br>N                                                                                                        | _    | _   | ns    | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |  |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C5X

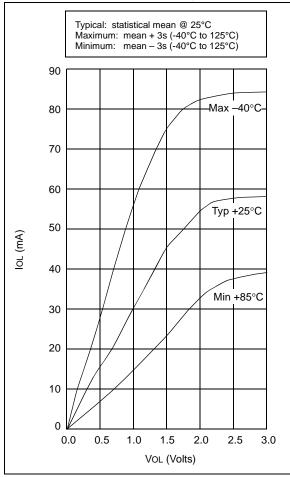

### FIGURE 20-9: IOL vs. VOL, VDD = 5 V