Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| 62mm) |

|-------|

|       |

|       |

|       |

#### 2.0 PIC16C5X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC16C5X Product Identification System at the back of this data sheet to specify the correct part number.

For the PIC16C5X family of devices, there are four device types, as indicated in the device number:

- C, as in PIC16C54C. These devices have EPROM program memory and operate over the standard voltage range.

- LC, as in PIC16LC54A. These devices have EPROM program memory and operate over an extended voltage range.

- CR, as in PIC16CR54A. These devices have ROM program memory and operate over the standard voltage range.

- LCR, as in PIC16LCR54A. These devices have ROM program memory and operate over an extended voltage range.

#### 2.1 UV Erasable Devices (EPROM)

The UV erasable versions offered in CERDIP packages, are optimal for prototype development and pilot programs.

UV erasable devices can be programmed for any of the four oscillator configurations. Microchip's PICSTART® Plus<sup>(1)</sup> and PRO MATE® programmers both support programming of the PIC16C5X. Third party programmers also are available. Refer to the

# Third Party Guide (DS00104) for a list of sources.2.2 One-Time-Programmable (OTP) Devices

The availability of OTP devices is especially useful for customers expecting frequent code changes and updates, or small volume applications.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must be programmed.

**Note 1:** PIC16LC54C and PIC16C54A devices require OSC2 not to be connected while programming with PICSTART® Plus programmer.

### 2.3 Quick-Turnaround-Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration bit options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

#### 2.4 Serialized Quick-Turnaround-Production (SQTP<sup>SM</sup>) Devices

Microchip offers the unique programming service where a few user defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential. The devices are identical to the OTP devices but with all EPROM locations and configuration bit options already programmed by the factory.

Serial programming allows each device to have a unique number which can serve as an entry code, password or ID number.

#### 2.5 Read Only Memory (ROM) Devices

Microchip offers masked ROM versions of several of the highest volume parts, giving the customer a low cost option for high volume, mature products.

TABLE 3-1: PINOUT DESCRIPTION - PIC16C54, PIC16C54, PIC16C56, PIC16C756, PIC16C758, PIC16C758

| D' N        | Pi  | n Numb | er    | Pin  | Buffer | B t di                                                                                                        |

|-------------|-----|--------|-------|------|--------|---------------------------------------------------------------------------------------------------------------|

| Pin Name    | DIP | SOIC   | SSOP  | Туре | Туре   | Description                                                                                                   |

| RA0         | 17  | 17     | 19    | I/O  | TTL    | Bi-directional I/O port                                                                                       |

| RA1         | 18  | 18     | 20    | I/O  | TTL    |                                                                                                               |

| RA2         | 1   | 1      | 1     | I/O  | TTL    |                                                                                                               |

| RA3         | 2   | 2      | 2     | I/O  | TTL    |                                                                                                               |

| RB0         | 6   | 6      | 7     | I/O  | TTL    | Bi-directional I/O port                                                                                       |

| RB1         | 7   | 7      | 8     | I/O  | TTL    |                                                                                                               |

| RB2         | 8   | 8      | 9     | I/O  | TTL    |                                                                                                               |

| RB3         | 9   | 9      | 10    | I/O  | TTL    |                                                                                                               |

| RB4         | 10  | 10     | 11    | I/O  | TTL    |                                                                                                               |

| RB5         | 11  | 11     | 12    | I/O  | TTL    |                                                                                                               |

| RB6         | 12  | 12     | 13    | I/O  | TTL    |                                                                                                               |

| RB7         | 13  | 13     | 14    | I/O  | TTL    |                                                                                                               |

| T0CKI       | 3   | 3      | 3     | I    | ST     | Clock input to Timer0. Must be tied to Vss or VDD, if not in                                                  |

|             |     |        |       |      |        | use, to reduce current consumption.                                                                           |

| MCLR/VPP    | 4   | 4      | 4     | I    | ST     | Master clear (RESET) input/programming voltage input.                                                         |

|             |     |        |       |      |        | This pin is an active low RESET to the device. Voltage on the MCLR/VPP pin must not exceed VDD to avoid unin- |

|             |     |        |       |      |        | tended entering of Programming mode.                                                                          |

| OSC1/CLKIN  | 16  | 16     | 18    | I    | ST     | Oscillator crystal input/external clock source input.                                                         |

| OSC2/CLKOUT | 15  | 15     | 17    | 0    |        | Oscillator crystal output. Connects to crystal or resonator                                                   |

|             |     |        |       |      |        | in crystal Oscillator mode. In RC mode, OSC2 pin outputs                                                      |

|             |     |        |       |      |        | CLKOUT, which has 1/4 the frequency of OSC1 and                                                               |

|             |     |        |       |      |        | denotes the instruction cycle rate.                                                                           |

| VDD         | 14  | 14     | 15,16 | Р    | _      | Positive supply for logic and I/O pins.                                                                       |

| Vss         | 5   | 5      | 5,6   | Р    | _      | Ground reference for logic and I/O pins.                                                                      |

Legend: I = input, O = output, I/O = input/output, P = power, — = Not Used, TTL = TTL input, ST = Schmitt Trigger input

### PIC16C5X

TABLE 3-2: PINOUT DESCRIPTION - PIC16C55, PIC16C57, PIC16CR57

| Din Name    | Pi  | n Numb | er   | Pin  | Buffer | Description                                                                                                                                                                                              |

|-------------|-----|--------|------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name    | DIP | SOIC   | SSOP | Туре | Type   | Description                                                                                                                                                                                              |

| RA0         | 6   | 6      | 5    | I/O  | TTL    | Bi-directional I/O port                                                                                                                                                                                  |

| RA1         | 7   | 7      | 6    | I/O  | TTL    | ·                                                                                                                                                                                                        |

| RA2         | 8   | 8      | 7    | I/O  | TTL    |                                                                                                                                                                                                          |

| RA3         | 9   | 9      | 8    | I/O  | TTL    |                                                                                                                                                                                                          |

| RB0         | 10  | 10     | 9    | I/O  | TTL    | Bi-directional I/O port                                                                                                                                                                                  |

| RB1         | 11  | 11     | 10   | I/O  | TTL    | ·                                                                                                                                                                                                        |

| RB2         | 12  | 12     | 11   | I/O  | TTL    |                                                                                                                                                                                                          |

| RB3         | 13  | 13     | 12   | I/O  | TTL    |                                                                                                                                                                                                          |

| RB4         | 14  | 14     | 13   | I/O  | TTL    |                                                                                                                                                                                                          |

| RB5         | 15  | 15     | 15   | I/O  | TTL    |                                                                                                                                                                                                          |

| RB6         | 16  | 16     | 16   | I/O  | TTL    |                                                                                                                                                                                                          |

| RB7         | 17  | 17     | 17   | I/O  | TTL    |                                                                                                                                                                                                          |

| RC0         | 18  | 18     | 18   | I/O  | TTL    | Bi-directional I/O port                                                                                                                                                                                  |

| RC1         | 19  | 19     | 19   | I/O  | TTL    |                                                                                                                                                                                                          |

| RC2         | 20  | 20     | 20   | I/O  | TTL    |                                                                                                                                                                                                          |

| RC3         | 21  | 21     | 21   | I/O  | TTL    |                                                                                                                                                                                                          |

| RC4         | 22  | 22     | 22   | I/O  | TTL    |                                                                                                                                                                                                          |

| RC5         | 23  | 23     | 23   | I/O  | TTL    |                                                                                                                                                                                                          |

| RC6         | 24  | 24     | 24   | I/O  | TTL    |                                                                                                                                                                                                          |

| RC7         | 25  | 25     | 25   | I/O  | TTL    |                                                                                                                                                                                                          |

| T0CKI       | 1   | 1      | 2    | I    | ST     | Clock input to Timer0. Must be tied to Vss or VDD, if not in use, to reduce current consumption.                                                                                                         |

| MCLR        | 28  | 28     | 28   | I    | ST     | Master clear (RESET) input. This pin is an active low RESET to the device.                                                                                                                               |

| OSC1/CLKIN  | 27  | 27     | 27   | I    | ST     | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT | 26  | 26     | 26   | 0    | _      | Oscillator crystal output. Connects to crystal or resonator in crystal Oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| VDD         | 2   | 2      | 3,4  | Р    | _      | Positive supply for logic and I/O pins.                                                                                                                                                                  |

| Vss         | 4   | 4      | 1,14 | Р    |        | Ground reference for logic and I/O pins.                                                                                                                                                                 |

| N/C         | 3,5 | 3,5    |      | _    |        | Unused, do not connect.                                                                                                                                                                                  |

Legend: I = input, O = output, I/O = input/output, P = power, — = Not Used, TTL = TTL input, ST = Schmitt Trigger input

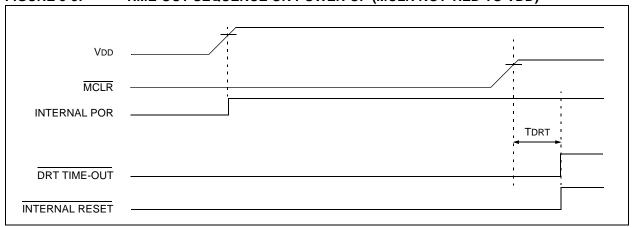

FIGURE 5-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD)

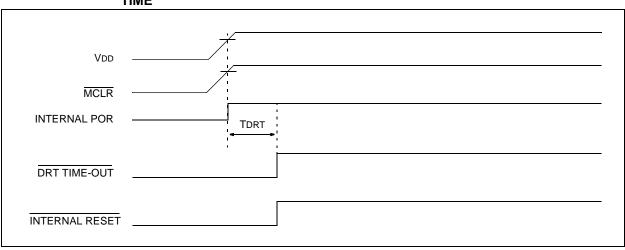

FIGURE 5-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): FAST VDD RISE TIME

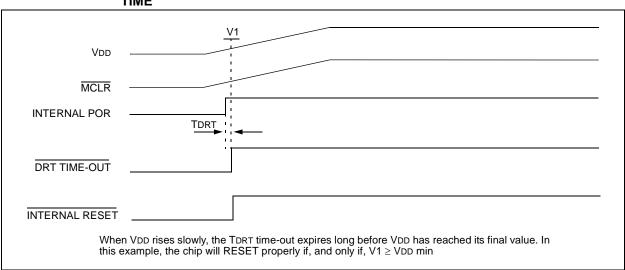

FIGURE 5-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE TIME

#### 6.3 STATUS Register

This register contains the arithmetic status of the ALU, the RESET status and the page preselect bits for program memories larger than 512 words.

The STATUS Register can be the destination for any instruction, as with any other register. If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not

writable. Therefore, the result of an instruction with the STATUS Register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS Register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS Register because these instructions do not affect the Z, DC or C bits from the STATUS Register. For other instructions which do affect STATUS Bits, see Section 10.0, Instruction Set Summary.

#### REGISTER 6-1: STATUS REGISTER (ADDRESS: 03h)

| R/W-0 | R/W-0 | R/W-0 | R-1 | R-1 | R/W-x | R/W-x | R/W-x |  |

|-------|-------|-------|-----|-----|-------|-------|-------|--|

| PA2   | PA1   | PA0   | TO  | PD  | Z     | DC    | С     |  |

| bit 7 |       |       |     |     |       |       | bit 0 |  |

bit 7: **PA2**: This bit unused at this time.

Use of the PA2 bit as a general purpose read/write bit is not recommended, since this may affect upward compatibility with future products.

bit 6-5: PA<1:0>: Program page preselect bits (PIC16C56/CR56)(PIC16C57/CR57)(PIC16C58/CR58)

00 = Page 0 (000h - 1FFh) - PIC16C56/CR56, PIC16C57/CR57, PIC16C58/CR58

01 = Page 1 (200h - 3FFh) - PIC16C56/CR56, PIC16C57/CR57, PIC16C58/CR58

10 = Page 2 (400h - 5FFh) - PIC16C57/CR57, PIC16C58/CR58

11 = Page 3 (600h - 7FFh) - PIC16C57/CR57, PIC16C58/CR58

Each page is 512 words.

Using the PA<1:0> bits as general purpose read/write bits in devices which do not use them for program page preselect is not recommended since this may affect upward compatibility with future products.

bit 4: **TO**: Time-out bit

1 = After power-up, CLRWDT instruction, or SLEEP instruction

0 = A WDT time-out occurred

bit 3: **PD**: Power-down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

bit 2: Z: Zero bit

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

bit 1: **DC**: Digit carry/borrow bit (for ADDWF and SUBWF instructions)

#### ADDWF

1 = A carry from the 4th low order bit of the result occurred

0 = A carry from the 4th low order bit of the result did not occur

#### **SUBWF**

1 = A borrow from the 4th low order bit of the result did not occur

0 = A borrow from the 4th low order bit of the result occurred

bit 0: C: Carry/borrow bit (for ADDWF, SUBWF and RRF, RLF instructions)

ADDWF SUBWF RRF or RLF

1 = A carry occurred 1 = A borrow did not occur

0 = A carry did not occur 0 = A borrow occurred

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR 1 = bit is set 0 = bit is cleared x = bit is unknown

Loaded with LSb or MSb, respectively

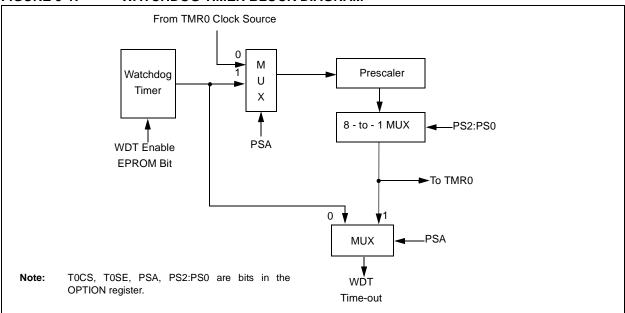

#### 9.2 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins have been stopped, for example, by execution of a SLEEP instruction. During normal operation or SLEEP, a WDT Reset or Wake-up Reset generates a device RESET.

The TO bit (STATUS<4>) will be cleared upon a Watchdog Timer Reset (Section 6.3).

The WDT can be permanently disabled by programming the configuration bit WDTE as a '0' (Section 9.1). Refer to the PIC16C5X Programming Specifications (Literature Number DS30190) to determine how to access the configuration word.

#### 9.2.1 WDT PERIOD

An 8-bit counter is available as a prescaler for the Timer0 module (Section 8.2), or as a postscaler for the Watchdog Timer (WDT), respectively. For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT, but not

both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the WDT, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio (Section 6.4).

The WDT has a nominal time-out period of 18 ms (with no prescaler). If a longer time-out period is desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT (under software control) by writing to the OPTION register. Thus, time-out a period of a nominal 2.3 seconds can be realized. These periods vary with temperature, VDD and part-to-part process variations (see Device Characterization).

Under worst case conditions (VDD = Min., Temperature = Max., WDT prescaler = 1:128), it may take several seconds before a WDT time-out occurs.

### 9.2.2 WDT PROGRAMMING CONSIDERATIONS

The CLRWDT instruction clears the WDT and the prescaler, if assigned to the WDT, and prevents it from timing out and generating a device RESET.

The SLEEP instruction RESETS the WDT and the prescaler, if assigned to the WDT. This gives the maximum SLEEP time before a WDT Wake-up Reset.

FIGURE 9-1: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 9-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on MCLR and WDT Reset |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|-----------------------------|

| N/A     | OPTION |       | 1     | Tosc  | Tose  | PSA   | PS2   | PS1   | PS0   | 11 1111                       | 11 1111                     |

Legend: u = unchanged, - = unimplemented, read as '0'. Shaded cells not used by Watchdog Timer.

#### 12.3 DC Characteristics: PIC16C54/55/56/57-RCE, XTE, 10E, HSE, LPE (Extended)

|              |        |                                                                                                                            | Standard Operating Conditions (unless otherwise specified) Operating Temperature $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for extended |                                 |                                    |                            |                                                                                                                                                                                            |  |

|--------------|--------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol | Characteristic/Device                                                                                                      | Min                                                                                                                                                        | Typ†                            | Max                                | Units                      | Conditions                                                                                                                                                                                 |  |

| D001         | VDD    | Supply Voltage PIC16C5X-RCE PIC16C5X-XTE PIC16C5X-10E PIC16C5X-HSE PIC16C5X-LPE                                            | 3.25<br>3.25<br>4.5<br>4.5<br>2.5                                                                                                                          | 11111                           | 6.0<br>6.0<br>5.5<br>5.5<br>6.0    | V<br>V<br>V<br>V           |                                                                                                                                                                                            |  |

| D002         | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>                                                                                  | _                                                                                                                                                          | 1.5*                            | _                                  | V                          | Device in SLEEP mode                                                                                                                                                                       |  |

| D003         | VPOR   | VDD Start Voltage to ensure<br>Power-on Reset                                                                              | _                                                                                                                                                          | Vss                             | _                                  | V                          | See Section 5.1 for details on Power-on Reset                                                                                                                                              |  |

| D004         | SVDD   | VDD Rise Rate to ensure<br>Power-on Reset                                                                                  | 0.05*                                                                                                                                                      | _                               | _                                  | V/ms                       | See Section 5.1 for details on Power-on Reset                                                                                                                                              |  |

| D010         | IDD    | Supply Current <sup>(2)</sup> PIC16C5X-RCE <sup>(3)</sup> PIC16C5X-XTE PIC16C5X-10E PIC16C5X-HSE PIC16C5X-HSE PIC16C5X-LPE | _<br>_<br>_<br>_                                                                                                                                           | 1.8<br>1.8<br>4.8<br>4.8<br>9.0 | 3.3<br>3.3<br>10<br>10<br>20<br>55 | mA<br>mA<br>mA<br>mA<br>μA | Fosc = 4 MHz, VDD = 5.5V<br>Fosc = 4 MHz, VDD = 5.5V<br>Fosc = 10 MHz, VDD = 5.5V<br>Fosc = 10 MHz, VDD = 5.5V<br>Fosc = 16 MHz, VDD = 5.5V<br>Fosc = 32 kHz, VDD = 3.25V,<br>WDT disabled |  |

| D020         | IPD    | Power-down Current <sup>(2)</sup>                                                                                          | _<br>_                                                                                                                                                     | 5.0<br>0.8                      | 22<br>18                           | μA<br>μA                   | VDD = 3.25V, WDT enabled<br>VDD = 3.25V, WDT disabled                                                                                                                                      |  |

<sup>\*</sup> These parameters are characterized but not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in  $k\Omega$ .

<sup>†</sup> Data in "Typ" column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

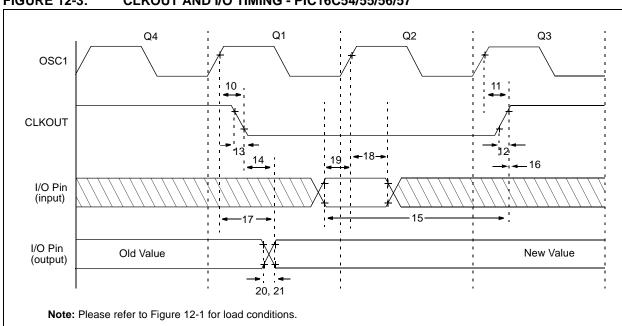

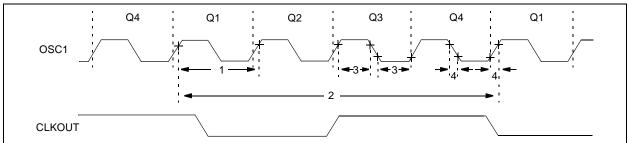

FIGURE 12-3: CLKOUT AND I/O TIMING - PIC16C54/55/56/57

TABLE 12-2: CLKOUT AND I/O TIMING REQUIREMENTS - PIC16C54/55/56/57

| AC Chara     | acteristics | Standard Operating Conditions (unless otherwise specified)  Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |              |      |      |       |  |  |  |

|--------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|-------|--|--|--|

| Param<br>No. | Symbol      | Characteristic                                                                                                                                                                                                                                   | Min          | Тур† | Max  | Units |  |  |  |

| 10           | TosH2ckL    | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                                                                                                                                                                                                                  | _            | 15   | 30** | ns    |  |  |  |

| 11           | TosH2ckH    | OSC1↑ to CLKOUT↑ <sup>(1)</sup>                                                                                                                                                                                                                  | _            | 15   | 30** | ns    |  |  |  |

| 12           | TckR        | CLKOUT rise time <sup>(1)</sup>                                                                                                                                                                                                                  | _            | 5.0  | 15** | ns    |  |  |  |

| 13           | TckF        | CLKOUT fall time <sup>(1)</sup>                                                                                                                                                                                                                  | _            | 5.0  | 15** | ns    |  |  |  |

| 14           | TckL2ioV    | CLKOUT↓ to Port out valid <sup>(1)</sup>                                                                                                                                                                                                         | _            | _    | 40** | ns    |  |  |  |

| 15           | TioV2ckH    | Port in valid before CLKOUT <sup>(1)</sup>                                                                                                                                                                                                       | 0.25 TCY+30* | _    | _    | ns    |  |  |  |

| 16           | TckH2ioI    | Port in hold after CLKOUT <sup>(1)</sup>                                                                                                                                                                                                         | 0*           | _    | _    | ns    |  |  |  |

| 17           | TosH2ioV    | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(2)</sup>                                                                                                                                                                                    | _            | _    | 100* | ns    |  |  |  |

| 18           | TosH2ioI    | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid (I/O in hold time)                                                                                                                                                                            | TBD          | _    | _    | ns    |  |  |  |

| 19           | TioV2osH    | Port input valid to OSC1↑ (I/O in setup time)                                                                                                                                                                                                    | TBD          |      | _    | ns    |  |  |  |

| 20           | TioR        | Port output rise time <sup>(2)</sup>                                                                                                                                                                                                             | _            | 10   | 25** | ns    |  |  |  |

| 21           | TioF        | Port output fall time <sup>(2)</sup>                                                                                                                                                                                                             | _            | 10   | 25** | ns    |  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

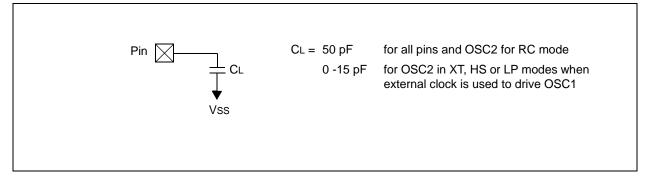

**Note 1:** Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

2: Please refer to Figure 12-1 for load conditions.

<sup>\*\*</sup> These parameters are design targets and are not tested. No characterization data available at this time.

<sup>†</sup> Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

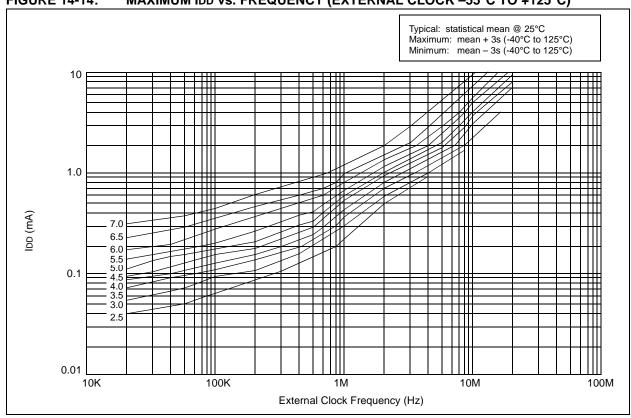

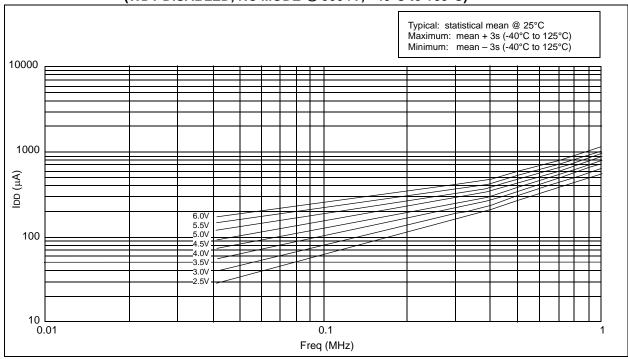

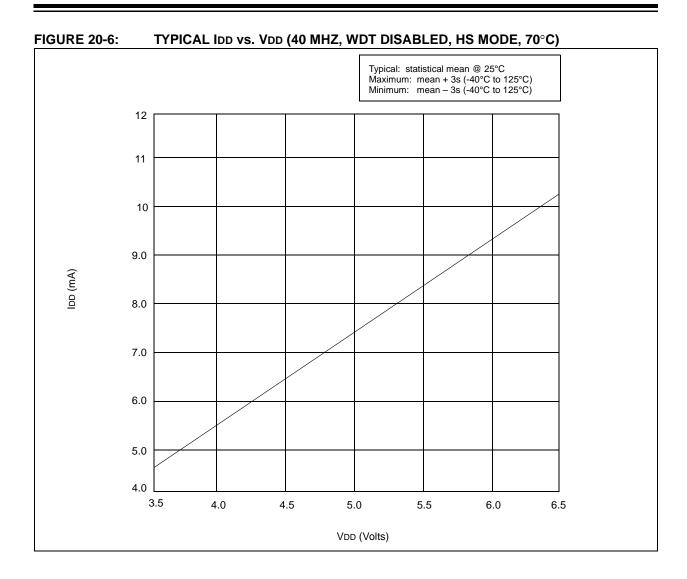

MAXIMUM IDD VS. FREQUENCY (EXTERNAL CLOCK, -40°C TO +85°C) FIGURE 14-13: Typical: statistical mean @ 25°C Maximum: mean + 3s (-40°C to 125°C) Minimum: mean - 3s (-40°C to 125°C) 10 1.0 IDD (mA) 7.0 6.5 0.1 4.0 3.5 = 3.0 0.01 10K 100K 1M 10M 100M External Clock Frequency (Hz)

TABLE 14-2: INPUT CAPACITANCE FOR PIC16C54/56

| Pin         | Typical Capacitance (pF) |          |  |  |  |

|-------------|--------------------------|----------|--|--|--|

| Pin         | 18L PDIP                 | 18L SOIC |  |  |  |

| RA port     | 5.0                      | 4.3      |  |  |  |

| RB port     | 5.0                      | 4.3      |  |  |  |

| MCLR        | 17.0                     | 17.0     |  |  |  |

| OSC1        | 4.0                      | 3.5      |  |  |  |

| OSC2/CLKOUT | 4.3                      | 3.5      |  |  |  |

| T0CKI       | 3.2                      | 2.8      |  |  |  |

All capacitance values are typical at 25°C. A part-to-part variation of  $\pm 25\%$  (three standard deviations) should be taken into account.

TABLE 14-3: INPUT CAPACITANCE FOR PIC16C55/57

|             | Typical Capacitance (pF) |          |  |  |  |

|-------------|--------------------------|----------|--|--|--|

| Pin         | 28L PDIP<br>(600 mil)    | 28L SOIC |  |  |  |

| RA port     | 5.2                      | 4.8      |  |  |  |

| RB port     | 5.6                      | 4.7      |  |  |  |

| RC port     | 5.0                      | 4.1      |  |  |  |

| MCLR        | 17.0                     | 17.0     |  |  |  |

| OSC1        | 6.6                      | 3.5      |  |  |  |

| OSC2/CLKOUT | 4.6                      | 3.5      |  |  |  |

| TOCKI       | 4.5                      | 3.5      |  |  |  |

All capacitance values are typical at 25°C. A part-to-part variation of  $\pm 25\%$  (three standard deviations) should be taken into account.

15.4 DC Characteristics: PIC16C54A-04, 10, 20, PIC16LC54A-04, PIC16LV54A-02 (Commercial) PIC16C54A-04I, 10I, 20I, PIC16LC54A-04I, PIC16LV54A-02I (Industrial) PIC16C54A-04E, 10E, 20E, PIC16LC54A-04E (Extended)

| DC CH        | ARACTE | RISTICS                                                                                                      | Standard Operating Conditions (unless otherwise specified) Operating Temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial $-20^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial-PIC16LV54A-02I $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for extended |                              |                                                        |                            |                                                                                                                                                                                                   |  |

|--------------|--------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol | Characteristic                                                                                               | Min                                                                                                                                                                                                                                                                                                                          | Тур†                         | Max                                                    | Units                      | Conditions                                                                                                                                                                                        |  |

| D030         | VIL    | Input Low Voltage I/O ports MCLR (Schmitt Trigger) TOCKI (Schmitt Trigger) OSC1 (Schmitt Trigger) OSC1       | Vss<br>Vss<br>Vss<br>Vss<br>Vss                                                                                                                                                                                                                                                                                              | <br> -<br> -<br> -           | 0.2 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.3 VDD | V<br>V<br>V                | Pin at hi-impedance  RC mode only <sup>(3)</sup> XT, HS and LP modes                                                                                                                              |  |

| D040         | VIH    | Input High Voltage I/O ports I/O ports MCLR (Schmitt Trigger) TOCKI (Schmitt Trigger) OSC1 (Schmitt Trigger) | 0.2 VDD + 1<br>2.0<br>0.85 VDD<br>0.85 VDD<br>0.85 VDD<br>0.7 VDD                                                                                                                                                                                                                                                            | <br> -<br> -<br> -<br> -     | VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD                 | V<br>V<br>V<br>V           | For all $VDD^{(4)}$<br>$4.0V < VDD \le 5.5V^{(4)}$<br>RC mode only <sup>(3)</sup><br>XT, HS and LP modes                                                                                          |  |

| D050         | VHYS   | Hysteresis of Schmitt<br>Trigger inputs                                                                      | 0.15 VDD*                                                                                                                                                                                                                                                                                                                    | _                            | _                                                      | V                          |                                                                                                                                                                                                   |  |

| D060         | IIL    | Input Leakage Current <sup>(1,2)</sup> I/O ports  MCLR MCLR TOCKI OSC1                                       | -1.0<br>-5.0<br><br>-3.0<br>-3.0                                                                                                                                                                                                                                                                                             | 0.5<br><br>0.5<br>0.5<br>0.5 | +1.0<br>+5.0<br>+3.0<br>+3.0                           | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ | For VDD $\leq$ 5.5V:<br>VSS $\leq$ VPIN $\leq$ VDD,<br>pin at hi-impedance<br>VPIN = VSS +0.25V<br>VPIN = VDD<br>VSS $\leq$ VPIN $\leq$ VDD<br>VSS $\leq$ VPIN $\leq$ VDD,<br>XT, HS and LP modes |  |

| D080         | VOL    | Output Low Voltage I/O ports OSC2/CLKOUT                                                                     | _                                                                                                                                                                                                                                                                                                                            |                              | 0.6<br>0.6                                             | V                          | IOL = 8.7 mA, VDD = 4.5V<br>IOL = 1.6 mA, VDD = 4.5V,<br>RC mode only                                                                                                                             |  |

|              | VOH    | Output High Voltage <sup>(2)</sup> I/O ports OSC2/CLKOUT                                                     | VDD - 0.7<br>VDD - 0.7                                                                                                                                                                                                                                                                                                       |                              | _                                                      | V<br>V                     | IOH = -5.4 mA, VDD = 4.5V<br>IOH = -1.0 mA, VDD = 4.5V,<br>RC mode only                                                                                                                           |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

<sup>2:</sup> Negative current is defined as coming out of the pin.

<sup>3:</sup> For the RC mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C5X be driven with external clock in RC mode.

#### **Timing Parameter Symbology and Load Conditions** 15.5

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

Low

2. TppS

| Т    |                                         |                    |

|------|-----------------------------------------|--------------------|

| F    | Frequency                               | T Time             |

| Lowe | ercase letters (pp) and their meanings: |                    |

| pp   |                                         |                    |

| 2    | to                                      | mc MCLR            |

| ck   | CLKOUT                                  | osc oscillator     |

| су   | cycle time                              | os OSC1            |

| drt  | device reset timer                      | t0 T0CKI           |

| io   | I/O port                                | wdt watchdog timer |

| Uppe | ercase letters and their meanings:      |                    |

| S    |                                         |                    |

| F    | Fall                                    | P Period           |

| Н    | High                                    | R Rise             |

| I    | Invalid (Hi-impedance)                  | V Valid            |

Hi-impedance

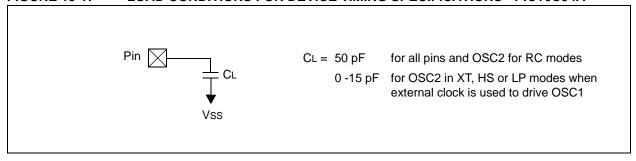

#### **FIGURE 15-1:** LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS - PIC16C54A

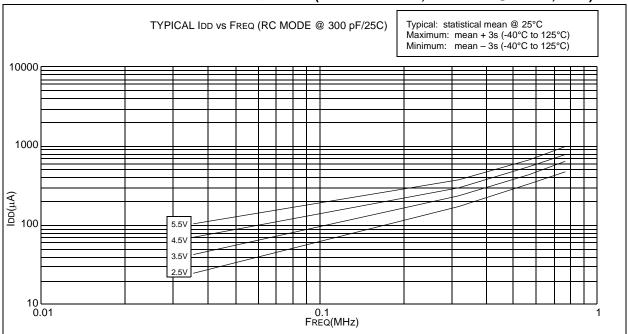

TYPICAL IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 300 PF, 25°C) Typical: statistical mean @ 25°C Maximum: mean + 3s (-40°C to 125°C) Minimum: mean - 3s (-40°C to 125°C) 10000 1000 IDD (μA) 100 5.5V 5.0V 4.5V 3.0V <u>—</u> 2.5V — 10 0.01 0.1 Freq (MHz)

FIGURE 16-14:

FIGURE 16-15: MAXIMUM IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 300 PF, -40°C to +85°C)

### 17.4 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| T                                          |        |  |  |  |  |

|--------------------------------------------|--------|--|--|--|--|

| F Frequency                                | T Time |  |  |  |  |

| Lowercase letters (pp) and their meanings: |        |  |  |  |  |

| рр  |                    |                    |

|-----|--------------------|--------------------|

| 2   | to                 | mc MCLR            |

| ck  | CLKOUT             | osc oscillator     |

| су  | cycle time         | os OSC1            |

| drt | device reset timer | t0 T0CKI           |

| io  | I/O port           | wdt watchdog timer |

Uppercase letters and their meanings:

| S |                        |   |              |

|---|------------------------|---|--------------|

| F | Fall                   | Р | Period       |

| Н | High                   | R | Rise         |

| 1 | Invalid (Hi-impedance) | V | Valid        |

| L | Low                    | Z | Hi-impedance |

## FIGURE 17-5: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS - PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/C58B/CR58B-04, 20

10

TYPICAL IDD vs FREQ(RC MODE @ 100 pF/25C) Typical: statistical mean @ 25°C Maximum: mean + 3s (-40°C to 125°C) Minimum: mean - 3s (-40°C to 125°C) 10000 1000 IDD(μA) 5.5\ 100 3.5

TYPICAL IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 100 PF, 25°C) FIGURE 18-12:

FREQ(MHz)

10 0.1

#### 19.4 Timing Diagrams and Specifications

FIGURE 19-3: EXTERNAL CLOCK TIMING - PIC16C5X-40

TABLE 19-1: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16C5X-40

| AC Characteristics |            | Standard Operating Conditions (unless otherwise specified)  Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |      |        |      |       |               |  |  |

|--------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------|------|--------|------|-------|---------------|--|--|

| Param<br>No.       | Symbol     | Characteristic                                                                                                                        |      | Typ†   | Max  | Units | Conditions    |  |  |

|                    | Fosc       | External CLKIN Frequency <sup>(1)</sup>                                                                                               | 20   | _      | 40   | MHz   | HS osc mode   |  |  |

| 1                  | Tosc       | External CLKIN Period <sup>(1)</sup>                                                                                                  | 25   | _      | _    | ns    | HS osc mode   |  |  |

| 2                  | Tcy        | Instruction Cycle Time <sup>(2)</sup>                                                                                                 | _    | 4/Fosc | _    | _     |               |  |  |

| 3                  | TosL, TosH | Clock in (OSC1) Low or High<br>Time                                                                                                   | 6.0* | _      | _    | ns    | HS oscillator |  |  |

| 4                  | TosR, TosF | Clock in (OSC1) Rise or Fall<br>Time                                                                                                  | _    | _      | 6.5* | ns    | HS oscillator |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

- Note 1: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption.

When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: Instruction cycle period (TcY) equals four times the input oscillator time base period.

<sup>†</sup> Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

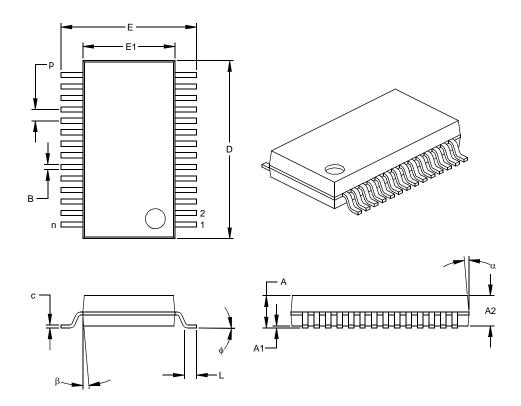

#### 28-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units |      | INCHES |      | MILLIMETERS* |        |        |  |

|--------------------------|-------|------|--------|------|--------------|--------|--------|--|

| Dimension                | MIN   | NOM  | MAX    | MIN  | NOM          | MAX    |        |  |

| Number of Pins           | n     |      | 28     |      |              | 28     |        |  |

| Pitch                    | р     |      | .026   |      |              | 0.65   |        |  |

| Overall Height           | Α     | .068 | .073   | .078 | 1.73         | 1.85   | 1.98   |  |

| Molded Package Thickness | A2    | .064 | .068   | .072 | 1.63         | 1.73   | 1.83   |  |

| Standoff §               | A1    | .002 | .006   | .010 | 0.05         | 0.15   | 0.25   |  |

| Overall Width            | Е     | .299 | .309   | .319 | 7.59         | 7.85   | 8.10   |  |

| Molded Package Width     | E1    | .201 | .207   | .212 | 5.11         | 5.25   | 5.38   |  |

| Overall Length           | D     | .396 | .402   | .407 | 10.06        | 10.20  | 10.34  |  |

| Foot Length              | L     | .022 | .030   | .037 | 0.56         | 0.75   | 0.94   |  |

| Lead Thickness           | С     | .004 | .007   | .010 | 0.10         | 0.18   | 0.25   |  |

| Foot Angle               | ф     | 0    | 4      | 8    | 0.00         | 101.60 | 203.20 |  |

| Lead Width               | В     | .010 | .013   | .015 | 0.25         | 0.32   | 0.38   |  |

| Mold Draft Angle Top     | α     | 0    | 5      | 10   | 0            | 5      | 10     |  |

| Mold Draft Angle Bottom  | β     | 0    | 5      | 10   | 0            | 5      | 10     |  |

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-150 Drawing No. C04-073

<sup>\*</sup> Controlling Parameter § Significant Characteristic

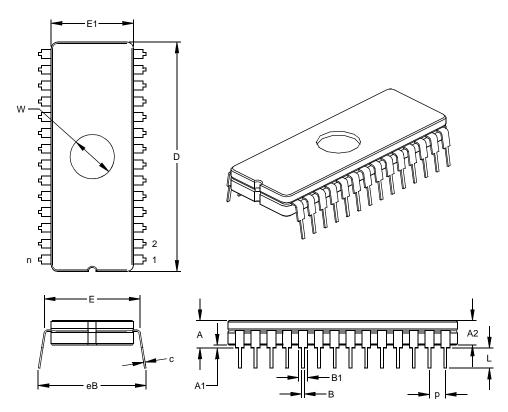

### 28-Lead Ceramic Dual In-line with Window (JW) - 600 mil (CERDIP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units  | INCHES* |       |       | MILLIMETERS |       |       |  |

|----------------------------|--------|---------|-------|-------|-------------|-------|-------|--|

| Dimension                  | Limits | MIN     | NOM   | MAX   | MIN         | NOM   | MAX   |  |

| Number of Pins             | n      |         | 28    |       |             | 28    |       |  |

| Pitch                      | р      |         | .100  |       |             | 2.54  |       |  |

| Top to Seating Plane       | Α      | .195    | .210  | .225  | 4.95        | 5.33  | 5.72  |  |

| Ceramic Package Height     | A2     | .155    | .160  | .165  | 3.94        | 4.06  | 4.19  |  |

| Standoff                   | A1     | .015    | .038  | .060  | 0.38        | 0.95  | 1.52  |  |

| Shoulder to Shoulder Width | Е      | .595    | .600  | .625  | 15.11       | 15.24 | 15.88 |  |

| Ceramic Pkg. Width         | E1     | .514    | .520  | .526  | 13.06       | 13.21 | 13.36 |  |

| Overall Length             | D      | 1.430   | 1.460 | 1.490 | 36.32       | 37.08 | 37.85 |  |

| Tip to Seating Plane       | L      | .125    | .138  | .150  | 3.18        | 3.49  | 3.81  |  |

| Lead Thickness             | С      | .008    | .010  | .012  | 0.20        | 0.25  | 0.30  |  |

| Upper Lead Width           | B1     | .050    | .058  | .065  | 1.27        | 1.46  | 1.65  |  |

| Lower Lead Width           | В      | .016    | .020  | .023  | 0.41        | 0.51  | 0.58  |  |

| Overall Row Spacing §      | eВ     | .610    | .660  | .710  | 15.49       | 16.76 | 18.03 |  |

| Window Diameter            | W      | .270    | .280  | .290  | 6.86        | 7.11  | 7.37  |  |

<sup>\*</sup> Controlling Parameter § Significant Characteristic JEDEC Equivalent: MO-103 Drawing No. C04-013

### PIC16C5X

#### APPENDIX A: COMPATIBILITY

To convert code written for PIC16CXX to PIC16C5X, the user should take the following steps:

- Check any CALL, GOTO or instructions that modify the PC to determine if any program memory page select operations (PA2, PA1, PA0 bits) need to be made.

- Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- Eliminate any special function register page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- Change RESET vector to proper value for processor used.

- 6. Remove any use of the ADDLW, RETURN and SUBLW instructions.

- 7. Rewrite any code segments that use interrupts.

#### APPENDIX B: REVISION HISTORY

**Revision KE (January 2013)**

Added a note to each package outline drawing.