#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 768B (512 x 12)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 25 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c54c-20i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

# 4.0 OSCILLATOR CONFIGURATIONS

# 4.1 Oscillator Types

PIC16C5Xs can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

- 1. LP: Low Power Crystal

- 2. XT: Crystal/Resonator

- 3. HS: High Speed Crystal/Resonator

- 4. RC: Resistor/Capacitor

**Note:** Not all oscillator selections available for all parts. See Section 9.1.

# 4.2 Crystal Oscillator/Ceramic Resonators

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 4-1). The PIC16C5X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source drive the OSC1/CLKIN pin (Figure 4-2).

### FIGURE 4-1: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

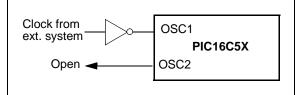

FIGURE 4-2:

# EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

### TABLE 4-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS -PIC16C5X, PIC16CR5X

| Osc<br>Type | Resonator<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |

|-------------|-------------------|------------------|------------------|

| XT          | 455 kHz           | 68-100 pF        | 68-100 pF        |

|             | 2.0 MHz           | 15-33 pF         | 15-33 pF         |

|             | 4.0 MHz           | 10-22 pF         | 10-22 pF         |

| HS          | 8.0 MHz           | 10-22 pF         | 10-22 pF         |

|             | 16.0 MHz          | 10 pF            | 10 pF            |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

### TABLE 4-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR -PIC16C5X. PIC16CR5X

| Osc<br>Type | Crystal<br>Freq       | Cap.Range<br>C1 | Cap. Range<br>C2 |

|-------------|-----------------------|-----------------|------------------|

| LP          | 32 kHz <sup>(1)</sup> | 15 pF           | 15 pF            |

| XT          | 100 kHz               | 15-30 pF        | 200-300 pF       |

|             | 200 kHz               | 15-30 pF        | 100-200 pF       |

|             | 455 kHz               | 15-30 pF        | 15-100 pF        |

|             | 1 MHz                 | 15-30 pF        | 15-30 pF         |

|             | 2 MHz                 | 15 pF           | 15 pF            |

|             | 4 MHz                 | 15 pF           | 15 pF            |

| HS          | 4 MHz                 | 15 pF           | 15 pF            |

|             | 8 MHz                 | 15 pF           | 15 pF            |

|             | 20 MHz                | 15 pF           | 15 pF            |

# Note 1: For VDD > 4.5V, C1 = C2 $\approx$ 30 pF is recommended.

These values are for design guidance only. Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

**Note:** If you change from this device to another device, please verify oscillator characteristics in your application.

# 5.1 Power-On Reset (POR)

The PIC16C5X family incorporates on-chip Power-On Reset (POR) circuitry which provides an internal chip RESET for most power-up situations. To use this feature, the user merely ties the MCLR/VPP pin to VDD. A simplified block diagram of the on-chip Power-On Reset circuit is shown in Figure 5-1.

The Power-On Reset circuit and the Device Reset Timer (Section 5.2) circuit are closely related. On power-up, the RESET latch is set and the DRT is <u>RESET</u>. The DRT timer begins counting once it detects MCLR to be high. After the time-out period, which is typically 18 ms, it will RESET the reset latch and thus end the on-chip RESET signal.

A power-up example where MCLR is not tied to VDD is shown in Figure 5-3. VDD is allowed to rise and stabilize before bringing MCLR high. The chip will actually come out of reset TDRT msec after MCLR goes high.

In Figure 5-4, the on-chip Power-On Reset feature is being used (MCLR and VDD are tied together). The VDD is stable before the start-up timer times out and there is no problem in getting a proper RESET. However, Figure 5-5 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses a high on the MCLR/VPP pin, and when the MCLR/VPP pin (and VDD) actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip is, therefore, not guaranteed to function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 5-2).

Note: When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For more information on PIC16C5X POR, see *Power-Up Considerations* - AN522 in the <u>Embedded Control Handbook</u>.

The POR circuit does not produce an internal RESET when VDD declines.

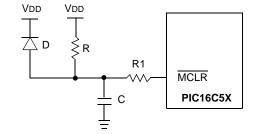

### FIGURE 5-2:

### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- External Power-On Reset circuit is required only if VDD power-up is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device electrical specification.

- R1 =  $100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

# 6.0 MEMORY ORGANIZATION

PIC16C5X memory is organized into program memory and data memory. For devices with more than 512 bytes of program memory, a paging scheme is used. Program memory pages are accessed using one or two STATUS Register bits. For devices with a data memory register file of more than 32 registers, a banking scheme is used. Data memory banks are accessed using the File Selection Register (FSR).

# 6.1 Program Memory Organization

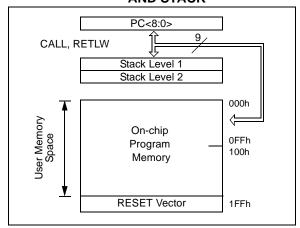

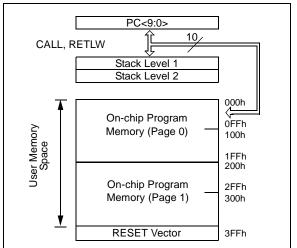

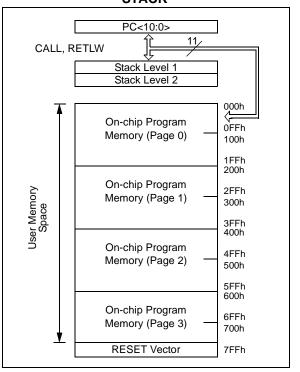

The PIC16C54, PIC16CR54 and PIC16C55 have a 9bit Program Counter (PC) capable of addressing a 512 x 12 program memory space (Figure 6-1). The PIC16C56 and PIC16CR56 have a 10-bit Program Counter (PC) capable of addressing a 1K x 12 program memory space (Figure 6-2). The PIC16CR57, PIC16C58 and PIC16CR58 have an 11-bit Program Counter capable of addressing a 2K x 12 program memory space (Figure 6-3). Accessing a location above the physically implemented address will cause a wraparound.

A NOP at the RESET vector location will cause a restart at location 000h. The RESET vector for the PIC16C54, PIC16CR54 and PIC16C55 is at 1FFh. The RESET vector for the PIC16C56 and PIC16CR56 is at 3FFh. The RESET vector for the PIC16C57, PIC16CR57, PIC16C58, and PIC16CR58 is at 7FFh. See Section 6.5 for additional information using CALL and GOTO instructions.

### FIGURE 6-1: PIC16C54/CR54/C55 PROGRAM MEMORY MAP AND STACK

### FIGURE 6-2:

### PIC16C56/CR56 PROGRAM MEMORY MAP AND STACK

FIGURE 6-3:

PIC16C57/CR57/C58/ CR58 PROGRAM MEMORY MAP AND STACK

# 6.2 Data Memory Organization

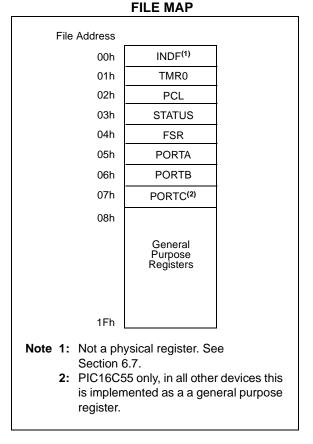

Data memory is composed of registers, or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: Special Function Registers and General Purpose Registers.

The Special Function Registers include the TMR0 register, the Program Counter (PC), the Status Register, the I/O registers (ports) and the File Select Register (FSR). In addition, Special Purpose Registers are used to control the I/O port configuration and prescaler options.

The General Purpose Registers are used for data and control information under command of the instructions.

For the PIC16C54, PIC16CR54, PIC16C56 and PIC16CR56, the register file is composed of 7 Special Function Registers and 25 General Purpose Registers (Figure 6-4).

For the PIC16C55, the register file is composed of 8 Special Function Registers and 24 General Purpose Registers.

For the PIC16C57 and PIC16CR57, the register file is composed of 8 Special Function Registers, 24 General Purpose Registers and up to 48 additional General Purpose Registers that may be addressed using a banking scheme (Figure 6-5).

For the PIC16C58 and PIC16CR58, the register file is composed of 7 Special Function Registers, 25 General Purpose Registers and up to 48 additional General Purpose Registers that may be addressed using a banking scheme (Figure 6-6).

### 6.2.1 GENERAL PURPOSE REGISTER FILE

The register file is accessed either directly or indirectly through the File Select Register (FSR). The FSR Register is described in Section 6.7.

## FIGURE 6-4: PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56 REGISTER

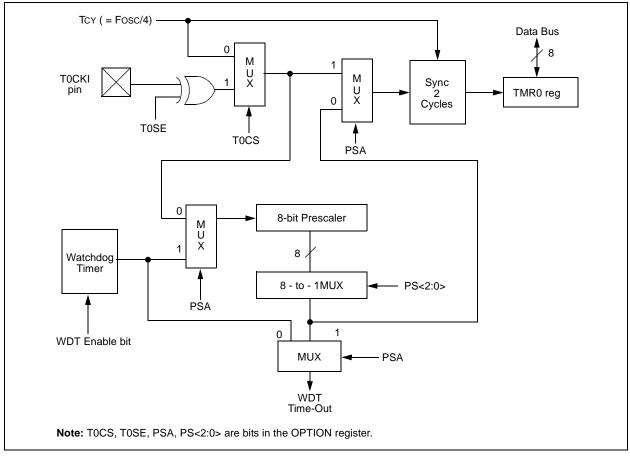

# 8.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer (WDT), respectively (Section 9.2.1). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT, but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the WDT, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a RESET, the prescaler contains all '0's.

### 8.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 8-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

### EXAMPLE 8-1: CHANGING PRESCALER (TIMER0→WDT)

| CLRWDT            | ;Clear WDT              |

|-------------------|-------------------------|

| CLRF TMR0         | Clear TMR0 & Prescaler  |

| MOVLW B'00xx1111' | ;Last 3 instructions in |

|                   | this example            |

| OPTION            | ;are required only if   |

|                   | ;desired                |

| CLRWDT            | ;PS<2:0> are 000 or     |

|                   | ;001                    |

| MOVLW B'00xx1xxx' | ;Set Prescaler to       |

| OPTION            | ;desired WDT rate       |

|                   |                         |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 8-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

# EXAMPLE 8-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| MOVLW  | B'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

|        |             | ;clock source       |

OPTION

# 9.1 Configuration Bits

Configuration bits can be programmed to select various device configurations. Two bits are for the selection of the oscillator type and one bit is the Watchdog Timer enable bit. Nine bits are code protection bits for the PIC16C54A, PIC16CR54A, PIC16C55A, PIC16C56A, PIC16CR56A, PIC16CR57C, PIC16CR57C, PIC16CR57C,

PIC16C58B, and PIC16CR58B devices (Register 9-1). One bit is for code protection for the PIC16C54, PIC16C55, PIC16C56 and PIC16C57 devices (Register 9-2).

QTP or ROM devices have the oscillator configuration programmed at the factory and these parts are tested accordingly (see "Product Identification System" diagrams in the back of this data sheet).

## REGISTER 9-1: CONFIGURATION WORD FOR PIC16C54A/CR54A/C54C/CR54C/C55A/C56A/ CR56A/C57C/CR57C/C58B/CR58B

| CP     | CP | CP | CP | CP | CP | CP | CP | CP | WDTE | FOSC1 | FOSC0 |

|--------|----|----|----|----|----|----|----|----|------|-------|-------|

| bit 11 |    |    |    |    |    |    |    |    |      |       | bit 0 |

bit 11-3: CP: Code Protection Bit

- 1 = Code protection off

- 0 =Code protection on

- bit 2: WDTE: Watchdog timer enable bit

- 1 = WDT enabled

- 0 = WDT disabled

#### bit 1-0: FOSC1:FOSC0: Oscillator Selection Bit

- 00 = LP oscillator

- 01 = XT oscillator

- 10 = HS oscillator

- 11 = RC oscillator

# **Note 1:** Refer to the PIC16C5X Programming Specification (Literature Number DS30190) to determine how to access the configuration word.

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared        | x = bit is unknown |

# 9.3 Power-Down Mode (SLEEP)

A device may be powered down (SLEEP) and later powered up (Wake-up from SLEEP).

### 9.3.1 SLEEP

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the TO bit (STATUS<4>) is set, the PD bit (STATUS<3>) is cleared and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, driving low, or hi-impedance).

It should be noted that a RESET generated by a WDT time-out does not drive the MCLR/VPP pin low.

For lowest current consumption while powered down, the T0CKI input should be at VDD or Vss and the  $\overline{\text{MCLR}}/\text{VPP}$  pin must be at a logic high level ( $\overline{\text{MCLR}}$  = VIH).

### 9.3.2 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. An external RESET input on MCLR/VPP pin.

- 2. A Watchdog Timer Time-out Reset (if WDT was enabled).

Both of these events cause a device RESET. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits can be used to determine the cause of device RESET. The  $\overline{\text{TO}}$  bit is cleared if a WDT timeout occurred (and caused wake-up). The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked.

The WDT is cleared when the device wakes from SLEEP, regardless of the wake-up source.

# 9.4 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

# 9.5 ID Locations

Four memory locations are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify.

Use only the lower 4 bits of the ID locations and always program the upper 8 bits as '1's.

**Note:** Microchip will assign a unique pattern number for QTP and SQTP requests and for ROM devices. This pattern number will be unique and traceable to the submitted code.

NOTES:

| CALL             | Subroutine Call                                                                                                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                                             |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} (PC) + 1 \rightarrow TOS; \\ k \rightarrow PC < 7:0 >; \\ (STATUS < 6:5 >) \rightarrow PC < 10:9 >; \\ 0 \rightarrow PC < 8 > \end{array}$                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                                                                |

| Encoding:        | 1001 kkkk kkkk                                                                                                                                                                                                                                                      |

| Description:     | Subroutine call. First, return<br>address (PC+1) is pushed onto the<br>stack. The eight bit immediate<br>address is loaded into PC bits<br><7:0>. The upper bits PC<10:9><br>are loaded from STATUS<6:5>,<br>PC<8> is cleared. CALL is a two-<br>cycle instruction. |

| Words:           | 1                                                                                                                                                                                                                                                                   |

| Cycles:          | 2                                                                                                                                                                                                                                                                   |

| Example:         | HERE CALL THERE                                                                                                                                                                                                                                                     |

| After Instruct   | address (HERE)<br>ion<br>address (THERE)                                                                                                                                                                                                                            |

| CLRF | Clear f |

|------|---------|

|      | Oloui I |

| Syntax:                                   | [ label ]                            | CLRF f                  |                               |

|-------------------------------------------|--------------------------------------|-------------------------|-------------------------------|

| Operands:                                 | $0 \le f \le 3^{-1}$                 | 1                       |                               |

| Operation:                                | $00h \rightarrow (f 1 \rightarrow Z$ | );                      |                               |

| Status Affected:                          | Z                                    |                         |                               |

| Encoding:                                 | 0000                                 | 011f                    | ffff                          |

| Description:                              |                                      | ents of re<br>and the Z | gister 'f' are<br>bit is set. |

| Words:                                    | 1                                    |                         |                               |

| Cycles:                                   | 1                                    |                         |                               |

| Example:                                  | CLRF                                 | FLAG_RE                 | IG                            |

| Before Instru<br>FLAG_R<br>After Instruct | EG =                                 | 0x5A                    |                               |

| FLAG_R<br>Z                               | EG =<br>=                            | 0x00<br>1               |                               |

| CLRW                                                                                                 | Clear W                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                              | [label] CLRW                                                                                                                                                                                                                                                                                                                                                                                            |

| Operands:                                                                                            | None                                                                                                                                                                                                                                                                                                                                                                                                    |

| Operation:                                                                                           | $\begin{array}{l} 00h \rightarrow (W); \\ 1 \rightarrow Z \end{array}$                                                                                                                                                                                                                                                                                                                                  |

| Status Affected:                                                                                     | Z                                                                                                                                                                                                                                                                                                                                                                                                       |

| Encoding:                                                                                            | 0000 0100 0000                                                                                                                                                                                                                                                                                                                                                                                          |

| Description:                                                                                         | The W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                         |

| Words:                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                       |

| Cycles:                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                       |

| Example:                                                                                             | CLRW                                                                                                                                                                                                                                                                                                                                                                                                    |

| W =<br>After Instruct                                                                                | ion                                                                                                                                                                                                                                                                                                                                                                                                     |

| W =<br>Z =                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                       |

| Z =                                                                                                  | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                    |

| Z =<br>CLRWDT<br>Syntax:                                                                             | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                    |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:                                                                | Clear Watchdog Timer<br>[ label ] CLRWDT<br>None                                                                                                                                                                                                                                                                                                                                                        |

| Z =<br>CLRWDT<br>Syntax:                                                                             | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                    |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:                                                                | Clear Watchdog Timer<br>[ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow TO;$                                                                                                                                                                                                                                                |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:<br>Operation:                                                  | Clear Watchdog Timer<br>[ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$<br>$1 \rightarrow \overline{PD}$                                                                                                                                                                                                    |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:                              | Clear Watchdog Timer<br>[ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$<br>$1 \rightarrow \overline{PD}$<br>$\overline{TO}, \overline{PD}$                                                                                                                                                                  |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                 | Clear Watchdog Timer[ label ] CLRWDTNone $00h \rightarrow WDT;$ $0 \rightarrow WDT$ prescaler (if assigned); $1 \rightarrow \overline{TO};$ $1 \rightarrow \overline{PD}$ $\overline{TO}, \overline{PD}$ $0000  0000  0100$ The CLRWDT instruction resets theWDT. It also resets the prescaler, ifthe prescaler is assigned to theWDT and not Timer0. Status bits                                       |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description: | Clear Watchdog Timer[ label ] CLRWDTNone $00h \rightarrow WDT$ ; $0 \rightarrow WDT$ prescaler (if assigned); $1 \rightarrow \overline{TO}$ ; $1 \rightarrow \overline{PD}$ $\overline{TO}$ , $\overline{PD}$ $0000$ $0000$ $0100$ The CLRWDT instruction resets theWDT. It also resets the prescaler, ifthe prescaler is assigned to theWDT and not Timer0. Status bitsTO and $\overline{PD}$ are set. |

| After Instruction |   |      |

|-------------------|---|------|

| WDT counter       | = | 0x00 |

| WDT prescaler     | = | 0    |

| TO                | = | 1    |

| PD                | = | 1    |

| MOVWF               | Move W to f                      |

|---------------------|----------------------------------|

| Syntax:             | [ <i>label</i> ] MOVWF f         |

| Operands:           | $0 \leq f \leq 31$               |

| Operation:          | $(W) \rightarrow (f)$            |

| Status Affected:    | None                             |

| Encoding:           | 0000 001f ffff                   |

| Description:        | Move data from the W register to |

|                     | register 'f'.                    |

| Words:              | 1                                |

| Cycles:             | 1                                |

| Example:            | MOVWF TEMP_REG                   |

| W<br>After Instruct | REG = 0xFF $= 0x4F$              |

| NOP              | No Operation |        |      |  |

|------------------|--------------|--------|------|--|

| Syntax:          | [ label ]    | NOP    |      |  |

| Operands:        | None         |        |      |  |

| Operation:       | No opera     | ation  |      |  |

| Status Affected: | None         |        |      |  |

| Encoding:        | 0000         | 0000   | 0000 |  |

| Description:     | No opera     | ation. |      |  |

| Words:           | 1            |        |      |  |

| Cycles:          | 1            |        |      |  |

| Example:         | NOP          |        |      |  |

| OPTION           | Load Ol             |             | egister |  |

|------------------|---------------------|-------------|---------|--|

| Syntax:          | [ label ]           | OPTIO       | N       |  |

| Operands:        | None                |             |         |  |

| Operation:       | $(W) \rightarrow C$ | PTION       |         |  |

| Status Affected: | None                |             |         |  |

| Encoding:        | 0000                | 0000        | 0010    |  |

| Description:     |                     | tent of the | 0       |  |

| Words:           | 1                   |             |         |  |

| Cycles:          | 1                   |             |         |  |

| Example          | OPTION              |             |         |  |

| Before Instru    | ction               |             |         |  |

| W                | •                   | 07          |         |  |

| After Instructi  | -                   |             |         |  |

| OPTION           | = 0x                | 07          |         |  |

| RETLW               | Return with Literal in W                                                                                                                                                            |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:             | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:           | $0 \leq k \leq 255$                                                                                                                                                                 |

| Operation:          | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |

| Status Affected:    | None                                                                                                                                                                                |

| Encoding:           | 1000 kkkk kkkk                                                                                                                                                                      |

| Description:        | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address). This<br>is a two-cycle instruction. |

| Words:              | 1                                                                                                                                                                                   |

| Cycles:             | 2                                                                                                                                                                                   |

| Example:            | CALL TABLE ;W contains<br>;table offset<br>;value.<br>• ;W now has table<br>• ;value.                                                                                               |

| TABLE               | <pre>ADDWF PC ;W = offset RETLW k1 ;Begin table RETLW k2 ;</pre>                                                                                                                    |

| Before Instru       |                                                                                                                                                                                     |

| W<br>After Instruct | = 0x07                                                                                                                                                                              |

| After Instruct<br>W | ion<br>= value of k8                                                                                                                                                                |

# PIC16C5X

| RLF                                          | Rotate Left f through Carry                                                                                                                                                                                                   |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                      | [ <i>label</i> ] RLF f,d                                                                                                                                                                                                      |

| Operands:                                    | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                    |

| Operation:                                   | See description below                                                                                                                                                                                                         |

| Status Affected:                             | С                                                                                                                                                                                                                             |

| Encoding:                                    | 0011 01df ffff                                                                                                                                                                                                                |

| Description:                                 | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag (STATUS<0>). If 'd'<br>is 0 the result is placed in the W<br>register. If 'd' is 1 the result is<br>stored back in<br>register 'f'. |

| Words:                                       | 1                                                                                                                                                                                                                             |

| Cycles:                                      | 1                                                                                                                                                                                                                             |

| Example:                                     | RLF REG1,0                                                                                                                                                                                                                    |

| Before Instru<br>REG1<br>C<br>After Instruct | = 1110 0110<br>= 0<br>tion                                                                                                                                                                                                    |

| REG1<br>W<br>C                               | = 1110 0110<br>= 1100 1100<br>= 1                                                                                                                                                                                             |

| RRF                                          | Rotate Right f through Carry                                                                                                                                                                                                   |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                      | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                       |

| Operands:                                    | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                     |

| Operation:                                   | See description below                                                                                                                                                                                                          |

| Status Affected:                             | С                                                                                                                                                                                                                              |

| Encoding:                                    | 0011 00df ffff                                                                                                                                                                                                                 |

| Description:                                 | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag (STATUS<0>). If 'd'<br>is 0 the result is placed in the W<br>register. If 'd' is 1 the result is<br>placed back in<br>register 'f'. |

| Words:                                       | 1                                                                                                                                                                                                                              |

| Cycles:                                      | 1                                                                                                                                                                                                                              |

| Example:                                     | RRF REG1,0                                                                                                                                                                                                                     |

| Before Instru<br>REG1<br>C<br>After Instruct | $= 1110 0110 \\ = 0$                                                                                                                                                                                                           |

| REG1<br>W<br>C                               | = 1110 0110<br>= 0111 0011<br>= 0                                                                                                                                                                                              |

| SLEEP            | Enter SLEEP Mode                                                                                                                                                                                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SLEEP                                                                                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                                                                                         |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT; \\ 0 \rightarrow WDT \text{ prescaler; if assigned} \\ 1 \rightarrow \overline{TO}; \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                                       |

| Status Affected: | TO, PD                                                                                                                                                                                                                                                                       |

| Encoding:        | 0000 0000 0011                                                                                                                                                                                                                                                               |

| Description:     | Time-out status bit $(\overline{TO})$ is set. The<br>power-down status bit $(\overline{PD})$ is<br>cleared. The WDT and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See section on SLEEP for more<br>details. |

| Words:           | 1                                                                                                                                                                                                                                                                            |

| Cycles:          | 1                                                                                                                                                                                                                                                                            |

| Example:         | SLEEP                                                                                                                                                                                                                                                                        |

| SUBWF                                                                                                                                                            | Subtract W from f                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                                                                          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                |

| Operands:                                                                                                                                                        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                |

| Operation:                                                                                                                                                       | $(f) - (W) \rightarrow (dest)$                                                                                                                                                            |

| Status Affected:                                                                                                                                                 | C, DC, Z                                                                                                                                                                                  |

| Encoding:                                                                                                                                                        | 0000 10df ffff                                                                                                                                                                            |

| Description:                                                                                                                                                     | Subtract (2's complement method)<br>the W register from register 'f'. If 'd'<br>is 0 the result is stored in the W<br>register. If 'd' is 1 the result is<br>stored back in register 'f'. |

| Words:                                                                                                                                                           | 1                                                                                                                                                                                         |

| Cycles:                                                                                                                                                          | 1                                                                                                                                                                                         |

| Example 1:                                                                                                                                                       | SUBWF REG1, 1                                                                                                                                                                             |

| Before Instru<br>REG1<br>W<br>C<br>After Instruct<br>REG1<br>W<br>C<br><u>Example 2</u> :<br>Before Instru<br>REG1<br>W<br>C<br>After Instruct<br>REG1<br>W<br>C | action<br>= 3<br>= 2<br>= ?<br>tion<br>= 1<br>= 2<br>= 1 ; result is positive<br>action<br>= 2<br>= 2<br>= ?                                                                              |

| Example 3:<br>Before Ins<br>REG1<br>W<br>C<br>After Instruct<br>REG1<br>W                                                                                        | = 1<br>= 2<br>= ?<br>tion<br>= 0xFF<br>= 2                                                                                                                                                |

| С                                                                                                                                                                | = 0 ; result is negative                                                                                                                                                                  |

| SWAPF                                                                                                                                                     | Swap Nibbles in f                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                                                                   | [label] SWAPF f,d                                                                                                                                                                                                                                                                                 |

| Operands:                                                                                                                                                 | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                        |

| Operation:                                                                                                                                                | (f<3:0>) → (dest<7:4>);<br>(f<7:4>) → (dest<3:0>)                                                                                                                                                                                                                                                 |

| Status Affected:                                                                                                                                          | None                                                                                                                                                                                                                                                                                              |

| Encoding:                                                                                                                                                 | 0011 10df ffff                                                                                                                                                                                                                                                                                    |

| Description:                                                                                                                                              | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is 0<br>the result is placed in W register. I<br>'d' is 1 the result is placed in<br>register 'f'.                                                                                                                           |

| Words:                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                 |

| Cycles:                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                 |

| Example                                                                                                                                                   | SWAPF REG1, 0                                                                                                                                                                                                                                                                                     |

| After Instruct<br>REG1                                                                                                                                    | tion<br>= 0xA5                                                                                                                                                                                                                                                                                    |

| REG1<br>W                                                                                                                                                 | = 0xA5<br>= 0x5A                                                                                                                                                                                                                                                                                  |

| REG1<br>W<br>TRIS                                                                                                                                         | = 0xA5<br>= 0x5A<br>Load TRIS Register                                                                                                                                                                                                                                                            |

| REG1<br>W<br>TRIS<br>Syntax:                                                                                                                              | = 0xA5<br>= 0x5A<br>Load TRIS Register<br>[ <i>label</i> ] TRIS f                                                                                                                                                                                                                                 |

| REG1<br>W<br>TRIS<br>Syntax:<br>Operands:                                                                                                                 | = 0xA5<br>= 0x5A<br>Load TRIS Register<br>[ <i>label</i> ] TRIS f<br>f = 5, 6 or 7                                                                                                                                                                                                                |

| REG1<br>W<br>TRIS<br>Syntax:<br>Operands:<br>Operation:                                                                                                   | = 0xA5<br>= 0x5A<br>Load TRIS Register<br>[ <i>label</i> ] TRIS f<br>f = 5, 6 or 7<br>(W) $\rightarrow$ TRIS register f                                                                                                                                                                           |

| REG1<br>W<br>TRIS<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                                               | = $0xA5$<br>= $0x5A$<br>Load TRIS Register<br>[ <i>label</i> ] TRIS f<br>f = 5, 6 or 7<br>(W) $\rightarrow$ TRIS register f<br>None                                                                                                                                                               |

| REG1<br>W<br>TRIS<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                                                  | = $0xA5$<br>= $0x5A$<br>Load TRIS Register<br>[ <i>label</i> ] TRIS f<br>f = 5, 6 or 7<br>(W) $\rightarrow$ TRIS register f<br>None<br>0000 0000 0fff                                                                                                                                             |

| REG1<br>W<br>TRIS<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                                               | = $0xA5$<br>= $0x5A$<br>Load TRIS Register<br>[ <i>label</i> ] TRIS f<br>f = 5, 6 or 7<br>(W) $\rightarrow$ TRIS register f<br>None<br>0000 0000 0fff<br>TRIS register 'f' (f = 5, 6, or 7) is                                                                                                    |

| REG1<br>W<br>TRIS<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                                                  | = 0xA5<br>= 0x5A<br>Load TRIS Register<br>[ <i>label</i> ] TRIS f<br>f = 5, 6 or 7<br>(W) $\rightarrow$ TRIS register f<br>None<br>0000 0000 0fff<br>TRIS register 'f' (f = 5, 6, or 7) is<br>loaded with the contents of the W                                                                   |

| REG1<br>W<br>TRIS<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                                                  | = 0xA5<br>= 0x5A<br>Load TRIS Register<br>[ <i>label</i> ] TRIS f<br>f = 5, 6 or 7<br>(W) → TRIS register f<br>None<br>0000 0000 0fff<br>TRIS register 'f' (f = 5, 6, or 7) is<br>loaded with the contents of the W<br>register.                                                                  |

| REG1<br>W<br>TRIS<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:                                        | = 0xA5<br>= 0x5A<br>Load TRIS Register<br>[ <i>label</i> ] TRIS f<br>f = 5, 6 or 7<br>(W) → TRIS register f<br>None<br>0000 0000 0fff<br>TRIS register 'f' (f = 5, 6, or 7) is<br>loaded with the contents of the W<br>register.<br>1                                                             |

| REG1<br>W<br>TRIS<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Example<br>Before Instru | = $0xA5$<br>= $0x5A$<br>Load TRIS Register<br>[ <i>label</i> ] TRIS f<br>f = 5, 6 or 7<br>(W) $\rightarrow$ TRIS register f<br>None<br>0000  0000  0fff<br>TRIS register 'f' (f = 5, 6, or 7) is<br>loaded with the contents of the W<br>register.<br>1<br>1<br>TRIS PORTB<br>Interval 1          |

| REG1<br>W<br>TRIS<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Example                  | = $0xA5$<br>= $0x5A$<br>Load TRIS Register<br>[ <i>label</i> ] TRIS f<br>f = 5, 6 or 7<br>(W) $\rightarrow$ TRIS register f<br>None<br>0000  0000  0fff<br>TRIS register 'f' (f = 5, 6, or 7) is<br>loaded with the contents of the W<br>register.<br>1<br>1<br>TRIS PORTB<br>inction<br>= $0xA5$ |

# PIC16C5X

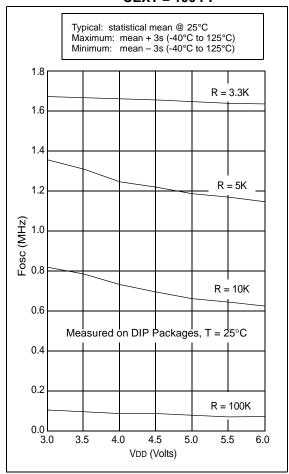

# **FIGURE 14-2: TYPICAL RC OSC** FREQUENCY vs. VDD, CEXT = 20 PF Typical: statistical mean @ 25°C Maximum: mean + 3s (-40°C to 125°C) Minimum: mean – 3s (-40°C to 125°C) 5.5 R = 3.3K5.0 4.5 R = 5K 4.0 3.5 Fosc (MHz) 3.0 R = 10K 2.5 2.0 Measured on DIP Packages, $T = 25^{\circ}C$ 1.5 1.0 R = 100K 0.5 0.0 3.0 3.5 4.0 4.5 5.0 5.5 6.0 VDD (Volts)

### FIGURE 14-3:

### TYPICAL RC OSC FREQUENCY vs. VDD, CEXT = 100 PF

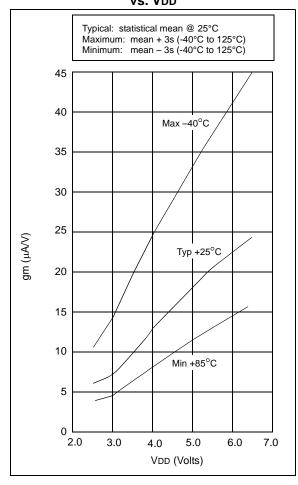

### FIGURE 16-18: TRANSCONDUCTANCE (gm) OF LP OSCILLATOR vs. VDD

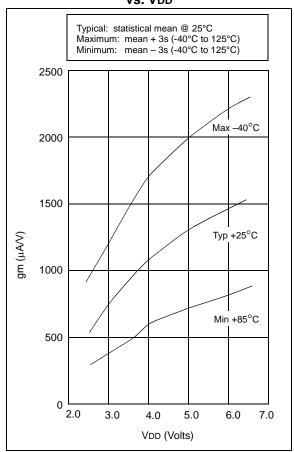

# FIGURE 16-19:

### TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

NOTES:

# 17.4 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. Tp | pS                                      |                    |

|-------|-----------------------------------------|--------------------|

| Т     |                                         |                    |

| F     | Frequency                               | T Time             |

| Lowe  | ercase letters (pp) and their meanings: |                    |

| рр    |                                         |                    |

| 2     | to                                      | mc MCLR            |

| ck    | CLKOUT                                  | osc oscillator     |

| су    | cycle time                              | os OSC1            |

| drt   | device reset timer                      | t0 T0CKI           |

| io    | I/O port                                | wdt watchdog timer |

| Uppe  | ercase letters and their meanings:      |                    |

| S     |                                         |                    |

| F     | Fall                                    | P Period           |

| н     | High                                    | R Rise             |

| T     | Invalid (Hi-impedance)                  | V Valid            |

| L     | Low                                     | Z Hi-impedance     |

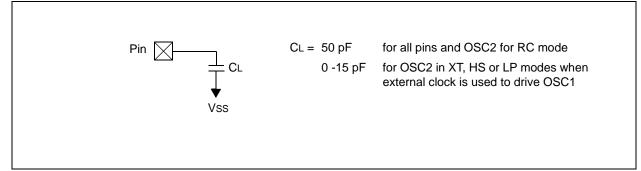

# FIGURE 17-5: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS -PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/C58B/CR58B-04, 20

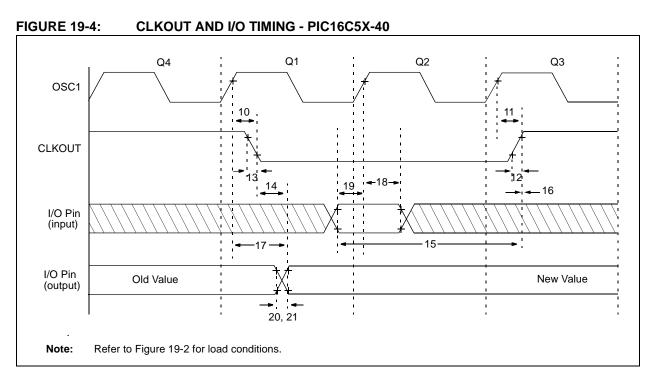

| TABLE 19-2: | CLKOUT AND I/O TIMING REQUIREMENTS - PIC16C5X-40 |

|-------------|--------------------------------------------------|

|             |                                                  |

| AC Characteristics |          | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |              |      |      |       |

|--------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|-------|

| Param<br>No.       | Symbol   | Characteristic                                                                                                                      | Min          | Тур† | Max  | Units |

| 10                 | TosH2ckL | OSC1↑ to CLKOUT↓ <sup>(1,2)</sup>                                                                                                   | —            | 15   | 30** | ns    |

| 11                 | TosH2ckH | OSC1↑ to CLKOUT↑ <sup>(1,2)</sup>                                                                                                   | —            | 15   | 30** | ns    |

| 12                 | TckR     | CLKOUT rise time <sup>(1,2)</sup>                                                                                                   | —            | 5.0  | 15** | ns    |

| 13                 | TckF     | CLKOUT fall time <sup>(1,2)</sup>                                                                                                   | —            | 5.0  | 15** | ns    |

| 14                 | TckL2ioV | CLKOUT↓ to Port out valid <sup>(1,2)</sup>                                                                                          | —            | —    | 40** | ns    |

| 15                 | TioV2ckH | Port in valid before CLKOUT <sup>(1,2)</sup>                                                                                        | 0.25 TCY+30* | —    | _    | ns    |

| 16                 | TckH2iol | Port in hold after CLKOUT <sup>(1,2)</sup>                                                                                          | 0*           | —    | _    | ns    |

| 17                 | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(2)</sup>                                                                       | —            | —    | 100  | ns    |

| 18                 | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid<br>(I/O in hold time)                                                            | TBD          | —    | —    | ns    |

| 19                 | TioV2osH | Port input valid to OSC1↑<br>(I/O in setup time)                                                                                    | TBD          | —    | —    | ns    |

| 20                 | TioR     | Port output rise time <sup>(2)</sup>                                                                                                | —            | 10   | 25** | ns    |

| 21                 | TioF     | Port output fall time <sup>(2)</sup>                                                                                                | —            | 10   | 25** | ns    |

\* These parameters are characterized but not tested.

- \*\* These parameters are design targets and are not tested. No characterization data available at this time.

- † Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

2: Refer to Figure 19-2 for load conditions.

© 1997-2013 Microchip Technology Inc.

# PIC16C5X