Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 768B (512 x 12)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 25 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c54c-20i-so |

|                            |                                                                            |

NOTES:

TABLE 3-2: PINOUT DESCRIPTION - PIC16C55, PIC16C57, PIC16CR57

| Din Name    | Pin Number |      | Pin Buffer | Buffer | Description |                                                                                                                                                                                                          |

|-------------|------------|------|------------|--------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name    | DIP        | SOIC | SSOP       | Туре   | Type        | Description                                                                                                                                                                                              |

| RA0         | 6          | 6    | 5          | I/O    | TTL         | Bi-directional I/O port                                                                                                                                                                                  |

| RA1         | 7          | 7    | 6          | I/O    | TTL         | ·                                                                                                                                                                                                        |

| RA2         | 8          | 8    | 7          | I/O    | TTL         |                                                                                                                                                                                                          |

| RA3         | 9          | 9    | 8          | I/O    | TTL         |                                                                                                                                                                                                          |

| RB0         | 10         | 10   | 9          | I/O    | TTL         | Bi-directional I/O port                                                                                                                                                                                  |

| RB1         | 11         | 11   | 10         | I/O    | TTL         | ·                                                                                                                                                                                                        |

| RB2         | 12         | 12   | 11         | I/O    | TTL         |                                                                                                                                                                                                          |

| RB3         | 13         | 13   | 12         | I/O    | TTL         |                                                                                                                                                                                                          |

| RB4         | 14         | 14   | 13         | I/O    | TTL         |                                                                                                                                                                                                          |

| RB5         | 15         | 15   | 15         | I/O    | TTL         |                                                                                                                                                                                                          |

| RB6         | 16         | 16   | 16         | I/O    | TTL         |                                                                                                                                                                                                          |

| RB7         | 17         | 17   | 17         | I/O    | TTL         |                                                                                                                                                                                                          |

| RC0         | 18         | 18   | 18         | I/O    | TTL         | Bi-directional I/O port                                                                                                                                                                                  |

| RC1         | 19         | 19   | 19         | I/O    | TTL         |                                                                                                                                                                                                          |

| RC2         | 20         | 20   | 20         | I/O    | TTL         |                                                                                                                                                                                                          |

| RC3         | 21         | 21   | 21         | I/O    | TTL         |                                                                                                                                                                                                          |

| RC4         | 22         | 22   | 22         | I/O    | TTL         |                                                                                                                                                                                                          |

| RC5         | 23         | 23   | 23         | I/O    | TTL         |                                                                                                                                                                                                          |

| RC6         | 24         | 24   | 24         | I/O    | TTL         |                                                                                                                                                                                                          |

| RC7         | 25         | 25   | 25         | I/O    | TTL         |                                                                                                                                                                                                          |

| T0CKI       | 1          | 1    | 2          | I      | ST          | Clock input to Timer0. Must be tied to Vss or VDD, if not in use, to reduce current consumption.                                                                                                         |

| MCLR        | 28         | 28   | 28         | I      | ST          | Master clear (RESET) input. This pin is an active low RESET to the device.                                                                                                                               |

| OSC1/CLKIN  | 27         | 27   | 27         | I      | ST          | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT | 26         | 26   | 26         | 0      | _           | Oscillator crystal output. Connects to crystal or resonator in crystal Oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| VDD         | 2          | 2    | 3,4        | Р      | _           | Positive supply for logic and I/O pins.                                                                                                                                                                  |

| Vss         | 4          | 4    | 1,14       | Р      |             | Ground reference for logic and I/O pins.                                                                                                                                                                 |

| N/C         | 3,5        | 3,5  |            | _      |             | Unused, do not connect.                                                                                                                                                                                  |

Legend: I = input, O = output, I/O = input/output, P = power, — = Not Used, TTL = TTL input, ST = Schmitt Trigger input

#### 5.1 Power-On Reset (POR)

The PIC16C5X family incorporates on-chip Power-On Reset (POR) circuitry which provides an internal chip RESET for most power-up situations. To use this feature, the user merely ties the  $\overline{\text{MCLR}}/\text{VPP}$  pin to VDD. A simplified block diagram of the on-chip Power-On Reset circuit is shown in Figure 5-1.

The Power-On Reset circuit and the Device Reset Timer (Section 5.2) circuit are closely related. On power-up, the RESET latch is set and the DRT is RESET. The DRT timer begins counting once it detects MCLR to be high. After the time-out period, which is typically 18 ms, it will RESET the reset latch and thus end the on-chip RESET signal.

A power-up example where  $\overline{MCLR}$  is not tied to VDD is shown in Figure 5-3. VDD is allowed to rise and stabilize before bringing  $\overline{MCLR}$  high. The chip will actually come out of reset TDRT msec after  $\overline{MCLR}$  goes high.

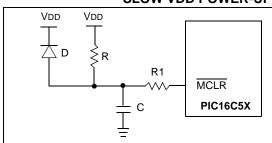

In Figure 5-4, the on-chip Power-On Reset feature is being used (MCLR and VDD are tied together). The VDD is stable before the start-up timer times out and there is no problem in getting a proper RESET. However, Figure 5-5 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses a high on the MCLR/VPP pin, and when the MCLR/VPP pin (and VDD) actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip is, therefore, not guaranteed to function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 5-2).

**Note:** When the device starts normal operation (exits the RESET condition), device oper-

ating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For more information on PIC16C5X POR, see *Power-Up Considerations* - AN522 in the <u>Embedded Control Handbook</u>.

The POR circuit does not produce an internal RESET when VDD declines.

# FIGURE 5-2: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- External Power-On Reset circuit is required only if VDD power-up is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device electrical specification.

- R1 =  $100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{\text{MCLR}}$  from external capacitor C in the event of  $\overline{\text{MCLR}}$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

#### **7.0 I/O PORTS**

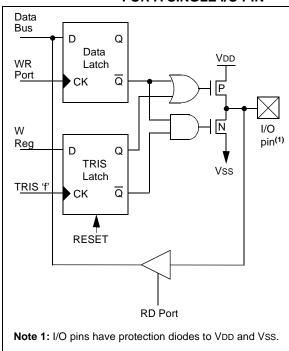

As with any other register, the I/O Registers can be written and read under program control. However, read instructions (e.g., MOVF PORTB, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers (TRISA, TRISB, TRISC) are all set.

#### 7.1 PORTA

PORTA is a 4-bit I/O Register. Only the low order 4 bits are used (RA<3:0>). Bits 7-4 are unimplemented and read as '0's.

#### 7.2 PORTB

PORTB is an 8-bit I/O Register (PORTB<7:0>).

#### 7.3 PORTC

PORTC is an 8-bit I/O Register for PIC16C55, PIC16C57 and PIC16CR57.

PORTC is a General Purpose Register for PIC16C54, PIC16CR54, PIC16C56, PIC16CR56, PIC16C58 and PIC16CR58.

### 7.4 TRIS Registers

The Output Driver Control Registers are loaded with the contents of the W Register by executing the TRIS f instruction. A '1' from a TRIS Register bit puts the corresponding output driver in a hi-impedance (input) mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer.

Note: A read of the ports reads the pins, not the output data latches. That is, if an output driver on a pin is enabled and driven high, but the external system is holding it low, a read of the port will indicate that the pin is low.

The TRIS Registers are "write-only" and are set (output drivers disabled) upon RESET.

#### 7.5 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 7-1. All ports may be used for both input and output operation. For input operations these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF PORTB, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit (in TRISA, TRISB, TRISC) must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin can be programmed individually as input or output.

FIGURE 7-1: EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

TABLE 7-1: SUMMARY OF PORT REGISTERS

| Address | Name  | Bit 7 | Bit 6                                       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on MCLR and WDT Reset |

|---------|-------|-------|---------------------------------------------|-------|-------|-------|-------|-------|-------|-------------------------------|-----------------------------|

| N/A     | TRIS  |       | I/O Control Registers (TRISA, TRISB, TRISC) |       |       |       |       |       |       | 1111 1111                     | 1111 1111                   |

| 05h     | PORTA | _     | _                                           | _     | _     | RA3   | RA2   | RA1   | RA0   | xxxx                          | uuuu                        |

| 06h     | PORTB | RB7   | RB6                                         | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | xxxx xxxx                     | uuuu uuuu                   |

| 07h     | PORTC | RC7   | RC6                                         | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx                     | uuuu uuuu                   |

Legend: x = unknown, u = unchanged, — = unimplemented, read as '0', Shaded cells = unimplemented, read as '0'

| ADDWF            | Add                    | W            | and f                                                                |               |                  |                    |

|------------------|------------------------|--------------|----------------------------------------------------------------------|---------------|------------------|--------------------|

| Syntax:          | [ lab                  | el]          | ADDWF                                                                | f,d           |                  |                    |

| Operands:        | 0 ≤ 1<br>d ∈           |              | -                                                                    |               |                  |                    |

| Operation:       | (W)                    | + (f)        | $\rightarrow$ (dest)                                                 |               |                  |                    |

| Status Affected: | C, D                   | )C, Z        | <u> </u>                                                             |               |                  |                    |

| Encoding:        | 00                     | 01           | 11df                                                                 | ff            | ff               |                    |

| Description:     | and<br>is st<br>'1' th | regi<br>orec | contents of<br>ster 'f'. If 'o<br>I in the W<br>esult is sto<br>'f'. | d' is<br>regi | 0 the<br>ster. I | result<br>f 'd' is |

| Words:           | 1                      |              |                                                                      |               |                  |                    |

| Cycles:          | 1                      |              |                                                                      |               |                  |                    |

| Example:         | ADD                    | WF           | TEMP_RE                                                              | EG,           | 0                |                    |

| Before Instr     | uctio                  | n            |                                                                      |               |                  |                    |

| W                |                        | =            | 0x17                                                                 |               |                  |                    |

| TEMP_I           |                        | =            | 0xC2                                                                 |               |                  |                    |

|                  | After Instruction      |              |                                                                      |               |                  |                    |

| W                |                        | =            | 0xD9                                                                 |               |                  |                    |

| TEMP_I           | REG                    | =            | 0xC2                                                                 |               |                  |                    |

| ANDWF                                                         | AND W with f                                                                                                                                                              |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                       | [ label ] ANDWF f,d                                                                                                                                                       |

| Operands:                                                     | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                         |

| Operation:                                                    | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                        |

| Status Affected:                                              | Z                                                                                                                                                                         |

| Encoding:                                                     | 0001 01df ffff                                                                                                                                                            |

| Description:                                                  | The contents of the W register are AND'ed with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is '1' the result is stored back in register 'f'. |

| Words:                                                        | 1                                                                                                                                                                         |

| Cycles:                                                       | 1                                                                                                                                                                         |

| Example:                                                      | ANDWF TEMP_REG, 1                                                                                                                                                         |

| Before Instru<br>W<br>TEMP_I<br>After Instruct<br>W<br>TEMP_I | = 0x17 $REG = 0xC2$ $tion$ $= 0x17$                                                                                                                                       |

| ANDLW                                                     | AND literal with W                                                                                                |  |  |  |  |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                                   | [ label ] ANDLW k                                                                                                 |  |  |  |  |

| Operands:                                                 | $0 \leq k \leq 255$                                                                                               |  |  |  |  |

| Operation:                                                | (W).AND. (k) $\rightarrow$ (W)                                                                                    |  |  |  |  |

| Status Affected:                                          | Z                                                                                                                 |  |  |  |  |

| Encoding:                                                 | 1110 kkkk kkkk                                                                                                    |  |  |  |  |

| Description:                                              | The contents of the W register are AND'ed with the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |  |

| Words:                                                    | 1                                                                                                                 |  |  |  |  |

| Cycles:                                                   | 1                                                                                                                 |  |  |  |  |

| Example:                                                  | ANDLW H'5F'                                                                                                       |  |  |  |  |

| Before Instruction  W = 0xA3  After Instruction  W = 0x03 |                                                                                                                   |  |  |  |  |

| BCF                      | Bit Clea                         | r f          |             |  |  |

|--------------------------|----------------------------------|--------------|-------------|--|--|

| Syntax:                  | [ label ]                        | BCF f,t      | )           |  |  |

| Operands:                | $0 \le f \le 31$ $0 \le b \le 7$ |              |             |  |  |

| Operation:               | $0 \rightarrow (f < b >)$        |              |             |  |  |

| Status Affected:         | None                             |              |             |  |  |

| Encoding:                | 0100                             | bbbf         | ffff        |  |  |

| Description:             | Bit 'b' in                       | register 'f' | is cleared. |  |  |

| Words:                   | 1                                |              |             |  |  |

| Cycles:                  | 1                                |              |             |  |  |

| Example:                 | BCF                              | FLAG_RE      | EG, 7       |  |  |

| Before Instruction       |                                  |              |             |  |  |

| FLAG_R<br>After Instruct | 0xC7                             |              |             |  |  |

| FLAG_R                   |                                  | 0x47         |             |  |  |

| COMF                                                 | Complement f                            |                                       |                                                                     |  |  |  |

|------------------------------------------------------|-----------------------------------------|---------------------------------------|---------------------------------------------------------------------|--|--|--|

| Syntax:                                              | [ label ]                               | COMF                                  | f,d                                                                 |  |  |  |

| Operands:                                            | $0 \le f \le 31$<br>$d \in [0,1]$       |                                       |                                                                     |  |  |  |

| Operation:                                           | $(\overline{f}) \rightarrow (dest)$     |                                       |                                                                     |  |  |  |

| Status Affected:                                     | Z                                       |                                       |                                                                     |  |  |  |

| Encoding:                                            | 0010                                    | 01df                                  | ffff                                                                |  |  |  |

| Description:                                         | complent is stored the result register. | nented. If<br>in the W<br>It is store | egister 'f' are 'd' is 0 the result register. If 'd' is 1 d back in |  |  |  |

| Words:                                               | 1                                       |                                       |                                                                     |  |  |  |

| Cycles:                                              | 1                                       |                                       |                                                                     |  |  |  |

| Example:                                             | COMF                                    | REG1,0                                |                                                                     |  |  |  |

| Before Instru<br>REG1<br>After Instruct<br>REG1<br>W | = 02<br>ion<br>= 02                     | x13<br>x13<br>xEC                     |                                                                     |  |  |  |

| DECF                                                    | Decrement f                                                                                                                        |                    |      |  |  |  |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|--|--|--|

| Syntax:                                                 | [ label ]                                                                                                                          | [ label ] DECF f,d |      |  |  |  |

| Operands:                                               | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                  |                    |      |  |  |  |

| Operation:                                              | $(f) - 1 \rightarrow$                                                                                                              | (dest)             |      |  |  |  |

| Status Affected:                                        | Z                                                                                                                                  |                    |      |  |  |  |

| Encoding:                                               | 0000                                                                                                                               | 11df               | ffff |  |  |  |

| Description:                                            | Decrement register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. |                    |      |  |  |  |

| Words:                                                  | 1                                                                                                                                  |                    |      |  |  |  |

| Cycles:                                                 | 1                                                                                                                                  |                    |      |  |  |  |

| Example:                                                | DECF                                                                                                                               | CNT,               | 1    |  |  |  |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0:<br>= 0<br>tion                                                                                                                | x01<br>x00         |      |  |  |  |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                      |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] DECFSZ f,d                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Operands:        | $0 \le f \le 31$                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                  | d ∈ [0,1]                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Operation:       | $(f) - 1 \rightarrow d$ ; skip if result = 0                                                                                                                                                                                                                                                                |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Encoding:        | 0010 11df ffff                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'.  If the result is 0, the next instruction, which is already fetched, is discarded and a NOP is executed instead making it a two-cycle instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Example:         | HERE DECFSZ CNT, 1                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                  | GOTO LOOP CONTINUE •                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Before Instru    | uction                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| PC               | = address (HERE)                                                                                                                                                                                                                                                                                            |  |  |  |  |

| After Instruct   |                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| CNT              | = CNT - 1;                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| if CNT<br>PC     | = 0,                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| if CNT           | = address (CONTINUE);<br>≠ 0.                                                                                                                                                                                                                                                                               |  |  |  |  |

| PC               | = address (HERE+1)                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] IORLW k                                                                                                |

| Operands:        | $0 \leq k \leq 255$                                                                                              |

| Operation:       | (W) .OR. $(k) \rightarrow (W)$                                                                                   |

| Status Affected: | Z                                                                                                                |

| Encoding:        | 1101 kkkk kkkk                                                                                                   |

| Description:     | The contents of the W register are OR'ed with the eight bit literal 'k'. The result is placed in the W register. |

| Words:           | 1                                                                                                                |

| Cycles:          | 1                                                                                                                |

| Example:         | IORLW 0x35                                                                                                       |

| Before Instru    | uction                                                                                                           |

| W =              |                                                                                                                  |

| After Instruc    |                                                                                                                  |

| W =              | 0xBF                                                                                                             |

| Z =              | 0                                                                                                                |

| IORWF                                                                                      | Inclusive OR W with f                                                                                                                                     |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                    | [ label ] IORWF f,d                                                                                                                                       |

| Operands:                                                                                  | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                         |

| Operation:                                                                                 | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                          |

| Status Affected:                                                                           | Z                                                                                                                                                         |

| Encoding:                                                                                  | 0001 00df ffff                                                                                                                                            |

| Description:                                                                               | Inclusive OR the W register with register 'f'. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'. |

| Words:                                                                                     | 1                                                                                                                                                         |

| Cycles:                                                                                    | 1                                                                                                                                                         |

| Example:                                                                                   | IORWF RESULT, 0                                                                                                                                           |

| Before Instru<br>RESUL <sup>-</sup><br>W<br>After Instruct<br>RESUL <sup>-</sup><br>W<br>Z | $\Gamma = 0x13$<br>= 0x91<br>tion                                                                                                                         |

| MOVF                                         | Move f                                                                                                                                                                                                                               |  |  |  |  |  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                      | [ label ] MOVF f,d                                                                                                                                                                                                                   |  |  |  |  |  |

| Operands:                                    | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                                                                                    |  |  |  |  |  |

| Operation:                                   | $(f) \rightarrow (dest)$                                                                                                                                                                                                             |  |  |  |  |  |

| Status Affected:                             | Z                                                                                                                                                                                                                                    |  |  |  |  |  |

| Encoding:                                    | 0010 00df ffff                                                                                                                                                                                                                       |  |  |  |  |  |

| Description:                                 | The contents of register 'f' is moved to destination 'd'. If 'd' is 0, destination is the W register. If 'd' is 1, the destination is file register 'f'. 'd' is 1 is useful to test a file register since status flag Z is affected. |  |  |  |  |  |

| Words:                                       | 1                                                                                                                                                                                                                                    |  |  |  |  |  |

| Cycles:                                      | 1                                                                                                                                                                                                                                    |  |  |  |  |  |

| Example:                                     | MOVF FSR, 0                                                                                                                                                                                                                          |  |  |  |  |  |

| After Instruction  W = value in FSR register |                                                                                                                                                                                                                                      |  |  |  |  |  |

| MOVLW                      | Move Lit            | teral to W | ı                  |  |  |

|----------------------------|---------------------|------------|--------------------|--|--|

| Syntax:                    | [ label ]           | MOVLW      | k                  |  |  |

| Operands:                  | $0 \le k \le 2$     | 55         |                    |  |  |

| Operation:                 | $k \rightarrow (W)$ |            |                    |  |  |

| Status Affected:           | None                |            |                    |  |  |

| Encoding:                  | 1100                | kkkk       | kkkk               |  |  |

| Description:               | The eighthe W re    |            | 'k' is loaded into |  |  |

| Words:                     | 1                   |            |                    |  |  |

| Cycles:                    | 1                   |            |                    |  |  |

| Example:                   | MOVLW               | 0x5A       |                    |  |  |

| After Instruction W = 0x5A |                     |            |                    |  |  |

#### 12.0 ELECTRICAL CHARACTERISTICS - PIC16C54A

### Absolute Maximum Ratings(†)

| Ambient Temperature under bias                                                     |                        |

|------------------------------------------------------------------------------------|------------------------|

| Storage Temperature                                                                | 65°C to +150°C         |

| Voltage on VDD with respect to Vss                                                 |                        |

| Voltage on MCLR with respect to Vss <sup>(1)</sup>                                 | 0V to +14V             |

| Voltage on all other pins with respect to Vss                                      | 0.6V to (VDD + 0.6V)   |

| Total power dissipation <sup>(2)</sup>                                             | 800 mW                 |

| Max. current out of Vss pin                                                        | 150 mA                 |

| Max. current into VDD pin                                                          |                        |

| Max. current into an input pin (T0CKI only)                                        | ±500 μA                |

| Input clamp current, IiK (VI < 0 or VI > VDD)                                      | ±20 mA                 |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                     | ±20 mA                 |

| Max. output current sunk by any I/O pin                                            | 25 mA                  |

| Max. output current sourced by any I/O pin                                         | 20 mA                  |

| Max. output current sourced by a single I/O port (PORTA, B or C)                   | 40 mA                  |

| Max. output current sunk by a single I/O port (PORTA, B or C)                      | 50 mA                  |

| Note 1: Voltage spikes below Vss at the MCLR pin_inducing currents greater than 80 | ) mA may cause latch-u |

**Note 1:** Voltage spikes below Vss at the  $\overline{\text{MCLR}}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50 to 100  $\Omega$  should be used when applying a "low" level to the  $\overline{\text{MCLR}}$  pin rather than pulling this pin directly to Vss.

<sup>2:</sup> Power Dissipation is calculated as follows: Pdis = VDD x {IDD –  $\Sigma$  IOH} +  $\Sigma$  {(VDD – VOH) x IOH} +  $\Sigma$ (VOL x IOL)

<sup>†</sup> NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## 12.6 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| T                                          |                |

|--------------------------------------------|----------------|

| F Frequency                                | T Time         |

| Lowercase letters (pp) and their meanings: |                |

| рр                                         |                |

| 2 to                                       | mc MCLR        |

| ck CLKOUT                                  | osc oscillator |

| cy cycle time                              | os OSC1        |

t0 T0CKI

wdt watchdog timer

Uppercase letters and their meanings:

drt device reset timer

io I/O port

| OPP | stoadd tottord arra trion trioarmigo. |   |              |

|-----|---------------------------------------|---|--------------|

| S   |                                       |   |              |

| F   | Fall                                  | Р | Period       |

| Н   | High                                  | R | Rise         |

| I   | Invalid (Hi-impedance)                | V | Valid        |

| L   | Low                                   | Z | Hi-impedance |

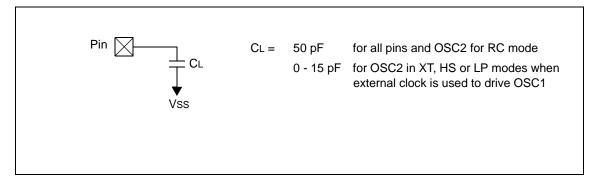

### FIGURE 12-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS - PIC16C54/55/56/57

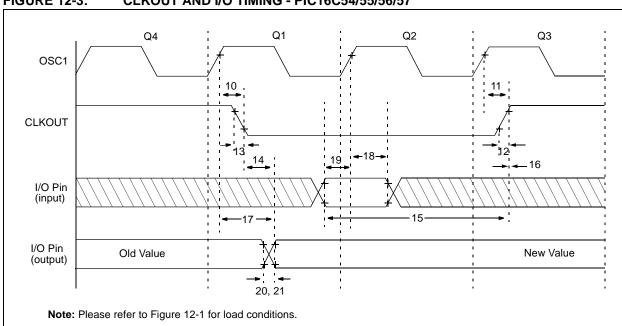

FIGURE 12-3: CLKOUT AND I/O TIMING - PIC16C54/55/56/57

TABLE 12-2: CLKOUT AND I/O TIMING REQUIREMENTS - PIC16C54/55/56/57

| AC Characteristics Standard Operating Conditions (unless otherwise specific Operating Temperature $0^{\circ}\text{C} \leq \text{TA} \leq +70^{\circ}\text{C}$ for commercia $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C}$ for extended |          |                                                                       |              |      |      |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------|--------------|------|------|-------|

| Param<br>No.                                                                                                                                                                                                                                                                                                                         | Symbol   | Characteristic                                                        | Min          | Typ† | Max  | Units |

| 10                                                                                                                                                                                                                                                                                                                                   | TosH2ckL | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                                       | _            | 15   | 30** | ns    |

| 11                                                                                                                                                                                                                                                                                                                                   | TosH2ckH | OSC1↑ to CLKOUT↑ <sup>(1)</sup>                                       | _            | 15   | 30** | ns    |

| 12                                                                                                                                                                                                                                                                                                                                   | TckR     | CLKOUT rise time <sup>(1)</sup>                                       | _            | 5.0  | 15** | ns    |

| 13                                                                                                                                                                                                                                                                                                                                   | TckF     | CLKOUT fall time <sup>(1)</sup>                                       | _            | 5.0  | 15** | ns    |

| 14                                                                                                                                                                                                                                                                                                                                   | TckL2ioV | CLKOUT↓ to Port out valid <sup>(1)</sup>                              | _            | _    | 40** | ns    |

| 15                                                                                                                                                                                                                                                                                                                                   | TioV2ckH | Port in valid before CLKOUT <sup>(1)</sup>                            | 0.25 TCY+30* | _    | _    | ns    |

| 16                                                                                                                                                                                                                                                                                                                                   | TckH2ioI | Port in hold after CLKOUT <sup>(1)</sup>                              | 0*           | _    | _    | ns    |

| 17                                                                                                                                                                                                                                                                                                                                   | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(2)</sup>         | _            | _    | 100* | ns    |

| 18                                                                                                                                                                                                                                                                                                                                   | TosH2ioI | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid (I/O in hold time) | TBD          | _    | _    | ns    |

| 19                                                                                                                                                                                                                                                                                                                                   | TioV2osH | Port input valid to OSC1↑ (I/O in setup time)                         | TBD          | _    | _    | ns    |

| 20                                                                                                                                                                                                                                                                                                                                   | TioR     | Port output rise time <sup>(2)</sup>                                  | _            | 10   | 25** | ns    |

| 21                                                                                                                                                                                                                                                                                                                                   | TioF     | Port output fall time <sup>(2)</sup>                                  | _            | 10   | 25** | ns    |

<sup>\*</sup> These parameters are characterized but not tested.

**Note 1:** Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

2: Please refer to Figure 12-1 for load conditions.

<sup>\*\*</sup> These parameters are design targets and are not tested. No characterization data available at this time.

<sup>†</sup> Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

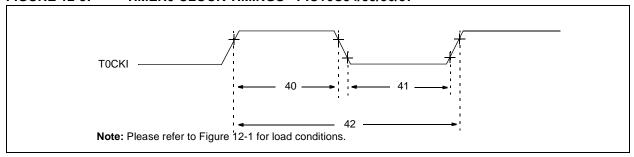

#### FIGURE 12-5: TIMER0 CLOCK TIMINGS - PIC16C54/55/56/57

TABLE 12-4: TIMERO CLOCK REQUIREMENTS - PIC16C54/55/56/57

| AC Ch        | AC Characteristics Standard Operating Conditions (unless otherwise specified)  Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                                        |                              |      |     |          |                                                                |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------|------|-----|----------|----------------------------------------------------------------|

| Param<br>No. | Symbol                                                                                                                                                                                                                                                              | Characteristic                                         | Min                          | Тур† | Max | Units    | Conditions                                                     |

| 40           | Tt0H                                                                                                                                                                                                                                                                | TOCKI High Pulse Width - No Prescaler - With Prescaler | 0.5 Tcy + 20*                | _    |     | ns<br>ns |                                                                |

| 41           | Tt0L                                                                                                                                                                                                                                                                | Tocki Low Pulse Width - No Prescaler - With Prescaler  | 0.5 TcY + 20*<br>10*         |      | _   | ns<br>ns |                                                                |

| 42           | Tt0P                                                                                                                                                                                                                                                                | T0CKI Period                                           | 20 or <u>TCY + 40</u> *<br>N | _    | _   | ns       | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |

These parameters are characterized but not tested.

<sup>†</sup> Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

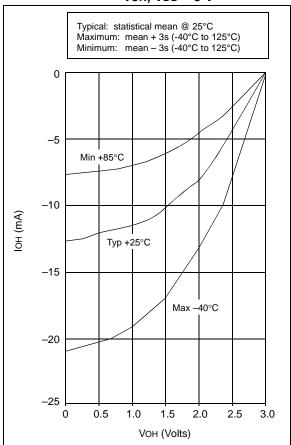

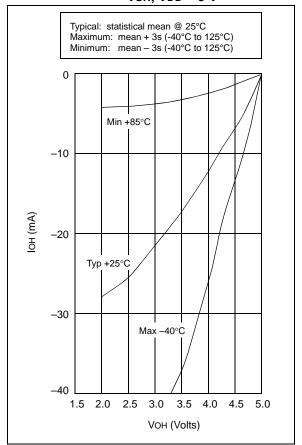

FIGURE 14-19: PORTA, B AND C IOH vs. Voh, VDD = 3 V

FIGURE 14-20: PORTA, B AND C IOH vs. Voh, VDD = 5 V

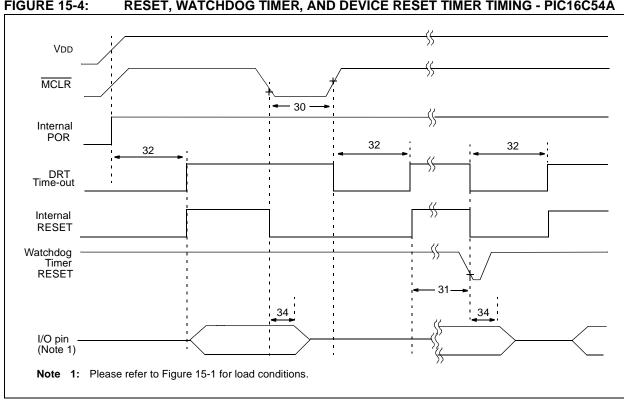

**FIGURE 15-4:** RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16C54A

**TABLE 15-3:** RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16C54A

| ./\BLL 10                                                       | TO COUNTY TO STATE OF THE PROPERTY OF THE PROP |                                                                  |   |                      |                  |          |                  |    |  |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---|----------------------|------------------|----------|------------------|----|--|

|                                                                 | Standard Operating Conditions (unless otherwise specified)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                  |   |                      |                  |          |                  |    |  |

|                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Operating Temperature                                            | ( | $0^{\circ}C \leq TA$ | . ≤ <b>+7</b> 0° | C for co | mmerci           | al |  |

| AC Charac                                                       | cteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $-40^{\circ}$ C $\leq$ TA $\leq$ +85 $^{\circ}$ C for industrial |   |                      |                  |          |                  |    |  |

| $-20$ °C $\leq$ TA $\leq$ +85°C for industrial - PIC16LV54A-02I |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                  |   |                      |                  |          | · PIC16LV54A-02I |    |  |