Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 768B (512 x 12)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 25 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6.25V                                                                |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c54t-xt-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 5-3: RESET CONDITIONS FOR ALL REGISTERS

| Register                       | Address | Power-On Reset | MCLR or WDT Reset |

|--------------------------------|---------|----------------|-------------------|

| W                              | N/A     | XXXX XXXX      | uuuu uuuu         |

| TRIS                           | N/A     | 1111 1111      | 1111 1111         |

| OPTION                         | N/A     | 11 1111        | 11 1111           |

| INDF                           | 00h     | XXXX XXXX      | uuuu uuuu         |

| TMR0                           | 01h     | XXXX XXXX      | uuuu uuuu         |

| PCL                            | 02h     | 1111 1111      | 1111 1111         |

| STATUS                         | 03h     | 0001 1xxx      | 000q quuu         |

| FSR <sup>(1)</sup>             | 04h     | 1xxx xxxx      | luuu uuuu         |

| PORTA                          | 05h     | xxxx           | uuuu              |

| PORTB                          | 06h     | XXXX XXXX      | uuuu uuuu         |

| PORTC <sup>(2)</sup>           | 07h     | XXXX XXXX      | uuuu uuuu         |

| General Purpose Register Files | 07-7Fh  | XXXX XXXX      | սսսս սսսս         |

Legend: x = unknown u = unchanged - = unimplemented, read as '0'<math>q = see tables in Table 5-1 for possible values.

- Note 1: These values are valid for PIC16C57/CR57/CR58/CR58. For the PIC16C54/CR54/C55/C56/CR56, the value on RESET is 111x xxxx and for MCLR and WDT Reset, the value is 111u uuuu.

- **2:** General purpose register file on PIC16C54/CR54/C56/CR56/C58/CR58.

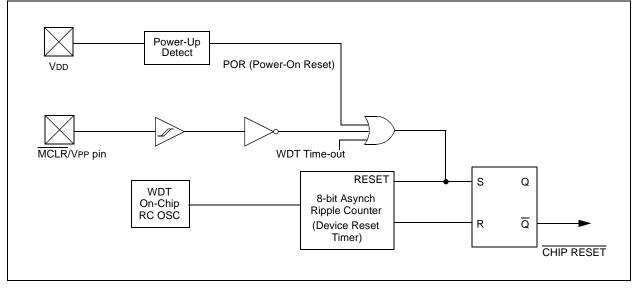

## FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

## 5.2 Device Reset Timer (DRT)

The Device Reset Timer (DRT) provides an 18 ms nominal time-out on RESET regardless of Oscillator mode used. The DRT operates on an internal RC oscillator. The processor is kept in RESET as long as the DRT is active. The DRT delay allows VDD to rise above VDD min., and for the oscillator to stabilize.

Oscillator circuits based on crystals or ceramic resonators require a certain time after power-up to establish a stable oscillation. The on-chip DRT keeps the device in a RESET condition for approximately 18 ms after the voltage on the MCLR/VPP pin has reached a logic high (VIH) level. Thus, external RC networks connected to the MCLR input are not required in most cases, allowing for savings in cost-sensitive and/or space restricted applications.

The Device Reset time delay will vary from chip to chip due to VDD, temperature, and process variation. See AC parameters for details.

The DRT will also be triggered upon a Watchdog Timer time-out. This is particularly important for applications using the WDT to wake the PIC16C5X from SLEEP mode automatically.

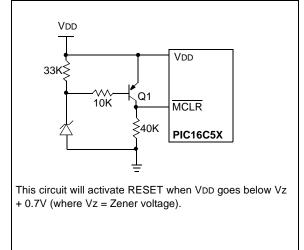

## 5.3 Reset on Brown-Out

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be RESET in the event of a brown-out.

To RESET PIC16C5X devices when a brown-out occurs, external brown-out protection circuits may be built, as shown in Figure 5-6, Figure 5-7 and Figure 5-8.

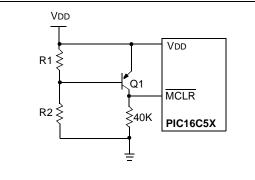

## FIGURE 5-7:

#### EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, although less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

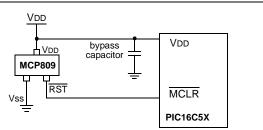

## FIGURE 5-8:

#### EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both "active high and active low" RESET pins. There are 7 different trip point selections to accommodate 5V and 3V systems.

## 6.3 STATUS Register

This register contains the arithmetic status of the ALU, the RESET status and the page preselect bits for program memories larger than 512 words.

The STATUS Register can be the destination for any instruction, as with any other register. If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not

writable. Therefore, the result of an instruction with the STATUS Register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS Register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS Register because these instructions do not affect the Z, DC or C bits from the STATUS Register. For other instructions which do affect STATUS Bits, see Section 10.0, Instruction Set Summary.

## REGISTER 6-1: STATUS REGISTER (ADDRESS: 03h)

|          | R/W-0                                                                                                                                 | R/W-0                              | R/W-0        | R-1          | R-1                        | R/W-x         | R/W-x          | R/W-x          |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------|--------------|----------------------------|---------------|----------------|----------------|--|

|          | PA2                                                                                                                                   | PA1                                | PA0          | TO           | PD                         | Z             | DC             | С              |  |

|          | bit 7                                                                                                                                 |                                    |              |              |                            |               |                | bit 0          |  |

| bit 7:   | PA2: This bit                                                                                                                         | unused at th                       | is time.     |              |                            |               |                |                |  |

|          |                                                                                                                                       | A2 bit as a ge<br>with future pr   |              | e read/write | bit is not recor           | mmended, sir  | nce this may a | affect upward  |  |

| bit 6-5: |                                                                                                                                       |                                    |              | -            | CR56)(PIC16                |               |                | 58)            |  |

|          |                                                                                                                                       |                                    |              |              | 16C57/CR57,<br>16C57/CR57, |               |                |                |  |

|          |                                                                                                                                       | (400h - 5FFh                       |              |              |                            | FIC 10C30/C   | N00            |                |  |

|          | 11 = Page 3                                                                                                                           | (600h - 7FFh                       | •            |              |                            |               |                |                |  |

|          | Each page is                                                                                                                          |                                    | deperal pur  | ose read/wr  | ite bits in devi           | ices which do | not use them   | for program    |  |

|          |                                                                                                                                       |                                    |              |              | affect upward              |               |                |                |  |

| bit 4:   | TO: Time-ou                                                                                                                           |                                    |              | ,            | •                          |               |                |                |  |

|          |                                                                                                                                       | ver-up, CLRWI<br>ime-out occur     |              | , or sleep i | nstruction                 |               |                |                |  |

| bit 3:   | PD: Power-d                                                                                                                           | lown bit                           |              |              |                            |               |                |                |  |

|          | •                                                                                                                                     | ver-up or by tl<br>ution of the SI |              |              |                            |               |                |                |  |

| bit 2:   | Z: Zero bit                                                                                                                           |                                    |              |              |                            |               |                |                |  |

|          |                                                                                                                                       | lt of an arithm<br>It of an arithm |              |              |                            |               |                |                |  |

| bit 1:   | DC: Digit car                                                                                                                         | ry/borrow bit                      | (for ADDWF a | nd SUBWF in  | structions)                |               |                |                |  |

|          | ADDWF                                                                                                                                 |                                    |              |              |                            |               |                |                |  |

|          |                                                                                                                                       | rom the 4th lo                     |              |              |                            |               |                |                |  |

|          | <ul> <li>a Carry from the 4th low order bit of the result did not occur</li> <li>SUBWF</li> </ul>                                     |                                    |              |              |                            |               |                |                |  |

|          | 1 = A borrow from the 4th low order bit of the result did not occur<br>0 = A borrow from the 4th low order bit of the result occurred |                                    |              |              |                            |               |                |                |  |

|          |                                                                                                                                       |                                    |              |              |                            |               |                |                |  |

| bit 0:   | •                                                                                                                                     | row bit (for AI                    |              |              | F instructions             |               | _              |                |  |

|          | <b>ADDWF</b><br>1 = A carry o                                                                                                         | ocurred                            |              | orrow did n  | ot occur                   | RRF or RLI    |                | , respectively |  |

|          | $\pm = \pi \operatorname{carry} 0$                                                                                                    | locurrou                           | / · ·        |              |                            |               |                |                |  |

| Legena:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared        | x = bit is unknown |

## 6.5.1 PAGING CONSIDERATIONS – PIC16C56/CR56, PIC16C57/CR57 AND PIC16C58/CR58

If the Program Counter is pointing to the last address of a selected memory page, when it increments it will cause the program to continue in the next higher page. However, the page preselect bits in the STATUS Register will not be updated. Therefore, the next GOTO, CALL or modify PCL instruction will send the program to the page specified by the page preselect bits (PA0 or PA<1:0>).

For example, a NOP at location 1FFh (page 0) increments the PC to 200h (page 1). A GOTO xxx at 200h will return the program to address xxh on page 0 (assuming that PA<1:0> are clear).

To prevent this, the page preselect bits must be updated under program control.

## 6.5.2 EFFECTS OF RESET

The Program Counter is set upon a RESET, which means that the PC addresses the last location in the last page (i.e., the RESET vector).

The STATUS Register page preselect bits are cleared upon a RESET, which means that page 0 is pre-selected.

Therefore, upon a RESET, a GOTO instruction at the RESET vector location will automatically cause the program to jump to page 0.

## 6.6 Stack

PIC16C5X devices have a 10-bit or 11-bit wide, two-level hardware push/pop stack.

A CALL instruction will push the current value of stack 1 into stack 2 and then push the current program counter value, incremented by one, into stack level 1. If more than two sequential CALL's are executed, only the most recent two return addresses are stored.

A RETLW instruction will pop the contents of stack level 1 into the program counter and then copy stack level 2 contents into level 1. If more than two sequential RETLW's are executed, the stack will be filled with the address previously stored in level 2. Note that the W Register will be loaded with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

For the RETLW instruction, the PC is loaded with the Top of Stack (TOS) contents. All of the devices covered in this data sheet have a two-level stack. The stack has the same bit width as the device PC, therefore, paging is not an issue when returning from a subroutine.

| CALL                                                                                                                                           | Subroutine Call                                                                                                                                                                                                                                                     |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                                                                                                                        | [ <i>label</i> ] CALL k                                                                                                                                                                                                                                             |  |  |  |

| Operands:                                                                                                                                      | $0 \leq k \leq 255$                                                                                                                                                                                                                                                 |  |  |  |

| Operation:                                                                                                                                     | $\begin{array}{l} (PC) + 1 \rightarrow TOS; \\ k \rightarrow PC < 7:0 >; \\ (STATUS < 6:5 >) \rightarrow PC < 10:9 >; \\ 0 \rightarrow PC < 8 > \end{array}$                                                                                                        |  |  |  |

| Status Affected:                                                                                                                               | None                                                                                                                                                                                                                                                                |  |  |  |

| Encoding:                                                                                                                                      | 1001 kkkk kkkk                                                                                                                                                                                                                                                      |  |  |  |

| Description:                                                                                                                                   | Subroutine call. First, return<br>address (PC+1) is pushed onto the<br>stack. The eight bit immediate<br>address is loaded into PC bits<br><7:0>. The upper bits PC<10:9><br>are loaded from STATUS<6:5>,<br>PC<8> is cleared. CALL is a two-<br>cycle instruction. |  |  |  |

| Words:                                                                                                                                         | 1                                                                                                                                                                                                                                                                   |  |  |  |

| Cycles:                                                                                                                                        | 2                                                                                                                                                                                                                                                                   |  |  |  |

| Example:                                                                                                                                       | HERE CALL THERE                                                                                                                                                                                                                                                     |  |  |  |

| Example: HERE CALL THERE<br>Before Instruction<br>PC = address (HERE)<br>After Instruction<br>PC = address (THERE)<br>TOS = address (HERE + 1) |                                                                                                                                                                                                                                                                     |  |  |  |

| CLRF | Clear f |

|------|---------|

|      | Oloui I |

| Syntax:                                   | [label] CLRF f                                                         |           |      |  |  |  |

|-------------------------------------------|------------------------------------------------------------------------|-----------|------|--|--|--|

| Operands:                                 | $0 \le f \le 3^{-1}$                                                   | 1         |      |  |  |  |

| Operation:                                | $\begin{array}{l} 00h \rightarrow (f); \\ 1 \rightarrow Z \end{array}$ |           |      |  |  |  |

| Status Affected:                          | Z                                                                      |           |      |  |  |  |

| Encoding:                                 | 0000                                                                   | 011f      | ffff |  |  |  |

| Description:                              | The contents of register 'f' are cleared and the Z bit is set.         |           |      |  |  |  |

| Words:                                    | 1                                                                      |           |      |  |  |  |

| Cycles:                                   | 1                                                                      |           |      |  |  |  |

| Example:                                  | CLRF                                                                   | FLAG_RE   | IG   |  |  |  |

| Before Instru<br>FLAG_R<br>After Instruct | EG =                                                                   | 0x5A      |      |  |  |  |

| FLAG_R<br>Z                               | EG =<br>=                                                              | 0x00<br>1 |      |  |  |  |

| CLRW                                                                                                 | Clear W                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                              | [label] CLRW                                                                                                                                                                                                                                                                                                                                                                                            |

| Operands:                                                                                            | None                                                                                                                                                                                                                                                                                                                                                                                                    |

| Operation:                                                                                           | $\begin{array}{l} 00h \rightarrow (W); \\ 1 \rightarrow Z \end{array}$                                                                                                                                                                                                                                                                                                                                  |

| Status Affected:                                                                                     | Z                                                                                                                                                                                                                                                                                                                                                                                                       |

| Encoding:                                                                                            | 0000 0100 0000                                                                                                                                                                                                                                                                                                                                                                                          |

| Description:                                                                                         | The W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                         |

| Words:                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                       |

| Cycles:                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                       |

| Example:                                                                                             | CLRW                                                                                                                                                                                                                                                                                                                                                                                                    |

| W =<br>After Instruct                                                                                | ion                                                                                                                                                                                                                                                                                                                                                                                                     |

| W =<br>Z =                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                       |

| Z =                                                                                                  | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                    |

| Z =<br>CLRWDT<br>Syntax:                                                                             | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                    |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:                                                                | Clear Watchdog Timer<br>[ label ] CLRWDT<br>None                                                                                                                                                                                                                                                                                                                                                        |

| Z =<br>CLRWDT<br>Syntax:                                                                             | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                    |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:                                                                | Clear Watchdog Timer<br>[ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow TO;$                                                                                                                                                                                                                                                |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:<br>Operation:                                                  | Clear Watchdog Timer<br>[ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$<br>$1 \rightarrow \overline{PD}$                                                                                                                                                                                                    |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:                              | Clear Watchdog Timer<br>[ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$<br>$1 \rightarrow \overline{PD}$<br>$\overline{TO}, \overline{PD}$                                                                                                                                                                  |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                 | Clear Watchdog Timer[ label ] CLRWDTNone $00h \rightarrow WDT;$ $0 \rightarrow WDT$ prescaler (if assigned); $1 \rightarrow \overline{TO};$ $1 \rightarrow \overline{PD}$ $\overline{TO}, \overline{PD}$ $0000  0000  0100$ The CLRWDT instruction resets theWDT. It also resets the prescaler, ifthe prescaler is assigned to theWDT and not Timer0. Status bits                                       |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description: | Clear Watchdog Timer[ label ] CLRWDTNone $00h \rightarrow WDT$ ; $0 \rightarrow WDT$ prescaler (if assigned); $1 \rightarrow \overline{TO}$ ; $1 \rightarrow \overline{PD}$ $\overline{TO}$ , $\overline{PD}$ $0000$ $0000$ $0100$ The CLRWDT instruction resets theWDT. It also resets the prescaler, ifthe prescaler is assigned to theWDT and not Timer0. Status bitsTO and $\overline{PD}$ are set. |

| After Instruction |   |      |

|-------------------|---|------|

| WDT counter       | = | 0x00 |

| WDT prescaler     | = | 0    |

| TO                | = | 1    |

| PD                | = | 1    |

## 13.1 DC Characteristics: PIC16CR54A-04, 10, 20, PIC16LCR54A-04 (Commercial) PIC16CR54A-04I, 10I, 20I, PIC16LCR54A-04I (Industrial)

| PIC16LCR54A-04           PIC16LCR54A-04I           (Commercial, Industrial)           PIC16CR54A-04, 10, 20           PIC16CR54A-04I, 10I, 20I           (Commercial, Industrial) |     |                                   | $ \begin{array}{l} \textbf{Standard Operating Conditions (unless otherwise specified)} \\ \text{Operating Temperature} & 0^{\circ}\text{C} \leq \text{TA} \leq +70^{\circ}\text{C} \text{ for commercial} \\ -40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C} \text{ for industrial} \\ \end{array} \\ \textbf{Standard Operating Conditions (unless otherwise specified)} \\ \text{Operating Temperature} & 0^{\circ}\text{C} \leq \text{TA} \leq +70^{\circ}\text{C} \text{ for commercial} \\ -40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C} \text{ for industrial} \\ \end{array} $ |                                 |                               |                      |                                                                                                                                        |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                   |     |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                 |                               |                      |                                                                                                                                        |  |

|                                                                                                                                                                                   | IPD | Power-down Current <sup>(2)</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                 |                               |                      |                                                                                                                                        |  |

| D006                                                                                                                                                                              |     | PIC16LCR54A-Commercial            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.0<br>2.0<br>3.0<br>5.0        | 6.0<br>8.0*<br>15<br>25       | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 2.5V, WDT disabled<br>VDD = 4.0V, WDT disabled<br>VDD = 6.0V, WDT disabled<br>VDD = 6.0V, WDT enabled                            |  |

| D006A                                                                                                                                                                             |     | PIC16CR54A-Commercial             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.0<br>2.0<br>3.0<br>5.0        | 6.0<br>8.0*<br>15<br>25       | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 2.5V, WDT disabled<br>VDD = 4.0V, WDT disabled<br>VDD = 6.0V, WDT disabled<br>VDD = 6.0V, WDT enabled                            |  |

| D007                                                                                                                                                                              |     | PIC16LCR54A-Industrial            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.0<br>2.0<br>3.0<br>3.0<br>5.0 | 8.0<br>10*<br>20*<br>18<br>45 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 2.5V, WDT disabled<br>VDD = 4.0V, WDT disabled<br>VDD = 4.0V, WDT enabled<br>VDD = 6.0V, WDT disabled<br>VDD = 6.0V, WDT enabled |  |

| D007A                                                                                                                                                                             |     | PIC16CR54A-Industrial             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.0<br>2.0<br>3.0<br>3.0<br>5.0 | 8.0<br>10*<br>20*<br>18<br>45 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 2.5V, WDT disabled<br>VDD = 4.0V, WDT disabled<br>VDD = 4.0V, WDT enabled<br>VDD = 6.0V, WDT disabled<br>VDD = 6.0V, WDT enabled |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- **Note 1:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

## 13.2 DC Characteristics: PIC16CR54A-04E, 10E, 20E (Extended)

|                                    |      | Standard Operating Conditions (unless otherwise specifieOperating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |             |                   |                 |                |                                                                                      |

|------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|-----------------|----------------|--------------------------------------------------------------------------------------|

| Param<br>No. Symbol Characteristic |      |                                                                                                                                    |             | Min Typ†          | Мах             | Units          | Conditions                                                                           |

| D001                               | Vdd  | Supply Voltage<br>RC, XT and LP modes<br>HS mode                                                                                   | 3.25<br>4.5 |                   | 6.0<br>5.5      | V<br>V         |                                                                                      |

| D002                               | Vdr  | RAM Data Retention Voltage <sup>(1)</sup>                                                                                          | —           | 1.5*              | —               | V              | Device in SLEEP mode                                                                 |

| D003                               | VPOR | VDD Start Voltage to ensure<br>Power-on Reset                                                                                      | —           | Vss               | —               | V              | See Section 5.1 for details on<br>Power-on Reset                                     |

| D004                               | Svdd | VDD Rise Rate to ensure Power-<br>on Reset                                                                                         | 0.05*       | _                 |                 | V/ms           | See Section 5.1 for details on<br>Power-on Reset                                     |

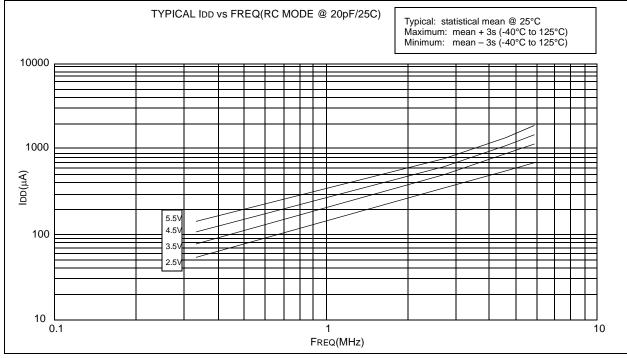

| D010                               | IDD  | Supply Current <sup>(2)</sup><br>RC <sup>(3)</sup> and XT modes<br>HS mode<br>HS mode                                              |             | 1.8<br>4.8<br>9.0 | 3.3<br>10<br>20 | mA<br>mA<br>mA | Fosc = 4.0 MHz, Vdd = 5.5V<br>Fosc = 10 MHz, Vdd = 5.5V<br>Fosc = 16 MHz, Vdd = 5.5V |

| D020                               | IPD  | Power-down Current <sup>(2)</sup>                                                                                                  |             | 5.0<br>0.8        | 22<br>18        | μΑ<br>μΑ       | VDD = 3.25V, WDT enabled<br>VDD = 3.25V, WDT disabled                                |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

## 15.0 ELECTRICAL CHARACTERISTICS - PIC16C54A

| Absolute Maximum Ratings <sup>(†)</sup>                                                                  |                                      |

|----------------------------------------------------------------------------------------------------------|--------------------------------------|

| Ambient temperature under bias                                                                           | –55°C to +125°C                      |

| Storage temperature                                                                                      | –65°C to +150°C                      |

| Voltage on VDD with respect to Vss                                                                       | 0 to +7.5V                           |

| Voltage on MCLR with respect to Vss                                                                      | 0 to +14V                            |

| Voltage on all other pins with respect to Vss                                                            | –0.6V to (VDD + 0.6V)                |

| Total power dissipation <sup>(1)</sup>                                                                   | 800 mW                               |

| Max. current out of Vss pin                                                                              | 150 mA                               |

| Max. current into Vod pin                                                                                | 100 mA                               |

| Max. current into an input pin (T0CKI only)                                                              | ±500 μA                              |

| Input clamp current, Iik (VI < 0 or VI > VDD)                                                            | ±20 mA                               |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                           |                                      |

| Max. output current sunk by any I/O pin                                                                  | 25 mA                                |

| Max. output current sourced by any I/O pin                                                               | 20 mA                                |

| Max. output current sourced by a single I/O port (PORTA or B)                                            | 50 mA                                |

| Max. output current sunk by a single I/O port (PORTA or B)                                               | 50 mA                                |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VD | D-VOH) X IOH} + $\Sigma$ (VOL X IOL) |

† NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## 15.5 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| oS                                         |                                                                                                                                                                                   |  |  |  |  |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                            |                                                                                                                                                                                   |  |  |  |  |

|                                            |                                                                                                                                                                                   |  |  |  |  |

| Frequency                                  | T Time                                                                                                                                                                            |  |  |  |  |

| Lowercase letters (pp) and their meanings: |                                                                                                                                                                                   |  |  |  |  |

|                                            |                                                                                                                                                                                   |  |  |  |  |

| to                                         | mc MCLR                                                                                                                                                                           |  |  |  |  |

| CLKOUT                                     | osc oscillator                                                                                                                                                                    |  |  |  |  |

| cycle time                                 | os OSC1                                                                                                                                                                           |  |  |  |  |

| device reset timer                         | t0 T0CKI                                                                                                                                                                          |  |  |  |  |

| I/O port                                   | wdt watchdog timer                                                                                                                                                                |  |  |  |  |

| Uppercase letters and their meanings:      |                                                                                                                                                                                   |  |  |  |  |

|                                            |                                                                                                                                                                                   |  |  |  |  |

| Fall                                       | P Period                                                                                                                                                                          |  |  |  |  |

| High                                       | R Rise                                                                                                                                                                            |  |  |  |  |

| Invalid (Hi-impedance)                     | V Valid                                                                                                                                                                           |  |  |  |  |

| Low                                        | Z Hi-impedance                                                                                                                                                                    |  |  |  |  |

|                                            | case letters (pp) and their meanings:<br>o<br>CLKOUT<br>cycle time<br>device reset timer<br>/O port<br>case letters and their meanings:<br>Fall<br>High<br>Invalid (Hi-impedance) |  |  |  |  |

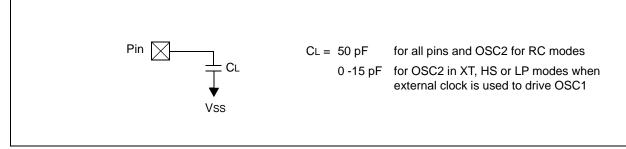

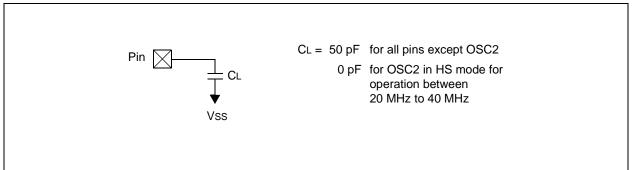

## FIGURE 15-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS - PIC16C54A

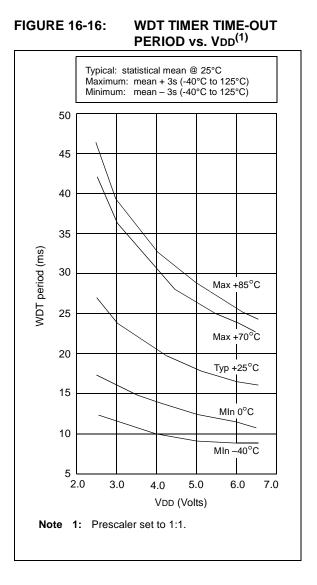

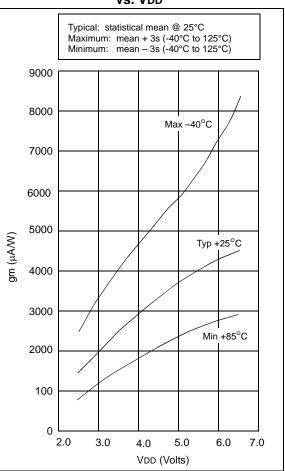

## FIGURE 16-17: TRANSCONDUCTANCE (gm) OF HS OSCILLATOR vs. VDD

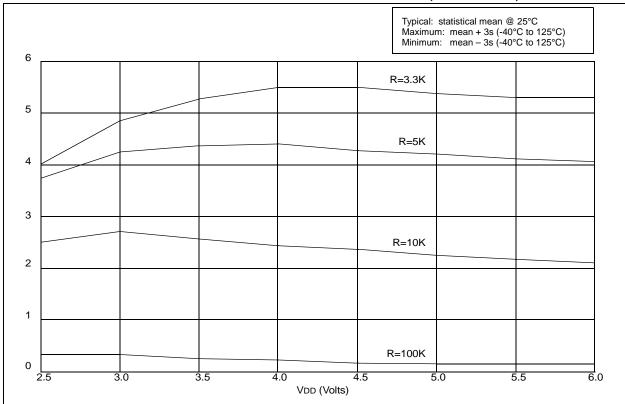

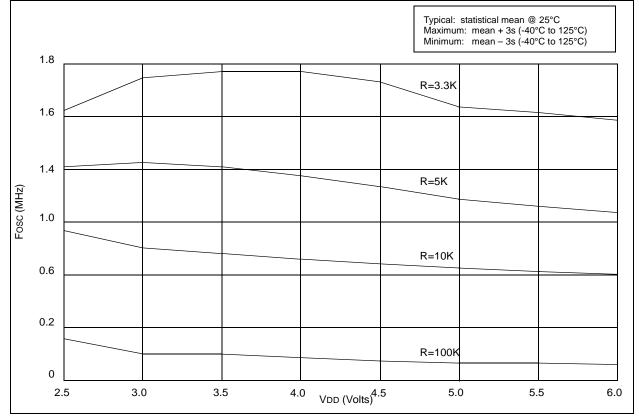

## FIGURE 18-2: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD, CEXT = 20 PF, 25°C

© 1997-2013 Microchip Technology Inc.

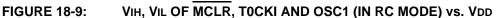

# PIC16C5X

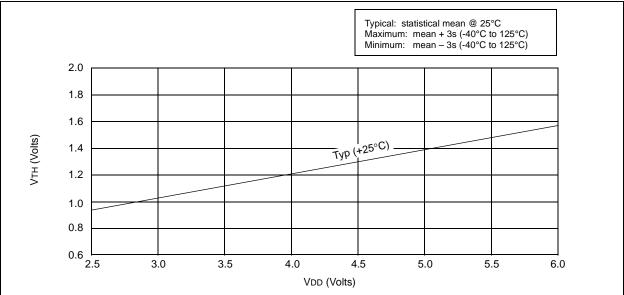

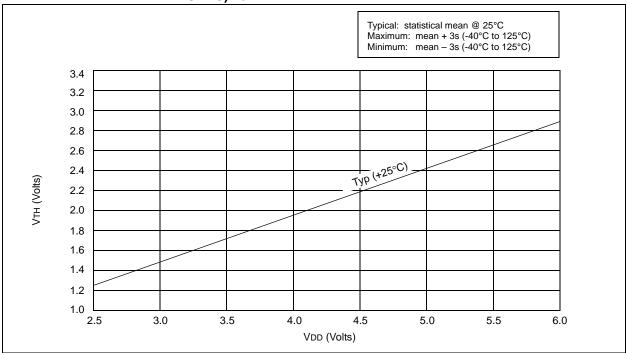

## FIGURE 18-10: VTH (INPUT THRESHOLD TRIP POINT VOLTAGE) OF OSC1 INPUT (IN XT, HS AND LP MODES) vs. VDD

## 19.0 ELECTRICAL CHARACTERISTICS - PIC16LC54C 40MHz

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                 | –55°C to +125°C               |

|----------------------------------------------------------------------------------------------------------------|-------------------------------|

| Storage temperature                                                                                            | –65°C to +150°C               |

| Voltage on VDD with respect to VSS                                                                             | 0 to +7.5V                    |

| Voltage on MCLR with respect to Vss                                                                            | 0 to +14V                     |

| Voltage on all other pins with respect to Vss                                                                  | –0.6V to (VDD + 0.6V)         |

| Total power dissipation <sup>(1)</sup>                                                                         | 800 mW                        |

| Max. current out of Vss pin                                                                                    | 150 mA                        |

| Max. current into Vod pin                                                                                      |                               |

| Max. current into an input pin (T0CKI only)                                                                    | ±500 μA                       |

| Input clamp current, liк (Vi <0 or Vi > VDD)                                                                   | ±20 mA                        |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                                 | ±20 mA                        |

| Max. output current sunk by any I/O pin                                                                        | 25 mA                         |

| Max. output current sourced by any I/O pin                                                                     | 20 mA                         |

| Max. output current sourced by a single I/O (Port A, B or C)                                                   | 50 mA                         |

| Max. output current sunk by a single I/O (Port A, B or C)                                                      | 50 mA                         |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) | x IOH} + $\Sigma$ (Vol x Iol) |

**†** NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## **19.3 Timing Parameter Symbology and Load Conditions**

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. Tp | 2. TppS                                    |                    |  |  |  |  |  |

|-------|--------------------------------------------|--------------------|--|--|--|--|--|

| Т     |                                            |                    |  |  |  |  |  |

| F     | Frequency                                  | T Time             |  |  |  |  |  |

| Lowe  | Lowercase letters (pp) and their meanings: |                    |  |  |  |  |  |

| рр    | pp                                         |                    |  |  |  |  |  |

| 2     | to                                         | mc MCLR            |  |  |  |  |  |

| ck    | CLKOUT                                     | osc oscillator     |  |  |  |  |  |

| су    | cycle time                                 | os OSC1            |  |  |  |  |  |

| drt   | device reset timer                         | t0 T0CKI           |  |  |  |  |  |

| io    | I/O port                                   | wdt watchdog timer |  |  |  |  |  |

| Uppe  | Uppercase letters and their meanings:      |                    |  |  |  |  |  |

| S     |                                            |                    |  |  |  |  |  |

| F     | Fall                                       | P Period           |  |  |  |  |  |

| н     | High                                       | R Rise             |  |  |  |  |  |

| Ι     | Invalid (Hi-impedance)                     | V Valid            |  |  |  |  |  |

| L     | Low                                        | Z Hi-impedance     |  |  |  |  |  |

## FIGURE 19-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS -PIC16C54C/C55A/C56A/C57C/C58B-40

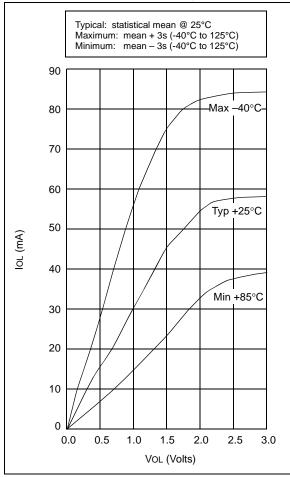

#### FIGURE 20-9: IOL vs. VOL, VDD = 5 V

## Package Marking Information (Cont'd)

18-Lead CERDIP Windowed

|  | XXXXXXXX<br>XXXXXXXX<br>YYWWNNN |

|--|---------------------------------|

|--|---------------------------------|

## 28-Lead CERDIP Windowed

Example

## Example

| Lege | end: XX?<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |  |  |  |

|------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Note | be carr                                     | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information.                                                                                                                                                                  |  |  |  |

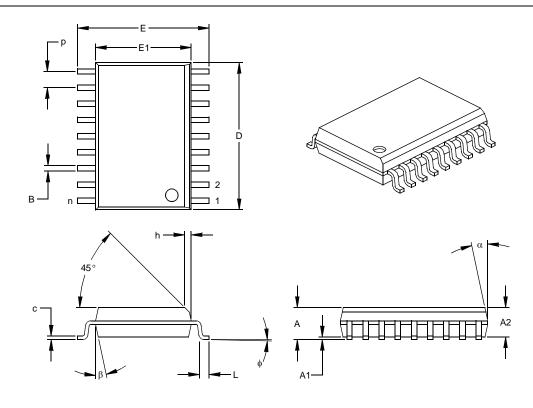

## 18-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                          | Units     | INCHES* |      | MILLIMETERS |       |       |       |

|--------------------------|-----------|---------|------|-------------|-------|-------|-------|

| Dimensi                  | on Limits | MIN     | NOM  | MAX         | MIN   | NOM   | MAX   |

| Number of Pins           | n         |         | 18   |             |       | 18    |       |

| Pitch                    | р         |         | .050 |             |       | 1.27  |       |

| Overall Height           | А         | .093    | .099 | .104        | 2.36  | 2.50  | 2.64  |

| Molded Package Thickness | A2        | .088    | .091 | .094        | 2.24  | 2.31  | 2.39  |

| Standoff §               | A1        | .004    | .008 | .012        | 0.10  | 0.20  | 0.30  |

| Overall Width            | E         | .394    | .407 | .420        | 10.01 | 10.34 | 10.67 |

| Molded Package Width     | E1        | .291    | .295 | .299        | 7.39  | 7.49  | 7.59  |

| Overall Length           | D         | .446    | .454 | .462        | 11.33 | 11.53 | 11.73 |

| Chamfer Distance         | h         | .010    | .020 | .029        | 0.25  | 0.50  | 0.74  |

| Foot Length              | L         | .016    | .033 | .050        | 0.41  | 0.84  | 1.27  |

| Foot Angle               | φ         | 0       | 4    | 8           | 0     | 4     | 8     |

| Lead Thickness           | С         | .009    | .011 | .012        | 0.23  | 0.27  | 0.30  |

| Lead Width               | В         | .014    | .017 | .020        | 0.36  | 0.42  | 0.51  |

| Mold Draft Angle Top     | α         | 0       | 12   | 15          | 0     | 12    | 15    |

| Mold Draft Angle Bottom  | β         | 0       | 12   | 15          | 0     | 12    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013 Drawing No. C04-051