#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 20                                                                        |

| Program Memory Size        | 768B (512 x 12)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 24 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

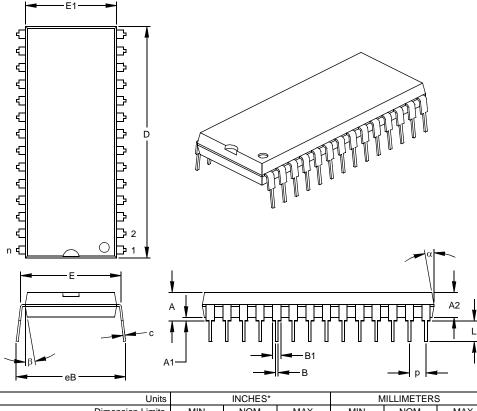

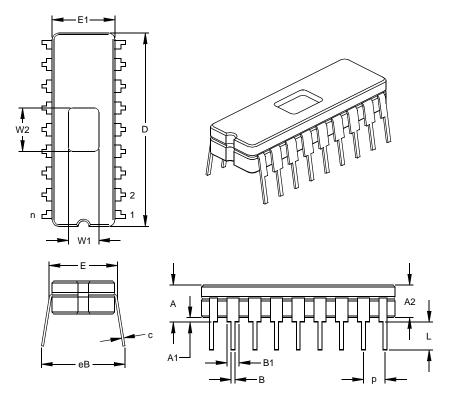

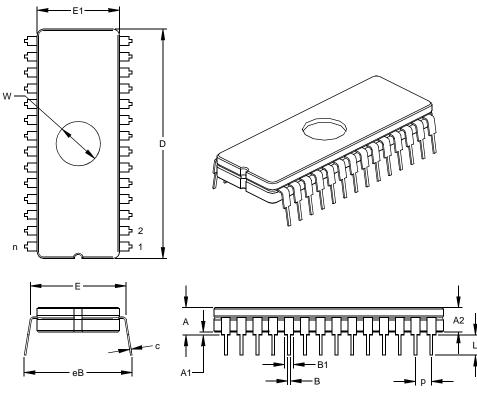

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c55-hsi-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.3 External Crystal Oscillator Circuit

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A welldesigned crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

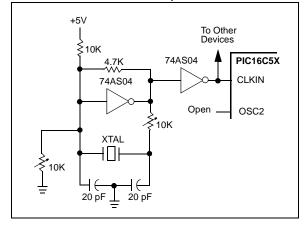

Figure 4-3 shows an implementation example of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

FIGURE 4-3: EXAMPLE OF EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT (USING XT, HS OR LP OSCILLATOR MODE)

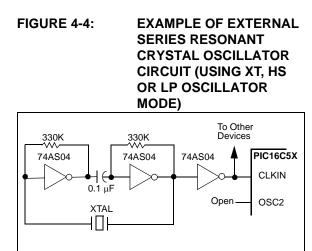

Figure 4-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

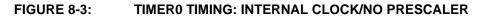

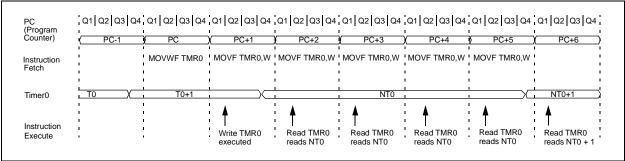

## FIGURE 8-4: TIMER0 TIMING: INTERNAL CLOCK/PRESCALER 1:2

#### TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6                                                      | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | <u>Value</u> on<br>MCLR and<br>WDT Reset |

|---------|--------|----------|------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------------------------------|------------------------------------------|

| 01h     | TMR0   | Timer0 - | Timer0 - 8-bit real-time clock/counter xxxx xxxx uuuu uuuu |       |       |       |       |       |       |                               |                                          |

| N/A     | OPTION | _        |                                                            | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 11 1111                       | 11 1111                                  |

Legend: x = unknown, u = unchanged, - = unimplemented. Shaded cells not used by Timer0.

| ADDWF                                                       | Add W                                                          | and f                                      |                                                      |                    |

|-------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------|------------------------------------------------------|--------------------|

| Syntax:                                                     | [ label ] A                                                    | DDWF                                       | f,d                                                  |                    |

| Operands:                                                   | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$ |                                            |                                                      |                    |

| Operation:                                                  | (W) + (f)                                                      | $\rightarrow$ (dest)                       |                                                      |                    |

| Status Affected:                                            | C, DC, Z                                                       |                                            |                                                      |                    |

| Encoding:                                                   | 0001                                                           | 11df                                       | ffff                                                 |                    |

| Description:                                                | and regis                                                      | ster 'f'. If 'd<br>in the W<br>sult is sto | of the W r<br>d' is 0 the<br>register. I<br>red back | result<br>f 'd' is |

| Words:                                                      | 1                                                              |                                            |                                                      |                    |

| Cycles:                                                     | 1                                                              |                                            |                                                      |                    |

| Example:                                                    | ADDWF                                                          | TEMP_RE                                    | CG, 0                                                |                    |

| Before Instr<br>W<br>TEMP_I<br>After Instruc<br>W<br>TEMP_F | =<br>REG =<br>ction<br>=                                       | 0x17<br>0xC2<br>0xD9<br>0xC2               |                                                      |                    |

| ANDWF                                                      | AND W with f                                                                                                                                                                            |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                    | [label] ANDWF f,d                                                                                                                                                                       |

| Operands:                                                  | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                          |

| Operation:                                                 | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                      |

| Status Affected:                                           | Z                                                                                                                                                                                       |

| Encoding:                                                  | 0001 01df ffff                                                                                                                                                                          |

| Description:                                               | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is 0<br>the result is stored in the W regis-<br>ter. If 'd' is '1' the result is stored<br>back in register 'f'. |

| Words:                                                     | 1                                                                                                                                                                                       |

| Cycles:                                                    | 1                                                                                                                                                                                       |

| Example:                                                   | ANDWF TEMP_REG, 1                                                                                                                                                                       |

| Before Instru<br>W<br>TEMP_<br>After Instruc<br>W<br>TEMP_ | = 0x17<br>REG = 0xC2<br>tion<br>= 0x17                                                                                                                                                  |

| ANDLW                                        | AND literal with W                                                                                                           |  |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                      | [ <i>label</i> ] ANDLW k                                                                                                     |  |  |  |

| Operands:                                    | $0 \leq k \leq 255$                                                                                                          |  |  |  |

| Operation:                                   | (W).AND. (k) $\rightarrow$ (W)                                                                                               |  |  |  |

| Status Affected:                             | Z                                                                                                                            |  |  |  |

| Encoding:                                    | 1110 kkkk kkkk                                                                                                               |  |  |  |

| Description:                                 | The contents of the W register are<br>AND'ed with the eight-bit literal 'k'.<br>The result is placed in the W regis-<br>ter. |  |  |  |

| Words:                                       | 1                                                                                                                            |  |  |  |

| Cycles:                                      | 1                                                                                                                            |  |  |  |

| Example:                                     | ANDLW H'5F'                                                                                                                  |  |  |  |

| Before Instru<br>W =<br>After Instruc<br>W = | 0xA3                                                                                                                         |  |  |  |

| BCF                                                        | Bit Clear f                                                        |              |             |  |  |

|------------------------------------------------------------|--------------------------------------------------------------------|--------------|-------------|--|--|

| Syntax:                                                    | [ <i>label</i> ] BCF f,b                                           |              |             |  |  |

| Operands:                                                  | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |              |             |  |  |

| Operation:                                                 | $0 \rightarrow (f < b$                                             | >)           |             |  |  |

| Status Affected:                                           | None                                                               |              |             |  |  |

| Encoding:                                                  | 0100                                                               | bbbf         | ffff        |  |  |

| Description:                                               | Bit 'b' in                                                         | register 'f' | is cleared. |  |  |

| Words:                                                     | 1                                                                  |              |             |  |  |

| Cycles:                                                    | 1                                                                  |              |             |  |  |

| Example:                                                   | BCF                                                                | FLAG_RE      | IG, 7       |  |  |

| Before Instruction<br>FLAG_REG = 0xC7<br>After Instruction |                                                                    |              |             |  |  |

| FLAG_F                                                     | REG =                                                              | 0x47         |             |  |  |

| CALL             | Subroutine Call                                                                                                                                                                                                                                                     |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                                             |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                                                                                                 |  |  |

| Operation:       | $(PC) + 1 \rightarrow TOS;$<br>$k \rightarrow PC < 7:0>;$<br>$(STATUS < 6:5>) \rightarrow PC < 10:9>;$<br>$0 \rightarrow PC < 8>$                                                                                                                                   |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                |  |  |

| Encoding:        | 1001 kkkk kkkk                                                                                                                                                                                                                                                      |  |  |

| Description:     | Subroutine call. First, return<br>address (PC+1) is pushed onto the<br>stack. The eight bit immediate<br>address is loaded into PC bits<br><7:0>. The upper bits PC<10:9><br>are loaded from STATUS<6:5>,<br>PC<8> is cleared. CALL is a two-<br>cycle instruction. |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                   |  |  |

| Cycles:          | 2                                                                                                                                                                                                                                                                   |  |  |

| Example:         | HERE CALL THERE                                                                                                                                                                                                                                                     |  |  |

| After Instruct   | address (HERE)<br>ion<br>address (THERE)                                                                                                                                                                                                                            |  |  |

| CLRF | Clear f |

|------|---------|

|      | Oloui I |

| Syntax:                                   | [ label ]                                                              | CLRF f                  |                               |

|-------------------------------------------|------------------------------------------------------------------------|-------------------------|-------------------------------|

| Operands:                                 | $0 \leq f \leq 31$                                                     |                         |                               |

| Operation:                                | $\begin{array}{l} 00h \rightarrow (f); \\ 1 \rightarrow Z \end{array}$ |                         |                               |

| Status Affected:                          | Z                                                                      |                         |                               |

| Encoding:                                 | 0000                                                                   | 011f                    | ffff                          |

| Description:                              |                                                                        | ents of re<br>and the Z | gister 'f' are<br>bit is set. |

| Words:                                    | 1                                                                      |                         |                               |

| Cycles:                                   | 1                                                                      |                         |                               |

| Example:                                  | CLRF                                                                   | FLAG_RE                 | IG                            |

| Before Instru<br>FLAG_R<br>After Instruct | EG =                                                                   | 0x5A                    |                               |

| FLAG_R<br>Z                               | EG =<br>=                                                              | 0x00<br>1               |                               |

| CLRW                                                                                                 | Clear W                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                              | [label] CLRW                                                                                                                                                                                                                                                                                                                                                                                            |

| Operands:                                                                                            | None                                                                                                                                                                                                                                                                                                                                                                                                    |

| Operation:                                                                                           | $\begin{array}{l} 00h \rightarrow (W); \\ 1 \rightarrow Z \end{array}$                                                                                                                                                                                                                                                                                                                                  |

| Status Affected:                                                                                     | Z                                                                                                                                                                                                                                                                                                                                                                                                       |

| Encoding:                                                                                            | 0000 0100 0000                                                                                                                                                                                                                                                                                                                                                                                          |

| Description:                                                                                         | The W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                         |

| Words:                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                       |

| Cycles:                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                       |

| Example:                                                                                             | CLRW                                                                                                                                                                                                                                                                                                                                                                                                    |

| W =<br>After Instruct                                                                                | ion                                                                                                                                                                                                                                                                                                                                                                                                     |

| W =<br>Z =                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                       |

| Z =                                                                                                  | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                    |

| Z =<br>CLRWDT<br>Syntax:                                                                             | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                    |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:                                                                | Clear Watchdog Timer<br>[ label ] CLRWDT<br>None                                                                                                                                                                                                                                                                                                                                                        |

| Z =<br>CLRWDT<br>Syntax:                                                                             | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                    |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:                                                                | Clear Watchdog Timer<br>[ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow TO;$                                                                                                                                                                                                                                                |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:<br>Operation:                                                  | Clear Watchdog Timer<br>[ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$<br>$1 \rightarrow \overline{PD}$                                                                                                                                                                                                    |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:                              | Clear Watchdog Timer<br>[ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$<br>$1 \rightarrow \overline{PD}$<br>$\overline{TO}, \overline{PD}$                                                                                                                                                                  |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                 | Clear Watchdog Timer[ label ] CLRWDTNone $00h \rightarrow WDT;$ $0 \rightarrow WDT$ prescaler (if assigned); $1 \rightarrow \overline{TO};$ $1 \rightarrow \overline{PD}$ $\overline{TO}, \overline{PD}$ $0000  0000  0100$ The CLRWDT instruction resets theWDT. It also resets the prescaler, ifthe prescaler is assigned to theWDT and not Timer0. Status bits                                       |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description: | Clear Watchdog Timer[ label ] CLRWDTNone $00h \rightarrow WDT$ ; $0 \rightarrow WDT$ prescaler (if assigned); $1 \rightarrow \overline{TO}$ ; $1 \rightarrow \overline{PD}$ $\overline{TO}$ , $\overline{PD}$ $0000$ $0000$ $0100$ The CLRWDT instruction resets theWDT. It also resets the prescaler, ifthe prescaler is assigned to theWDT and not Timer0. Status bitsTO and $\overline{PD}$ are set. |

| After Instruction |   |      |

|-------------------|---|------|

| WDT counter       | = | 0x00 |

| WDT prescaler     | = | 0    |

| TO                | = | 1    |

| PD                | = | 1    |

# PIC16C5X

| IORLW                                               | Inclusive OR literal with W                                                                                                 |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                                             | [ <i>label</i> ] IORLW k                                                                                                    |  |  |

| Operands:                                           | $0 \le k \le 255$                                                                                                           |  |  |

| Operation:                                          | (W) .OR. (k) $\rightarrow$ (W)                                                                                              |  |  |

| Status Affected:                                    | Z                                                                                                                           |  |  |

| Encoding:                                           | 1101 kkkk kkkk                                                                                                              |  |  |

| Description:                                        | The contents of the W register are<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W regis-<br>ter. |  |  |

| Words:                                              | 1                                                                                                                           |  |  |

| Cycles:                                             | 1                                                                                                                           |  |  |

| Example:                                            | IORLW 0x35                                                                                                                  |  |  |

| Before Instru<br>W =<br>After Instruc<br>W =<br>Z = | 0x9A<br>tion                                                                                                                |  |  |

| IORWF                                                            | Inclusive OR W with f                                                                                                                                                 |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                          | [ <i>label</i> ] IORWF f,d                                                                                                                                            |

| Operands:                                                        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                            |

| Operation:                                                       | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                                      |

| Status Affected:                                                 | Z                                                                                                                                                                     |

| Encoding:                                                        | 0001 00df ffff                                                                                                                                                        |

| Description:                                                     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |

| Words:                                                           | 1                                                                                                                                                                     |

| Cycles:                                                          | 1                                                                                                                                                                     |

| Example:                                                         | IORWF RESULT, 0                                                                                                                                                       |

| Before Instru<br>RESUL<br>W<br>After Instruct<br>RESUL<br>W<br>Z | Γ = 0x13<br>= 0x91<br>tion                                                                                                                                            |

| MOVF                                           | Move f                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:                                        | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| Operands:                                      | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| Operation:                                     | $(f) \rightarrow (dest)$                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| Status Affected:                               | Z                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Encoding:                                      | 0010 00df ffff                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| Description:                                   | The contents of register 'f' is<br>moved to destination 'd'. If 'd' is 0,<br>destination is the W register. If 'd'<br>is 1, the destination is file<br>register 'f'. 'd' is 1 is useful to test a<br>file register since status flag Z is<br>affected. |  |  |  |  |  |  |  |  |

| Words:                                         | 1                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Cycles:                                        | 1                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Example:                                       | MOVF FSR, 0                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| After Instruction<br>W = value in FSR register |                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| MOVLW                         | Move Literal to W    |       |               |        |  |  |  |  |  |  |

|-------------------------------|----------------------|-------|---------------|--------|--|--|--|--|--|--|

| Syntax:                       | [ label ]            | MOVLW | k             |        |  |  |  |  |  |  |

| Operands:                     | $0 \le k \le 255$    |       |               |        |  |  |  |  |  |  |

| Operation:                    | $k \rightarrow (W)$  |       |               |        |  |  |  |  |  |  |

| Status Affected:              | None                 |       |               |        |  |  |  |  |  |  |

| Encoding:                     | 1100                 | kkkk  | kkkk          |        |  |  |  |  |  |  |

| Description:                  | The eigh<br>the W re |       | 'k' is loaded | d into |  |  |  |  |  |  |

| Words:                        | 1                    |       |               |        |  |  |  |  |  |  |

| Cycles:                       | 1                    |       |               |        |  |  |  |  |  |  |

| Example:                      | MOVLW                | 0x5A  |               |        |  |  |  |  |  |  |

| After Instruction<br>W = 0x5A |                      |       |               |        |  |  |  |  |  |  |

| SUBWF            | Subt                                                                                                      | ract W           | from f               |  |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------|------------------|----------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [label                                                                                                    | JSL              | JBWF f,d             |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le f$                                                                                                 | ≤ 31             |                      |  |  |  |  |  |  |  |  |

| •                | d ∈ [0                                                                                                    | D,1]             |                      |  |  |  |  |  |  |  |  |

| Operation:       | (f) – (                                                                                                   | W) $\rightarrow$ | (dest)               |  |  |  |  |  |  |  |  |

| Status Affected: | C, DO                                                                                                     | C, Z             |                      |  |  |  |  |  |  |  |  |

| Encoding:        | 000                                                                                                       | - 1              | Odf ffff             |  |  |  |  |  |  |  |  |

| Description:     | Subtract (2's complement method)<br>the W register from register 'f'. If 'd'                              |                  |                      |  |  |  |  |  |  |  |  |

|                  | is 0 the result is stored in the W<br>register. If 'd' is 1 the result is<br>stored back in register 'f'. |                  |                      |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                         |                  |                      |  |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                         |                  |                      |  |  |  |  |  |  |  |  |

| Example 1:       | SUBW                                                                                                      | FF               | REG1, 1              |  |  |  |  |  |  |  |  |

| Before Instru    | ction                                                                                                     |                  |                      |  |  |  |  |  |  |  |  |

| REG1             | =                                                                                                         | 3                |                      |  |  |  |  |  |  |  |  |

| W                | =                                                                                                         | 2                |                      |  |  |  |  |  |  |  |  |

| С                | =                                                                                                         | ?                |                      |  |  |  |  |  |  |  |  |

| After Instruct   | ion                                                                                                       |                  |                      |  |  |  |  |  |  |  |  |

| REG1             | =                                                                                                         | 1                |                      |  |  |  |  |  |  |  |  |

| W<br>C           | =                                                                                                         | 2<br>1           | , recult is positive |  |  |  |  |  |  |  |  |

| Example 2:       | =                                                                                                         | I                | ; result is positive |  |  |  |  |  |  |  |  |

| Before Instru    | ction                                                                                                     |                  |                      |  |  |  |  |  |  |  |  |

| REG1             | =                                                                                                         | 2                |                      |  |  |  |  |  |  |  |  |

| W                | =                                                                                                         | 2                |                      |  |  |  |  |  |  |  |  |

| C                | =                                                                                                         | ?                |                      |  |  |  |  |  |  |  |  |

| After Instruct   | ion                                                                                                       |                  |                      |  |  |  |  |  |  |  |  |

| REG1             | =                                                                                                         | 0                |                      |  |  |  |  |  |  |  |  |

| W                | =                                                                                                         | 2                |                      |  |  |  |  |  |  |  |  |

| С                | =                                                                                                         | 1                | ; result is zero     |  |  |  |  |  |  |  |  |

| Example 3:       |                                                                                                           |                  |                      |  |  |  |  |  |  |  |  |

| Before Ins       | tructio                                                                                                   |                  |                      |  |  |  |  |  |  |  |  |

| REG1             | =                                                                                                         | 1                |                      |  |  |  |  |  |  |  |  |

| W                | =                                                                                                         | 2                |                      |  |  |  |  |  |  |  |  |

| C                | =                                                                                                         | ?                |                      |  |  |  |  |  |  |  |  |

| After Instruct   |                                                                                                           | 0.VEE            |                      |  |  |  |  |  |  |  |  |

| REG1<br>W        | =                                                                                                         | 0xFF<br>2        |                      |  |  |  |  |  |  |  |  |

| C                | _                                                                                                         | 2                | ; result is negative |  |  |  |  |  |  |  |  |

| Ũ                | -                                                                                                         | U                | , isourio nogativo   |  |  |  |  |  |  |  |  |

| SWAPF                                                               | Swap Nibbles in f                                                                                                                                                        |  |  |  |  |  |  |  |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:                                                             | [label] SWAPF f,d                                                                                                                                                        |  |  |  |  |  |  |  |

| Operands:                                                           | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                                         |  |  |  |  |  |  |  |

| Operation:                                                          | $(f<3:0>) \rightarrow (dest<7:4>);$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                                |  |  |  |  |  |  |  |

| Status Affected:                                                    | None                                                                                                                                                                     |  |  |  |  |  |  |  |

| Encoding:                                                           | 0011 10df ffff                                                                                                                                                           |  |  |  |  |  |  |  |

| Description:                                                        | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is 0<br>the result is placed in W register. If<br>'d' is 1 the result is placed in<br>register 'f'. |  |  |  |  |  |  |  |

| Words:                                                              | 1                                                                                                                                                                        |  |  |  |  |  |  |  |

| Cycles:                                                             | 1                                                                                                                                                                        |  |  |  |  |  |  |  |

| Example                                                             | SWAPF REG1, 0                                                                                                                                                            |  |  |  |  |  |  |  |

| REG1<br>After Instruct<br>REG1<br>W                                 | = 0xA5<br>ion<br>= 0xA5<br>= 0x5A                                                                                                                                        |  |  |  |  |  |  |  |

| TRIS                                                                | Load TRIS Register                                                                                                                                                       |  |  |  |  |  |  |  |

| Syntax:                                                             | [ <i>label</i> ] TRIS f                                                                                                                                                  |  |  |  |  |  |  |  |

| Operands:                                                           | f = 5, 6 or 7                                                                                                                                                            |  |  |  |  |  |  |  |

| Operation:                                                          | (W) $\rightarrow$ TRIS register f                                                                                                                                        |  |  |  |  |  |  |  |

| Status Affected:                                                    | None                                                                                                                                                                     |  |  |  |  |  |  |  |

| Encoding:                                                           | 0000 0000 0fff                                                                                                                                                           |  |  |  |  |  |  |  |

| Description:                                                        | TRIS register 'f' ( $f = 5, 6, or 7$ ) is<br>loaded with the contents of the W<br>register.                                                                              |  |  |  |  |  |  |  |

| Words:                                                              | 1                                                                                                                                                                        |  |  |  |  |  |  |  |

| Cycles:                                                             | 1                                                                                                                                                                        |  |  |  |  |  |  |  |

| Example                                                             | TRIS PORTB                                                                                                                                                               |  |  |  |  |  |  |  |

| Before Instruction<br>W = 0xA5<br>After Instruction<br>TRISB = 0xA5 |                                                                                                                                                                          |  |  |  |  |  |  |  |

NOTES:

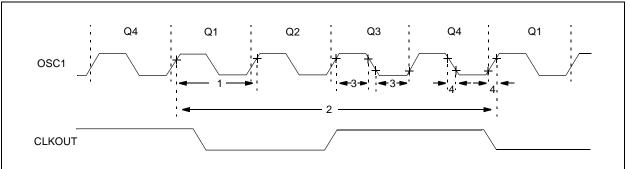

#### **13.6 Timing Diagrams and Specifications**

#### FIGURE 13-2: EXTERNAL CLOCK TIMING - PIC16CR54A

#### TABLE 13-1: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16CR54A

| AC Chara     | cteristics | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |      |     |       |                  |  |  |  |

|--------------|------------|------------------------------------------------------|-----|------|-----|-------|------------------|--|--|--|

| Param<br>No. | Symbol     | Characteristic                                       | Min | Тур† | Max | Units | Conditions       |  |  |  |

|              | Fosc       | External CLKIN Frequency <sup>(1)</sup>              | DC  | _    | 4.0 | MHz   | XT OSC mode      |  |  |  |

|              |            |                                                      | DC  | —    | 4.0 | MHz   | HS osc mode (04) |  |  |  |

|              |            |                                                      | DC  | _    | 10  | MHz   | HS osc mode (10) |  |  |  |

|              |            |                                                      | DC  | —    | 20  | MHz   | HS osc mode (20) |  |  |  |

|              |            |                                                      | DC  | _    | 200 | kHz   | LP osc mode      |  |  |  |

|              |            | Oscillator Frequency <sup>(1)</sup>                  | DC  |      | 4.0 | MHz   | RC OSC mode      |  |  |  |

|              |            |                                                      | 0.1 | _    | 4.0 | MHz   | XT osc mode      |  |  |  |

|              |            |                                                      | 4.0 | _    | 4.0 | MHz   | HS osc mode (04) |  |  |  |

|              |            |                                                      | 4.0 | _    | 10  | MHz   | HS osc mode (10) |  |  |  |

|              |            |                                                      | 4.0 | _    | 20  | MHz   | HS osc mode (20) |  |  |  |

|              |            |                                                      | 5.0 | —    | 200 | kHz   | LP osc mode      |  |  |  |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

**2:** Instruction cycle period (TCY) equals four times the input oscillator time base period.

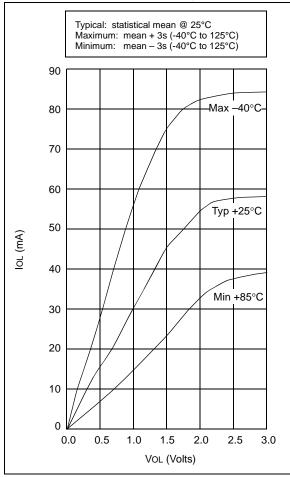

### 15.1 DC Characteristics: PIC16C54A-04, 10, 20 (Commercial) PIC16C54A-04I, 10I, 20I (Industrial) PIC16LC54A-04 (Commercial) PIC16LC54A-04I (Industrial)

| PIC16LC54A-04<br>PIC16LC54A-04I                                                                         |        |                                               |            | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial    |              |          |                                                                                                       |  |  |  |

|---------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|-------------------------------------------------------------------------------------------------------|--|--|--|

| (Commercial, Industrial)<br>PIC16C54A-04, 10, 20<br>PIC16C54A-04I, 10I, 20I<br>(Commercial, Industrial) |        |                                               |            | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |              |          |                                                                                                       |  |  |  |

| Param<br>No.                                                                                            | Symbol | Characteristic/Device                         | Min        | Тур†                                                                                                                                                                                         | Max          | Units    | Conditions                                                                                            |  |  |  |

|                                                                                                         | Vdd    | Supply Voltage                                |            |                                                                                                                                                                                              | •            |          |                                                                                                       |  |  |  |

| D001                                                                                                    |        | PIC16LC54A                                    | 3.0<br>2.5 | _                                                                                                                                                                                            | 6.25<br>6.25 | V<br>V   | XT and RC modes<br>LP mode                                                                            |  |  |  |

| D001A                                                                                                   |        | PIC16C54A                                     | 3.0<br>4.5 | _                                                                                                                                                                                            | 6.25<br>5.5  | V<br>V   | RC, XT and LP modes<br>HS mode                                                                        |  |  |  |

| D002                                                                                                    | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>  | —          | 1.5*                                                                                                                                                                                         | —            | V        | Device in SLEEP mode                                                                                  |  |  |  |

| D003                                                                                                    | VPOR   | VDD Start Voltage to<br>ensure Power-on Reset | —          | Vss                                                                                                                                                                                          | —            | V        | See Section 5.1 for details on<br>Power-on Reset                                                      |  |  |  |

| D004                                                                                                    | SVDD   | VDD Rise Rate to ensure<br>Power-on Reset     | 0.05*      | —                                                                                                                                                                                            | —            | V/ms     | See Section 5.1 for details on<br>Power-on Reset                                                      |  |  |  |

|                                                                                                         | IDD    | Supply Current <sup>(2)</sup>                 |            |                                                                                                                                                                                              |              |          |                                                                                                       |  |  |  |

| D005                                                                                                    |        | PIC16LC5X                                     | —          | 0.5                                                                                                                                                                                          | 2.5          | mA       | Fosc = 4.0 MHz, VDD = 5.5V,<br>RC <sup>(3)</sup> and XT modes                                         |  |  |  |

|                                                                                                         |        |                                               | —          | 11                                                                                                                                                                                           | 27           | μA       | Fosc = 32 kHz, VDD = 2.5V,<br>WDT disabled, LP mode, Commercial                                       |  |  |  |

|                                                                                                         |        |                                               | —          | 11                                                                                                                                                                                           | 35           | μA       | Fosc = 32 kHz, VDD = 2.5V,<br>WDT disabled, LP mode, Industrial                                       |  |  |  |

| D005A                                                                                                   |        | PIC16C5X                                      | —          | 1.8                                                                                                                                                                                          | 2.4          | mA       | Fosc = 4.0 MHz, VDD = 5.5V,<br>RC <sup>(3)</sup> and XT modes                                         |  |  |  |

|                                                                                                         |        |                                               | —          | 2.4                                                                                                                                                                                          | 8.0          | mA       | Fosc = 10 MHz, VDD = 5.5V, HS mode                                                                    |  |  |  |

|                                                                                                         |        |                                               | _          | 4.5<br>14                                                                                                                                                                                    | 16<br>29     | mA<br>μA | Fosc = 20 MHz, VDD = 5.5V, HS mode<br>Fosc = 32 kHz, VDD = 3.0V,<br>WDT disabled, LP mode, Commercial |  |  |  |

|                                                                                                         |        |                                               | —          | 17                                                                                                                                                                                           | 37           | μA       | Fosc = $32 \text{ kHz}$ , VDD = $3.0 \text{V}$ ,<br>WDT disabled, LP mode, Industrial                 |  |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

These parameters are characterized but not tested.

- † Data in "Typ" column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

#### 15.3 DC Characteristics: PIC16LV54A-02 (Commercial) PIC16LV54A-02I (Industrial)

| PIC16LV54A-02<br>PIC16LV54A-02I<br>(Commercial, Industrial) |        |                                                                                                                     |       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                        |                      |                                                                                                                |  |  |

|-------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------|------------------------|----------------------|----------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.                                                | Symbol | Characteristic                                                                                                      | Min   | Тур†                                                 | Max                    | Units                | Conditions                                                                                                     |  |  |

| D001                                                        | Vdd    | Supply Voltage<br>RC and XT modes                                                                                   | 2.0   | _                                                    | 3.8                    | V                    |                                                                                                                |  |  |

| D002                                                        | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                                                                        | _     | 1.5*                                                 | —                      | V                    | Device in SLEEP mode                                                                                           |  |  |

| D003                                                        | VPOR   | VDD Start Voltage to ensure<br>Power-on Reset                                                                       | —     | Vss                                                  | —                      | V                    | See Section 5.1 for details on<br>Power-on Reset                                                               |  |  |

| D004                                                        | Svdd   | VDD Rise Rate to ensure<br>Power-on Reset                                                                           | 0.05* | —                                                    | —                      | V/ms                 | See Section 5.1 for details on<br>Power-on Reset                                                               |  |  |

| D010                                                        | IDD    | <b>Supply Current<sup>(2)</sup></b><br>RC <sup>(3)</sup> and XT modes<br>LP mode, Commercial<br>LP mode, Industrial |       | 0.5<br>11<br>14                                      | <br>27<br>35           | mA<br>μA<br>μA       | Fosc = 2.0 MHz, VDD = 3.0V<br>Fosc = 32 kHz, VDD = 2.5V WDT disabled<br>Fosc = 32 kHz, VDD = 2.5V WDT disabled |  |  |

| D020                                                        | IPD    | <b>Power-down Current<sup>(2,4)</sup></b><br>Commercial<br>Commercial<br>Industrial<br>Industrial                   |       | 2.5<br>0.25<br>3.5<br>0.3                            | 12<br>4.0<br>14<br>5.0 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 2.5V, WDT enabled<br>VDD = 2.5V, WDT disabled<br>VDD = 2.5V, WDT enabled<br>VDD = 2.5V, WDT disabled     |  |  |

These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to VSS, T0CKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- **3:** Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

- 4: The oscillator start-up time can be as much as 8 seconds for XT and LP oscillator selection on wake-up from SLEEP mode or during initial power-up.

| TABLE 15-1: | EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16C54A |

|-------------|------------------------------------------------|

|-------------|------------------------------------------------|

| AC Chara     | acteristics | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -20^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} - PIC16LV54A-02I \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |      |        |        |       |                          |  |  |

|--------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|--------|-------|--------------------------|--|--|

| Param<br>No. | Symbol      | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                     | Min  | Тур†   | Max    | Units | Conditions               |  |  |

| 1            | Tosc        | External CLKIN Period <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                               | 250  | _      |        | ns    | XT OSC mode              |  |  |

|              |             |                                                                                                                                                                                                                                                                                                                                                                                                                    | 500  | —      | —      | ns    | XT osc mode (PIC16LV54A) |  |  |

|              |             |                                                                                                                                                                                                                                                                                                                                                                                                                    | 250  | —      | —      | ns    | HS osc mode (04)         |  |  |