Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 20                                                                        |

| Program Memory Size        | 768B (512 x 12)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 24 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6.25V                                                                |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c55-rci-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

### 4.0 OSCILLATOR CONFIGURATIONS

### 4.1 Oscillator Types

PIC16C5Xs can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

- 1. LP: Low Power Crystal

- 2. XT: Crystal/Resonator

- 3. HS: High Speed Crystal/Resonator

- 4. RC: Resistor/Capacitor

**Note:** Not all oscillator selections available for all parts. See Section 9.1.

### 4.2 Crystal Oscillator/Ceramic Resonators

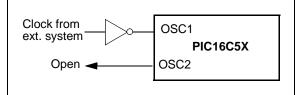

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 4-1). The PIC16C5X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source drive the OSC1/CLKIN pin (Figure 4-2).

### FIGURE 4-1: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

FIGURE 4-2:

### EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

### TABLE 4-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS -PIC16C5X, PIC16CR5X

| Osc<br>Type | Resonator<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |

|-------------|-------------------|------------------|------------------|

| XT          | 455 kHz           | 68-100 pF        | 68-100 pF        |

|             | 2.0 MHz           | 15-33 pF         | 15-33 pF         |

|             | 4.0 MHz           | 10-22 pF         | 10-22 pF         |

| HS          | 8.0 MHz           | 10-22 pF         | 10-22 pF         |

|             | 16.0 MHz          | 10 pF            | 10 pF            |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

### TABLE 4-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR -PIC16C5X. PIC16CR5X

|             | ,                     |                 |                  |  |

|-------------|-----------------------|-----------------|------------------|--|

| Osc<br>Type | Crystal<br>Freq       | Cap.Range<br>C1 | Cap. Range<br>C2 |  |

| LP          | 32 kHz <sup>(1)</sup> | 15 pF           | 15 pF            |  |

| XT          | 100 kHz               | 15-30 pF        | 200-300 pF       |  |

|             | 200 kHz               | 15-30 pF        | 100-200 pF       |  |

|             | 455 kHz               | 15-30 pF        | 15-100 pF        |  |

|             | 1 MHz                 | 15-30 pF        | 15-30 pF         |  |

|             | 2 MHz                 | 15 pF           | 15 pF            |  |

|             | 4 MHz                 | 15 pF           | 15 pF            |  |

| HS          | 4 MHz                 | 15 pF           | 15 pF            |  |

|             | 8 MHz                 | 15 pF           | 15 pF            |  |

|             | 20 MHz                | 15 pF           | 15 pF            |  |

### Note 1: For VDD > 4.5V, C1 = C2 $\approx$ 30 pF is recommended.

These values are for design guidance only. Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

**Note:** If you change from this device to another device, please verify oscillator characteristics in your application.

### 7.0 I/O PORTS

As with any other register, the I/O Registers can be written and read under program control. However, read instructions (e.g., MOVF PORTB, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers (TRISA, TRISB, TRISC) are all set.

### 7.1 PORTA

PORTA is a 4-bit I/O Register. Only the low order 4 bits are used (RA<3:0>). Bits 7-4 are unimplemented and read as '0's.

### 7.2 PORTB

PORTB is an 8-bit I/O Register (PORTB<7:0>).

### 7.3 PORTC

PORTC is an 8-bit I/O Register for PIC16C55, PIC16C57 and PIC16CR57.

PORTC is a General Purpose Register for PIC16C54, PIC16CR54, PIC16CR56, PIC16CR56, PIC16CS8 and PIC16CR58.

### 7.4 TRIS Registers

The Output Driver Control Registers are loaded with the contents of the W Register by executing the TRIS f instruction. A '1' from a TRIS Register bit puts the corresponding output driver in a hi-impedance (input) mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer.

| Note: | A read of the ports reads the pins, not the    |

|-------|------------------------------------------------|

|       | output data latches. That is, if an output     |

|       | driver on a pin is enabled and driven high,    |

|       | but the external system is holding it low, a   |

|       | read of the port will indicate that the pin is |

|       | low.                                           |

The TRIS Registers are "write-only" and are set (output drivers disabled) upon RESET.

| TABLE 7-1: | SUMMARY OF PORT REGISTERS |

|------------|---------------------------|

|            |                           |

#### Value on Value on Bit 4 Bit 3 Bit 1 Bit 0 MCLR and Address Name Bit 7 Bit 6 Bit 5 Bit 2 Power-On Reset WDT Reset TRIS N/A I/O Control Registers (TRISA, TRISB, TRISC) 1111 1111 1111 1111 05h PORTA RA3 RA2 RA1 RA0 \_ \_ \_ \_ xxxx \_ \_ \_ \_ uuuu PORTB 06h RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0 XXXX XXXX uuuu uuuu 07h PORTC RC7 RC6 RC5 RC4 RC3 RC2 RC1 RC0 XXXX XXXX uuuu uuuu

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0', Shaded cells = unimplemented, read as '0'

### 7.5 I/O Interfacing

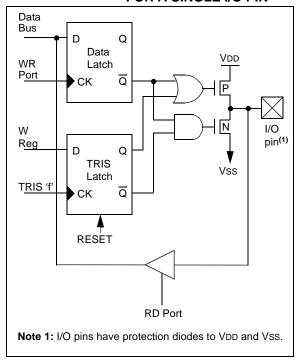

The equivalent circuit for an I/O port pin is shown in Figure 7-1. All ports may be used for both input and output operation. For input operations these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF PORTB, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit (in TRISA, TRISB, TRISC) must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin can be programmed individually as input or output.

### FIGURE 7-1: EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

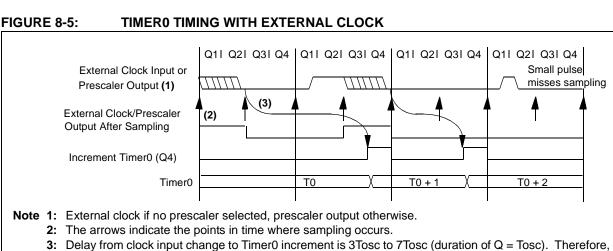

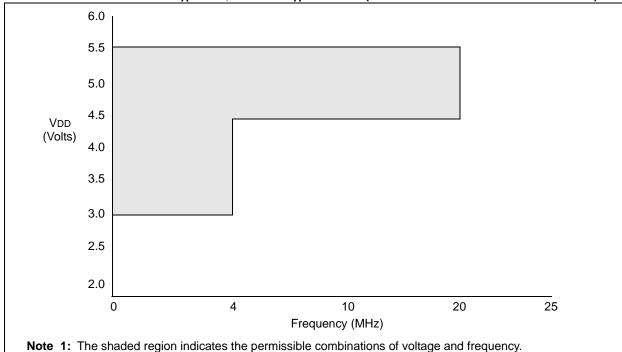

### 8.1 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 8.1.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 8-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 8.1.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 8-5 shows the delay from the external clock edge to the timer incrementing.

Belay from clock input change to Timer0 increment is 3 lose to 7 lose (duration of Q = lose). There the error in measuring the interval between two edges on Timer0 input = ± 4 Tose max.

### 9.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits that deal with the needs of realtime applications. The PIC16C5X family of microcontrollers have a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These features are:

- Oscillator Selection (Section 4.0)

- RESET (Section 5.0)

- Power-On Reset (Section 5.1)

- Device Reset Timer (Section 5.2)

- Watchdog Timer (WDT) (Section 9.2)

- SLEEP (Section 9.3)

- Code protection (Section 9.4)

- ID locations (Section 9.5)

The PIC16C5X Family has a Watchdog Timer which can be shut off only through configuration bit WDTE. It runs off of its own RC oscillator for added reliability. There is an 18 ms delay provided by the Device Reset Timer (DRT), intended to keep the chip in RESET until the crystal oscillator is stable. With this timer on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake up from SLEEP through external RESET or through a Watchdog Timer time-out. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options. NOTES:

# PIC16C5X

| COMF                                                 | Complement f                                                                                                                                                          |  |  |  |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                              | [label] COMF f,d                                                                                                                                                      |  |  |  |

| Operands:                                            | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                            |  |  |  |

| Operation:                                           | $(\overline{f}) \rightarrow (dest)$                                                                                                                                   |  |  |  |

| Status Affected:                                     | Z                                                                                                                                                                     |  |  |  |

| Encoding:                                            | 0010 01df ffff                                                                                                                                                        |  |  |  |

| Description:                                         | The contents of register 'f' are<br>complemented. If 'd' is 0 the result<br>is stored in the W register. If 'd' is 1<br>the result is stored back in<br>register 'f'. |  |  |  |

| Words:                                               | 1                                                                                                                                                                     |  |  |  |

| Cycles:                                              | 1                                                                                                                                                                     |  |  |  |

| Example:                                             | COMF REG1,0                                                                                                                                                           |  |  |  |

| Before Instru<br>REG1<br>After Instruct<br>REG1<br>W | = 0x13                                                                                                                                                                |  |  |  |

| DECF                                                    | Decreme                                                                                                                                     | ent f   |      |  |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------|------|--|

| Syntax:                                                 | [ label ]                                                                                                                                   | DECF f, | d    |  |

| Operands:                                               | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                              |         |      |  |

| Operation:                                              | $(f) - 1 \rightarrow$                                                                                                                       | (dest)  |      |  |

| Status Affected:                                        | Z                                                                                                                                           |         |      |  |

| Encoding:                                               | 0000                                                                                                                                        | 11df    | ffff |  |

| Description:                                            | Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If<br>'d' is 1 the result is stored back in<br>register 'f'. |         |      |  |

| Words:                                                  | 1                                                                                                                                           |         |      |  |

| Cycles:                                                 | 1                                                                                                                                           |         |      |  |

| Example:                                                | DECF                                                                                                                                        | CNT,    | 1    |  |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0<br>= 0<br>ion                                                                                                                           | <01     |      |  |

| DECFSZ                                                | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                               | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                        |

| Operands:                                             | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                                |

| Operation:                                            | (f) $-1 \rightarrow d$ ; skip if result = 0                                                                                                                                                                                                                                                                                               |

| Status Affected:                                      | None                                                                                                                                                                                                                                                                                                                                      |

| Encoding:                                             | 0010 11df ffff                                                                                                                                                                                                                                                                                                                            |

| Description:                                          | The contents of register 'f' are dec-<br>remented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded and a NOP is executed<br>instead making it a two-cycle<br>instruction. |

| Words:                                                | 1                                                                                                                                                                                                                                                                                                                                         |

| Cycles:                                               | 1(2)                                                                                                                                                                                                                                                                                                                                      |

| Example:                                              | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                        |

| Before Instru<br>PC                                   | = address (HERE)                                                                                                                                                                                                                                                                                                                          |

| After Instruct<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC | tion<br>= CNT - 1;<br>= 0,<br>= address (CONTINUE);<br>≠ 0,<br>= address (HERE+1)                                                                                                                                                                                                                                                         |

# PIC16C5X

| IORLW                                               | Inclusive OR literal with W                                                                                                 |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                             | [label] IORLW k                                                                                                             |  |  |  |

| Operands:                                           | $0 \leq k \leq 255$                                                                                                         |  |  |  |

| Operation:                                          | (W) .OR. (k) $\rightarrow$ (W)                                                                                              |  |  |  |

| Status Affected:                                    | Z                                                                                                                           |  |  |  |

| Encoding:                                           | 1101 kkkk kkkk                                                                                                              |  |  |  |

| Description:                                        | The contents of the W register are<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W regis-<br>ter. |  |  |  |

| Words:                                              | 1                                                                                                                           |  |  |  |

| Cycles:                                             | 1                                                                                                                           |  |  |  |

| Example:                                            | IORLW 0x35                                                                                                                  |  |  |  |

| Before Instru<br>W =<br>After Instruc<br>W =<br>Z = | 0x9A<br>tion                                                                                                                |  |  |  |

| IORWF                                                            | Inclusive OR W with f                                                                                                                                                 |  |  |  |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                                          | [ <i>label</i> ] IORWF f,d                                                                                                                                            |  |  |  |

| Operands:                                                        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                            |  |  |  |

| Operation:                                                       | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                                      |  |  |  |

| Status Affected:                                                 | Z                                                                                                                                                                     |  |  |  |

| Encoding:                                                        | 0001 00df ffff                                                                                                                                                        |  |  |  |

| Description:                                                     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |  |  |  |

| Words:                                                           | 1                                                                                                                                                                     |  |  |  |

| Cycles:                                                          | 1                                                                                                                                                                     |  |  |  |

| Example:                                                         | IORWF RESULT, 0                                                                                                                                                       |  |  |  |

| Before Instru<br>RESUL<br>W<br>After Instruct<br>RESUL<br>W<br>Z | Γ = 0x13<br>= 0x91<br>tion                                                                                                                                            |  |  |  |

| MOVF                  | Move f                                                                                                                                                                                                                                                 |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:               | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                              |

| Operands:             | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                                                                                         |

| Operation:            | $(f) \rightarrow (dest)$                                                                                                                                                                                                                               |

| Status Affected:      | Z                                                                                                                                                                                                                                                      |

| Encoding:             | 0010 00df ffff                                                                                                                                                                                                                                         |

| Description:          | The contents of register 'f' is<br>moved to destination 'd'. If 'd' is 0,<br>destination is the W register. If 'd'<br>is 1, the destination is file<br>register 'f'. 'd' is 1 is useful to test a<br>file register since status flag Z is<br>affected. |

| Words:                | 1                                                                                                                                                                                                                                                      |

| Cycles:               | 1                                                                                                                                                                                                                                                      |

| Example:              | MOVF FSR, 0                                                                                                                                                                                                                                            |

| After Instruct<br>W = | tion<br>- value in FSR register                                                                                                                                                                                                                        |

| MOVLW                         | Move Literal to W    |       |               |        |

|-------------------------------|----------------------|-------|---------------|--------|

| Syntax:                       | [ label ]            | MOVLW | k             |        |

| Operands:                     | $0 \leq k \leq 2$    | 55    |               |        |

| Operation:                    | $k \rightarrow (W)$  |       |               |        |

| Status Affected:              | None                 |       |               |        |

| Encoding:                     | 1100                 | kkkk  | kkkk          |        |

| Description:                  | The eigh<br>the W re |       | 'k' is loaded | d into |

| Words:                        | 1                    |       |               |        |

| Cycles:                       | 1                    |       |               |        |

| Example:                      | MOVLW                | 0x5A  |               |        |

| After Instruction<br>W = 0x5A |                      |       |               |        |

### 12.2 DC Characteristics: PIC16C54/55/56/57-RCI, XTI, 10I, HSI, LPI (Industrial)

|              |                              |                                                                                                                                              | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                       |                                    |                            |                                                                                                                                                                                                          |  |  |

|--------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No. | Symbol Characteristic/Device |                                                                                                                                              | Min                                                                                                                                       | Тур†                                  | Max                                | Units                      | Conditions                                                                                                                                                                                               |  |  |

| D001         | Vdd                          | Supply Voltage<br>PIC16C5X-RCI<br>PIC16C5X-XTI<br>PIC16C5X-10I<br>PIC16C5X-HSI<br>PIC16C5X-LPI                                               | 3.0<br>3.0<br>4.5<br>4.5<br>2.5                                                                                                           |                                       | 6.25<br>6.25<br>5.5<br>5.5<br>6.25 | V<br>V<br>V<br>V           |                                                                                                                                                                                                          |  |  |

| D002         | Vdr                          | RAM Data Retention Voltage <sup>(1)</sup>                                                                                                    |                                                                                                                                           | 1.5*                                  |                                    | V                          | Device in SLEEP mode                                                                                                                                                                                     |  |  |

| D003         | VPOR                         | VDD Start Voltage to ensure<br>Power-on Reset                                                                                                | —                                                                                                                                         | Vss                                   | —                                  | V                          | See Section 5.1 for details on<br>Power-on Reset                                                                                                                                                         |  |  |

| D004         | SVDD                         | VDD Rise Rate to ensure<br>Power-on Reset                                                                                                    | 0.05*                                                                                                                                     |                                       | —                                  | V/ms                       | See Section 5.1 for details on<br>Power-on Reset                                                                                                                                                         |  |  |

| D010         | IDD                          | Supply Current <sup>(2)</sup><br>PIC16C5X-RCI <sup>(3)</sup><br>PIC16C5X-XTI<br>PIC16C5X-10I<br>PIC16C5X-HSI<br>PIC16C5X-HSI<br>PIC16C5X-LPI |                                                                                                                                           | 1.8<br>1.8<br>4.8<br>4.8<br>9.0<br>15 | 3.3<br>3.3<br>10<br>10<br>20<br>40 | mA<br>mA<br>mA<br>mA<br>μA | Fosc = 4 MHz, VDD = $5.5V$<br>Fosc = 4 MHz, VDD = $5.5V$<br>Fosc = 10 MHz, VDD = $5.5V$<br>Fosc = 10 MHz, VDD = $5.5V$<br>Fosc = 20 MHz, VDD = $5.5V$<br>Fosc = $32$ kHz, VDD = $3.0V$ ,<br>WDT disabled |  |  |

| D020         | Ipd                          | Power-down Current <sup>(2)</sup>                                                                                                            | _                                                                                                                                         | 4.0<br>0.6                            | 14<br>12                           | μΑ<br>μΑ                   | VDD = 3.0V, WDT enabled<br>VDD = 3.0V, WDT disabled                                                                                                                                                      |  |  |

\* These parameters are characterized but not tested.

- † Data in "Typ" column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- **3:** Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

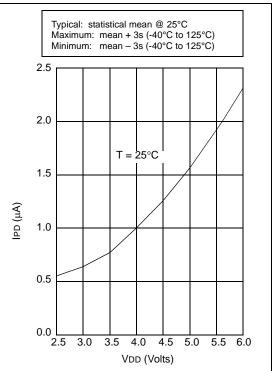

### FIGURE 14-5: TYPICAL IPD vs. VDD, WATCHDOG DISABLED

### 15.1 DC Characteristics: PIC16C54A-04, 10, 20 (Commercial) PIC16C54A-04I, 10I, 20I (Industrial) PIC16LC54A-04 (Commercial) PIC16LC54A-04I (Industrial)

| PIC16LC54A-04<br>PIC16LC54A-04I<br>(Commercial, Industrial) |                                                                             |                                               |            | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                                                                                                                                                              |          |                                                                                                       |  |  |  |  |

|-------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIC16C                                                      | PIC16C54A-04, 10, 20<br>PIC16C54A-04I, 10I, 20I<br>(Commercial, Industrial) |                                               |            |                                                                                                                                                                                           | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |          |                                                                                                       |  |  |  |  |

| Param<br>No. Symbol Characteristic/Device                   |                                                                             |                                               | Min        | Тур†                                                                                                                                                                                      | Max                                                                                                                                                                                          | Units    | Conditions                                                                                            |  |  |  |  |

|                                                             | Vdd                                                                         | Supply Voltage                                |            |                                                                                                                                                                                           | •                                                                                                                                                                                            |          |                                                                                                       |  |  |  |  |

| D001                                                        |                                                                             | PIC16LC54A                                    | 3.0<br>2.5 | _                                                                                                                                                                                         | 6.25<br>6.25                                                                                                                                                                                 | V<br>V   | XT and RC modes<br>LP mode                                                                            |  |  |  |  |

| D001A                                                       |                                                                             | PIC16C54A                                     | 3.0<br>4.5 | _                                                                                                                                                                                         | 6.25<br>5.5                                                                                                                                                                                  | V<br>V   | RC, XT and LP modes<br>HS mode                                                                        |  |  |  |  |

| D002                                                        | Vdr                                                                         | RAM Data Retention<br>Voltage <sup>(1)</sup>  | —          | 1.5*                                                                                                                                                                                      | —                                                                                                                                                                                            | V        | Device in SLEEP mode                                                                                  |  |  |  |  |

| D003                                                        | VPOR                                                                        | VDD Start Voltage to<br>ensure Power-on Reset | —          | Vss                                                                                                                                                                                       | —                                                                                                                                                                                            | V        | See Section 5.1 for details on<br>Power-on Reset                                                      |  |  |  |  |

| D004                                                        | SVDD                                                                        | VDD Rise Rate to ensure<br>Power-on Reset     | 0.05*      | —                                                                                                                                                                                         | —                                                                                                                                                                                            | V/ms     | See Section 5.1 for details on<br>Power-on Reset                                                      |  |  |  |  |

|                                                             | IDD                                                                         | Supply Current <sup>(2)</sup>                 |            |                                                                                                                                                                                           |                                                                                                                                                                                              |          |                                                                                                       |  |  |  |  |

| D005                                                        |                                                                             | PIC16LC5X                                     | —          | 0.5                                                                                                                                                                                       | 2.5                                                                                                                                                                                          | mA       | Fosc = 4.0 MHz, VDD = 5.5V,<br>RC <sup>(3)</sup> and XT modes                                         |  |  |  |  |

|                                                             |                                                                             |                                               | —          | 11                                                                                                                                                                                        | 27                                                                                                                                                                                           | μΑ       | Fosc = 32 kHz, VDD = 2.5V,<br>WDT disabled, LP mode, Commercial                                       |  |  |  |  |

|                                                             |                                                                             |                                               | —          | 11                                                                                                                                                                                        | 35                                                                                                                                                                                           | μA       | Fosc = 32 kHz, VDD = 2.5V,<br>WDT disabled, LP mode, Industrial                                       |  |  |  |  |

| D005A                                                       |                                                                             | PIC16C5X                                      | —          | 1.8                                                                                                                                                                                       | 2.4                                                                                                                                                                                          | mA       | Fosc = 4.0 MHz, VDD = 5.5V,<br>RC <sup>(3)</sup> and XT modes                                         |  |  |  |  |

|                                                             |                                                                             |                                               | —          | 2.4                                                                                                                                                                                       | 8.0                                                                                                                                                                                          | mA       | Fosc = 10 MHz, VDD = 5.5V, HS mode                                                                    |  |  |  |  |

|                                                             |                                                                             |                                               | _          | 4.5<br>14                                                                                                                                                                                 | 16<br>29                                                                                                                                                                                     | mA<br>μA | Fosc = 20 MHz, VDD = 5.5V, HS mode<br>Fosc = 32 kHz, VDD = 3.0V,<br>WDT disabled, LP mode, Commercial |  |  |  |  |

|                                                             |                                                                             |                                               | —          | 17                                                                                                                                                                                        | 37                                                                                                                                                                                           | μA       | Fosc = $32 \text{ kHz}$ , VDD = $3.0 \text{V}$ ,<br>WDT disabled, LP mode, Industrial                 |  |  |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

These parameters are characterized but not tested.

- † Data in "Typ" column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

## PIC16C5X

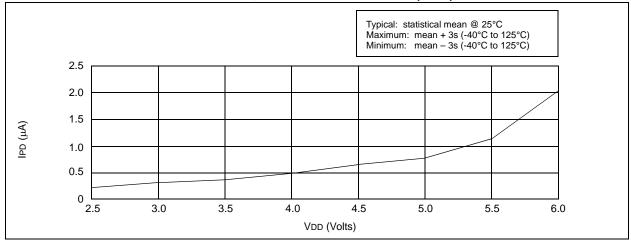

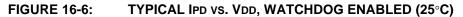

### FIGURE 16-5: TYPICAL IPD vs. VDD, WATCHDOG DISABLED (25°C)

### 17.0 ELECTRICAL CHARACTERISTICS - PIC16LC54A

### Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                   | –55°C to +125°C             |

|------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Storage temperature                                                                                              |                             |

| Voltage on VDD with respect to VSS                                                                               | 0 to +7.5V                  |

| Voltage on MCLR with respect to Vss                                                                              | 0 to +14V                   |

| Voltage on all other pins with respect to Vss                                                                    | 0.6V to (VDD + 0.6V)        |

| Total power dissipation <sup>(1)</sup>                                                                           | 800 mW                      |

| Max. current out of Vss pin                                                                                      | 150 mA                      |

| Max. current into Vod pin                                                                                        |                             |

| Max. current into an input pin (T0CKI only)                                                                      | ±500 μA                     |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                     | ±20 mA                      |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                                   | ±20 mA                      |

| Max. output current sunk by any I/O pin                                                                          | 25 mA                       |

| Max. output current sourced by any I/O pin                                                                       | 20 mA                       |

| Max. output current sourced by a single I/O (Port A, B or C)                                                     | 50 mA                       |

| Max. output current sunk by a single I/O (Port A, B or C)                                                        | 50 mA                       |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) x | IOH} + $\Sigma$ (VOL x IOL) |

**†** NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## PIC16C5X

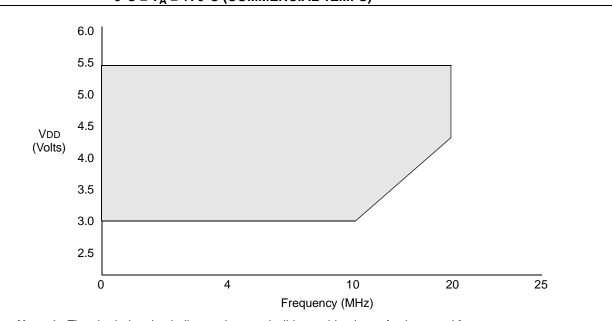

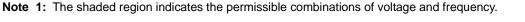

**2**: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

2: The maximum rated speed of the part limits the permissible combinations of voltage and frequency.

Please reference the Product Identification System section for the maximum rated speed of the parts.

### TABLE 17-1: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16C5X, PIC16CR5X

| AC Chara     | cteristics | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |            |        |            |          |                                |  |  |

|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|------------|----------|--------------------------------|--|--|

| Param<br>No. | Symbol     | Characteristic                                                                                                                                                                                                                                                                                                                   | Min        | Тур†   | Max        | Units    | Conditions                     |  |  |

| 2            | Тсу        | Instruction Cycle Time <sup>(2)</sup>                                                                                                                                                                                                                                                                                            | —          | 4/Fosc |            | —        |                                |  |  |

| 3            | TosL, TosH | Clock in (OSC1) Low or High<br>Time                                                                                                                                                                                                                                                                                              | 50*<br>20* | _      |            | ns<br>ns | XT oscillator<br>HS oscillator |  |  |

| 4            | TosR, TosF | Clock in (OSC1) Rise or Fall<br>Time                                                                                                                                                                                                                                                                                             | 2.0*       | _      | <br>25*    | μS<br>ns | LP oscillator<br>XT oscillator |  |  |

|              |            |                                                                                                                                                                                                                                                                                                                                  | _          | _      | 25*<br>50* | ns<br>ns | HS oscillator<br>LP oscillator |  |  |

- \* These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption.

When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

2: Instruction cycle period (TCY) equals four times the input oscillator time base period.

#### **FIGURE 17-9:** TIMER0 CLOCK TIMINGS - PIC16C5X, PIC16CR5X

#### **TABLE 17-4:** TIMER0 CLOCK REQUIREMENTS - PIC16C5X, PIC16CR5X

| ļ            | AC Chara | cteristics Standard Operatin<br>Operating Temperat | g Conditions (unless otherwise specified)<br>ure $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |     |       |                                                                |

|--------------|----------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|----------------------------------------------------------------|

| Param<br>No. | Symbol   | Characteristic                                     | Min                                                                                                                                                                                                                   | Тур† | Max | Units | Conditions                                                     |

| 40           | Tt0H     | T0CKI High Pulse Width<br>- No Prescaler           | 0.5 Tcy + 20*                                                                                                                                                                                                         |      | _   | ns    |                                                                |

|              |          | - With Prescaler                                   | 10*                                                                                                                                                                                                                   | _    | —   | ns    |                                                                |

| 41           | TtOL     | T0CKI Low Pulse Width<br>- No Prescaler            | 0.5 Tcy + 20*                                                                                                                                                                                                         | _    | _   | ns    |                                                                |

|              |          | - With Prescaler                                   | 10*                                                                                                                                                                                                                   | _    | _   | ns    |                                                                |

| 42           | Tt0P     | T0CKI Period                                       | 20 or <u>Tcy + 40</u> *<br>N                                                                                                                                                                                          | _    |     | ns    | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

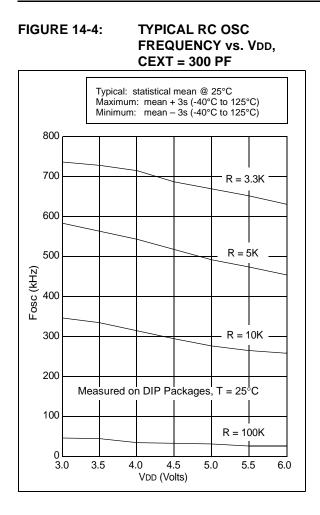

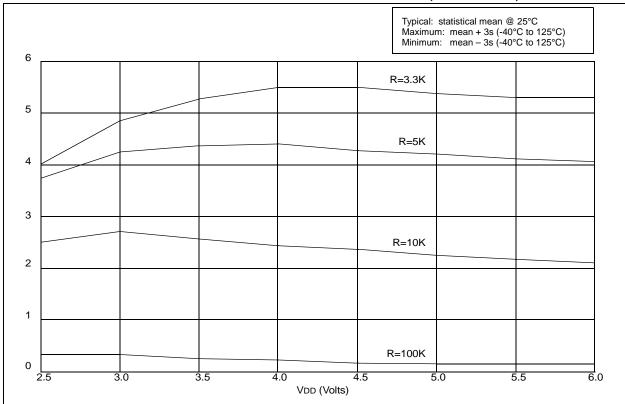

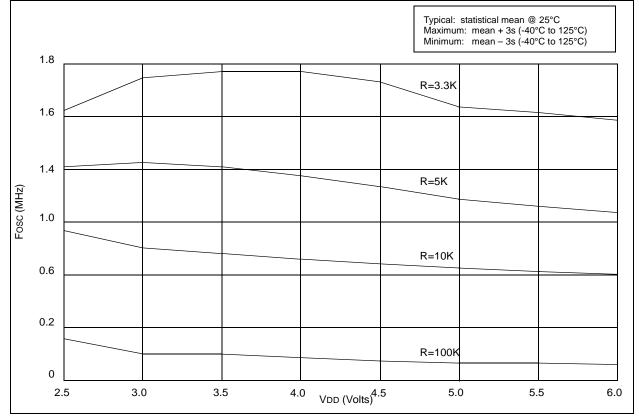

### FIGURE 18-2: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD, CEXT = 20 PF, 25°C

### **19.3 Timing Parameter Symbology and Load Conditions**

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. Tp | 2. TppS                                    |                    |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--------------------|--|--|--|--|--|--|--|

| Т     |                                            |                    |  |  |  |  |  |  |  |

| F     | Frequency                                  | T Time             |  |  |  |  |  |  |  |

| Lowe  | Lowercase letters (pp) and their meanings: |                    |  |  |  |  |  |  |  |

| рр    |                                            |                    |  |  |  |  |  |  |  |

| 2     | to                                         | mc MCLR            |  |  |  |  |  |  |  |

| ck    | CLKOUT                                     | osc oscillator     |  |  |  |  |  |  |  |

| су    | cycle time                                 | os OSC1            |  |  |  |  |  |  |  |

| drt   | device reset timer                         | t0 T0CKI           |  |  |  |  |  |  |  |

| io    | I/O port                                   | wdt watchdog timer |  |  |  |  |  |  |  |

| Uppe  | ercase letters and their meanings:         |                    |  |  |  |  |  |  |  |

| S     |                                            |                    |  |  |  |  |  |  |  |

| F     | Fall                                       | P Period           |  |  |  |  |  |  |  |

| н     | High                                       | R Rise             |  |  |  |  |  |  |  |

| Ι     | Invalid (Hi-impedance)                     | V Valid            |  |  |  |  |  |  |  |

| L     | Low                                        | Z Hi-impedance     |  |  |  |  |  |  |  |

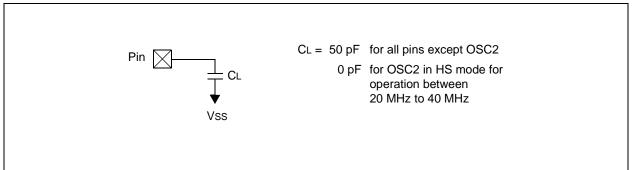

### FIGURE 19-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS -PIC16C54C/C55A/C56A/C57C/C58B-40

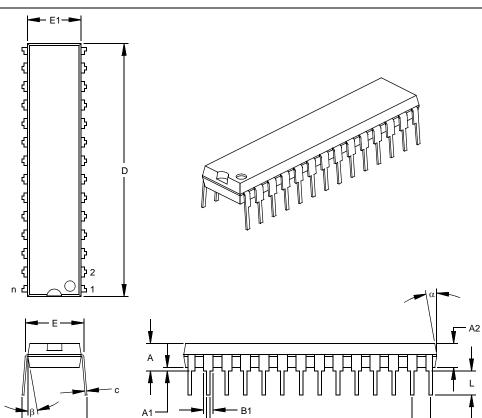

### 28-Lead Skinny Plastic Dual In-line (SP) - 300 mil (PDIP)

в

|                            | INCHES*   |       |       | MILLIMETERS |       |       |       |

|----------------------------|-----------|-------|-------|-------------|-------|-------|-------|

| Dimensi                    | on Limits | MIN   | NOM   | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n         |       | 28    |             |       | 28    |       |

| Pitch                      | р         |       | .100  |             |       | 2.54  |       |

| Top to Seating Plane       | А         | .140  | .150  | .160        | 3.56  | 3.81  | 4.06  |

| Molded Package Thickness   | A2        | .125  | .130  | .135        | 3.18  | 3.30  | 3.43  |

| Base to Seating Plane      | A1        | .015  |       |             | 0.38  |       |       |

| Shoulder to Shoulder Width | E         | .300  | .310  | .325        | 7.62  | 7.87  | 8.26  |

| Molded Package Width       | E1        | .275  | .285  | .295        | 6.99  | 7.24  | 7.49  |

| Overall Length             | D         | 1.345 | 1.365 | 1.385       | 34.16 | 34.67 | 35.18 |

| Tip to Seating Plane       | L         | .125  | .130  | .135        | 3.18  | 3.30  | 3.43  |

| Lead Thickness             | С         | .008  | .012  | .015        | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1        | .040  | .053  | .065        | 1.02  | 1.33  | 1.65  |

| Lower Lead Width           | В         | .016  | .019  | .022        | 0.41  | 0.48  | 0.56  |

| Overall Row Spacing        | èB        | .320  | .350  | .430        | 8.13  | 8.89  | 10.92 |

| Mold Draft Angle Top       | α         | 5     | 10    | 15          | 5     | 10    | 15    |

| Mold Draft Angle Bottom    | β         | 5     | 10    | 15          | 5     | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

eВ

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MO-095

Drawing No. C04-070

- p -

Notes:

NOTES: