Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Active                                                                    |

|---------------------------------------------------------------------------|

| PIC                                                                       |

| 8-Bit                                                                     |

| 4MHz                                                                      |

| -                                                                         |

| POR, WDT                                                                  |

| 20                                                                        |

| 768B (512 x 12)                                                           |

| OTP                                                                       |

| -                                                                         |

| 24 x 8                                                                    |

| 3V ~ 6.25V                                                                |

| -                                                                         |

| External                                                                  |

| -40°C ~ 85°C (TA)                                                         |

| Through Hole                                                              |

| 28-DIP (0.300", 7.62mm)                                                   |

| 28-SPDIP                                                                  |

| https://www.e-xfl.com/product-detail/microchip-technology/pic16c55-rci-sp |

|                                                                           |

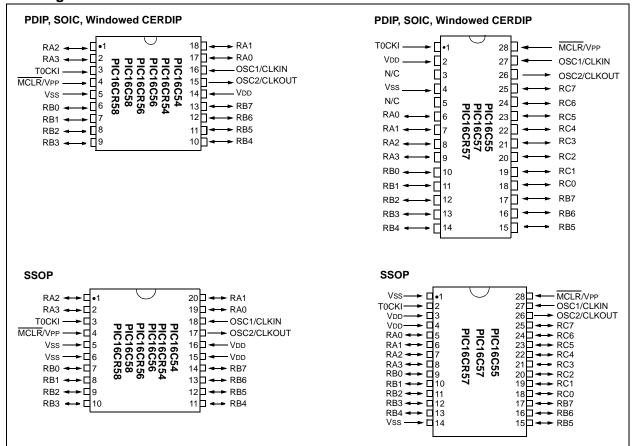

## **Pin Diagrams**

### **Device Differences**

DS30453E-page 2

| Device Differences |                  |                                      |            |                                    |                   |                |  |  |  |

|--------------------|------------------|--------------------------------------|------------|------------------------------------|-------------------|----------------|--|--|--|

| Device             | Voltage<br>Range | Oscillator<br>Selection<br>(Program) | Oscillator | Process<br>Technology<br>(Microns) | ROM<br>Equivalent | MCLR<br>Filter |  |  |  |

| PIC16C54           | 2.5-6.25         | Factory                              | See Note 1 | 1.2                                | PIC16CR54A        | No             |  |  |  |

| PIC16C54A          | 2.0-6.25         | User                                 | See Note 1 | 0.9                                | _                 | No             |  |  |  |

| PIC16C54C          | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | PIC16CR54C        | Yes            |  |  |  |

| PIC16C55           | 2.5-6.25         | Factory                              | See Note 1 | 1.7                                | _                 | No             |  |  |  |

| PIC16C55A          | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | _                 | Yes            |  |  |  |

| PIC16C56           | 2.5-6.25         | Factory                              | See Note 1 | 1.7                                | _                 | No             |  |  |  |

| PIC16C56A          | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | PIC16CR56A        | Yes            |  |  |  |

| PIC16C57           | 2.5-6.25         | Factory                              | See Note 1 | 1.2                                | _                 | No             |  |  |  |

| PIC16C57C          | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | PIC16CR57C        | Yes            |  |  |  |

| PIC16C58B          | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | PIC16CR58B        | Yes            |  |  |  |

| PIC16CR54A         | 2.5-6.25         | Factory                              | See Note 1 | 1.2                                | N/A               | Yes            |  |  |  |

| PIC16CR54C         | 2.5-5.5          | Factory                              | See Note 1 | 0.7                                | N/A               | Yes            |  |  |  |

| PIC16CR56A         | 2.5-5.5          | Factory                              | See Note 1 | 0.7                                | N/A               | Yes            |  |  |  |

| PIC16CR57C         | 2.5-5.5          | Factory                              | See Note 1 | 0.7                                | N/A               | Yes            |  |  |  |

| PIC16CR58B         | 2.5-5.5          | Factory                              | See Note 1 | 0.7                                | N/A               | Yes            |  |  |  |

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

Note: The table shown above shows the generic names of the PIC16C5X devices. For device varieties, please refer to Section 2.0.

## PIC16C5X

NOTES:

### 6.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions to control the operation of the device (Table 6-1).

The Special Registers can be classified into two sets. The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

TABLE 6-1: SPECIAL FUNCTION REGISTER SUMMARY

| Address            | Name   | Bit 7    | Bit 6       | Bit 5       | Bit 4     | Bit 3     | Bit 2     | Bit 1      | Bit 0    | Value on<br>Power-on<br>Reset | Details<br>on Page |

|--------------------|--------|----------|-------------|-------------|-----------|-----------|-----------|------------|----------|-------------------------------|--------------------|

| N/A                | TRIS   | I/O Cont | rol Regis   | ters (TRIS  |           | 1111 1111 | 35        |            |          |                               |                    |

| N/A                | OPTION | Contains | s control b | oits to con | figure Ti | mer0 and  | Timer0/V  | VDT pres   | caler    | 11 1111                       | 30                 |

| 00h                | INDF   | Uses co  | ntents of   | FSR to ac   | ddress da | ata memo  | ry (not a | physical r | egister) | XXXX XXXX                     | 32                 |

| 01h                | TMR0   | Timer0 N | Module R    | egister     |           |           |           |            |          | XXXX XXXX                     | 38                 |

| 02h <sup>(1)</sup> | PCL    | Low ord  | er 8 bits c | of PC       |           |           |           |            |          | 1111 1111                     | 31                 |

| 03h                | STATUS | PA2      | PA1         | PA0         | TO        | PD        | Z         | DC         | С        | 0001 1xxx                     | 29                 |

| 04h                | FSR    | Indirect | data mem    | ory addre   | ess point | er        |           |            | I.       | 1xxx xxxx <sup>(3)</sup>      | 32                 |

| 05h                | PORTA  | _        | _           | _           | _         | RA3       | RA2       | RA1        | RA0      | XXXX                          | 35                 |

| 06h                | PORTB  | RB7      | RB6         | RB5         | RB4       | RB3       | RB2       | RB1        | RB0      | XXXX XXXX                     | 35                 |

| 07h <sup>(2)</sup> | PORTC  | RC7      | RC6         | RC5         | RC4       | RC3       | RC2       | RC1        | RC0      | xxxx xxxx                     | 35                 |

Legend: x = unknown, u = unchanged, -= unimplemented, read as '0' (if applicable). Shaded cells = unimplemented or unused

**Note** 1: The upper byte of the Program Counter is not directly accessible. See Section 6.5 for an explanation of how to access these bits.

<sup>2:</sup> File address 07h is a General Purpose Register on the PIC16C54, PIC16CR54, PIC16C56, PIC16CR56, PIC16C58 and PIC16CR58.

<sup>3:</sup> These values are valid for PIC16C57/CR57/C58/CR58. For the PIC16C54/CR54/C55/C56/CR56, the value on RESET is 111x xxxx and for MCLR and WDT Reset, the value is 111u uuuu.

## PIC16C5X

NOTES:

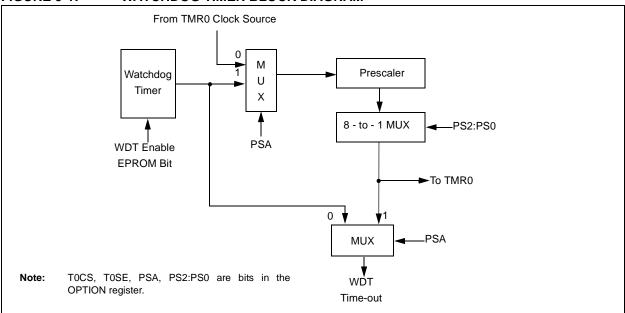

## 9.2 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins have been stopped, for example, by execution of a SLEEP instruction. During normal operation or SLEEP, a WDT Reset or Wake-up Reset generates a device RESET.

The TO bit (STATUS<4>) will be cleared upon a Watchdog Timer Reset (Section 6.3).

The WDT can be permanently disabled by programming the configuration bit WDTE as a '0' (Section 9.1). Refer to the PIC16C5X Programming Specifications (Literature Number DS30190) to determine how to access the configuration word.

### 9.2.1 WDT PERIOD

An 8-bit counter is available as a prescaler for the Timer0 module (Section 8.2), or as a postscaler for the Watchdog Timer (WDT), respectively. For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT, but not

both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the WDT, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio (Section 6.4).

The WDT has a nominal time-out period of 18 ms (with no prescaler). If a longer time-out period is desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT (under software control) by writing to the OPTION register. Thus, time-out a period of a nominal 2.3 seconds can be realized. These periods vary with temperature, VDD and part-to-part process variations (see Device Characterization).

Under worst case conditions (VDD = Min., Temperature = Max., WDT prescaler = 1:128), it may take several seconds before a WDT time-out occurs.

## 9.2.2 WDT PROGRAMMING CONSIDERATIONS

The CLRWDT instruction clears the WDT and the prescaler, if assigned to the WDT, and prevents it from timing out and generating a device RESET.

The SLEEP instruction RESETS the WDT and the prescaler, if assigned to the WDT. This gives the maximum SLEEP time before a WDT Wake-up Reset.

FIGURE 9-1: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 9-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on MCLR and WDT Reset |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|-----------------------------|

| N/A     | OPTION | _     | _     | Tosc  | Tose  | PSA   | PS2   | PS1   | PS0   | 11 1111                       | 11 1111                     |

Legend: u = unchanged, - = unimplemented, read as '0'. Shaded cells not used by Watchdog Timer.

| ADDWF            | Add W and f                       |                     |                                                                      |               |                  |                    |  |  |

|------------------|-----------------------------------|---------------------|----------------------------------------------------------------------|---------------|------------------|--------------------|--|--|

| Syntax:          | [ lab                             | [ label ] ADDWF f,d |                                                                      |               |                  |                    |  |  |

| Operands:        | $0 \le f \le 31$<br>$d \in [0,1]$ |                     |                                                                      |               |                  |                    |  |  |

| Operation:       | (W)                               | + (f)               | $\rightarrow$ (dest)                                                 |               |                  |                    |  |  |

| Status Affected: | C, D                              | )C, Z               | <u> </u>                                                             |               |                  |                    |  |  |

| Encoding:        | 00                                | 01                  | 11df                                                                 | ff            | ff               |                    |  |  |

| Description:     | and<br>is st<br>'1' th            | regi<br>orec        | contents of<br>ster 'f'. If 'o<br>I in the W<br>esult is sto<br>'f'. | d' is<br>regi | 0 the<br>ster. I | result<br>f 'd' is |  |  |

| Words:           | 1                                 |                     |                                                                      |               |                  |                    |  |  |

| Cycles:          | 1                                 |                     |                                                                      |               |                  |                    |  |  |

| Example:         | ADD                               | WF                  | TEMP_RE                                                              | EG,           | 0                |                    |  |  |

| Before Instr     | uctio                             | n                   |                                                                      |               |                  |                    |  |  |

| W                |                                   | =                   | 0x17                                                                 |               |                  |                    |  |  |

| TEMP_I           |                                   | 0xC2                |                                                                      |               |                  |                    |  |  |

| After Instruc    |                                   |                     |                                                                      |               |                  |                    |  |  |

| W                | = 0xD9                            |                     |                                                                      |               |                  |                    |  |  |

| TEMP_I           | REG                               | =                   | 0xC2                                                                 |               |                  |                    |  |  |

| ANDWF                                                         | AND W with f                                                                                                                                                              |  |  |  |  |  |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                       | [ label ] ANDWF f,d                                                                                                                                                       |  |  |  |  |  |

| Operands:                                                     | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                         |  |  |  |  |  |

| Operation:                                                    | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                        |  |  |  |  |  |

| Status Affected:                                              | Z                                                                                                                                                                         |  |  |  |  |  |

| Encoding:                                                     | 0001 01df ffff                                                                                                                                                            |  |  |  |  |  |

| Description:                                                  | The contents of the W register are AND'ed with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is '1' the result is stored back in register 'f'. |  |  |  |  |  |

| Words:                                                        | 1                                                                                                                                                                         |  |  |  |  |  |

| Cycles:                                                       | 1                                                                                                                                                                         |  |  |  |  |  |

| Example:                                                      | ANDWF TEMP_REG, 1                                                                                                                                                         |  |  |  |  |  |

| Before Instru<br>W<br>TEMP_I<br>After Instruct<br>W<br>TEMP_I | = 0x17 $REG = 0xC2$ $tion$ $= 0x17$                                                                                                                                       |  |  |  |  |  |

| ANDLW                                        | AND literal with W                                                                                                |  |  |  |  |  |  |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                      | [ label ] ANDLW k                                                                                                 |  |  |  |  |  |  |

| Operands:                                    | $0 \leq k \leq 255$                                                                                               |  |  |  |  |  |  |

| Operation:                                   | (W).AND. (k) $\rightarrow$ (W)                                                                                    |  |  |  |  |  |  |

| Status Affected:                             | Z                                                                                                                 |  |  |  |  |  |  |

| Encoding:                                    | 1110 kkkk kkkk                                                                                                    |  |  |  |  |  |  |

| Description:                                 | The contents of the W register are AND'ed with the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |  |

| Words:                                       | 1                                                                                                                 |  |  |  |  |  |  |

| Cycles:                                      | 1                                                                                                                 |  |  |  |  |  |  |

| Example:                                     | ANDLW H'5F'                                                                                                       |  |  |  |  |  |  |

| Before Instru<br>W =<br>After Instruc<br>W = | 0xA3                                                                                                              |  |  |  |  |  |  |

| BCF                      | Bit Clea                         | r f          |             |  |  |  |  |  |

|--------------------------|----------------------------------|--------------|-------------|--|--|--|--|--|

| Syntax:                  | [ label ] BCF f,b                |              |             |  |  |  |  |  |

| Operands:                | $0 \le f \le 31$ $0 \le b \le 7$ |              |             |  |  |  |  |  |

| Operation:               | $0 \rightarrow (f < b)$          | >)           |             |  |  |  |  |  |

| Status Affected:         | atus Affected: None              |              |             |  |  |  |  |  |

| Encoding:                | 0100                             | bbbf         | ffff        |  |  |  |  |  |

| Description:             | Bit 'b' in                       | register 'f' | is cleared. |  |  |  |  |  |

| Words:                   | 1                                |              |             |  |  |  |  |  |

| Cycles:                  | 1                                |              |             |  |  |  |  |  |

| Example:                 | BCF FLAG_REG, 7                  |              |             |  |  |  |  |  |

| Before Instru            |                                  | 0.07         |             |  |  |  |  |  |

| FLAG_R<br>After Instruct |                                  | 0xC7         |             |  |  |  |  |  |

| FLAG_R                   |                                  | 0x47         |             |  |  |  |  |  |

### 15.0 ELECTRICAL CHARACTERISTICS - PIC16C54A

Absolute Maximum Ratings(†) Storage temperature ——65°C to +150°C Voltage on all other pins with respect to Vss ......—0.6V to (VDD + 0.6V) Total power dissipation<sup>(1)</sup>......800 mW Input clamp current, IK (VI < 0 or VI > VDD)......±20 mA Output clamp current, IOK (VO < 0 or VO > VDD) ......±20 mA

Note 1: Power dissipation is calculated as follows: Pdis = VDD x {IDD -  $\Sigma$  IOH} +  $\Sigma$  {(VDD-VOH) x IOH} +  $\Sigma$ (VOL x IOL)

† NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### **Timing Parameter Symbology and Load Conditions** 15.5

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

Low

2. TppS

| Т    |                                         |                    |

|------|-----------------------------------------|--------------------|

| F    | Frequency                               | T Time             |

| Lowe | ercase letters (pp) and their meanings: |                    |

| рр   |                                         |                    |

| 2    | to                                      | mc MCLR            |

| ck   | CLKOUT                                  | osc oscillator     |

| су   | cycle time                              | os OSC1            |

| drt  | device reset timer                      | t0 T0CKI           |

| io   | I/O port                                | wdt watchdog timer |

| Uppe | ercase letters and their meanings:      |                    |

| S    |                                         |                    |

| F    | Fall                                    | P Period           |

| Н    | High                                    | R Rise             |

| I    | Invalid (Hi-impedance)                  | V Valid            |

Hi-impedance

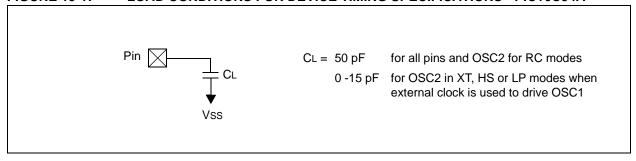

#### **FIGURE 15-1:** LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS - PIC16C54A

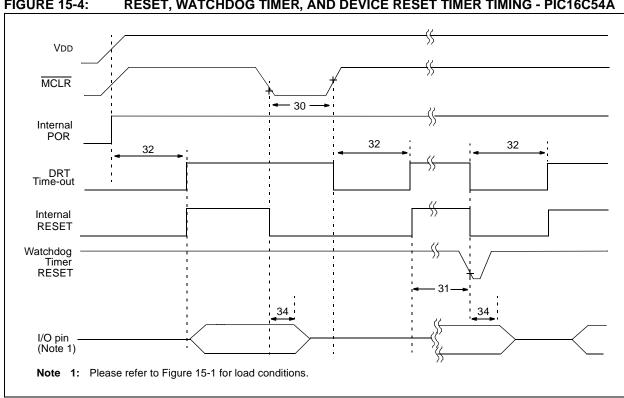

FIGURE 15-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16C54A

**TABLE 15-3:** RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16C54A

|                                                                           | Standard Operating Conditions (unless otherwise specified) |  |     |                     |        |           |            |                  |  |

|---------------------------------------------------------------------------|------------------------------------------------------------|--|-----|---------------------|--------|-----------|------------|------------------|--|

| Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |                                                            |  |     |                     |        |           |            | al               |  |

| AC Charac                                                                 | cteristics                                                 |  | -40 | $^{\circ}C \leq TA$ | ≤ +85° | C for inc | lustrial   |                  |  |

|                                                                           |                                                            |  | -20 | $^{\circ}C \leq TA$ | ≤ +85° | C for inc | lustrial - | · PIC16LV54A-02I |  |

|                                                                           | $-40^{\circ}$ C $\leq$ TA $\leq$ +125°C for extended       |  |     |                     |        |           |            |                  |  |

|                                                                           |                                                            |  |     |                     |        |           |            |                  |  |

| Param<br>No. | Symbol | Characteristic                                | Min       | Тур† | Max         | Units    | Conditions                                 |

|--------------|--------|-----------------------------------------------|-----------|------|-------------|----------|--------------------------------------------|

| 30           | TmcL   | MCLR Pulse Width (low)                        | 100*<br>1 | _    |             | ns<br>μs | VDD = 5.0V<br>VDD = 5.0V (PIC16LV54A only) |

| 31           | Twdt   | Watchdog Timer Time-out Period (No Prescaler) | 9.0*      | 18*  | 30*         | ms       | VDD = 5.0V (Comm)                          |

| 32           | TDRT   | Device Reset Timer Period                     | 9.0*      | 18*  | 30*         | ms       | VDD = 5.0V (Comm)                          |

| 34           | Tioz   | I/O Hi-impedance from MCLR Low                | _         | _    | 100*<br>1μs | ns<br>—  | (PIC16LV54A only)                          |

These parameters are characterized but not tested.

Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

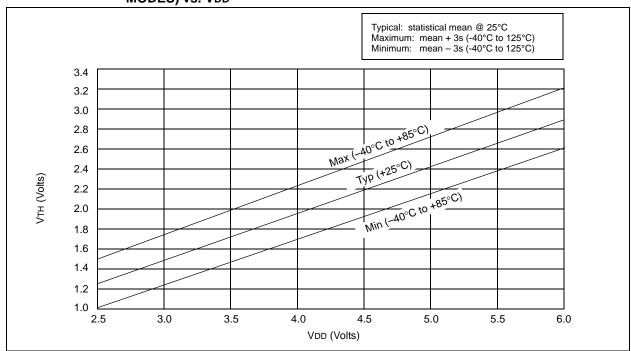

Typical: statistical mean @ 25°C Maximum: mean + 3s (-40°C to 125°C) Minimum: mean - 3s (-40°C to 125°C) 10000 1000 IDD (μA) 100 10 0.1 10 Freq (MHz)

**FIGURE 16-10:** TYPICAL IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 20 PF, 25°C)

**FIGURE 16-11: MAXIMUM IDD vs. FREQUENCY** (WDT DISABLED, RC MODE @ 20 PF, -40°C to +85°C)

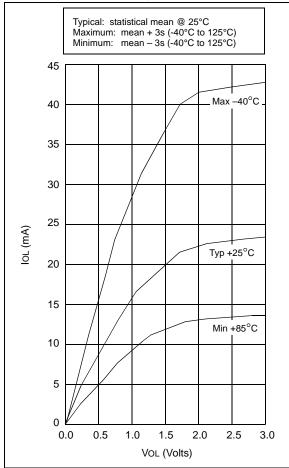

FIGURE 16-22: PORTA, B AND C IOL vs. Vol., VDD = 3V

TABLE 16-2: INPUT CAPACITANCE FOR PIC16C54A/C58A

| Pin         | Typical Capacitance (pF) |          |  |  |  |  |

|-------------|--------------------------|----------|--|--|--|--|

| PIII        | 18L PDIP                 | 18L SOIC |  |  |  |  |

| RA port     | 5.0                      | 4.3      |  |  |  |  |

| RB port     | 5.0                      | 4.3      |  |  |  |  |

| MCLR        | 17.0                     | 17.0     |  |  |  |  |

| OSC1        | 4.0                      | 3.5      |  |  |  |  |

| OSC2/CLKOUT | 4.3                      | 3.5      |  |  |  |  |

| T0CKI       | 3.2                      | 2.8      |  |  |  |  |

All capacitance values are typical at 25°C. A part-to-part variation of  $\pm 25\%$  (three standard deviations) should be taken into account.

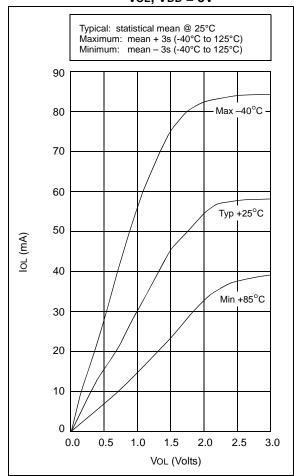

FIGURE 16-23: PORTA, B AND C IOL vs. Vol., VDD = 5V

17.3 DC Characteristics: PIC16C54C/C55A/C56A/C57C/C58B-04, 20 (Commercial, Industrial, Extended)

PIC16LC54C/LC55A/LC56A/LC57C/LC58B-04 (Commercial, Industrial)

PIC16CR54C/CR56A/CR57C/CR58B-04, 20 (Commercial, Industrial, Extended)

PIC16LCR54C/LCR56A/LCR57C/LCR58B-04 (Commercial, Industrial)

| DC CHARACTERISTICS |        |                                                                                                                   | Standard Operating Conditions (unless otherwise specified)  Operating Temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for extended |                   |                                                                  |                      |                                                                                                 |  |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                                                                                    | Min                                                                                                                                                                                                                                                    | Тур†              | Max                                                              | Units                | Conditions                                                                                      |  |

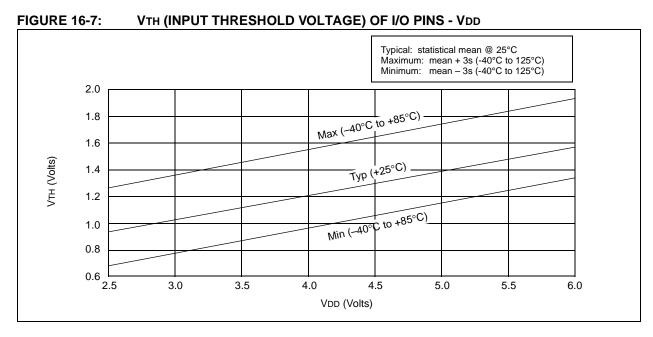

| D030               | VIL    | Input Low Voltage I/O Ports I/O Ports MCLR (Schmitt Trigger) T0CKI (Schmitt Trigger) OSC1 (Schmitt Trigger) OSC1  | Vss<br>Vss<br>Vss<br>Vss<br>Vss                                                                                                                                                                                                                        | _<br>_<br>_<br>_  | 0.8 V<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.3 VDD | V<br>V<br>V<br>V     | 4.5V <vdd 5.5v="" mode="" only<sup="" otherwise="" rc="" ≤="">(3) XT, HS and LP modes</vdd>     |  |

| D040               | ViH    | Input High Voltage I/O ports I/O ports MCLR (Schmitt Trigger) T0CKI (Schmitt Trigger) OSC1 (Schmitt Trigger) OSC1 | 2.0<br>0.25 Vdd+0.8<br>0.85 Vdd<br>0.85 Vdd<br>0.85 Vdd<br>0.7 Vdd                                                                                                                                                                                     | _<br>_<br>_<br>_  | VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD                           | V<br>V<br>V<br>V     | 4.5V < VDD ≤ 5.5V Otherwise  RC mode only <sup>(3)</sup> XT, HS and LP modes                    |  |

| D050               | VHYS   | Hysteresis of Schmitt<br>Trigger inputs                                                                           | 0.15 VDD*                                                                                                                                                                                                                                              | _                 | _                                                                | V                    |                                                                                                 |  |

| D060               | lı∟    | Input Leakage Current <sup>(1,2)</sup> I/O ports                                                                  | -1.0                                                                                                                                                                                                                                                   | 0.5               | +1.0                                                             | μА                   | For VDD ≤ 5.5V:<br>VSS ≤ VPIN ≤ VDD,<br>pin at hi-impedance                                     |  |

|                    |        | MCLR<br>MCLR<br>TOCKI<br>OSC1                                                                                     | -5.0<br>-3.0<br>-3.0                                                                                                                                                                                                                                   | 0.5<br>0.5<br>0.5 | +5.0<br>+3.0<br>+3.0<br>—                                        | μΑ<br>μΑ<br>μΑ<br>μΑ | VPIN = VSS +0.25V<br>VPIN = VDD<br>VSS ≤ VPIN ≤ VDD<br>VSS ≤ VPIN ≤ VDD,<br>XT, HS and LP modes |  |

| D080               | Vol    | Output Low Voltage I/O ports OSC2/CLKOUT                                                                          |                                                                                                                                                                                                                                                        | _                 | 0.6<br>0.6                                                       | V<br>V               | IOL = 8.7 mA, VDD = 4.5V<br>IOL = 1.6 mA, VDD = 4.5V,<br>RC mode only                           |  |

| D090               | Voн    | Output High Voltage <sup>(2)</sup> I/O ports OSC2/CLKOUT                                                          | VDD - 0.7<br>VDD - 0.7                                                                                                                                                                                                                                 | _                 |                                                                  | V<br>V               | IOH = -5.4 mA, VDD = 4.5V<br>IOH = -1.0 mA, VDD = 4.5V,<br>RC mode only                         |  |

These parameters are characterized but not tested.

<sup>†</sup> Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

<sup>2:</sup> Negative current is defined as coming out of the pin.

**<sup>3:</sup>** For the RC mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C5X be driven with external clock in RC mode.

## 19.3 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| T                                          |         |

|--------------------------------------------|---------|

| F Frequency                                | T Time  |

| Lowercase letters (pp) and their meanings: |         |

| рр                                         |         |

| 2 40                                       | ma MOLD |

| pp  |                    |                    |

|-----|--------------------|--------------------|

| 2   | to                 | mc MCLR            |

| ck  | CLKOUT             | osc oscillator     |

| су  | cycle time         | os OSC1            |

| drt | device reset timer | t0 T0CKI           |

| io  | I/O port           | wdt watchdog timer |

Uppercase letters and their meanings:

|   | opportation that their meanings. |   |              |  |  |  |  |  |

|---|----------------------------------|---|--------------|--|--|--|--|--|

| S |                                  |   |              |  |  |  |  |  |

| F | Fall                             | Р | Period       |  |  |  |  |  |

| Н | High                             | R | Rise         |  |  |  |  |  |

| 1 | Invalid (Hi-impedance)           | V | Valid        |  |  |  |  |  |

| L | Low                              | Z | Hi-impedance |  |  |  |  |  |

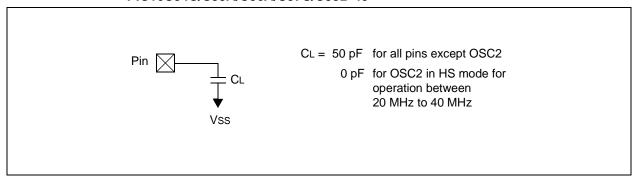

# FIGURE 19-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS - PIC16C54C/C55A/C56A/C57C/C58B-40

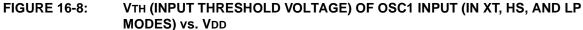

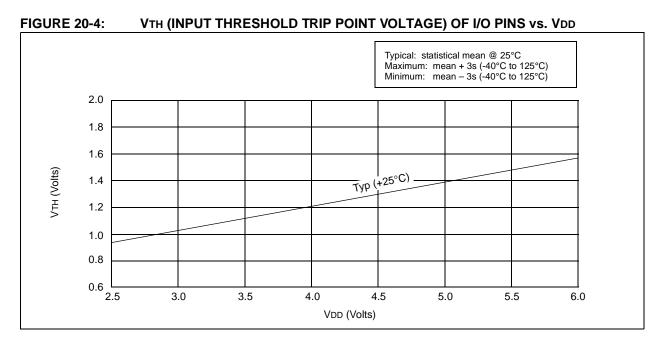

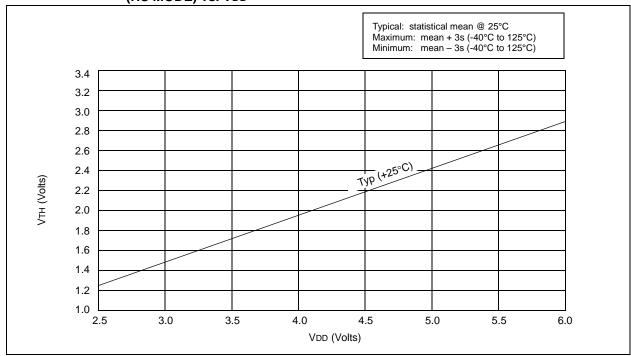

FIGURE 20-5: VTH (INPUT THRESHOLD TRIP POINT VOLTAGE) OF OSC1 INPUT (HS MODE) vs. Vdd

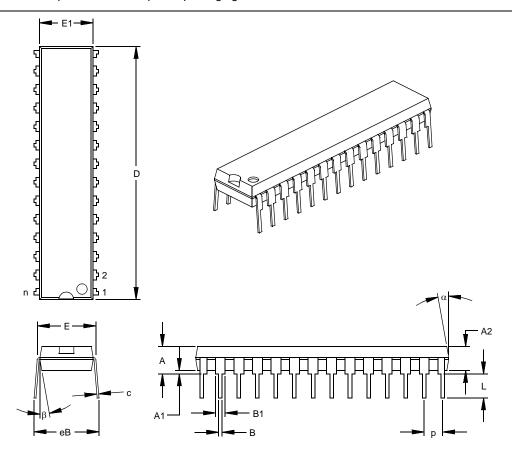

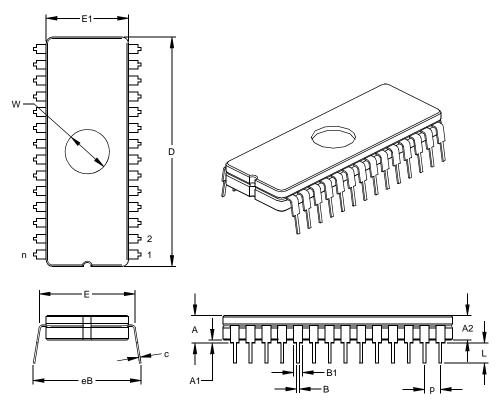

## 28-Lead Skinny Plastic Dual In-line (SP) - 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            |      | INCHES* |       | MILLIMETERS |       |       |       |

|----------------------------|------|---------|-------|-------------|-------|-------|-------|

| Dimension Limits           |      | MIN     | NOM   | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n    |         | 28    |             |       | 28    |       |

| Pitch                      | р    |         | .100  |             |       | 2.54  |       |

| Top to Seating Plane       | Α    | .140    | .150  | .160        | 3.56  | 3.81  | 4.06  |

| Molded Package Thickness   | A2   | .125    | .130  | .135        | 3.18  | 3.30  | 3.43  |

| Base to Seating Plane      | A1   | .015    |       |             | 0.38  |       |       |

| Shoulder to Shoulder Width | Е    | .300    | .310  | .325        | 7.62  | 7.87  | 8.26  |

| Molded Package Width       | E1   | .275    | .285  | .295        | 6.99  | 7.24  | 7.49  |

| Overall Length             | D    | 1.345   | 1.365 | 1.385       | 34.16 | 34.67 | 35.18 |

| Tip to Seating Plane       | L    | .125    | .130  | .135        | 3.18  | 3.30  | 3.43  |

| Lead Thickness             | С    | .008    | .012  | .015        | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1   | .040    | .053  | .065        | 1.02  | 1.33  | 1.65  |

| Lower Lead Width           | В    | .016    | .019  | .022        | 0.41  | 0.48  | 0.56  |

| Overall Row Spacing        | § eB | .320    | .350  | .430        | 8.13  | 8.89  | 10.92 |

| Mold Draft Angle Top       | α    | 5       | 10    | 15          | 5     | 10    | 15    |

| Mold Draft Angle Bottom    |      | 5       | 10    | 15          | 5     | 10    | 15    |

<sup>\*</sup> Controlling Parameter § Significant Characteristic

Notes:

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

<sup>.010&</sup>quot; (0.254mm) per side.

JEDEC Equivalent: MO-095

Drawing No. C04-070

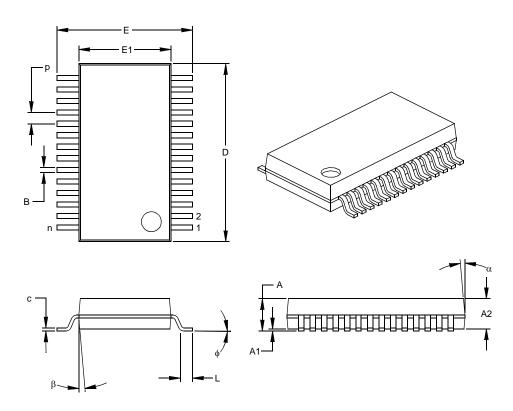

## 28-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          |    | INCHES |      | MILLIMETERS* |       |        |        |

|--------------------------|----|--------|------|--------------|-------|--------|--------|

| Dimension Limits         |    | MIN    | NOM  | MAX          | MIN   | NOM    | MAX    |

| Number of Pins           | n  |        | 28   |              |       | 28     |        |

| Pitch                    | р  |        | .026 |              |       | 0.65   |        |

| Overall Height           | Α  | .068   | .073 | .078         | 1.73  | 1.85   | 1.98   |

| Molded Package Thickness | A2 | .064   | .068 | .072         | 1.63  | 1.73   | 1.83   |

| Standoff §               | A1 | .002   | .006 | .010         | 0.05  | 0.15   | 0.25   |

| Overall Width            | Е  | .299   | .309 | .319         | 7.59  | 7.85   | 8.10   |

| Molded Package Width     | E1 | .201   | .207 | .212         | 5.11  | 5.25   | 5.38   |

| Overall Length           | D  | .396   | .402 | .407         | 10.06 | 10.20  | 10.34  |

| Foot Length              | L  | .022   | .030 | .037         | 0.56  | 0.75   | 0.94   |

| Lead Thickness           | С  | .004   | .007 | .010         | 0.10  | 0.18   | 0.25   |

| Foot Angle               | ф  | 0      | 4    | 8            | 0.00  | 101.60 | 203.20 |

| Lead Width               | В  | .010   | .013 | .015         | 0.25  | 0.32   | 0.38   |

| Mold Draft Angle Top     | α  | 0      | 5    | 10           | 0     | 5      | 10     |

| Mold Draft Angle Bottom  | β  | 0      | 5    | 10           | 0     | 5      | 10     |

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-150 Drawing No. C04-073

<sup>\*</sup> Controlling Parameter § Significant Characteristic

## 28-Lead Ceramic Dual In-line with Window (JW) - 600 mil (CERDIP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            |    | INCHES* |       | MILLIMETERS |       |       |       |

|----------------------------|----|---------|-------|-------------|-------|-------|-------|

| Dimension Limits           |    | MIN     | NOM   | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n  |         | 28    |             |       | 28    |       |

| Pitch                      | р  |         | .100  |             |       | 2.54  |       |

| Top to Seating Plane       | Α  | .195    | .210  | .225        | 4.95  | 5.33  | 5.72  |

| Ceramic Package Height     | A2 | .155    | .160  | .165        | 3.94  | 4.06  | 4.19  |

| Standoff                   | A1 | .015    | .038  | .060        | 0.38  | 0.95  | 1.52  |

| Shoulder to Shoulder Width | Е  | .595    | .600  | .625        | 15.11 | 15.24 | 15.88 |

| Ceramic Pkg. Width         | E1 | .514    | .520  | .526        | 13.06 | 13.21 | 13.36 |

| Overall Length             | D  | 1.430   | 1.460 | 1.490       | 36.32 | 37.08 | 37.85 |

| Tip to Seating Plane       | L  | .125    | .138  | .150        | 3.18  | 3.49  | 3.81  |

| Lead Thickness             | С  | .008    | .010  | .012        | 0.20  | 0.25  | 0.30  |

| Upper Lead Width           | B1 | .050    | .058  | .065        | 1.27  | 1.46  | 1.65  |

| Lower Lead Width           |    | .016    | .020  | .023        | 0.41  | 0.51  | 0.58  |

| Overall Row Spacing §      | еВ | .610    | .660  | .710        | 15.49 | 16.76 | 18.03 |

| Window Diameter W          |    | .270    | .280  | .290        | 6.86  | 7.11  | 7.37  |

<sup>\*</sup> Controlling Parameter § Significant Characteristic JEDEC Equivalent: MO-103 Drawing No. C04-013

## PIC16C5X

## APPENDIX A: COMPATIBILITY

To convert code written for PIC16CXX to PIC16C5X, the user should take the following steps:

- Check any CALL, GOTO or instructions that modify the PC to determine if any program memory page select operations (PA2, PA1, PA0 bits) need to be made.

- Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- Eliminate any special function register page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- Change RESET vector to proper value for processor used.

- 6. Remove any use of the ADDLW, RETURN and SUBLW instructions.

- 7. Rewrite any code segments that use interrupts.

### APPENDIX B: REVISION HISTORY

**Revision KE (January 2013)**

Added a note to each package outline drawing.