Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 20                                                                        |

| Program Memory Size        | 768B (512 x 12)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 24 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6.25V                                                                |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c55-xti-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

#### 3.1 **Clocking Scheme/Instruction** Cycle

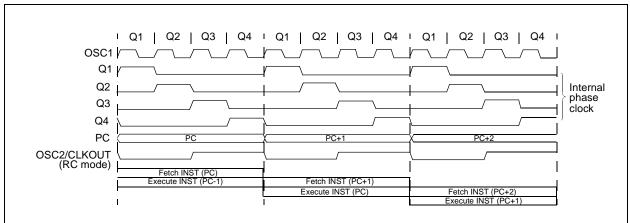

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter is incremented every Q1 and the instruction is fetched from program memory and latched into the instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-2 and Example 3-1.

#### 3.2 Instruction Flow/Pipelining

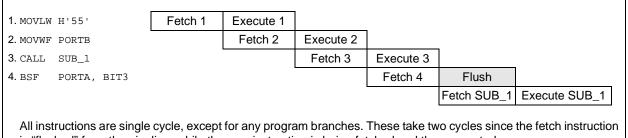

An Instruction Cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: **CLOCK/INSTRUCTION CYCLE**

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

#### 4.3 External Crystal Oscillator Circuit

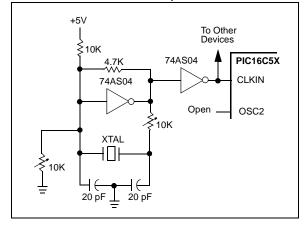

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A welldesigned crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

Figure 4-3 shows an implementation example of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

FIGURE 4-3: EXAMPLE OF EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT (USING XT, HS OR LP OSCILLATOR MODE)

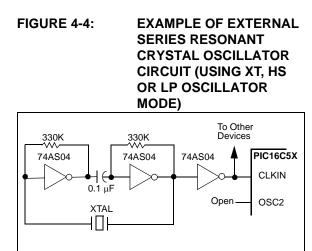

Figure 4-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### TABLE 5-3: RESET CONDITIONS FOR ALL REGISTERS

| Register                       | Address | Power-On Reset | MCLR or WDT Reset |

|--------------------------------|---------|----------------|-------------------|

| W                              | N/A     | XXXX XXXX      | uuuu uuuu         |

| TRIS                           | N/A     | 1111 1111      | 1111 1111         |

| OPTION                         | N/A     | 11 1111        | 11 1111           |

| INDF                           | 00h     | XXXX XXXX      | uuuu uuuu         |

| TMR0                           | 01h     | XXXX XXXX      | uuuu uuuu         |

| PCL                            | 02h     | 1111 1111      | 1111 1111         |

| STATUS                         | 03h     | 0001 1xxx      | 000q quuu         |

| FSR <sup>(1)</sup>             | 04h     | 1xxx xxxx      | luuu uuuu         |

| PORTA                          | 05h     | xxxx           | uuuu              |

| PORTB                          | 06h     | XXXX XXXX      | uuuu uuuu         |

| PORTC <sup>(2)</sup>           | 07h     | XXXX XXXX      | uuuu uuuu         |

| General Purpose Register Files | 07-7Fh  | XXXX XXXX      | սսսս սսսս         |

Legend: x = unknown u = unchanged - = unimplemented, read as '0'<math>q = see tables in Table 5-1 for possible values.

- Note 1: These values are valid for PIC16C57/CR57/CR58/CR58. For the PIC16C54/CR54/C55/C56/CR56, the value on RESET is 111x xxxx and for MCLR and WDT Reset, the value is 111u uuuu.

- **2:** General purpose register file on PIC16C54/CR54/C56/CR56/C58/CR58.

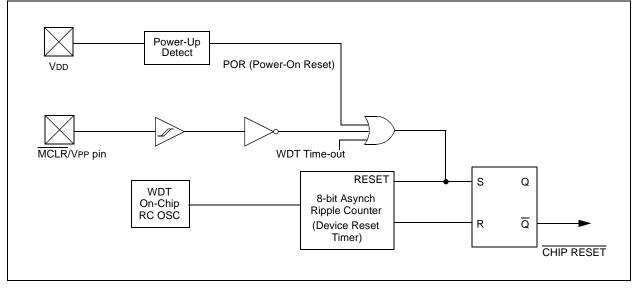

#### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 6.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions to control the operation of the device (Table 6-1).

The Special Registers can be classified into two sets. The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

| Address            | Name   | Bit 7    | Bit 6                                                                 | Bit 5       | Bit 4     | Bit 3    | Bit 2    | Bit 1     | Bit 0     | Value on<br>Power-on<br>Reset | Details<br>on Page |

|--------------------|--------|----------|-----------------------------------------------------------------------|-------------|-----------|----------|----------|-----------|-----------|-------------------------------|--------------------|

| N/A                | TRIS   | I/O Cont | rol Regis                                                             | ters (TRIS  | SA, TRIS  | B, TRISC | ;)       |           |           | 1111 1111                     | 35                 |

| N/A                | OPTION | Contains | s control b                                                           | oits to cor | figure Ti | mer0 and | Timer0/V | VDT pres  | caler     | 11 1111                       | 30                 |

| 00h                | INDF   | Uses co  | Uses contents of FSR to address data memory (not a physical register) |             |           |          | egister) | XXXX XXXX | 32        |                               |                    |

| 01h                | TMR0   | Timer0   | Timer0 Module Register                                                |             |           |          |          |           | XXXX XXXX | 38                            |                    |

| 02h <sup>(1)</sup> | PCL    | Low ord  | er 8 bits c                                                           | of PC       |           |          |          |           |           | 1111 1111                     | 31                 |

| 03h                | STATUS | PA2      | PA1                                                                   | PA0         | TO        | PD       | Z        | DC        | С         | 0001 1xxx                     | 29                 |

| 04h                | FSR    | Indirect | data merr                                                             | nory addre  | ess point | er       |          |           |           | 1xxx xxxx <b>(3)</b>          | 32                 |

| 05h                | PORTA  | —        | —                                                                     | —           | —         | RA3      | RA2      | RA1       | RA0       | xxxx                          | 35                 |

| 06h                | PORTB  | RB7      | RB6                                                                   | RB5         | RB4       | RB3      | RB2      | RB1       | RB0       | XXXX XXXX                     | 35                 |

| 07h <sup>(2)</sup> | PORTC  | RC7      | RC6                                                                   | RC5         | RC4       | RC3      | RC2      | RC1       | RC0       | XXXX XXXX                     | 35                 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0' (if applicable). Shaded cells = unimplemented or unused

**Note** 1: The upper byte of the Program Counter is not directly accessible. See Section 6.5 for an explanation of how to access these bits.

2: File address 07h is a General Purpose Register on the PIC16C54, PIC16CR54, PIC16C56, PIC16CR56, PIC16CR58 and PIC16CR58.

3: These values are valid for PIC16C57/CR57/C58/CR58. For the PIC16C54/CR54/C55/C56/CR56, the value on RESET is 111x xxxx and for MCLR and WDT Reset, the value is 111u uuuu.

## 6.5 Program Counter

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one, every instruction cycle, unless an instruction changes the PC.

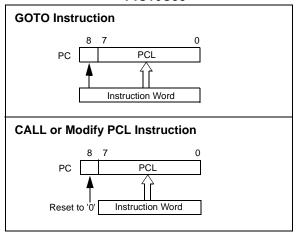

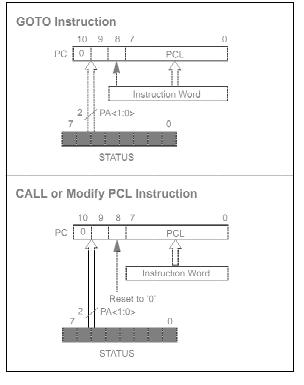

For a GOTO instruction, bits 8:0 of the PC are provided by the GOTO instruction word. The PC Latch (PCL) is mapped to PC<7:0> (Figure 6-7, Figure 6-8 and Figure 6-9).

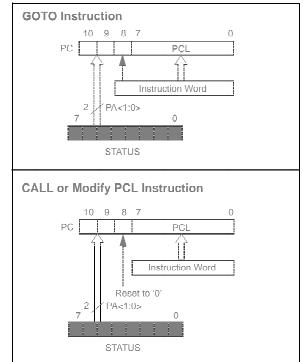

For the PIC16C56, PIC16CR56, PIC16C57, PIC16CR57, PIC16C757, PIC16C58 and PIC16CR58, a page number must be supplied as well. Bit5 and bit6 of the STA-TUS Register provide page information to bit9 and bit10 of the PC (Figure 6-8 and Figure 6-9).

For a CALL instruction, or any instruction where the PCL is the destination, bits 7:0 of the PC again are provided by the instruction word. However, PC<8> does not come from the instruction word, but is always cleared (Figure 6-7 and Figure 6-8).

Instructions where the PCL is the destination, or modify PCL instructions, include MOVWF PCL, ADDWF PCL, and BSF PCL, 5.

For the PIC16C56, PIC16CR56, PIC16C57, PIC16CR57, PIC16C58 and PIC16CR58, a page number again must be supplied. Bit5 and bit6 of the STA-TUS Register provide page information to bit9 and bit10 of the PC (Figure 6-8 and Figure 6-9).

| Note: | Because PC<8> is cleared in the CALL           |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|

|       | instruction, or any modify PCL instruction,    |  |  |  |  |

|       | all subroutine calls or computed jumps are     |  |  |  |  |

|       | limited to the first 256 locations of any pro- |  |  |  |  |

|       | gram memory page (512 words long).             |  |  |  |  |

#### FIGURE 6-7: LOADING OF PC BRANCH INSTRUCTIONS - PIC16C54, PIC16CR54, PIC16C55

#### FIGURE 6-8:

#### LOADING OF PC BRANCH INSTRUCTIONS - PIC16C56/PIC16CR56

FIGURE 6-9:

LOADING OF PC BRANCH INSTRUCTIONS - PIC16C57/PIC16CR57, AND PIC16C58/ PIC16CR58

| ADDWF                                                       | Add W                                                                                                                                                                         | and f                                                          |      |  |  |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------|--|--|

| Syntax:                                                     | [ label ] A                                                                                                                                                                   | [label]ADDWF f,d                                               |      |  |  |

| Operands:                                                   | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$ |      |  |  |

| Operation:                                                  | (W) + (f)                                                                                                                                                                     | $\rightarrow$ (dest)                                           |      |  |  |

| Status Affected:                                            | C, DC, Z                                                                                                                                                                      |                                                                |      |  |  |

| Encoding:                                                   | 0001                                                                                                                                                                          | 11df                                                           | ffff |  |  |

| Description:                                                | Add the contents of the W register<br>and register 'f'. If 'd' is 0 the result<br>is stored in the W register. If 'd' is<br>'1' the result is stored back in<br>register 'f'. |                                                                |      |  |  |

| Words:                                                      | 1                                                                                                                                                                             |                                                                |      |  |  |

| Cycles:                                                     | 1                                                                                                                                                                             |                                                                |      |  |  |

| Example:                                                    | ADDWF                                                                                                                                                                         | TEMP_RE                                                        | G, 0 |  |  |

| Before Instr<br>W<br>TEMP_I<br>After Instruc<br>W<br>TEMP_F | =<br>REG =<br>ction<br>=                                                                                                                                                      | 0x17<br>0xC2<br>0xD9<br>0xC2                                   |      |  |  |

| ANDWF                                                      | AND W with f                                                                                                                                                                            |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                    | [label] ANDWF f,d                                                                                                                                                                       |

| Operands:                                                  | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                          |

| Operation:                                                 | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                      |

| Status Affected:                                           | Z                                                                                                                                                                                       |

| Encoding:                                                  | 0001 01df ffff                                                                                                                                                                          |

| Description:                                               | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is 0<br>the result is stored in the W regis-<br>ter. If 'd' is '1' the result is stored<br>back in register 'f'. |

| Words:                                                     | 1                                                                                                                                                                                       |

| Cycles:                                                    | 1                                                                                                                                                                                       |

| Example:                                                   | ANDWF TEMP_REG, 1                                                                                                                                                                       |

| Before Instru<br>W<br>TEMP_<br>After Instruc<br>W<br>TEMP_ | = 0x17<br>REG = 0xC2<br>tion<br>= 0x17                                                                                                                                                  |

| ANDLW                                        | AND literal with W                                                                                                           |  |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                      | [ <i>label</i> ] ANDLW k                                                                                                     |  |  |  |

| Operands:                                    | $0 \le k \le 255$                                                                                                            |  |  |  |

| Operation:                                   | (W).AND. (k) $\rightarrow$ (W)                                                                                               |  |  |  |

| Status Affected:                             | Z                                                                                                                            |  |  |  |

| Encoding:                                    | 1110 kkkk kkkk                                                                                                               |  |  |  |

| Description:                                 | The contents of the W register are<br>AND'ed with the eight-bit literal 'k'.<br>The result is placed in the W regis-<br>ter. |  |  |  |

| Words:                                       | 1                                                                                                                            |  |  |  |

| Cycles:                                      | 1                                                                                                                            |  |  |  |

| Example:                                     | ANDLW H'5F'                                                                                                                  |  |  |  |

| Before Instru<br>W =<br>After Instruc<br>W = | 0xA3                                                                                                                         |  |  |  |

| BCF                                                        | Bit Clea               | r f                                                                |             |  |  |  |

|------------------------------------------------------------|------------------------|--------------------------------------------------------------------|-------------|--|--|--|

| Syntax:                                                    | [ label ]              | [label] BCF f,b                                                    |             |  |  |  |

| Operands:                                                  |                        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |             |  |  |  |

| Operation:                                                 | $0 \rightarrow (f < b$ | >)                                                                 |             |  |  |  |

| Status Affected:                                           | None                   |                                                                    |             |  |  |  |

| Encoding:                                                  | 0100                   | bbbf                                                               | ffff        |  |  |  |

| Description:                                               | Bit 'b' in             | register 'f'                                                       | is cleared. |  |  |  |

| Words:                                                     | 1                      |                                                                    |             |  |  |  |

| Cycles:                                                    | 1                      |                                                                    |             |  |  |  |

| Example:                                                   | BCF                    | FLAG_RE                                                            | IG, 7       |  |  |  |

| Before Instruction<br>FLAG_REG = 0xC7<br>After Instruction |                        |                                                                    |             |  |  |  |

| FLAG_F                                                     | REG =                  | 0x47                                                               |             |  |  |  |

| MOVWF               | Move W to f                      |

|---------------------|----------------------------------|

| Syntax:             | [ <i>label</i> ] MOVWF f         |

| Operands:           | $0 \leq f \leq 31$               |

| Operation:          | $(W) \rightarrow (f)$            |

| Status Affected:    | None                             |

| Encoding:           | 0000 001f ffff                   |

| Description:        | Move data from the W register to |

|                     | register 'f'.                    |

| Words:              | 1                                |

| Cycles:             | 1                                |

| Example:            | MOVWF TEMP_REG                   |

| W<br>After Instruct | REG = 0xFF $= 0x4F$              |

| NOP              | No Operation |        |      |  |

|------------------|--------------|--------|------|--|

| Syntax:          | [ label ]    | NOP    |      |  |

| Operands:        | None         |        |      |  |

| Operation:       | No opera     | ation  |      |  |

| Status Affected: | None         |        |      |  |

| Encoding:        | 0000         | 0000   | 0000 |  |

| Description:     | No opera     | ation. |      |  |

| Words:           | 1            |        |      |  |

| Cycles:          | 1            |        |      |  |

| Example:         | NOP          |        |      |  |

| OPTION             | Load Ol             |              | egister |  |

|--------------------|---------------------|--------------|---------|--|

| Syntax:            | [ label ]           | OPTIO        | N       |  |

| Operands:          | None                |              |         |  |

| Operation:         | $(W) \rightarrow C$ | <b>PTION</b> |         |  |

| Status Affected:   | None                |              |         |  |

| Encoding:          | 0000                | 0000         | 0010    |  |

| Description:       |                     | tent of the  | 0       |  |

| Words:             | 1                   |              |         |  |

| Cycles:            | 1                   |              |         |  |

| Example            | OPTION              |              |         |  |

| Before Instruction |                     |              |         |  |

| W                  | •                   | 07           |         |  |

| After Instructi    | -                   |              |         |  |

| OPTION             | = 0x                | 07           |         |  |

| RETLW               | Return with Literal in W                                                                                                                                                            |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:             | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:           | $0 \leq k \leq 255$                                                                                                                                                                 |

| Operation:          | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |

| Status Affected:    | None                                                                                                                                                                                |

| Encoding:           | 1000 kkkk kkkk                                                                                                                                                                      |

| Description:        | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address). This<br>is a two-cycle instruction. |

| Words:              | 1                                                                                                                                                                                   |

| Cycles:             | 2                                                                                                                                                                                   |

| Example:            | CALL TABLE ;W contains<br>;table offset<br>;value.<br>• ;W now has table<br>• ;value.                                                                                               |

| TABLE               | <pre>ADDWF PC ;W = offset RETLW k1 ;Begin table RETLW k2 ;</pre>                                                                                                                    |

| Before Instru       |                                                                                                                                                                                     |

| W<br>After Instruct | = 0x07                                                                                                                                                                              |

| After Instruct<br>W | = value of k8                                                                                                                                                                       |

# PIC16C5X

| RLF                                                  | F Rotate Left f through Carry                                                                                                                                                                                                 |  |  |  |  |  |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                              | [ <i>label</i> ] RLF f,d                                                                                                                                                                                                      |  |  |  |  |  |

| Operands:                                            | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                    |  |  |  |  |  |

| Operation:                                           | See description below                                                                                                                                                                                                         |  |  |  |  |  |

| Status Affected:                                     | С                                                                                                                                                                                                                             |  |  |  |  |  |

| Encoding:                                            | 0011 01df ffff                                                                                                                                                                                                                |  |  |  |  |  |

| Description:                                         | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag (STATUS<0>). If 'd'<br>is 0 the result is placed in the W<br>register. If 'd' is 1 the result is<br>stored back in<br>register 'f'. |  |  |  |  |  |

| Words:                                               | 1                                                                                                                                                                                                                             |  |  |  |  |  |

| Cycles:                                              | 1                                                                                                                                                                                                                             |  |  |  |  |  |

| Example:                                             | RLF REG1,0                                                                                                                                                                                                                    |  |  |  |  |  |

| Before Instru<br>REG1<br>C<br>After Instruct<br>REG1 | = 1110 0110<br>= 0<br>tion                                                                                                                                                                                                    |  |  |  |  |  |

| W<br>C                                               | = 1110 0110<br>= 1100 1100<br>= 1                                                                                                                                                                                             |  |  |  |  |  |

| RRF                                         | Rotate Right f through Carry                                                                                                                                                                                                   |  |  |  |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                     | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                       |  |  |  |

| Operands:                                   | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                     |  |  |  |

| Operation:                                  | See description below                                                                                                                                                                                                          |  |  |  |

| Status Affected:                            | С                                                                                                                                                                                                                              |  |  |  |

| Encoding:                                   | 0011 00df ffff                                                                                                                                                                                                                 |  |  |  |

| Description:                                | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag (STATUS<0>). If 'd'<br>is 0 the result is placed in the W<br>register. If 'd' is 1 the result is<br>placed back in<br>register 'f'. |  |  |  |

| Words:                                      | 1                                                                                                                                                                                                                              |  |  |  |

| Cycles:                                     | 1                                                                                                                                                                                                                              |  |  |  |

| Example:                                    | RRF REG1,0                                                                                                                                                                                                                     |  |  |  |

| Before Instru<br>REG1<br>C<br>After Instruc | $= 1110 0110 \\ = 0$                                                                                                                                                                                                           |  |  |  |

| REG1<br>W<br>C                              | = 1110 0110<br>= 0111 0011<br>= 0                                                                                                                                                                                              |  |  |  |

| SLEEP            | Enter SLEEP Mode                                                                                                                                                                                                                                   |       |      |   |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|---|--|

| Syntax:          | [label]                                                                                                                                                                                                                                            | SLEEP |      |   |  |

| Operands:        | None                                                                                                                                                                                                                                               |       |      |   |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT; \\ 0 \rightarrow WDT \ prescaler; \ if \ assigned \\ 1 \rightarrow \overline{TO}; \\ 0 \rightarrow \overline{PD} \end{array}$                                                                               |       |      |   |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                                             |       |      | _ |  |

| Encoding:        | 0000                                                                                                                                                                                                                                               | 0000  | 0011 |   |  |

| Description:     | Time-out status bit (TO) is set. The<br>power-down status bit (PD) is<br>cleared. The WDT and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See section on SLEEP for more<br>details. |       |      |   |  |

| Words:           | 1                                                                                                                                                                                                                                                  |       |      |   |  |

| Cycles:          | 1                                                                                                                                                                                                                                                  |       |      |   |  |

| Example:         | SLEEP                                                                                                                                                                                                                                              |       |      |   |  |

## 11.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK™ Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC<sup>™</sup> In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup>1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

#### 11.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup>-based application that contains:

- An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- A project manager

- Customizable toolbar and key mapping

- A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the cost-effective simulator to a full-featured emulator with minimal retraining.

## 11.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCUs.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

#### 11.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

## 12.6 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. Tp | 2. TppS                                 |        |                |  |  |  |  |

|-------|-----------------------------------------|--------|----------------|--|--|--|--|

| Т     |                                         |        |                |  |  |  |  |

| F     | Frequency                               | T Time |                |  |  |  |  |

| Lowe  | ercase letters (pp) and their meanings: |        |                |  |  |  |  |

| рр    |                                         |        |                |  |  |  |  |

| 2     | to                                      | mc     | MCLR           |  |  |  |  |

| ck    | CLKOUT                                  | OSC    | oscillator     |  |  |  |  |

| су    | cycle time                              | OS     | OSC1           |  |  |  |  |

| drt   | device reset timer                      | t0     | ТОСКІ          |  |  |  |  |

| io    | I/O port                                | wdt    | watchdog timer |  |  |  |  |

| Uppe  | ercase letters and their meanings:      |        |                |  |  |  |  |

| S     |                                         |        |                |  |  |  |  |

| F     | Fall                                    | Р      | Period         |  |  |  |  |

| н     | High                                    | R      | Rise           |  |  |  |  |

| I.    | Invalid (Hi-impedance)                  | V      | Valid          |  |  |  |  |

| L     | Low                                     | Ζ      | Hi-impedance   |  |  |  |  |

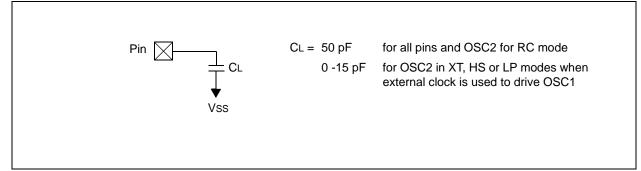

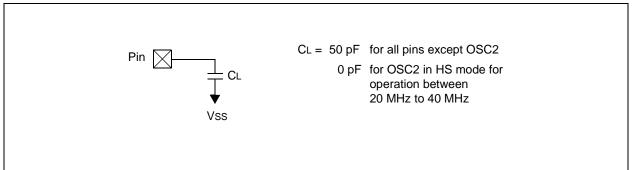

#### FIGURE 12-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS - PIC16C54/55/56/57

# 15.0 ELECTRICAL CHARACTERISTICS - PIC16C54A

| Absolute Maximum Ratings <sup>(†)</sup>                                                                  |                                      |

|----------------------------------------------------------------------------------------------------------|--------------------------------------|

| Ambient temperature under bias                                                                           | –55°C to +125°C                      |

| Storage temperature                                                                                      | –65°C to +150°C                      |

| Voltage on VDD with respect to Vss                                                                       | 0 to +7.5V                           |

| Voltage on MCLR with respect to Vss                                                                      | 0 to +14V                            |

| Voltage on all other pins with respect to Vss                                                            | –0.6V to (VDD + 0.6V)                |

| Total power dissipation <sup>(1)</sup>                                                                   | 800 mW                               |

| Max. current out of Vss pin                                                                              | 150 mA                               |

| Max. current into Vod pin                                                                                | 100 mA                               |

| Max. current into an input pin (T0CKI only)                                                              | ±500 μA                              |

| Input clamp current, Iik (VI < 0 or VI > VDD)                                                            | ±20 mA                               |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                           |                                      |

| Max. output current sunk by any I/O pin                                                                  | 25 mA                                |

| Max. output current sourced by any I/O pin                                                               | 20 mA                                |

| Max. output current sourced by a single I/O port (PORTA or B)                                            | 50 mA                                |

| Max. output current sunk by a single I/O port (PORTA or B)                                               | 50 mA                                |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VD | D-VOH) X IOH} + $\Sigma$ (VOL X IOL) |

† NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

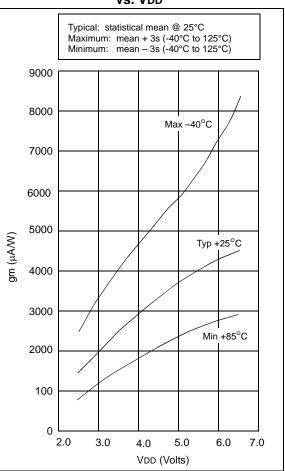

#### FIGURE 16-17: TRANSCONDUCTANCE (gm) OF HS OSCILLATOR vs. VDD

## 17.4 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. Tp | 2. TppS                                 |                    |  |  |  |  |

|-------|-----------------------------------------|--------------------|--|--|--|--|

| Т     |                                         |                    |  |  |  |  |

| F     | Frequency                               | T Time             |  |  |  |  |

| Lowe  | ercase letters (pp) and their meanings: |                    |  |  |  |  |

| рр    |                                         |                    |  |  |  |  |

| 2     | to                                      | mc MCLR            |  |  |  |  |

| ck    | CLKOUT                                  | osc oscillator     |  |  |  |  |

| су    | cycle time                              | os OSC1            |  |  |  |  |

| drt   | device reset timer                      | t0 T0CKI           |  |  |  |  |

| io    | I/O port                                | wdt watchdog timer |  |  |  |  |

| Uppe  | ercase letters and their meanings:      |                    |  |  |  |  |

| S     |                                         |                    |  |  |  |  |

| F     | Fall                                    | P Period           |  |  |  |  |

| н     | High                                    | R Rise             |  |  |  |  |

| T     | Invalid (Hi-impedance)                  | V Valid            |  |  |  |  |

| L     | Low                                     | Z Hi-impedance     |  |  |  |  |

#### FIGURE 17-5: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS -PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/C58B/CR58B-04, 20

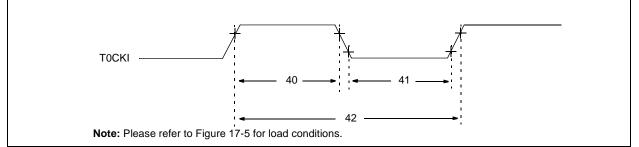

#### **FIGURE 17-9:** TIMER0 CLOCK TIMINGS - PIC16C5X, PIC16CR5X

#### **TABLE 17-4:** TIMER0 CLOCK REQUIREMENTS - PIC16C5X, PIC16CR5X

| ļ            | AC Chara | Standard Operatin<br>Operating Temperat  |                              | TA ≤ +7<br>TA ≤ +8 | 0°C fo<br>5°C fo | r comm<br>r indust | nercial<br>trial                                               |

|--------------|----------|------------------------------------------|------------------------------|--------------------|------------------|--------------------|----------------------------------------------------------------|

| Param<br>No. | Symbol   | Characteristic                           | Min                          | Тур†               | Max              | Units              | Conditions                                                     |

| 40           | Tt0H     | T0CKI High Pulse Width<br>- No Prescaler | 0.5 Tcy + 20*                |                    | _                | ns                 |                                                                |

|              |          | - With Prescaler                         | 10*                          | _                  | —                | ns                 |                                                                |

| 41           | TtOL     | T0CKI Low Pulse Width<br>- No Prescaler  | 0.5 Tcy + 20*                | _                  | _                | ns                 |                                                                |

|              |          | - With Prescaler                         | 10*                          | _                  | _                | ns                 |                                                                |

| 42           | Tt0P     | T0CKI Period                             | 20 or <u>Tcy + 40</u> *<br>N | _                  | _                | ns                 | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

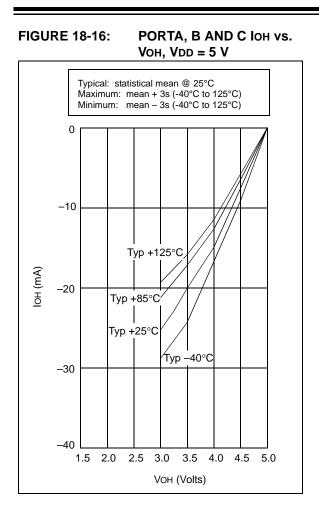

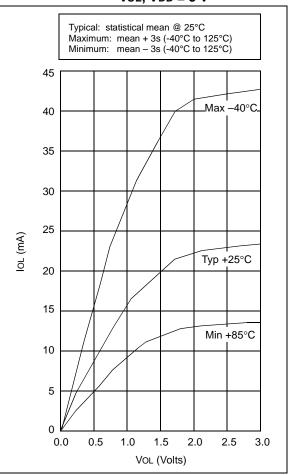

#### FIGURE 18-17: PORTA, B AND C IOL vs. Vol, VDD = 3 V

## **19.3 Timing Parameter Symbology and Load Conditions**

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. Tp | 2. TppS                                 |                    |  |  |  |  |

|-------|-----------------------------------------|--------------------|--|--|--|--|

| Т     |                                         |                    |  |  |  |  |

| F     | Frequency                               | T Time             |  |  |  |  |

| Lowe  | ercase letters (pp) and their meanings: |                    |  |  |  |  |

| рр    |                                         |                    |  |  |  |  |

| 2     | to                                      | mc MCLR            |  |  |  |  |

| ck    | CLKOUT                                  | osc oscillator     |  |  |  |  |

| су    | cycle time                              | os OSC1            |  |  |  |  |

| drt   | device reset timer                      | t0 T0CKI           |  |  |  |  |

| io    | I/O port                                | wdt watchdog timer |  |  |  |  |

| Uppe  | ercase letters and their meanings:      |                    |  |  |  |  |

| S     |                                         |                    |  |  |  |  |

| F     | Fall                                    | P Period           |  |  |  |  |

| н     | High                                    | R Rise             |  |  |  |  |

| Ι     | Invalid (Hi-impedance)                  | V Valid            |  |  |  |  |

| L     | Low                                     | Z Hi-impedance     |  |  |  |  |

#### FIGURE 19-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS -PIC16C54C/C55A/C56A/C57C/C58B-40

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                            | - <u>xx</u>                                                                                                                                                                                                                                                                   | Ť                                                                                                                                                             | <u>/xx</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <u>xxx</u> | Exa                          | nples                                                                                       | S:                                                                                                                                                                                                                                                           |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                              | Frequency<br>Range/OSC<br>Type           PIC16C54           PIC16C54A           PIC16C54C           PIC16C55A           PIC16C55A           PIC16C55A           PIC16C56A           PIC16C56A           PIC16C57C           PIC16C57C           PIC16C58B           PIC16C58B | Temperature<br>Range                                                                                                                                          | $\begin{array}{c} -(2) \\ \lambda_{T}(2) \\ (2) \\ C_{T}(2) \\ C_{T}(2) \\ 2) \\ -(2) \\ -(2) \\ \lambda_{T}(2) \\ 2) \\ -(2) \\ C_{T}(2) \\ C_{T}(2) \\ -(2) \\ C_{T}(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ -(2) \\ $ | Pattern    | a)<br>b)<br>c)<br>d)<br>Note | PDIP<br>QTP<br>PIC16<br>packa<br>PIC16<br>cial te<br>dard '<br>PIC1<br>temp<br>MHz,<br>#123 | C = normal voltage range<br>LC = extended                                                                                                                                                                                                                    |

| Frequency Range/<br>Oscillator Type | 04 200 KHz (LI<br>10 10 MHz (HS<br>20 20 MHz (HS<br>40 40 MHz (HS<br>b <sup>(4)</sup> No oscillato<br>*RC/LP/XT/HS a<br>-02 is available for<br>-04/10/20 options                                                                                                             | Crystal<br>ystal/Resonator<br>Crystal<br>P) or 2 MHz (XT an<br>P) or 4 MHz (XT an<br>conly)<br>conly)<br>conly)<br>r type for JW packa<br>re for 16C54/55/56/ | nd RC)<br>ages <sup>(3)</sup><br>/57 devices on<br>all other device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | S          |                              | 3:                                                                                          | T = in tape and reel - SOIC and SSOP<br>packages only<br>JW Devices are UV erasable and can be<br>programmed to any device configura-<br>tion. JW Devices meet the electrical<br>requirements of each oscillator type,<br>including LC devices.<br>b = Blank |

| Temperature Range                   | $b^{(4)} = 0^{\circ}C$<br>$I = -40^{\circ}C$<br>$E = -40^{\circ}C$                                                                                                                                                                                                            | to +85°C                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |                              |                                                                                             |                                                                                                                                                                                                                                                              |

| Package                             | JW = 28-pin<br>DIP <sup>(3)</sup><br>P = 28-pin<br>SO = 300 m<br>SS = 209 m<br>SP = 28-pin                                                                                                                                                                                    | Waffle Pack<br>600 mil/18-pin 300<br>600 mil/18-pin 300<br>il SOIC<br>il SSOP<br>300 mil Skinny PD<br>for additional packa                                    | 0 mil PDIP<br>DIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |                              |                                                                                             |                                                                                                                                                                                                                                                              |

| Pattern                             |                                                                                                                                                                                                                                                                               | I code (factory spe<br>lank for OTP and W                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |                              |                                                                                             |                                                                                                                                                                                                                                                              |

#### Sales and Support

#### **Data Sheets**