Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 20                                                                         |

| Program Memory Size        | 768B (512 x 12)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 25 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c55at-20-so |

# 6.7 Indirect Data Addressing; INDF and FSR Registers

The INDF Register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR Register (FSR is a *pointer*). This is indirect addressing.

### **EXAMPLE 6-1: INDIRECT ADDRESSING**

- Register file 08 contains the value 10h

- Register file 09 contains the value 0Ah

- · Load the value 08 into the FSR Register

- A read of the INDF Register will return the value of 10h

- Increment the value of the FSR Register by one (FSR = 09h)

- A read of the INDF register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF Register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 6-2.

# EXAMPLE 6-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | MOVLW | H'10' | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ; to RAM             |

| NEXT     | CLRF  | INDF  | ;clear INDF Register |

|          | INCF  | FSR,F | ;inc pointer         |

|          | BTFSC | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;NO, clear next      |

| CONTINUE |       |       |                      |

|          |       |       | :YES, continue       |

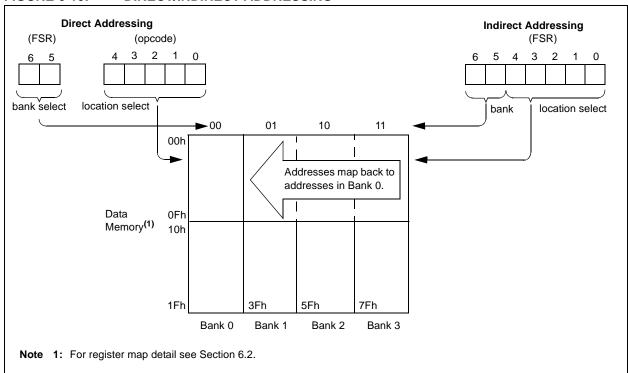

The FSR is either a 5-bit (PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56) or 7-bit (PIC16C57, PIC16CR57, PIC16CR58, PIC16CR58) wide register. It is used in conjunction with the INDF Register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56:** These do not use banking. FSR<6:5> bits are unimplemented and read as '1's.

**PIC16C57, PIC16CR57, PIC16C58, PIC16CR58:** FSR<6:5> are the bank select bits and are used to select the bank to be addressed (00 = bank 0, 01 = bank 1, 10 = bank 2, 11 = bank 3).

### FIGURE 6-10: DIRECT/INDIRECT ADDRESSING

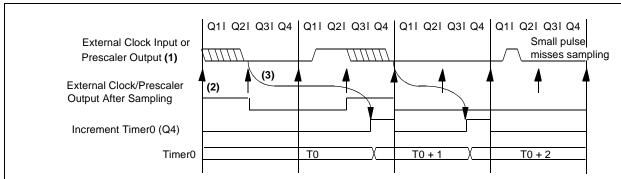

# 8.1 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

# 8.1.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 8-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

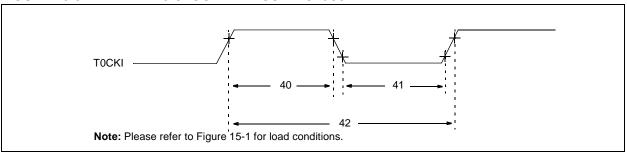

When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for T0CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T0CKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 8.1.2 TIMERO INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 8-5 shows the delay from the external clock edge to the timer incrementing.

FIGURE 8-5: TIMERO TIMING WITH EXTERNAL CLOCK

- Note 1: External clock if no prescaler selected, prescaler output otherwise.

- 2: The arrows indicate the points in time where sampling occurs.

- 3: Delay from clock input change to Timer0 increment is 3Tosc to 7Tosc (duration of Q = Tosc). Therefore, the error in measuring the interval between two edges on Timer0 input =  $\pm$  4Tosc max.

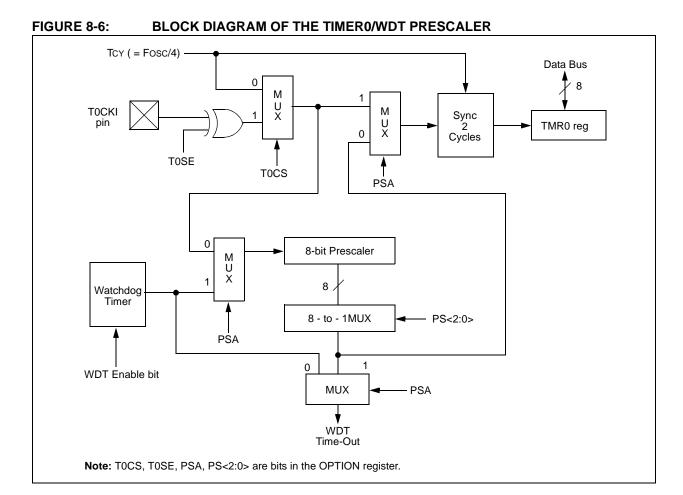

#### 8.2 **Prescaler**

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer (WDT), respectively (Section 9.2.1). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT, but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the WDT, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1,x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a RESET, the prescaler contains all '0's.

### 8.2.1 SWITCHING PRESCALER **ASSIGNMENT**

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 8-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

### **EXAMPLE 8-1: CHANGING PRESCALER** (TIMER0→WDT)

CLRWDT ;Clear WDT ;Clear TMR0 & Prescaler CLRF TMR0 MOVIW B'00xx1111' ;Last 3 instructions in this example OPTION ; are required only if ;desired CLRWDT ;PS<2:0> are 000 or ;001 MOVLW B'00xx1xxx' ;Set Prescaler to OPTION ;desired WDT rate

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 8-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

### **EXAMPLE 8-2: CHANGING PRESCALER** (WDT→TIMER0)

CLRWDT ;Clear WDT and ;prescaler ;Select TMR0, new MOVLW B'xxxx0xxx' ;prescale value and ; clock source

OPTION

# 9.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits that deal with the needs of real-time applications. The PIC16C5X family of microcontrollers have a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These features are:

- Oscillator Selection (Section 4.0)

- RESET (Section 5.0)

- Power-On Reset (Section 5.1)

- Device Reset Timer (Section 5.2)

- Watchdog Timer (WDT) (Section 9.2)

- SLEEP (Section 9.3)

- Code protection (Section 9.4)

- ID locations (Section 9.5)

The PIC16C5X Family has a Watchdog Timer which can be shut off only through configuration bit WDTE. It runs off of its own RC oscillator for added reliability. There is an 18 ms delay provided by the Device Reset Timer (DRT), intended to keep the chip in RESET until the crystal oscillator is stable. With this timer on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake up from SLEEP through external RESET or through a Watchdog Timer time-out. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

# PIC16C5X

TABLE 10-2: INSTRUCTION SET SUMMARY

| Mnemo     | nic,    | Description                  | Cycles           | 12-l | Bit Opc | ode  | Status                         | Notes |

|-----------|---------|------------------------------|------------------|------|---------|------|--------------------------------|-------|

| Opera     | nds     | Description                  | Cycles           | MSb  |         | LSb  | Affected                       | Notes |

| ADDWF     | f,d     | Add W and f                  | 1                | 0001 | 11df    | ffff | C,DC,Z                         | 1,2,4 |

| ANDWF     | f,d     | AND W with f                 | 1                | 0001 | 01df    | ffff | Z                              | 2,4   |

| CLRF      | f       | Clear f                      | 1                | 0000 | 011f    | ffff | Z                              | 4     |

| CLRW      | _       | Clear W                      | 1                | 0000 | 0100    | 0000 | Z                              |       |

| COMF      | f, d    | Complement f                 | 1                | 0010 | 01df    | ffff | Z                              |       |

| DECF      | f, d    | Decrement f                  | 1                | 0000 | 11df    | ffff | Z                              | 2,4   |

| DECFSZ    | f, d    | Decrement f, Skip if 0       | 1(2)             | 0010 | 11df    | ffff | None                           | 2,4   |

| INCF      | f, d    | Increment f                  | 1                | 0010 | 10df    | ffff | Z                              | 2,4   |

| INCFSZ    | f, d    | Increment f, Skip if 0       | 1 <sup>(2)</sup> | 0011 | 11df    | ffff | None                           | 2,4   |

| IORWF     | f, d    | Inclusive OR W with f        | 1                | 0001 | 00df    | ffff | Z                              | 2,4   |

| MOVF      | f, d    | Move f                       | 1                | 0010 | 00df    | ffff | Z                              | 2,4   |

| MOVWF     | f       | Move W to f                  | 1                | 0000 | 001f    | ffff | None                           | 1,4   |

| NOP       | _       | No Operation                 | 1                | 0000 | 0000    | 0000 | None                           |       |

| RLF       | f, d    | Rotate left f through Carry  | 1                | 0011 | 01df    | ffff | С                              | 2,4   |

| RRF       | f, d    | Rotate right f through Carry | 1                | 0011 | 00df    | ffff | С                              | 2,4   |

| SUBWF     | f, d    | Subtract W from f            | 1                | 0000 | 10df    | ffff | C,DC,Z                         | 1,2,4 |

| SWAPF     | f, d    | Swap f                       | 1                | 0011 | 10df    | ffff | None                           | 2,4   |

| XORWF     | f, d    | Exclusive OR W with f        | 1                | 0001 | 10df    | ffff | Z                              | 2,4   |

| BIT-ORIEN | TED FIL | E REGISTER OPERATIONS        |                  |      |         |      |                                |       |

| BCF       | f, b    | Bit Clear f                  | 1                | 0100 | bbbf    | ffff | None                           | 2,4   |

| BSF       | f, b    | Bit Set f                    | 1                | 0101 | bbbf    | ffff | None                           | 2,4   |

| BTFSC     | f, b    | Bit Test f, Skip if Clear    | 1 (2)            | 0110 | bbbf    | ffff | None                           |       |

| BTFSS     | f, b    | Bit Test f, Skip if Set      | 1 (2)            | 0111 | bbbf    | ffff | None                           |       |

| LITERAL A | ND CON  | ITROL OPERATIONS             |                  | •    |         |      |                                |       |

| ANDLW     | k       | AND literal with W           | 1                | 1110 | kkkk    | kkkk | Ζ                              |       |

| CALL      | k       | Call subroutine              | 2                | 1001 | kkkk    | kkkk | None                           | 1     |

| CLRWDT    | k       | Clear Watchdog Timer         | 1                | 0000 | 0000    | 0100 | TO, PD                         |       |

| GOTO      | k       | Unconditional branch         | 2                | 101k | kkkk    | kkkk | None                           |       |

| IORLW     | k       | Inclusive OR Literal with W  | 1                | 1101 | kkkk    | kkkk | Z                              |       |

| MOVLW     | k       | Move Literal to W            | 1                | 1100 | kkkk    | kkkk | None                           |       |

| OPTION    | k       | Load OPTION register         | 1                | 0000 | 0000    | 0010 | None                           |       |

| RETLW     | k       | Return, place Literal in W   | 2                | 1000 | kkkk    | kkkk | None                           |       |

| SLEEP     | _       | Go into standby mode         | 1                | 0000 | 0000    | 0011 | $\overline{TO}, \overline{PD}$ |       |

| TRIS      | f       | Load TRIS register           | 1                | 0000 | 0000    | Offf | None                           | 3     |

| XORLW     | k       | Exclusive OR Literal to W    | 1                | 1111 | kkkk    | kkkk | Z                              |       |

- **Note 1:** The 9th bit of the program counter will be forced to a '0' by any instruction that writes to the PC except for GOTO (see Section 6.5 for more on program counter).

- 2: When an I/O register is modified as a function of itself (e.g. MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

- 3: The instruction TRIS f, where f = 5, 6 or 7 causes the contents of the W register to be written to the tristate latches of PORTA, B or C respectively. A '1' forces the pin to a hi-impedance state and disables the output buffers.

- **4:** If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared (if assigned to TMR0).

| CALL                                                                                                                                | Subroutine Call                                                                                                                                             | CLRW                                                                 | Clear W                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                                             | [ label ] CALL k                                                                                                                                            | Syntax:                                                              | [ label ] CLRW                                                                                                                                                                                                                                                                                                                                                                                       |

| Operands:                                                                                                                           | $0 \leq k \leq 255$                                                                                                                                         | Operands:                                                            | None                                                                                                                                                                                                                                                                                                                                                                                                 |

| Operation:                                                                                                                          | (PC) + 1→ TOS;<br>k → PC<7:0>;                                                                                                                              | Operation:                                                           | $00h \rightarrow (W);$ $1 \rightarrow Z$                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                     | (STATUS<6:5>) → PC<10:9>;<br>0 → PC<8>                                                                                                                      | Status Affected:                                                     | Z                                                                                                                                                                                                                                                                                                                                                                                                    |

| Status Affected:                                                                                                                    | None                                                                                                                                                        | Encoding:                                                            | 0000 0100 0000                                                                                                                                                                                                                                                                                                                                                                                       |

| Encoding:                                                                                                                           | 1001 kkkk kkkk                                                                                                                                              | Description:                                                         | The W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                      |

| Description:                                                                                                                        | Subroutine call. First, return address (PC+1) is pushed onto the                                                                                            | Words:                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                     | stack. The eight bit immediate                                                                                                                              | Cycles:                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                     | address is loaded into PC bits                                                                                                                              | Example:                                                             | CLRW                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                     | <7:0>. The upper bits PC<10:9> are loaded from STATUS<6:5>, PC<8> is cleared. CALL is a two-cycle instruction.                                              | After Instruc                                                        | = 0x5A                                                                                                                                                                                                                                                                                                                                                                                               |

| Words:                                                                                                                              | 1                                                                                                                                                           | Z =                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                      |

| Cycles:                                                                                                                             | 2                                                                                                                                                           |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                      |

| _                                                                                                                                   |                                                                                                                                                             |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                      |

| Example:                                                                                                                            | HERE CALL THERE                                                                                                                                             | CLRWDT                                                               | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                 |

| Before Instr                                                                                                                        | uction                                                                                                                                                      | CLRWDT                                                               | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                     | uction<br>= address (HERE)                                                                                                                                  | Syntax:                                                              | [ label ] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                     |

| Before Instr<br>PC =<br>After Instruc<br>PC =<br>TOS =                                                                              | uction = address (HERE) ction = address (THERE) = address (HERE + 1)                                                                                        | _                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                      |

| Before Instr<br>PC =<br>After Instruc<br>PC =                                                                                       | uction = address (HERE) ction = address (THERE) = address (HERE + 1)  Clear f                                                                               | Syntax: Operands:                                                    | [ label ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{10};$                                                                                                                                                                                                                                                                 |

| Before Instruction PC = After Instruction PC = TOS = CLRF Syntax:                                                                   | uction = address (HERE) ction = address (THERE) = address (HERE + 1)  Clear f  [ label ] CLRF f                                                             | Syntax: Operands: Operation:                                         | [ label ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow \frac{WD}{T}$ prescaler (if assigned);<br>$1 \rightarrow \frac{TO}{PD};$<br>$1 \rightarrow \overline{PD}$                                                                                                                                                                                                                       |

| Before Instruction PC = After Instruction PC = TOS =  CLRF  Syntax: Operands:                                                       | uction = address (HERE) ction = address (THERE) = address (HERE + 1)  Clear f  [ label ] CLRF f  0 \le f \le 31                                             | Syntax: Operands: Operation: Status Affected:                        | [ label ] CLRWDT<br>None<br>$00h \rightarrow WDT$ ;<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO}$ ;<br>$1 \rightarrow \overline{PD}$<br>$\overline{TO}$ , $\overline{PD}$                                                                                                                                                                                         |

| Before Instruction PC = After Instruction PC = TOS = CLRF Syntax:                                                                   | uction = address (HERE) ction = address (THERE) = address (HERE + 1)  Clear f  [ $label$ ] CLRF f $0 \le f \le 31$ $00h \rightarrow (f)$ ;                  | Syntax: Operands: Operation: Status Affected: Encoding:              | [ label ] CLRWDT  None $00h \rightarrow WDT;$ $0 \rightarrow WDT$ prescaler (if assigned); $1 \rightarrow \overline{TO};$ $1 \rightarrow \overline{PD}$ $\overline{TO}, \overline{PD}$ $0000  0000  0100$ The CLRWDT instruction resets the WDT. It also resets the prescaler, if                                                                                                                    |

| Before Instruction PC = After Instruction PC = TOS =  CLRF  Syntax: Operands: Operation:  Status Affected:                          | uction = address (HERE) ction = address (THERE) = address (HERE + 1)  Clear f  [ label ] CLRF f $0 \le f \le 31$ $00h \rightarrow (f);$ $1 \rightarrow Z$ Z | Syntax: Operands: Operation: Status Affected: Encoding:              | [ label ] CLRWDT  None $00h \rightarrow WDT;$ $0 \rightarrow WDT$ prescaler (if assigned); $1 \rightarrow \overline{TO};$ $1 \rightarrow \overline{PD}$ $\overline{TO}, \overline{PD}$ $0000  0000  0100$ The CLRWDT instruction resets the                                                                                                                                                          |

| Before Instruction PC = After Instruction PC = TOS = TOS =  CLRF  Syntax: Operands: Operands: Operation: Status Affected: Encoding: | uction = address (HERE) etion = address (THERE) = address (HERE + 1)  Clear f  [ label ] CLRF f $0 \le f \le 31$ $00h \rightarrow (f);$ $1 \rightarrow Z$ Z | Syntax: Operands: Operation: Status Affected: Encoding:              | [ label ] CLRWDT  None $00h \rightarrow WDT$ ; $0 \rightarrow WDT$ prescaler (if assigned); $1 \rightarrow \overline{10}$ ; $1 \rightarrow \overline{PD}$ $\overline{TO}$ , $\overline{PD}$ $0000  0000  0100$ The CLRWDT instruction resets the WDT. It also resets the prescaler, if the prescaler is assigned to the WDT and not Timer0. Status bits                                              |

| Before Instruction PC = After Instruction PC = TOS =  CLRF  Syntax: Operands: Operation:  Status Affected:                          | uction = address (HERE) ction = address (THERE) = address (HERE + 1)  Clear f  [ label ] CLRF f $0 \le f \le 31$ $00h \rightarrow (f);$ $1 \rightarrow Z$ Z | Syntax: Operands: Operation: Status Affected: Encoding: Description: | [ label ] CLRWDT  None $00h \rightarrow WDT$ ; $0 \rightarrow WDT$ prescaler (if assigned); $1 \rightarrow \overline{TO}$ ; $1 \rightarrow \overline{PD}$ $\overline{TO}$ , $\overline{PD}$ $0000  0000  0100$ The CLRWDT instruction resets the WDT. It also resets the prescaler, if the prescaler is assigned to the WDT and not Timer0. Status bits $\overline{TO}$ and $\overline{PD}$ are set. |

Before Instruction

After Instruction

TO

$\overline{\mathsf{PD}}$

WDT counter =

WDT counter =

WDT prescaler =

0x00

0

1

1

Before Instruction

After Instruction

Ζ

FLAG\_REG =

FLAG\_REG =

CLRF

FLAG\_REG

0x5A

0x00

1

Cycles:

Example:

| GOTO                    | Unconditional Branch                                                                                                                                                        |  |  |  |  |  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:                 | [ label ] GOTO k                                                                                                                                                            |  |  |  |  |  |  |  |

| Operands:               | $0 \leq k \leq 511$                                                                                                                                                         |  |  |  |  |  |  |  |

| Operation:              | $k \rightarrow PC<8:0>$ ;<br>STATUS<6:5> $\rightarrow PC<10:9>$                                                                                                             |  |  |  |  |  |  |  |

| Status Affected:        | : None                                                                                                                                                                      |  |  |  |  |  |  |  |

| Encoding:               | 101k kkkk kkkk                                                                                                                                                              |  |  |  |  |  |  |  |

| Description:            | GOTO is an unconditional branch. The 9-bit immediate value is loaded into PC bits <8:0>. The upper bits of PC are loaded from STATUS<6:5>. GOTO is a two-cycle instruction. |  |  |  |  |  |  |  |

| Words:                  | 1                                                                                                                                                                           |  |  |  |  |  |  |  |

| Cycles:                 | 2                                                                                                                                                                           |  |  |  |  |  |  |  |

| Example:                | GOTO THERE                                                                                                                                                                  |  |  |  |  |  |  |  |

| After Instructi<br>PC = | After Instruction                                                                                                                                                           |  |  |  |  |  |  |  |

| INCF                 | Increment f                                                                                                                                              |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:              | [ label ] INCF f,d                                                                                                                                       |

| Operands:            | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                        |

| Operation:           | $(f) + 1 \rightarrow (dest)$                                                                                                                             |

| Status Affected:     | Z                                                                                                                                                        |

| Encoding:            | 0010 10df ffff                                                                                                                                           |

| Description:         | The contents of register 'f' are incremented. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'. |

| Words:               | 1                                                                                                                                                        |

| Cycles:              | 1                                                                                                                                                        |

| Example:             | INCF CNT, 1                                                                                                                                              |

| Before Instru<br>CNT | uction<br>= 0xFF                                                                                                                                         |

| Z                    | = 0                                                                                                                                                      |

| After Instruc        |                                                                                                                                                          |

| CNT                  | = 0x00                                                                                                                                                   |

| Z                    | = 1                                                                                                                                                      |

| INCFSZ              | Increment f, Skip if 0                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:             | [ label ] INCFSZ f,d                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Operands:           | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Operation:          | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Status Affected:    | None                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Encoding:           | 0011 11df ffff                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Description:        | The contents of register 'f' are incremented. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'.  If the result is 0, then the next instruction, which is already fetched, is discarded and a NOP is executed instead making it a two-cycle instruction. |  |  |  |  |  |

| Words:              | 1                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Cycles:             | 1(2)                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Example:            | HERE INCFSZ CNT, 1 GOTO LOOP                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|                     | CONTINUE •                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                     | •                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Doforo Inotru       | • ation                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Before Instru<br>PC | = address (HERE)                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| After Instruct      | , ,                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| CNT                 | = CNT + 1;                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| if CNT              | = 0,                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| PC<br>if CNT        | <pre>= address (CONTINUE); ≠ 0,</pre>                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| PC                  | = address (HERE +1)                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|                     |                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

## 11.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can also link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian is a librarian for precompiled code to be used with the MPLINK object linker. When a routine from a library is called from another source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. The MPLIB object librarian manages the creation and modification of library files.

The MPLINK object linker features include:

- Integration with MPASM assembler and MPLAB C17 and MPLAB C18 C compilers.

- Allows all memory areas to be defined as sections to provide link-time flexibility.

The MPLIB object librarian features include:

- Easier linking because single libraries can be included instead of many smaller files.

- Helps keep code maintainable by grouping related modules together.

- Allows libraries to be created and modules to be added, listed, replaced, deleted or extracted.

## 11.5 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC-hosted environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user-defined key press, to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and the MPLAB C18 C compilers and the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent multiproject software development tool.

# 11.6 MPLAB ICE High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB ICE universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers (MCUs). Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE in-circuit emulator system has been designed as a real-time emulation system, with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft® Windows environment were chosen to best make these features available to you, the end user.

## 11.7 ICEPIC In-Circuit Emulator

The ICEPIC low cost, in-circuit emulator is a solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X and PIC16CXXX families of 8-bit One-Time-Programmable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules, or daughter boards. The emulator is capable of emulating without target application circuitry being present.

TABLE 13-1: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16CR54A

AC Characteristics Standard Operating Conditions (unless otherwise specified)

Operating Temperature  $0^{\circ}\text{C} \leq \text{Ta} \leq +70^{\circ}\text{C}$  for commercial  $-40^{\circ}\text{C} \leq \text{Ta} \leq +85^{\circ}\text{C}$  for industrial  $-40^{\circ}\text{C} \leq \text{Ta} \leq +125^{\circ}\text{C}$  for extended

| Param<br>No. | Symbol     | Characteristic                        | Min  | Тур†   | Max    | Units | Conditions       |

|--------------|------------|---------------------------------------|------|--------|--------|-------|------------------|

| 1            | Tosc       | External CLKIN Period <sup>(1)</sup>  | 250  |        | _      | ns    | XT osc mode      |

|              |            |                                       | 250  | _      | _      | ns    | HS osc mode (04) |

|              |            |                                       | 100  | _      | _      | ns    | HS osc mode (10) |

|              |            |                                       | 50   | _      | _      | ns    | HS osc mode (20) |

|              |            |                                       | 5.0  | _      | _      | μS    | LP osc mode      |

|              |            | Oscillator Period <sup>(1)</sup>      | 250  | _      | _      | ns    | RC osc mode      |

|              |            |                                       | 250  | _      | 10,000 | ns    | XT osc mode      |

|              |            |                                       | 250  | _      | 250    | ns    | HS osc mode (04) |

|              |            |                                       | 100  | _      | 250    | ns    | HS osc mode (10) |

|              |            |                                       | 50   | _      | 250    | ns    | HS osc mode (20) |

|              |            |                                       | 5.0  | _      | 200    | μS    | LP osc mode      |

| 2            | Tcy        | Instruction Cycle Time <sup>(2)</sup> | _    | 4/Fosc | _      | _     |                  |

| 3            | TosL, TosH | Clock in (OSC1) Low or High           | 50*  | _      | _      | ns    | XT oscillator    |

|              |            | Time                                  | 20*  | _      | _      | ns    | HS oscillator    |

|              |            |                                       | 2.0* | _      | _      | μS    | LP oscillator    |

| 4            | TosR, TosF | Clock in (OSC1) Rise or Fall          | _    | _      | 25*    | ns    | XT oscillator    |

|              |            | Time                                  | _    | _      | 25*    | ns    | HS oscillator    |

|              |            |                                       |      |        | 50*    | ns    | LP oscillator    |

- \* These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: Instruction cycle period (TCY) equals four times the input oscillator time base period.

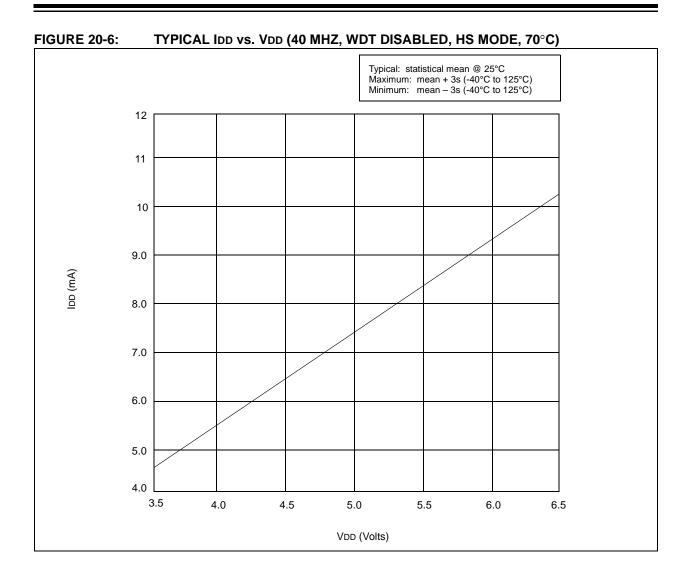

## 14.0 DEVICE CHARACTERIZATION - PIC16C54A

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean –  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

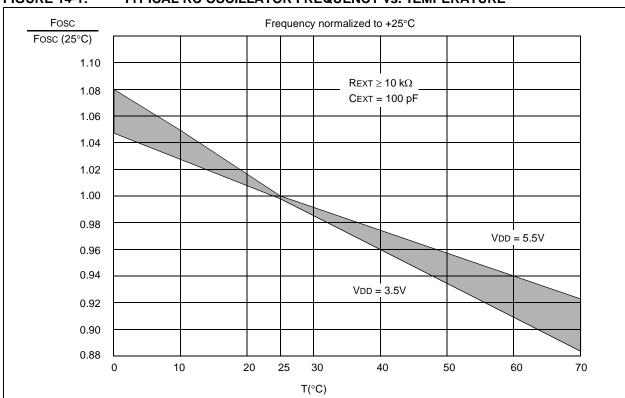

FIGURE 14-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

TABLE 14-1: RC OSCILLATOR FREQUENCIES

| Сехт   | REXT | Average<br>Fosc @ 5 V, 25°C |       |  |  |  |

|--------|------|-----------------------------|-------|--|--|--|

| 20 pF  | 3.3K | 5 MHz                       | ± 27% |  |  |  |

|        | 5K   | 3.8 MHz                     | ± 21% |  |  |  |

|        | 10K  | 2.2 MHz                     | ± 21% |  |  |  |

|        | 100K | 262 kHz                     | ± 31% |  |  |  |

| 100 pF | 3.3K | 1.6 MHz                     | ± 13% |  |  |  |

|        | 5K   | 1.2 MHz                     | ± 13% |  |  |  |

|        | 10K  | 684 kHz                     | ± 18% |  |  |  |

|        | 100K | 71 kHz                      | ± 25% |  |  |  |

| 300 pF | 3.3K | 660 kHz                     | ± 10% |  |  |  |

|        | 5.0K | 484 kHz                     | ± 14% |  |  |  |

|        | 10K  | 267 kHz                     | ± 15% |  |  |  |

|        | 100K | 29 kHz                      | ± 19% |  |  |  |

The frequencies are measured on DIP packages.

The percentage variation indicated here is part-to-part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviations from the average value for VDD = 5V.

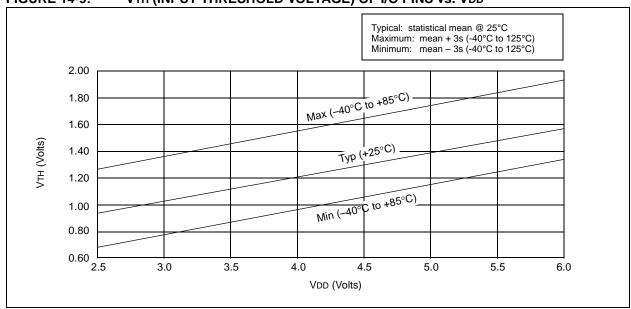

FIGURE 14-9: VTH (INPUT THRESHOLD VOLTAGE) OF I/O PINS vs. VDD

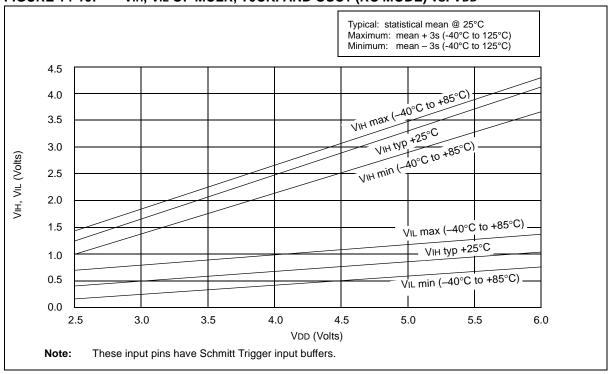

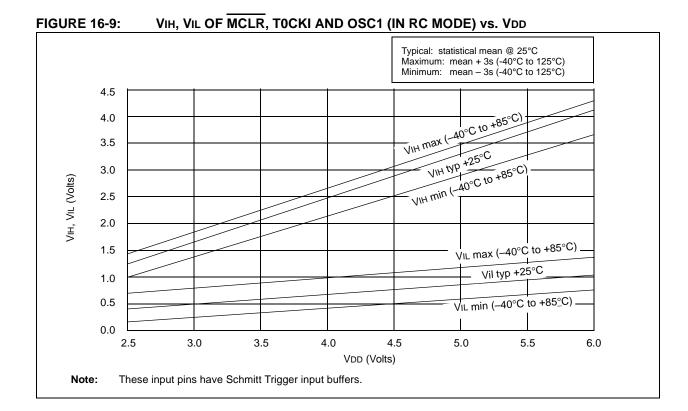

FIGURE 14-10: VIH, VIL OF MCLR, TOCKI AND OSC1 (RC MODE) vs. VDD

# 15.2 DC Characteristics: PIC16C54A-04E, 10E, 20E (Extended) PIC16LC54A-04E (Extended)

| PIC16L<br>(Extend |                      |                                               |                                                                                                                                                           |      |              | $-40$ °C $\leq$ TA $\leq$ +125°C for extended |                                                               |  |

|-------------------|----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|-----------------------------------------------|---------------------------------------------------------------|--|

| PIC16C<br>(Extend | <b>54A-04E,</b> ded) | 10E, 20E                                      | Standard Operating Conditions (unless otherwise specified Operating Temperature $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |      |              |                                               |                                                               |  |

| Param<br>No.      | Symbol               | Characteristic                                | Min                                                                                                                                                       | Тур† | Conditions   |                                               |                                                               |  |

|                   | VDD                  | Supply Voltage                                |                                                                                                                                                           |      |              |                                               |                                                               |  |

| D001              |                      | PIC16LC54A                                    | 3.0<br>2.5                                                                                                                                                |      | 6.25<br>6.25 | -                                             | XT and RC modes<br>LP mode                                    |  |

| D001A             |                      | PIC16C54A                                     | 3.5<br>4.5                                                                                                                                                | _    | 5.5<br>5.5   | V                                             | RC and XT modes<br>HS mode                                    |  |

| D002              | Vdr                  | RAM Data Retention Voltage <sup>(1)</sup>     | _                                                                                                                                                         | 1.5* | _            | V                                             | Device in SLEEP mode                                          |  |

| D003              | VPOR                 | VDD Start Voltage to ensure<br>Power-on Reset | _                                                                                                                                                         | Vss  | _            | V                                             | See Section 5.1 for details on Power-on Reset                 |  |

| D004              | SVDD                 | VDD Rise Rate to ensure<br>Power-on Reset     | 0.05*                                                                                                                                                     | _    | _            | V/ms                                          | See Section 5.1 for details on<br>Power-on Reset              |  |

|                   | IDD                  | Supply Current <sup>(2)</sup>                 |                                                                                                                                                           |      |              |                                               |                                                               |  |

| D010              |                      | PIC16LC54A                                    | _                                                                                                                                                         | 0.5  | 25           | mA                                            | Fosc = 4.0 MHz, VDD = 5.5V, RC <sup>(3)</sup> and XT modes    |  |

|                   |                      |                                               | _                                                                                                                                                         | 11   | 27           | μА                                            | FOSC = 32 kHz, VDD = 2.5V,<br>LP mode, Commercial             |  |

|                   |                      |                                               | _                                                                                                                                                         | 11   | 35           | μА                                            | FOSC = 32 kHz, VDD = 2.5V,<br>LP mode, Industrial             |  |

|                   |                      |                                               | _                                                                                                                                                         | 11   | 37           | μА                                            | FOSC = 32 kHz, VDD = 2.5V,<br>LP mode, Extended               |  |

| D010A             |                      | PIC16C54A                                     | _                                                                                                                                                         | 1.8  | 3.3          | mA                                            | Fosc = 4.0 MHz, VDD = 5.5V,<br>RC <sup>(3)</sup> and XT modes |  |

|                   |                      |                                               | _                                                                                                                                                         | 4.8  | 10           | mA                                            | FOSC = 10 MHz, VDD = 5.5V,<br>HS mode                         |  |

|                   |                      |                                               | _                                                                                                                                                         | 9.0  | 20           | mA                                            | FOSC = 20 MHz, VDD = 5.5V,<br>HS mode                         |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- \* These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, ToCKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in  $k\Omega$ .

#### **FIGURE 15-5: TIMERO CLOCK TIMINGS - PIC16C54A**

| TABLE 15-4: | TIMERO CLO   | CK REQUIREMENTS - PI  | C16C54A                                                         |

|-------------|--------------|-----------------------|-----------------------------------------------------------------|

|             |              | Standard Operating Co | nditions (unless otherwise specified)                           |

|             |              | Operating Temperature | $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial             |

| AC Cha      | racteristics |                       | $-40$ °C $\leq$ TA $\leq$ +85°C for industrial                  |

|             |              |                       | $-20$ °C $\leq$ TA $\leq$ +85°C for industrial - PIC16LV54A-02I |

|             |              |                       | $-40$ °C $\leq$ TA $\leq$ +125°C for extended                   |

|             |              |                       |                                                                 |

| Param<br>No. | Symbol | Characteristic         | Min                     | Тур† | Max | Units | Conditions            |

|--------------|--------|------------------------|-------------------------|------|-----|-------|-----------------------|

| 40           | Tt0H   | T0CKI High Pulse Width |                         |      |     |       |                       |

|              |        | - No Prescaler         | 0.5 Tcy + 20*           | _    | _   | ns    |                       |

|              |        | - With Prescaler       | 10*                     | -    | _   | ns    |                       |

| 41           | TtOL   | T0CKI Low Pulse Width  |                         |      |     |       |                       |

|              |        | - No Prescaler         | 0.5 Tcy + 20*           | _    | _   | ns    |                       |

|              |        | - With Prescaler       | 10*                     | -    | _   | ns    |                       |

| 42           | Tt0P   | T0CKI Period           | 20 or <u>Tcy + 40</u> * | _    | _   | ns    | Whichever is greater. |

|              |        |                        | N                       |      |     |       | N = Prescale Value    |

|              |        |                        |                         |      |     |       | (1, 2, 4,, 256)       |

These parameters are characterized but not tested.

<sup>†</sup> Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

© 1997-2013 Microchip Technology Inc.

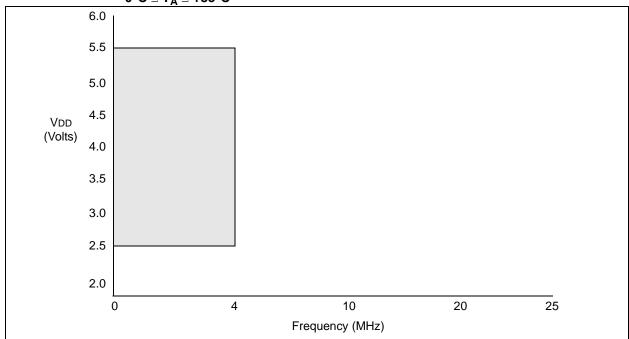

FIGURE 17-3: PIC16LC54C/55A/56A/57C/58B VOLTAGE-FREQUENCY GRAPH,  $0^{\circ}C \leq T_{A} \leq +85^{\circ}C$

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

2: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

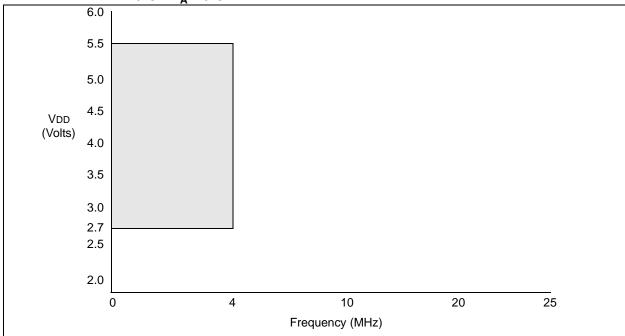

FIGURE 17-4: PIC16LC54C/55A/56A/57C/58B VOLTAGE-FREQUENCY GRAPH,  $-40^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 0^{\circ}\text{C}$

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

2: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

17.1 DC Characteristics:PIC16C54C/C55A/C56A/C57C/C58B-04, 20 (Commercial, Industrial)

PIC16LC54C/LC55A/LC56A/LC57C/LC58B-04 (Commercial, Industrial)

PIC16CR54C/CR56A/CR57C/CR58B-04, 20 (Commercial, Industrial)

PIC16LCR54C/LCR56A/LCR57C/LCR58B-04 (Commercial, Industrial)

| PIC16LC5X PIC16LCR5X (Commercial, Industrial)  PIC16C5X PIC16CR5X (Commercial, Industrial) |        |                                               | Operating Temperature |             |                   |             | ions (unless otherwise specified)<br>$0^{\circ}\text{C} \leq \text{TA} \leq +70^{\circ}\text{C}$ for commercial<br>$-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for industrial<br>ions (unless otherwise specified)<br>$0^{\circ}\text{C} \leq \text{TA} \leq +70^{\circ}\text{C}$ for commercial<br>$-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for industrial |

|--------------------------------------------------------------------------------------------|--------|-----------------------------------------------|-----------------------|-------------|-------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                                                                               | Symbol | Characteristic/Device                         | Min                   | Тур†        | Max               | Units       | Conditions                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                            | VDD    | Supply Voltage                                |                       |             |                   |             |                                                                                                                                                                                                                                                                                                                                                                                                    |

| D001                                                                                       |        | PIC16LC5X                                     | 2.5<br>2.7<br>2.5     | _<br>_<br>_ | 5.5<br>5.5<br>5.5 | V<br>V<br>V | -40°C ≤ TA ≤ + 85°C, 16LCR5X<br>-40°C ≤ TA ≤ 0°C, 16LC5X<br>0°C ≤ TA ≤ + 85°C 16LC5X                                                                                                                                                                                                                                                                                                               |

| D001A                                                                                      |        | PIC16C5X                                      | 3.0<br>4.5            | _           | 5.5<br>5.5        | V<br>V      | RC, XT, LP and HS mode<br>from 0 - 10 MHz<br>from 10 - 20 MHz                                                                                                                                                                                                                                                                                                                                      |

| D002                                                                                       | VDR    | RAM Data Retention Voltage <sup>(1)</sup>     | _                     | 1.5*        | _                 | V           | Device in SLEEP mode                                                                                                                                                                                                                                                                                                                                                                               |

| D003                                                                                       | VPOR   | VDD Start Voltage to ensure<br>Power-on Reset | _                     | Vss         | _                 | V           | See Section 5.1 for details on Power-on Reset                                                                                                                                                                                                                                                                                                                                                      |

| D004                                                                                       | SVDD   | VDD Rise Rate to ensure<br>Power-on Reset     | 0.05*                 | _           | _                 | V/ms        | See Section 5.1 for details on Power-on Reset                                                                                                                                                                                                                                                                                                                                                      |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

# PIC16C5X

## APPENDIX A: COMPATIBILITY

To convert code written for PIC16CXX to PIC16C5X, the user should take the following steps:

- Check any CALL, GOTO or instructions that modify the PC to determine if any program memory page select operations (PA2, PA1, PA0 bits) need to be made.

- Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- Eliminate any special function register page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- Change RESET vector to proper value for processor used.