#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 1.5KB (1K x 12)                                                          |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 25 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c56-hsi-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

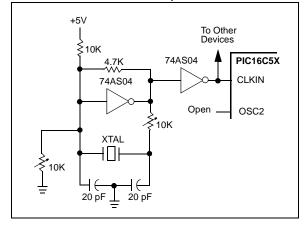

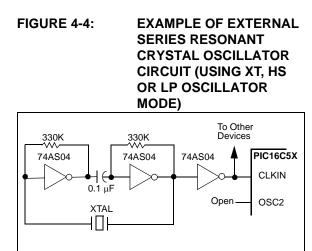

# 4.3 External Crystal Oscillator Circuit

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A welldesigned crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

Figure 4-3 shows an implementation example of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

FIGURE 4-3: EXAMPLE OF EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT (USING XT, HS OR LP OSCILLATOR MODE)

Figure 4-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

# PIC16C5X

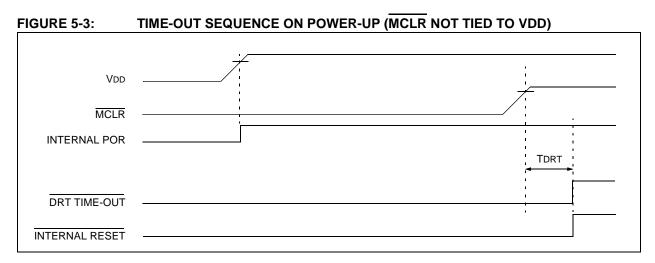

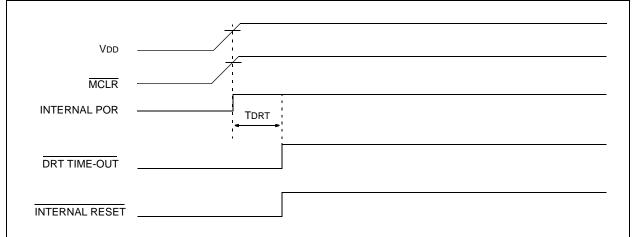

# FIGURE 5-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): FAST VDD RISE TIME

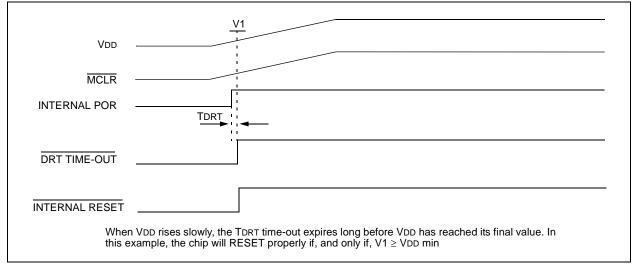

# FIGURE 5-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE TIME

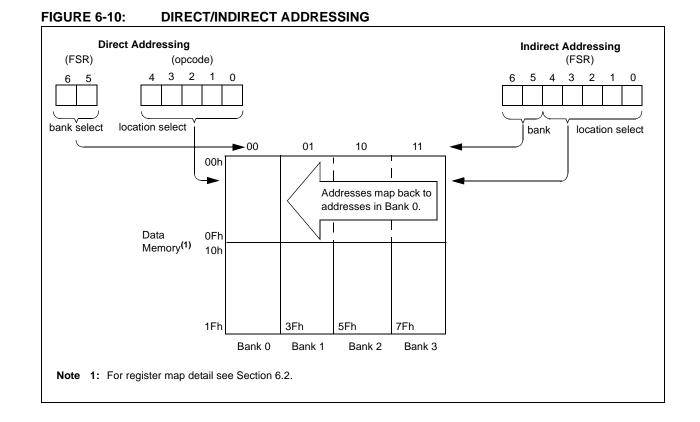

# 6.7 Indirect Data Addressing; INDF and FSR Registers

The INDF Register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR Register (FSR is a *pointer*). This is indirect addressing.

### EXAMPLE 6-1: INDIRECT ADDRESSING

- Register file 08 contains the value 10h

- Register file 09 contains the value 0Ah

- · Load the value 08 into the FSR Register

- A read of the INDF Register will return the value of 10h

- Increment the value of the FSR Register by one (FSR = 09h)

- A read of the INDF register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF Register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 6-2.

# EXAMPLE 6-2:

### HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | MOVLW | H'10' | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ; to RAM             |

| NEXT     | CLRF  | INDF  | ;clear INDF Register |

|          | INCF  | FSR,F | ;inc pointer         |

|          | BTFSC | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;NO, clear next      |

| CONTINUE |       |       |                      |

|          | :     |       | ;YES, continue       |

The FSR is either a 5-bit (PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56) or 7-bit (PIC16C57, PIC16CR57, PIC16CR58, PIC16CR58) wide register. It is used in conjunction with the INDF Register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56:** These do not use banking. FSR<6:5> bits are unimplemented and read as '1's.

**PIC16C57**, **PIC16CR57**, **PIC16C58**, **PIC16CR58**: FSR<6:5> are the bank select bits and are used to select the bank to be addressed (00 = bank 0, 01 = bank 1, 10 = bank 2, 11 = bank 3).

© 1997-2013 Microchip Technology Inc.

| ADDWF                                                       | Add W                                                                                                                                                                         | and f                        |      |  |  |  |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|--|--|--|

| Syntax:                                                     | [ label ] A                                                                                                                                                                   | [ label ] ADDWF f,d          |      |  |  |  |

| Operands:                                                   | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                |                              |      |  |  |  |

| Operation:                                                  | (W) + (f)                                                                                                                                                                     | $\rightarrow$ (dest)         |      |  |  |  |

| Status Affected:                                            | C, DC, Z                                                                                                                                                                      |                              |      |  |  |  |

| Encoding:                                                   | 0001                                                                                                                                                                          | 11df                         | ffff |  |  |  |

| Description:                                                | Add the contents of the W register<br>and register 'f'. If 'd' is 0 the result<br>is stored in the W register. If 'd' is<br>'1' the result is stored back in<br>register 'f'. |                              |      |  |  |  |

| Words:                                                      | 1                                                                                                                                                                             |                              |      |  |  |  |

| Cycles:                                                     | 1                                                                                                                                                                             |                              |      |  |  |  |

| Example:                                                    | ADDWF                                                                                                                                                                         | TEMP_RE                      | G, 0 |  |  |  |

| Before Instr<br>W<br>TEMP_I<br>After Instruc<br>W<br>TEMP_F | =<br>REG =<br>ction<br>=                                                                                                                                                      | 0x17<br>0xC2<br>0xD9<br>0xC2 |      |  |  |  |

| ANDWF                                                                                                                                                  | AND W with f                                                                                                                                                                            |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                                                                                                                                | [label] ANDWF f,d                                                                                                                                                                       |  |  |  |  |

| Operands:                                                                                                                                              | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                          |  |  |  |  |

| Operation:                                                                                                                                             | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                      |  |  |  |  |

| Status Affected:                                                                                                                                       | Z                                                                                                                                                                                       |  |  |  |  |

| Encoding:                                                                                                                                              | 0001 01df ffff                                                                                                                                                                          |  |  |  |  |

| Description:                                                                                                                                           | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is 0<br>the result is stored in the W regis-<br>ter. If 'd' is '1' the result is stored<br>back in register 'f'. |  |  |  |  |

| Words:                                                                                                                                                 | 1                                                                                                                                                                                       |  |  |  |  |

| Cycles:                                                                                                                                                | 1                                                                                                                                                                                       |  |  |  |  |

| Example:                                                                                                                                               | ANDWF TEMP_REG, 1                                                                                                                                                                       |  |  |  |  |

| Example: ANDWF TEMP_REG, 1<br>Before Instruction<br>W = 0x17<br>TEMP_REG = 0xC2<br>After Instruction<br>W = 0x17<br>TEMP_REG = 0x17<br>TEMP_REG = 0x02 |                                                                                                                                                                                         |  |  |  |  |

| ANDLW                                        | AND literal with W                                                                                                           |  |  |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                      | [ <i>label</i> ] ANDLW k                                                                                                     |  |  |  |  |

| Operands:                                    | $0 \le k \le 255$                                                                                                            |  |  |  |  |

| Operation:                                   | (W).AND. (k) $\rightarrow$ (W)                                                                                               |  |  |  |  |

| Status Affected:                             | Z                                                                                                                            |  |  |  |  |

| Encoding:                                    | 1110 kkkk kkkk                                                                                                               |  |  |  |  |

| Description:                                 | The contents of the W register are<br>AND'ed with the eight-bit literal 'k'.<br>The result is placed in the W regis-<br>ter. |  |  |  |  |

| Words:                                       | 1                                                                                                                            |  |  |  |  |

| Cycles:                                      | 1                                                                                                                            |  |  |  |  |

| Example:                                     | ANDLW H'5F'                                                                                                                  |  |  |  |  |

| Before Instru<br>W =<br>After Instruc<br>W = | 0xA3                                                                                                                         |  |  |  |  |

| BCF                                                        | Bit Clear f                                                                |                 |             |  |  |  |  |

|------------------------------------------------------------|----------------------------------------------------------------------------|-----------------|-------------|--|--|--|--|

| Syntax:                                                    | [ label ]                                                                  | [label] BCF f,b |             |  |  |  |  |

| Operands:                                                  | $\begin{array}{l} 0 \leq f \leq 3^{\prime} \\ 0 \leq b \leq 7 \end{array}$ | -               |             |  |  |  |  |

| Operation:                                                 | $0 \rightarrow (f < b$                                                     | >)              |             |  |  |  |  |

| Status Affected:                                           | None                                                                       |                 |             |  |  |  |  |

| Encoding:                                                  | 0100                                                                       | bbbf            | ffff        |  |  |  |  |

| Description:                                               | Bit 'b' in                                                                 | register 'f'    | is cleared. |  |  |  |  |

| Words:                                                     | 1                                                                          |                 |             |  |  |  |  |

| Cycles:                                                    | 1                                                                          |                 |             |  |  |  |  |

| Example:                                                   | BCF                                                                        | FLAG_RE         | IG, 7       |  |  |  |  |

| Before Instruction<br>FLAG_REG = 0xC7<br>After Instruction |                                                                            |                 |             |  |  |  |  |

| FLAG_F                                                     | REG =                                                                      | 0x47            |             |  |  |  |  |

# 12.6 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. Tp | nS                                      |                    |

|-------|-----------------------------------------|--------------------|

|       | PO                                      |                    |

| Т     |                                         |                    |

| F     | Frequency                               | T Time             |

| Lowe  | ercase letters (pp) and their meanings: |                    |

| рр    |                                         |                    |

| 2     | to                                      | mc MCLR            |

| ck    | CLKOUT                                  | osc oscillator     |

| су    | cycle time                              | os OSC1            |

| drt   | device reset timer                      | t0 T0CKI           |

| io    | I/O port                                | wdt watchdog timer |

| Uppe  | ercase letters and their meanings:      |                    |

| S     |                                         |                    |

| F     | Fall                                    | P Period           |

| Н     | High                                    | R Rise             |

| I     | Invalid (Hi-impedance)                  | V Valid            |

| L     | Low                                     | Z Hi-impedance     |

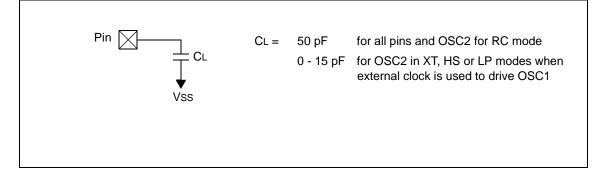

# FIGURE 12-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS - PIC16C54/55/56/57

#### 13.4 DC Characteristics: PIC16CR54A-04E, 10E, 20E (Extended)

| DC CHARACTERISTICS |        | Standard Operating Conditions (unless otherwise specified)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |           |      |          |       |                                               |

|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|-----------|------|----------|-------|-----------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                       | Min       | Тур† | Мах      | Units | Conditions                                    |

| D030               | VIL    | Input Low Voltage                                                                                                                    |           |      |          |       |                                               |

|                    |        | I/O ports                                                                                                                            | Vss       |      | 0.15 Vdd | V     | Pin at hi-impedance                           |

|                    |        | MCLR (Schmitt Trigger)                                                                                                               | Vss       |      | 0.15 VDD | V     |                                               |

|                    |        | T0CKI (Schmitt Trigger)                                                                                                              | Vss       |      | 0.15 VDD | V     |                                               |

|                    |        | OSC1 (Schmitt Trigger)                                                                                                               | Vss       |      | 0.15 VDD | V     | RC mode only <sup>(3)</sup>                   |

|                    |        | OSC1                                                                                                                                 | Vss       | —    | 0.3 Vdd  | V     | XT, HS and LP modes                           |

| D040               | Vін    | Input High Voltage                                                                                                                   |           |      |          |       |                                               |

|                    |        | I/O ports                                                                                                                            | 0.45 Vdd  |      | Vdd      | V     | For all VDD <sup>(4)</sup>                    |

|                    |        | I/O ports                                                                                                                            | 2.0       |      | Vdd      | V     | $4.0V < VDD \le 5.5V^{(4)}$                   |

|                    |        | I/O ports                                                                                                                            | 0.36 Vdd  |      | Vdd      | V     | VDD > 5.5V                                    |

|                    |        | MCLR (Schmitt Trigger)                                                                                                               | 0.85 VDD  |      | Vdd      | V     |                                               |

|                    |        | T0CKI (Schmitt Trigger)                                                                                                              | 0.85 VDD  |      | Vdd      | V     |                                               |

|                    |        | OSC1 (Schmitt Trigger)                                                                                                               | 0.85 VDD  |      | Vdd      | V     | RC mode only <sup>(3)</sup>                   |

|                    |        | OSC1                                                                                                                                 | 0.7 Vdd   | —    | Vdd      | V     | XT, HS and LP modes                           |

| D050               | VHYS   | Hysteresis of Schmitt<br>Trigger inputs                                                                                              | 0.15 Vdd* | —    | _        | V     |                                               |

| D060               | lı∟    | Input Leakage Current <sup>(1,2)</sup>                                                                                               |           |      |          |       | <b>For</b> VDD ≤ <b>5.5</b> V:                |

|                    |        | I/O ports                                                                                                                            | -1.0      | 0.5  | +1.0     | μA    | $VSS \leq VPIN \leq VDD$ ,                    |

|                    |        |                                                                                                                                      |           |      |          | •     | pin at hi-impedance                           |

|                    |        | MCLR                                                                                                                                 | -5.0      |      | _        | μA    | VPIN = VSS + 0.25V                            |

|                    |        | MCLR                                                                                                                                 | _         | 0.5  | +5.0     | μΑ    | VPIN = VDD                                    |

|                    |        | TOCKI                                                                                                                                | -3.0      | 0.5  | +3.0     | μΑ    | $VSS \leq VPIN \leq VDD$                      |

|                    |        | OSC1                                                                                                                                 | -3.0      | 0.5  | +3.0     | μA    | $VSS \leq VPIN \leq VDD$ ,                    |

|                    |        |                                                                                                                                      |           |      |          |       | XT, HS and LP modes                           |

| D080               | Vol    | Output Low Voltage                                                                                                                   |           |      |          |       |                                               |

|                    |        | I/O ports                                                                                                                            | l —       | —    | 0.6      | V     | IOL = 8.7 mA, VDD = 4.5V                      |

|                    |        | OSC2/CLKOUT                                                                                                                          |           |      | 0.6      | V     | IOL = 1.6  mA, VDD = 4.5 V,                   |

|                    |        |                                                                                                                                      |           |      |          |       | RC mode only                                  |

| D090               | Voh    | Output High Voltage <sup>(2)</sup>                                                                                                   |           |      |          |       |                                               |

|                    |        | I/O ports                                                                                                                            | Vdd - 0.7 | —    | —        | V     | IOH = −5.4 mA, VDD = 4.5\                     |

|                    |        | OSC2/CLKOUT                                                                                                                          | Vdd - 0.7 | —    | -        | V     | IOH = -1.0  mA,  VDD = 4.5  V<br>RC mode only |

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

**2:** Negative current is defined as coming out of the pin.

3: For the RC mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C5X be driven with external clock in RC mode.

4: The user may use the better of the two specifications.

| AC Char      | acteristics | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |        |        |       |                  |  |

|--------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|--------|-------|------------------|--|

| Param<br>No. | Symbol      | Characteristic                                                                                                                                                                                                                                 | Min  | Тур†   | Max    | Units | Conditions       |  |

| 1            | Tosc        | External CLKIN Period <sup>(1)</sup>                                                                                                                                                                                                           | 250  | _      | _      | ns    | XT osc mode      |  |

|              |             |                                                                                                                                                                                                                                                | 250  | —      | —      | ns    | HS osc mode (04) |  |

|              |             |                                                                                                                                                                                                                                                | 100  | —      |        | ns    | HS osc mode (10) |  |

|              |             |                                                                                                                                                                                                                                                | 50   | —      |        | ns    | HS osc mode (20) |  |

|              |             |                                                                                                                                                                                                                                                | 5.0  | _      | _      | μS    | LP OSC mode      |  |

|              |             | Oscillator Period <sup>(1)</sup>                                                                                                                                                                                                               | 250  |        | _      | ns    | RC OSC mode      |  |

|              |             |                                                                                                                                                                                                                                                | 250  | —      | 10,000 | ns    | XT OSC mode      |  |

|              |             |                                                                                                                                                                                                                                                | 250  | —      | 250    | ns    | HS OSC mode (04) |  |

|              |             |                                                                                                                                                                                                                                                | 100  | —      | 250    | ns    | HS osc mode (10) |  |

|              |             |                                                                                                                                                                                                                                                | 50   | —      | 250    | ns    | HS osc mode (20) |  |

|              |             |                                                                                                                                                                                                                                                | 5.0  | _      | 200    | μS    | LP OSC mode      |  |

| 2            | Тсу         | Instruction Cycle Time <sup>(2)</sup>                                                                                                                                                                                                          | —    | 4/Fosc |        | _     |                  |  |

| 3            | TosL, TosH  | Clock in (OSC1) Low or High                                                                                                                                                                                                                    | 50*  |        | _      | ns    | XT oscillator    |  |

|              |             | Time                                                                                                                                                                                                                                           | 20*  | —      | —      | ns    | HS oscillator    |  |

|              |             |                                                                                                                                                                                                                                                | 2.0* | _      | —      | μS    | LP oscillator    |  |

| 4            | TosR, TosF  | Clock in (OSC1) Rise or Fall                                                                                                                                                                                                                   | _    | —      | 25*    | ns    | XT oscillator    |  |

|              |             | Time                                                                                                                                                                                                                                           | —    | —      | 25*    | ns    | HS oscillator    |  |

|              |             |                                                                                                                                                                                                                                                | _    | —      | 50*    | ns    | LP oscillator    |  |

| TABLE 13-1: | EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16CR54A |

|-------------|-------------------------------------------------|

|-------------|-------------------------------------------------|

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

when an external clock input is used, the "max" cycle time limit is "Du" (no clock) for all device

2: Instruction cycle period (TcY) equals four times the input oscillator time base period.

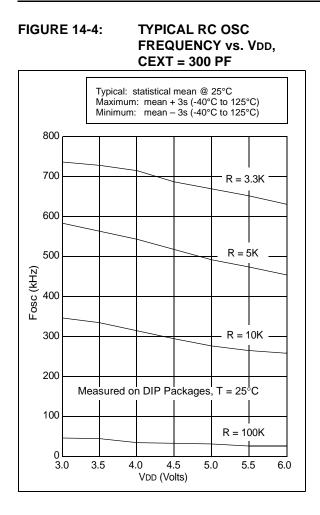

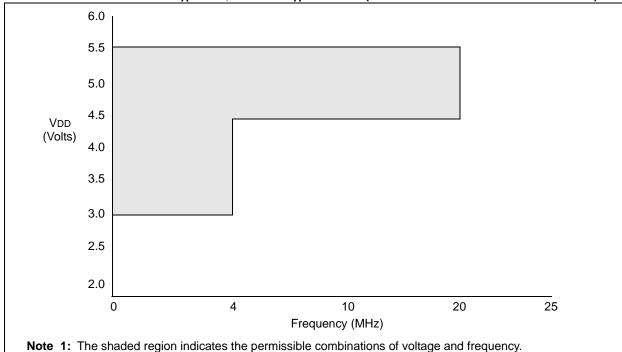

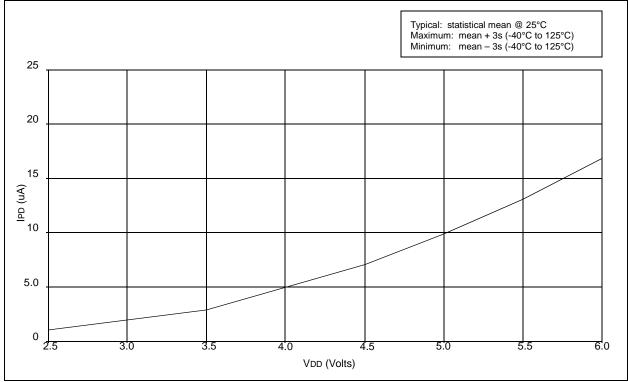

# 14.0 DEVICE CHARACTERIZATION - PIC16C54A

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

# TABLE 14-1: RC OSCILLATOR FREQUENCIES

| Сехт   | Rext | Average<br>Fosc @ 5 V, 25°C |       |  |  |

|--------|------|-----------------------------|-------|--|--|

| 20 pF  | 3.3K | 5 MHz                       | ± 27% |  |  |

|        | 5K   | 3.8 MHz                     | ± 21% |  |  |

|        | 10K  | 2.2 MHz                     | ± 21% |  |  |

|        | 100K | 262 kHz                     | ± 31% |  |  |

| 100 pF | 3.3K | 1.6 MHz                     | ± 13% |  |  |

|        | 5K   | 1.2 MHz                     | ± 13% |  |  |

|        | 10K  | 684 kHz                     | ± 18% |  |  |

|        | 100K | 71 kHz                      | ± 25% |  |  |

| 300 pF | 3.3K | 660 kHz                     | ± 10% |  |  |

|        | 5.0K | 484 kHz                     | ± 14% |  |  |

|        | 10K  | 267 kHz                     | ± 15% |  |  |

|        | 100K | 29 kHz                      | ± 19% |  |  |

The frequencies are measured on DIP packages.

The percentage variation indicated here is part-to-part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviations from the average value for VDD = 5V.

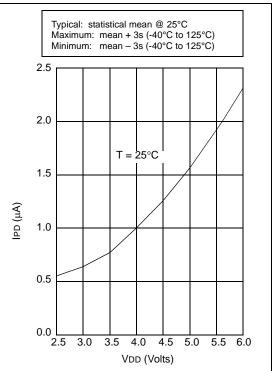

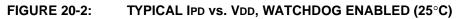

#### FIGURE 14-5: TYPICAL IPD vs. VDD, WATCHDOG DISABLED

# 15.2 DC Characteristics: PIC16

# PIC16C54A-04E, 10E, 20E (Extended) PIC16LC54A-04E (Extended)

|                   | PIC16LC54A-04EStandard Operating Conditions (unless otherwise spect<br>Operating Temperature(Extended) $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                   |                                                                                                                                     |             |           |                                                                                         |                                                                               |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| PIC16C<br>(Extend | ,                                                                                                                                                           | 10E, 20E                          | Standard Operating Conditions (unless otherwise spectrum)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for external |             |           | tions (unless otherwise specified) $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                                                               |

| Param<br>No.      | Symbol                                                                                                                                                      | Characteristic                    | Min Typ† Max Units Conditions                                                                                                       |             |           |                                                                                         | Conditions                                                                    |

|                   | IPD                                                                                                                                                         | Power-down Current <sup>(2)</sup> |                                                                                                                                     |             |           |                                                                                         |                                                                               |

| D020              |                                                                                                                                                             | PIC16LC54A                        | _                                                                                                                                   | 2.5<br>0.25 | 15<br>7.0 | μΑ<br>μΑ                                                                                | VDD = 2.5V, WDT enabled,<br>Extended<br>VDD = 2.5V, WDT disabled,<br>Extended |

| D020A             |                                                                                                                                                             | PIC16C54A                         |                                                                                                                                     | 5.0<br>0.8  | 22<br>18* | μΑ<br>μΑ                                                                                | VDD = 3.5V, WDT enabled<br>VDD = 3.5V, WDT disabled                           |

Legend: Rows with standard voltage device data only are shaded for improved readability.

\* These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- **3:** Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

© 1997-2013 Microchip Technology Inc.

NOTES:

NOTES:

# PIC16C5X

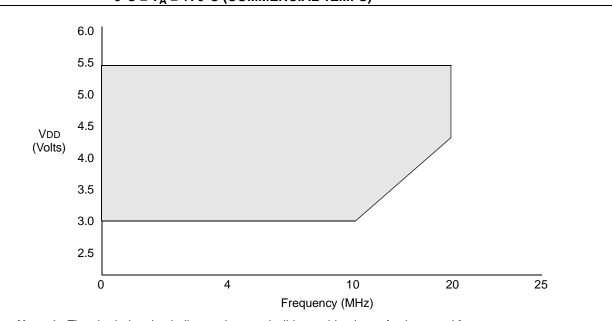

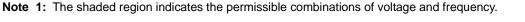

**2**: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

2: The maximum rated speed of the part limits the permissible combinations of voltage and frequency.

Please reference the Product Identification System section for the maximum rated speed of the parts.

#### 17.3 DC Characteristics: PIC16C54C/C55A/C56A/C57C/C58B-04, 20 (Commercial, Industrial, Extended) PIC16LC54C/LC55A/LC56A/LC57C/LC58B-04 (Commercial, Industrial) PIC16CR54C/CR56A/CR57C/CR58B-04, 20 (Commercial, Industrial, Extended) PIC16LCR54C/LCR56A/LCR57C/LCR58B-04 (Commercial, Industrial)

| DC CHARACTERISTICS |        |                                                                                                                                     | Standard Operat<br>Operating Tempe                                             | nditions (unless otherwise specified)<br>$0^{\circ}C \le TA \le +70^{\circ}C$ for commercial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                                                  |                            |                                                                                                                                                                                                   |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                      | Min                                                                            | Тур†                                                                                                                                                                                                          | Max                                                              | Units                      | Conditions                                                                                                                                                                                        |

| D030               | VIL    | Input Low Voltage<br>I/O Ports<br>I/O Ports<br>MCLR (Schmitt Trigger)<br>TOCKI (Schmitt Trigger)<br>OSC1 (Schmitt Trigger)<br>OSC1  | Vss<br>Vss<br>Vss<br>Vss<br>Vss<br>Vss<br>Vss                                  | <br><br>                                                                                                                                                                                                      | 0.8 V<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.3 VDD | V<br>V<br>V<br>V<br>V      | 4.5V <v<sub>DD ≤ 5.5V<br/>Otherwise<br/>RC mode only<sup>(3)</sup><br/>XT, HS and LP modes</v<sub>                                                                                                |

| D040               | Viн    | Input High Voltage<br>I/O ports<br>I/O ports<br>MCLR (Schmitt Trigger)<br>TOCKI (Schmitt Trigger)<br>OSC1 (Schmitt Trigger)<br>OSC1 | 2.0<br>0.25 Vdd+0.8<br>0.85 Vdd<br>0.85 Vdd<br>0.85 Vdd<br>0.85 Vdd<br>0.7 Vdd | <br>                                                                                                                                                                                                          | Vdd<br>Vdd<br>Vdd<br>Vdd<br>Vdd<br>Vdd<br>Vdd                    | V<br>V<br>V<br>V<br>V      | 4.5V < VDD ≤ 5.5V<br>Otherwise<br>RC mode only <sup>(3)</sup><br>XT, HS and LP modes                                                                                                              |

| D050               | VHYS   | Hysteresis of Schmitt<br>Trigger inputs                                                                                             | 0.15 Vdd*                                                                      | —                                                                                                                                                                                                             | _                                                                | V                          |                                                                                                                                                                                                   |

| D060               | Ιι∟    | Input Leakage Current <sup>(1,2)</sup><br>I/O ports<br><u>MCLR</u><br>MCLR<br>T0CKI<br>OSC1                                         | -1.0<br>-5.0<br>-3.0<br>-3.0                                                   | 0.5<br>—<br>0.5<br>0.5<br>0.5                                                                                                                                                                                 | +1.0<br>+5.0<br>+3.0<br>+3.0<br>—                                | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ | For VDD $\leq$ 5.5V:<br>VSS $\leq$ VPIN $\leq$ VDD,<br>pin at hi-impedance<br>VPIN = VSS +0.25V<br>VPIN = VDD<br>VSS $\leq$ VPIN $\leq$ VDD<br>VSS $\leq$ VPIN $\leq$ VDD,<br>XT, HS and LP modes |

| D080               | Vol    | Output Low Voltage<br>I/O ports<br>OSC2/CLKOUT                                                                                      |                                                                                | _                                                                                                                                                                                                             | 0.6<br>0.6                                                       | V<br>V                     | IOL = 8.7  mA, VDD = 4.5V<br>IOL = 1.6  mA, VDD = 4.5V,<br>RC mode only                                                                                                                           |

| D090               | Vон    | Output High Voltage <sup>(2)</sup><br>I/O ports<br>OSC2/CLKOUT                                                                      | Vdd - 0.7<br>Vdd - 0.7                                                         | _                                                                                                                                                                                                             | _                                                                | V<br>V                     | IOH = -5.4 mA, VDD = 4.5V<br>IOH = -1.0 mA, VDD = 4.5V,<br>RC mode only                                                                                                                           |

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- Note 1: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

- **2:** Negative current is defined as coming out of the pin.

- 3: For the RC mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C5X be driven with external clock in RC mode.

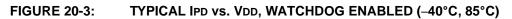

# 18.0 DEVICE CHARACTERIZATION - PIC16LC54A

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

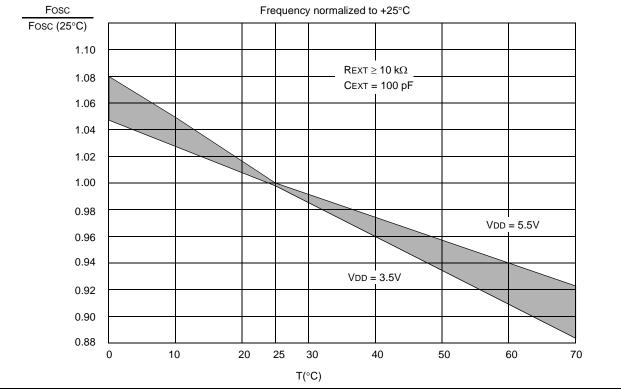

FIGURE 18-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

# TABLE 18-1: RC OSCILLATOR FREQUENCIES

| Сехт   | Rext | Average<br>Fosc @ 5V, 25°C |       |

|--------|------|----------------------------|-------|

| 20 pF  | 3.3K | 5 MHz                      | ± 27% |

|        | 5K   | 3.8 MHz                    | ± 21% |

|        | 10K  | 2.2 MHz                    | ± 21% |

|        | 100K | 262 kHz                    | ± 31% |

| 100 pF | 3.3K | 1.63 MHz                   | ± 13% |

|        | 5K   | 1.2 MHz                    | ± 13% |

|        | 10K  | 684 kHz                    | ± 18% |

|        | 100K | 71 kHz                     | ± 25% |

| 300 pF | 3.3K | 660 kHz                    | ± 10% |

|        | 5.0K | 484 kHz                    | ± 14% |

|        | 10K  | 267 kHz                    | ± 15% |

|        | 100K | 29 kHz                     | ± 19% |

The frequencies are measured on DIP packages.

The percentage variation indicated here is part-to-part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviation from average value for VDD = 5V.

# 19.1 DC Characteristics:PIC16C54C/C55A/C56A/C57C/C58B-40 (Commercial)<sup>(1)</sup>

|              | <b>54C/C55</b><br>mercial) | A/C56A/C57C/C58B-40                           |       | ard Ope<br>ing Tem | -          |          | tions (unless otherwise specified) $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |

|--------------|----------------------------|-----------------------------------------------|-------|--------------------|------------|----------|----------------------------------------------------------------------------------------|

| Param<br>No. | Symbol                     | Characteristic                                | Min   | Тур†               | Max        | Units    | Conditions                                                                             |

| D001         | Vdd                        | Supply Voltage                                | 4.5   | -                  | 5.5        | V        | HS mode from 20 - 40 MHz                                                               |

| D002         | Vdr                        | RAM Data Retention Voltage <sup>(2)</sup>     |       | 1.5*               | —          | V        | Device in SLEEP mode                                                                   |

| D003         | VPOR                       | VDD Start Voltage to ensure<br>Power-on Reset | —     | Vss                | —          | V        | See Section 5.1 for details on<br>Power-on Reset                                       |

| D004         | SVDD                       | VDD Rise Rate to ensure Power-<br>on Reset    | 0.05* | _                  | —          | V/ms     | See Section 5.1 for details on<br>Power-on Reset                                       |

| D010         | Idd                        | Supply Current <sup>(3)</sup>                 | _     | 5.2<br>6.8         | 12.3<br>16 | mA<br>mA | Fosc = 40 MHz, VDD = $4.5V$ , HS mode<br>Fosc = 40 MHz, VDD = $5.5V$ , HS mode         |

| D020         | IPD                        | Power-down Current <sup>(3)</sup>             | _     | 1.8<br>9.8         | 7.0<br>27* | μΑ<br>μΑ | VDD = 5.5V, WDT disabled, Commercial<br>VDD = 5.5V, WDT enabled, Commercial            |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** Device operation between 20 MHz to 40 MHz requires the following: VDD between 4.5V to 5.5V, OSC1 pin externally driven, OSC2 pin not connected, HS oscillator mode and commercial temperatures. For operation between DC and 20 MHz, See Section 19.1.

- **2:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

# 21.0 PACKAGING INFORMATION

# 21.1 Package Marketing Information

### 18-Lead PDIP

# 28-Lead Skinny PDIP (.300")

# 28-Lead PDIP (.600")

### 18-Lead SOIC

# 28-Lead SOIC

# 20-Lead SSOP

# 28-Lead SSOP

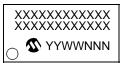

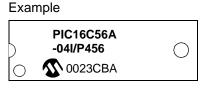

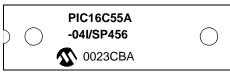

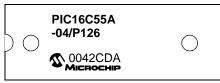

### Example

# Example

# Example

# Example

# Example

# Example

# w

| W Register                 |        |

|----------------------------|--------|

| Value on reset             | 20     |

| Wake-up from SLEEP         | 19, 47 |

| Watchdog Timer (WDT)       | 43, 46 |

| Period                     |        |

| Programming Considerations |        |

| Register values on reset   |        |

| WWW, On-Line Support       |        |

| X                          |        |

| XORLW                      | 60     |

| XORWF                      |        |

| Z                          |        |

| Zero (Z) bit               | 9, 29  |