Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 1.5KB (1K x 12)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 25 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c56-hsi-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16C5X

### 8-Bit EPROM/ROM-Based CMOS Microcontrollers

### 1.0 GENERAL DESCRIPTION

The PIC16C5X from Microchip Technology is a family of low cost, high performance, 8-bit fully static, EPROM/ROM-based CMOS microcontrollers. It employs a RISC architecture with only 33 single word/ single cycle instructions. All instructions are single cycle except for program branches which take two cycles. The PIC16C5X delivers performance in an order of magnitude higher than its competitors in the same price category. The 12-bit wide instructions are highly symmetrical resulting in 2:1 code compression over other 8-bit microcontrollers in its class. The easy to use and easy to remember instruction set reduces development time significantly.

The PIC16C5X products are equipped with special features that reduce system cost and power requirements. The Power-on Reset (POR) and Device Reset Timer (DRT) eliminate the need for external RESET circuitry. There are four oscillator configurations to choose from, including the power saving LP (Low Power) oscillator and cost saving RC oscillator. Power saving SLEEP mode, Watchdog Timer and Code Protection features improve system cost, power and reliability.

The UV erasable CERDIP packaged versions are ideal for code development, while the cost effective One Time Programmable (OTP) versions are suitable for production in any volume. The customer can take full advantage of Microchip's price leadership in OTP microcontrollers, while benefiting from the OTP's flexibility.

The PIC16C5X products are supported by a full featured macro assembler, a software simulator, an in-circuit emulator, a low cost development programmer and a full featured programmer. All the tools are supported on IBM<sup>®</sup> PC and compatible machines.

### 1.1 Applications

The PIC16C5X series fits perfectly in applications ranging from high speed automotive and appliance motor control to low power remote transmitters/receivers, pointing devices and telecom processors. The EPROM technology makes customizing application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages, for through hole or surface mounting, make this microcontroller series perfect for applications with space limitations. Low cost, low power, high performance ease of use and I/O flexibility make the PIC16C5X series very versatile even in areas where no microcontroller use has been considered before (e.g., timer functions, replacement of "glue" logic in larger systems, co-processor applications).

|             |     | Pin Number |      | Pin Buffer | Buffer | Description                                                                                                                                                                                                       |

|-------------|-----|------------|------|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name    | DIP | SOIC       | SSOP | Туре       | Туре   | Description                                                                                                                                                                                                       |

| RA0         | 6   | 6          | 5    | I/O        | TTL    | Bi-directional I/O port                                                                                                                                                                                           |

| RA1         | 7   | 7          | 6    | I/O        | TTL    |                                                                                                                                                                                                                   |

| RA2         | 8   | 8          | 7    | I/O        | TTL    |                                                                                                                                                                                                                   |

| RA3         | 9   | 9          | 8    | I/O        | TTL    |                                                                                                                                                                                                                   |

| RB0         | 10  | 10         | 9    | I/O        | TTL    | Bi-directional I/O port                                                                                                                                                                                           |

| RB1         | 11  | 11         | 10   | I/O        | TTL    |                                                                                                                                                                                                                   |

| RB2         | 12  | 12         | 11   | I/O        | TTL    |                                                                                                                                                                                                                   |

| RB3         | 13  | 13         | 12   | I/O        | TTL    |                                                                                                                                                                                                                   |

| RB4         | 14  | 14         | 13   | I/O        | TTL    |                                                                                                                                                                                                                   |

| RB5         | 15  | 15         | 15   | I/O        | TTL    |                                                                                                                                                                                                                   |

| RB6         | 16  | 16         | 16   | I/O        | TTL    |                                                                                                                                                                                                                   |

| RB7         | 17  | 17         | 17   | I/O        | TTL    |                                                                                                                                                                                                                   |

| RC0         | 18  | 18         | 18   | I/O        | TTL    | Bi-directional I/O port                                                                                                                                                                                           |

| RC1         | 19  | 19         | 19   | I/O        | TTL    |                                                                                                                                                                                                                   |

| RC2         | 20  | 20         | 20   | I/O        | TTL    |                                                                                                                                                                                                                   |

| RC3         | 21  | 21         | 21   | I/O        | TTL    |                                                                                                                                                                                                                   |

| RC4         | 22  | 22         | 22   | I/O        | TTL    |                                                                                                                                                                                                                   |

| RC5         | 23  | 23         | 23   | I/O        | TTL    |                                                                                                                                                                                                                   |

| RC6         | 24  | 24         | 24   | I/O        | TTL    |                                                                                                                                                                                                                   |

| RC7         | 25  | 25         | 25   | I/O        | TTL    |                                                                                                                                                                                                                   |

| TOCKI       | 1   | 1          | 2    | Ι          | ST     | Clock input to Timer0. Must be tied to Vss or VDD, if not in use, to reduce current consumption.                                                                                                                  |

| MCLR        | 28  | 28         | 28   | I          | ST     | Master clear (RESET) input. This pin is an active low RESET to the device.                                                                                                                                        |

| OSC1/CLKIN  | 27  | 27         | 27   | I          | ST     | Oscillator crystal input/external clock source input.                                                                                                                                                             |

| OSC2/CLKOUT | 26  | 26         | 26   | 0          | _      | Oscillator crystal output. Connects to crystal or resonator<br>in crystal Oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| Vdd         | 2   | 2          | 3,4  | Р          | _      | Positive supply for logic and I/O pins.                                                                                                                                                                           |

| Vss         | 4   | 4          | 1,14 | Р          |        | Ground reference for logic and I/O pins.                                                                                                                                                                          |

| N/C         | 3,5 | 3,5        |      | _          |        | Unused, do not connect.                                                                                                                                                                                           |

### TABLE 3-2: PINOUT DESCRIPTION - PIC16C55, PIC16C57, PIC16CR57

Legend: I = input, O = output, I/O = input/output, P = power, — = Not Used, TTL = TTL input, ST = Schmitt Trigger input

NOTES:

### 4.3 External Crystal Oscillator Circuit

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A welldesigned crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

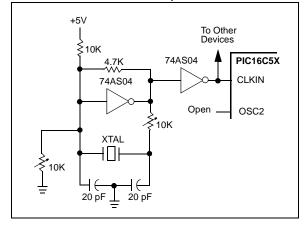

Figure 4-3 shows an implementation example of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

FIGURE 4-3: EXAMPLE OF EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT (USING XT, HS OR LP OSCILLATOR MODE)

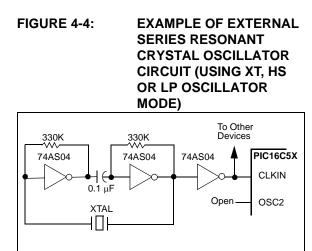

Figure 4-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

### 5.0 RESET

PIC16C5X devices may be RESET in one of the following ways:

- Power-On Reset (POR)

- MCLR Reset (normal operation)

- MCLR Wake-up Reset (from SLEEP)

- WDT Reset (normal operation)

- WDT Wake-up Reset (from SLEEP)

Table 5-1 shows these RESET conditions for the PCL and STATUS registers.

Some registers are not affected in any RESET condition. Their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-On Reset (POR), MCLR or WDT Reset. A MCLR or WDT wake-up from SLEEP also results in a device RESET, and not a continuation of operation before SLEEP. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits (STATUS <4:3>) are set or cleared depending on the different RESET conditions (Table 5-1). These bits may be used to determine the nature of the RESET.

Table 5-3 lists a full description of RESET states of all registers. Figure 5-1 shows a simplified block diagram of the On-chip Reset circuit.

### TABLE 5-1: STATUS BITS AND THEIR SIGNIFICANCE

| Condition                     | ТО | PD |

|-------------------------------|----|----|

| Power-On Reset                | 1  | 1  |

| MCLR Reset (normal operation) | u  | u  |

| MCLR Wake-up (from SLEEP)     | 1  | 0  |

| WDT Reset (normal operation)  | 0  | 1  |

| WDT Wake-up (from SLEEP)      | 0  | 0  |

Legend: u = unchanged, x = unknown, - = unimplemented read as '0'.

### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH RESET

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR | <u>Value</u> on<br>MCLR and<br>WDT Reset |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------|------------------------------------------|

| 03h     | STATUS | PA2   | PA1   | PA0   | TO    | PD    | Z     | DC    | С     | 0001 1xxx       | 000q quuu                                |

Legend: u = unchanged, x = unknown, q = see Table 5-1 for possible values.

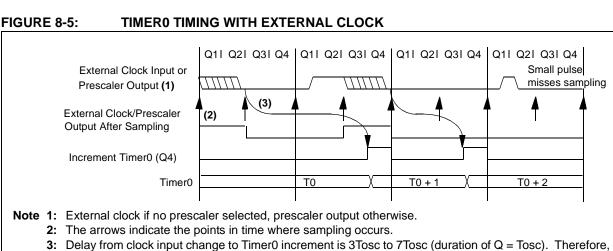

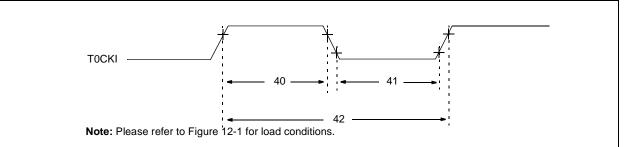

### 8.1 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 8.1.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 8-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 8.1.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 8-5 shows the delay from the external clock edge to the timer incrementing.

Belay from clock input change to Timer0 increment is 3 lose to 7 lose (duration of Q = lose). There the error in measuring the interval between two edges on Timer0 input = ± 4 Tose max.

### 8.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer (WDT), respectively (Section 9.2.1). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT, but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the WDT, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a RESET, the prescaler contains all '0's.

### 8.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 8-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

### EXAMPLE 8-1: CHANGING PRESCALER (TIMER0→WDT)

| CLRWDT            | ;Clear WDT              |

|-------------------|-------------------------|

| CLRF TMR0         | Clear TMR0 & Prescaler  |

| MOVLW B'00xx1111' | ;Last 3 instructions in |

|                   | this example            |

| OPTION            | ;are required only if   |

|                   | ;desired                |

| CLRWDT            | ;PS<2:0> are 000 or     |

|                   | ;001                    |

| MOVLW B'00xx1xxx' | ;Set Prescaler to       |

| OPTION            | ;desired WDT rate       |

|                   |                         |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 8-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

### EXAMPLE 8-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| MOVLW  | B'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

|        |             | ;clock source       |

OPTION

NOTES:

| GOTO                   | Unconditional Branch                                                                                                                                                                        |         |      |  |  |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|--|--|--|--|

| Syntax:                | [ label ]                                                                                                                                                                                   | GOTO    | k    |  |  |  |  |

| Operands:              | $0 \le k \le 511$                                                                                                                                                                           |         |      |  |  |  |  |

| Operation:             | $k \rightarrow PC < 8:0>;$<br>STATUS <6:5> $\rightarrow PC < 10:9>$                                                                                                                         |         |      |  |  |  |  |

| Status Affected:       | None                                                                                                                                                                                        |         |      |  |  |  |  |

| Encoding:              | 101k                                                                                                                                                                                        | kkkk    | kkkk |  |  |  |  |

| Description:           | GOTO is an unconditional branch.<br>The 9-bit immediate value is<br>loaded into PC bits <8:0>. The<br>upper bits of PC are loaded from<br>STATUS<6:5>. GOTO is a two-<br>cycle instruction. |         |      |  |  |  |  |

| Words:                 | 1                                                                                                                                                                                           |         |      |  |  |  |  |

| Cycles:                | 2                                                                                                                                                                                           |         |      |  |  |  |  |

| Example:               | GOTO THERE                                                                                                                                                                                  |         |      |  |  |  |  |

| After Instruct<br>PC = | ion<br>address                                                                                                                                                                              | G (THER | E)   |  |  |  |  |

| INCF                                                    | Increment f                                                                                                                                                          |  |  |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                                 | [label] INCF f,d                                                                                                                                                     |  |  |  |  |

| Operands:                                               | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                                     |  |  |  |  |

| Operation:                                              | (f) + 1 $\rightarrow$ (dest)                                                                                                                                         |  |  |  |  |

| Status Affected:                                        | Z                                                                                                                                                                    |  |  |  |  |

| Encoding:                                               | 0010 10df ffff                                                                                                                                                       |  |  |  |  |

| Description:                                            | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |  |  |  |  |

| Words:                                                  | 1                                                                                                                                                                    |  |  |  |  |

| Cycles:                                                 | 1                                                                                                                                                                    |  |  |  |  |

| Example:                                                | INCF CNT, 1                                                                                                                                                          |  |  |  |  |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0xFF<br>= 0                                                                                                                                                        |  |  |  |  |

| INCFSZ                               | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                              | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Operands:                            | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Operation:                           | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Status Affected:                     | None                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Encoding:                            | 0011 11df ffff                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Description:                         | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'.<br>If the result is 0, then the next<br>instruction, which is already<br>fetched, is discarded and a NOP is<br>executed instead making it a two-<br>cycle instruction. |  |  |  |  |

| Words:                               | 1                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Cycles:                              | 1(2)                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Example:                             | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•<br>•                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Before Instru<br>PC<br>After Instruc | = address (HERE)                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| CNT<br>if CNT<br>PC<br>if CNT<br>PC  | <pre>= CNT + 1;<br/>= 0,<br/>= address (CONTINUE);<br/>≠ 0,<br/>= address (HERE +1)</pre>                                                                                                                                                                                                                                                   |  |  |  |  |

| MOVWF               | Move W to f                      |  |  |  |  |  |

|---------------------|----------------------------------|--|--|--|--|--|

| Syntax:             | [ <i>label</i> ] MOVWF f         |  |  |  |  |  |

| Operands:           | $0 \leq f \leq 31$               |  |  |  |  |  |

| Operation:          | $(W) \rightarrow (f)$            |  |  |  |  |  |

| Status Affected:    | None                             |  |  |  |  |  |

| Encoding:           | 0000 001f ffff                   |  |  |  |  |  |

| Description:        | Move data from the W register to |  |  |  |  |  |

|                     | register 'f'.                    |  |  |  |  |  |

| Words:              | 1                                |  |  |  |  |  |

| Cycles:             | 1                                |  |  |  |  |  |

| Example:            | MOVWF TEMP_REG                   |  |  |  |  |  |

| W<br>After Instruct | REG = 0xFF $= 0x4F$              |  |  |  |  |  |

| NOP              | No Operation |        |      |  |  |

|------------------|--------------|--------|------|--|--|

| Syntax:          | [ label ]    | NOP    |      |  |  |

| Operands:        | None         |        |      |  |  |

| Operation:       | No operation |        |      |  |  |

| Status Affected: | None         |        |      |  |  |

| Encoding:        | 0000         | 0000   | 0000 |  |  |

| Description:     | No opera     | ation. |      |  |  |

| Words:           | 1            |        |      |  |  |

| Cycles:          | 1            |        |      |  |  |

| Example:         | NOP          |        |      |  |  |

| OPTION           | Load Ol             |                                                                   | egister |  |  |  |

|------------------|---------------------|-------------------------------------------------------------------|---------|--|--|--|

| Syntax:          | [ label ]           | OPTIO                                                             | N       |  |  |  |

| Operands:        | None                |                                                                   |         |  |  |  |

| Operation:       | $(W) \rightarrow C$ | PTION                                                             |         |  |  |  |

| Status Affected: | None                |                                                                   |         |  |  |  |

| Encoding:        | 0000                | 0000                                                              | 0010    |  |  |  |

| Description:     |                     | The content of the W register is loaded into the OPTION register. |         |  |  |  |

| Words:           | 1                   |                                                                   |         |  |  |  |

| Cycles:          | 1                   |                                                                   |         |  |  |  |

| Example          | OPTION              |                                                                   |         |  |  |  |

| Before Instru    | ction               |                                                                   |         |  |  |  |

| W                | •                   | 07                                                                |         |  |  |  |

| After Instructi  |                     |                                                                   |         |  |  |  |

| OPTION           | = 0x                | 07                                                                |         |  |  |  |

| RETLW               | Return with Literal in W                                                                                                                                                            |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:             | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:           | $0 \leq k \leq 255$                                                                                                                                                                 |

| Operation:          | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |

| Status Affected:    | None                                                                                                                                                                                |

| Encoding:           | 1000 kkkk kkkk                                                                                                                                                                      |

| Description:        | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address). This<br>is a two-cycle instruction. |

| Words:              | 1                                                                                                                                                                                   |

| Cycles:             | 2                                                                                                                                                                                   |

| Example:            | CALL TABLE ;W contains<br>;table offset<br>;value.<br>• ;W now has table<br>• ;value.                                                                                               |

| TABLE               | <pre>ADDWF PC ;W = offset RETLW k1 ;Begin table RETLW k2 ;</pre>                                                                                                                    |

| Before Instru       |                                                                                                                                                                                     |

| W<br>After Instruct | = 0x07                                                                                                                                                                              |

| After Instruct<br>W | = value of k8                                                                                                                                                                       |

| SUBWF                                                                                                                                                                                                                                | Subti                                                                  | ract W                           | / from f                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                                                                                                                                              | [label                                                                 | ] SU                             | JBWF f,d                                                                                                                        |

| Operands:                                                                                                                                                                                                                            | $0 \le f \le$                                                          | ≤ 31                             |                                                                                                                                 |

|                                                                                                                                                                                                                                      | d ∈ [0                                                                 | ),1]                             |                                                                                                                                 |

| Operation:                                                                                                                                                                                                                           | (f) – (                                                                | W) $\rightarrow$                 | (dest)                                                                                                                          |

| Status Affected:                                                                                                                                                                                                                     | C, DC                                                                  | C, Z                             |                                                                                                                                 |

| Encoding:                                                                                                                                                                                                                            | 000                                                                    | 0 10                             | Odf ffff                                                                                                                        |

| Description:                                                                                                                                                                                                                         | the W<br>is 0 th<br>regist                                             | / regist<br>ne resu<br>er. If 'c | 's complement method)<br>ter from register 'f'. If 'd'<br>ult is stored in the W<br>d' is 1 the result is<br>c in register 'f'. |

| Words:                                                                                                                                                                                                                               | 1                                                                      |                                  |                                                                                                                                 |

| Cycles:                                                                                                                                                                                                                              | 1                                                                      |                                  |                                                                                                                                 |

| Example 1:                                                                                                                                                                                                                           | SUBW                                                                   | FR                               | REG1, 1                                                                                                                         |

| Before Instruct<br>REG1<br>W<br>C<br>After Instruct<br>REG1<br>W<br>C<br>Example 2:<br>Before Instruct<br>REG1<br>W<br>C<br>After Instruct<br>REG1<br>W<br>C<br>Example 3:<br>Before Ins<br>REG1<br>W<br>C<br>After Instruct<br>REG1 | =<br>=<br>=<br>=<br>=<br>ion<br>=<br>=<br>truction<br>=<br>=<br>=<br>= | 1<br>2<br>?<br>0xFF              | ; result is positive<br>; result is zero                                                                                        |

| W<br>C                                                                                                                                                                                                                               | =<br>=                                                                 | 2<br>0                           | ; result is negative                                                                                                            |

| -                                                                                                                                                                                                                                    |                                                                        | -                                | ,                                                                                                                               |

| SWAPF                                          | Swap Nibbles in f                                                                                                                                                        |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                        | [label] SWAPF f,d                                                                                                                                                        |

| Operands:                                      | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                                         |

| Operation:                                     | $(f<3:0>) \rightarrow (dest<7:4>);$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                                |

| Status Affected:                               | None                                                                                                                                                                     |

| Encoding:                                      | 0011 10df ffff                                                                                                                                                           |

| Description:                                   | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is 0<br>the result is placed in W register. If<br>'d' is 1 the result is placed in<br>register 'f'. |

| Words:                                         | 1                                                                                                                                                                        |

| Cycles:                                        | 1                                                                                                                                                                        |

| Example                                        | SWAPF REG1, 0                                                                                                                                                            |

| REG1<br>After Instruct<br>REG1<br>W            | = 0xA5<br>ion<br>= 0xA5<br>= 0x5A                                                                                                                                        |

| TRIS                                           | Load TRIS Register                                                                                                                                                       |

| Syntax:                                        | [ <i>label</i> ] TRIS f                                                                                                                                                  |

| Operands:                                      | f = 5, 6 or 7                                                                                                                                                            |

| Operation:                                     | (W) $\rightarrow$ TRIS register f                                                                                                                                        |

| Status Affected:                               | None                                                                                                                                                                     |

| Encoding:                                      | 0000 0000 0fff                                                                                                                                                           |

| Description:                                   | TRIS register 'f' ( $f = 5, 6, or 7$ ) is<br>loaded with the contents of the W<br>register.                                                                              |

| Words:                                         | 1                                                                                                                                                                        |

| Cycles:                                        | 1                                                                                                                                                                        |

| Example                                        | TRIS PORTB                                                                                                                                                               |

| Before Instru<br>W<br>After Instructi<br>TRISB | = 0xA5<br>on                                                                                                                                                             |

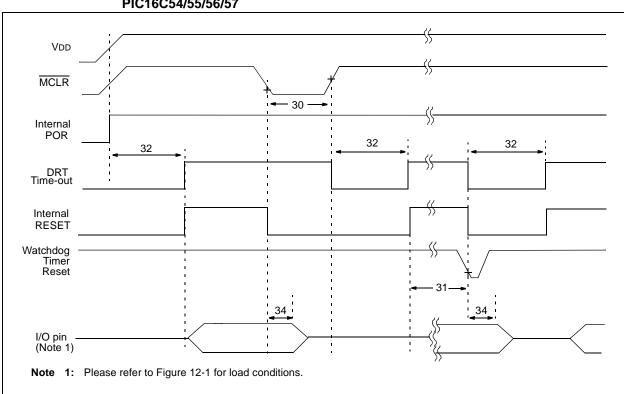

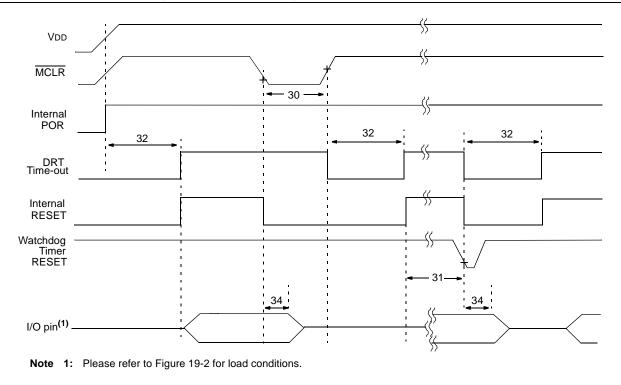

### FIGURE 12-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING -PIC16C54/55/56/57

### TABLE 12-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16C54/55/56/57

| AC Chara     | cteristics | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |     |      |    |                   |  |

|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|----|-------------------|--|

| Param<br>No. | Symbol     | Characteristic Min Typ† Max Units Conditions                                                                                                                                                                                                             |      |     |      |    |                   |  |

| 30           | TmcL       | MCLR Pulse Width (low)                                                                                                                                                                                                                                   | 100* | —   | —    | ns | VDD = 5.0V        |  |

| 31           | Twdt       | Watchdog Timer Time-out Period<br>(No Prescaler)                                                                                                                                                                                                         | 9.0* | 18* | 30*  | ms | VDD = 5.0V (Comm) |  |

| 32           | Tdrt       | Device Reset Timer Period                                                                                                                                                                                                                                | 9.0* | 18* | 30*  | ms | VDD = 5.0V (Comm) |  |

| 34           | Tioz       | I/O Hi-impedance from MCLR Low                                                                                                                                                                                                                           | _    | _   | 100* | ns |                   |  |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### FIGURE 12-5: TIMER0 CLOCK TIMINGS - PIC16C54/55/56/57

### TABLE 12-4: TIMER0 CLOCK REQUIREMENTS - PIC16C54/55/56/57

| AC Ch        | AC CharacteristicsStandard Operating Conditions (unless otherwise specified)<br>Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                                              |                              |  |   |          |                                                                |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------|--|---|----------|----------------------------------------------------------------|--|--|--|

| Param<br>No. | Symbol                                                                                                                                                                                                                                                                     | Symbol Characteristic Min Typ†                               |                              |  |   | Units    | Conditions                                                     |  |  |  |

| 40           | Tt0H                                                                                                                                                                                                                                                                       | T0CKI High Pulse Width<br>- No Prescaler<br>- With Prescaler | 0.5 Tcy + 20*<br>10*         |  |   | ns<br>ns |                                                                |  |  |  |

| 41           | TtOL                                                                                                                                                                                                                                                                       | TOCKI Low Pulse Width<br>- No Prescaler<br>- With Prescaler  | 0.5 TCY + 20*<br>10*         |  | _ | ns       |                                                                |  |  |  |

| 42           | Tt0P                                                                                                                                                                                                                                                                       | T0CKI Period                                                 | 20 or <u>Tcy + 40</u> *<br>N |  | — | ns       | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |  |  |  |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

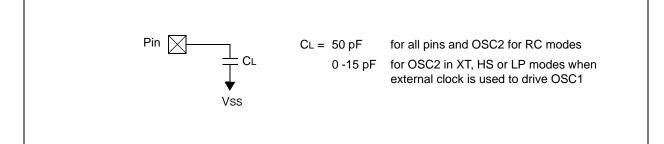

### 13.5 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. Tp | pS                                      |                    |

|-------|-----------------------------------------|--------------------|

| Т     |                                         |                    |

| F     | Frequency                               | T Time             |

| Lowe  | ercase letters (pp) and their meanings: |                    |

| рр    |                                         |                    |

| 2     | to                                      | mc MCLR            |

| ck    | CLKOUT                                  | osc oscillator     |

| су    | cycle time                              | os OSC1            |

| drt   | device reset timer                      | t0 T0CKI           |

| io    | I/O port                                | wdt watchdog timer |

| Uppe  | ercase letters and their meanings:      |                    |

| S     |                                         |                    |

| F     | Fall                                    | P Period           |

| Н     | High                                    | R Rise             |

| I     | Invalid (Hi-impedance)                  | V Valid            |

| L     | Low                                     | Z Hi-impedance     |

### FIGURE 13-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS - PIC16CR54A

## PIC16C5X

### 15.2 DC Characteristics: PIC16C54A-04E, 10E, 20E (Extended) PIC16LC54A-04E (Extended)

|                   |                              | FICTULCJ                                      | -7 0-                                                |      | cnac                                                 | ч)         |                                                               |  |  |  |

|-------------------|------------------------------|-----------------------------------------------|------------------------------------------------------|------|------------------------------------------------------|------------|---------------------------------------------------------------|--|--|--|

|                   | PIC16LC54A-04E<br>(Extended) |                                               |                                                      |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |            |                                                               |  |  |  |

| PIC16C<br>(Extend |                              | 10E, 20E                                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |                                                      |            |                                                               |  |  |  |

| Param<br>No.      | Symbol                       | Characteristic                                | Min                                                  | Max  | Units                                                | Conditions |                                                               |  |  |  |

|                   | Vdd                          | Supply Voltage                                |                                                      |      | •                                                    |            |                                                               |  |  |  |

| D001              |                              | PIC16LC54A                                    | 3.0<br>2.5                                           | _    | 6.25<br>6.25                                         | V<br>V     | XT and RC modes<br>LP mode                                    |  |  |  |

| D001A             |                              | PIC16C54A                                     | 3.5<br>4.5                                           |      | 5.5<br>5.5                                           | V<br>V     | RC and XT modes<br>HS mode                                    |  |  |  |

| D002              | Vdr                          | RAM Data Retention Voltage <sup>(1)</sup>     | _                                                    | 1.5* |                                                      | V          | Device in SLEEP mode                                          |  |  |  |

| D003              | VPOR                         | VDD Start Voltage to ensure<br>Power-on Reset | —                                                    | Vss  | -                                                    | V          | See Section 5.1 for details on<br>Power-on Reset              |  |  |  |

| D004              | SVDD                         | VDD Rise Rate to ensure<br>Power-on Reset     | 0.05*                                                | _    |                                                      | V/ms       | See Section 5.1 for details on<br>Power-on Reset              |  |  |  |

|                   | Idd                          | Supply Current <sup>(2)</sup>                 | •                                                    |      | •                                                    |            |                                                               |  |  |  |

| D010              |                              | PIC16LC54A                                    | —                                                    | 0.5  | 25                                                   | mA         | Fosc = 4.0 MHz, VDD = 5.5V,<br>RC <sup>(3)</sup> and XT modes |  |  |  |

|                   |                              |                                               | —                                                    | 11   | 27                                                   | μA         | Fosc = 32 kHz, VDD = 2.5V,<br>LP mode, Commercial             |  |  |  |

|                   |                              |                                               | —                                                    | 11   | 35                                                   | μA         | Fosc = 32 kHz, VDD = 2.5V,<br>LP mode, Industrial             |  |  |  |

|                   |                              |                                               | _                                                    | 11   | 37                                                   | μA         | Fosc = 32 kHz, VDD = 2.5V,<br>LP mode, Extended               |  |  |  |

| D010A             |                              | PIC16C54A                                     | —                                                    | 1.8  | 3.3                                                  | mA         | Fosc = 4.0 MHz, VDD = 5.5V, $RC^{(3)}$ and XT modes           |  |  |  |

|                   |                              |                                               | —                                                    | 4.8  | 10                                                   | mA         | Fosc = 10 MHz, VDD = 5.5V,<br>HS mode                         |  |  |  |

|                   |                              |                                               | —                                                    | 9.0  | 20                                                   | mA         | Fosc = 20 MHz, VDD = 5.5V,<br>HS mode                         |  |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- \* These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

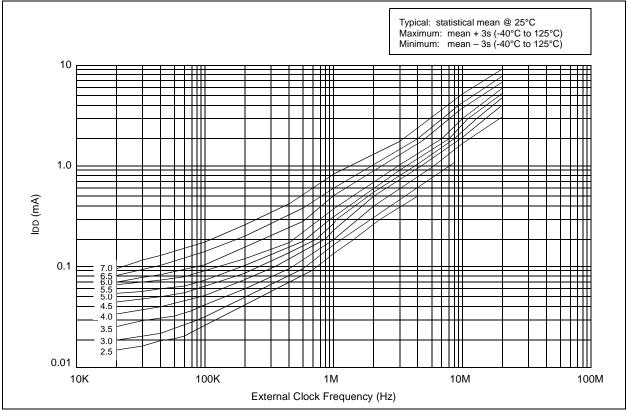

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- **3:** Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

### 17.1 DC Characteristics:PIC16C54C/C55A/C56A/C57C/C58B-04, 20 (Commercial, Industrial) PIC16LC54C/LC55A/LC56A/LC57C/LC58B-04 (Commercial, Industrial) PIC16CR54C/CR56A/CR57C/CR58B-04, 20 (Commercial, Industrial) PIC16LCR54C/LCR56A/LCR57C/LCR58B-04 (Commercial, Industrial)

| PIC16LC<br>PIC16LC<br>(Comm                       | -   | ustrial)                          | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                                                                                                                                                                                                                                                                                                    |                                                        |                                              |                                                                                                                                                                                                                                                                                                                          |  |  |

|---------------------------------------------------|-----|-----------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIC16C5X<br>PIC16CR5X<br>(Commercial, Industrial) |     |                                   |                                                       | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}\mbox{C} \leq \mbox{TA} \leq +70^{\circ}\mbox{C} \mbox{ for commercial} \\ -40^{\circ}\mbox{C} \leq \mbox{TA} \leq +85^{\circ}\mbox{C for industrial} \end{array}$ |                                                        |                                              |                                                                                                                                                                                                                                                                                                                          |  |  |

| Param<br>No. Symbol Characteristic/Device         |     |                                   |                                                       | Тур†                                                                                                                                                                                                                                                                                               | Max                                                    | Units                                        | Conditions                                                                                                                                                                                                                                                                                                               |  |  |

|                                                   | IPD | Power-down Current <sup>(2)</sup> |                                                       |                                                                                                                                                                                                                                                                                                    |                                                        |                                              |                                                                                                                                                                                                                                                                                                                          |  |  |

| D020                                              |     | PIC16LC5X                         |                                                       | 0.25<br>0.25<br>1<br>1.25                                                                                                                                                                                                                                                                          | 2<br>3<br>5<br>8                                       | μΑ<br>μΑ<br>μΑ<br>μΑ                         | VDD = 2.5V, WDT disabled, Commercial $VDD = 2.5V$ , WDT disabled, Industrial $VDD = 2.5V$ , WDT enabled, Commercial $VDD = 2.5V$ , WDT enabled, Industrial                                                                                                                                                               |  |  |

| D020A                                             |     | PIC16C5X                          |                                                       | 0.25<br>0.25<br>1.8<br>2.0<br>4<br>4<br>9.8<br>12                                                                                                                                                                                                                                                  | 4.0<br>5.0<br>7.0*<br>8.0*<br>12*<br>14*<br>27*<br>30* | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 3.0V, WDT disabled, Commercial<br>VDD = 3.0V, WDT disabled, Industrial<br>VDD = 5.5V, WDT disabled, Industrial<br>VDD = 5.5V, WDT disabled, Industrial<br>VDD = 3.0V, WDT enabled, Commercial<br>VDD = 3.0V, WDT enabled, Industrial<br>VDD = 5.5V, WDT enabled, Commercial<br>VDD = 5.5V, WDT enabled, Industrial |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to VSS, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

**3:** Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

### FIGURE 19-5: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16C5X-40

### TABLE 19-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16C5X-40

| AC Charac    | teristics | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercial)Operating Voltage VDD range is described in Section 19.1. |       |      |       |    |                   |  |  |

|--------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|----|-------------------|--|--|

| Param<br>No. | Symbol    | Characteristic Min Typ† Max Units Condit                                                                                                                                                   |       |      |       |    |                   |  |  |

| 30           | TmcL      | MCLR Pulse Width (low)                                                                                                                                                                     | 1000* | _    | _     | ns | VDD = 5.0V        |  |  |

| 31           | Twdt      | Watchdog Timer Time-out Period<br>(No Prescaler)                                                                                                                                           | 9.0*  | 18*  | 30*   | ms | VDD = 5.0V (Comm) |  |  |

| 32           | Tdrt      | Device Reset Timer Period                                                                                                                                                                  | 9.0*  | 18*  | 30*   | ms | VDD = 5.0V (Comm) |  |  |

| 34           | Tioz      | I/O Hi-impedance from MCLR Low                                                                                                                                                             | 100*  | 300* | 1000* | ns |                   |  |  |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

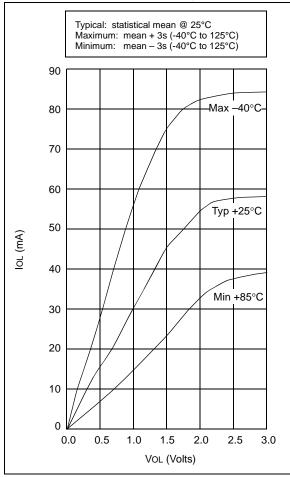

### FIGURE 20-9: IOL vs. VOL, VDD = 5 V

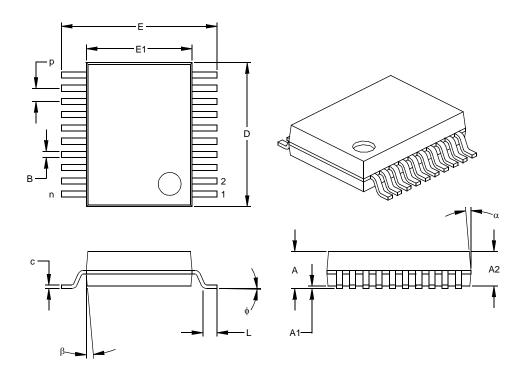

### 20-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units INCHES* |      |      |      |      |        | MILLIMETERS |  |  |  |

|--------------------------|---------------|------|------|------|------|--------|-------------|--|--|--|

| Dimensio                 | MIN           | NOM  | MAX  | MIN  | NOM  | MAX    |             |  |  |  |

| Number of Pins           | n             |      | 20   |      |      | 20     |             |  |  |  |

| Pitch                    | р             |      | .026 |      |      | 0.65   |             |  |  |  |

| Overall Height           | Α             | .068 | .073 | .078 | 1.73 | 1.85   | 1.98        |  |  |  |

| Molded Package Thickness | A2            | .064 | .068 | .072 | 1.63 | 1.73   | 1.83        |  |  |  |

| Standoff §               | A1            | .002 | .006 | .010 | 0.05 | 0.15   | 0.25        |  |  |  |

| Overall Width            | Е             | .299 | .309 | .322 | 7.59 | 7.85   | 8.18        |  |  |  |

| Molded Package Width     | E1            | .201 | .207 | .212 | 5.11 | 5.25   | 5.38        |  |  |  |

| Overall Length           | D             | .278 | .284 | .289 | 7.06 | 7.20   | 7.34        |  |  |  |

| Foot Length              | L             | .022 | .030 | .037 | 0.56 | 0.75   | 0.94        |  |  |  |

| Lead Thickness           | С             | .004 | .007 | .010 | 0.10 | 0.18   | 0.25        |  |  |  |

| Foot Angle               | ф             | 0    | 4    | 8    | 0.00 | 101.60 | 203.20      |  |  |  |

| Lead Width               | В             | .010 | .013 | .015 | 0.25 | 0.32   | 0.38        |  |  |  |

| Mold Draft Angle Top     | α             | 0    | 5    | 10   | 0    | 5      | 10          |  |  |  |

| Mold Draft Angle Bottom  | β             | 0    | 5    | 10   | 0    | 5      | 10          |  |  |  |

\* Controlling Parameter

§ Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-150 Drawing No. C04-072