Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 12                                                                      |

| Program Memory Size        | 1.5KB (1K x 12)                                                         |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 25 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6.25V                                                            |

| Data Converters            | -                                                                       |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 18-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c56-lp-p |

|                            |                                                                         |

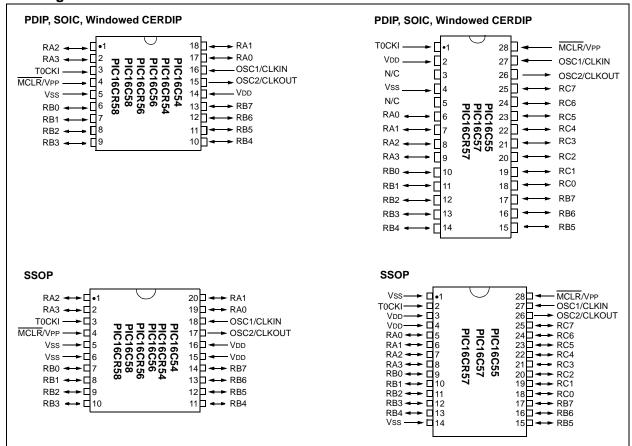

## **Pin Diagrams**

## **Device Differences**

DS30453E-page 2

| Device Dillere | Device Differences                                                 |         |            |                   |                |     |  |  |  |  |  |  |

|----------------|--------------------------------------------------------------------|---------|------------|-------------------|----------------|-----|--|--|--|--|--|--|

| Device         | voltage Range Oscillator Selection Oscillator Technology (Microns) |         | Technology | ROM<br>Equivalent | MCLR<br>Filter |     |  |  |  |  |  |  |

| PIC16C54       | 2.5-6.25                                                           | Factory | See Note 1 | 1.2               | PIC16CR54A     | No  |  |  |  |  |  |  |

| PIC16C54A      | 2.0-6.25                                                           | User    | See Note 1 | 0.9               | _              | No  |  |  |  |  |  |  |

| PIC16C54C      | 2.5-5.5                                                            | User    | See Note 1 | 0.7               | PIC16CR54C     | Yes |  |  |  |  |  |  |

| PIC16C55       | 2.5-6.25                                                           | Factory | See Note 1 | 1.7               | _              | No  |  |  |  |  |  |  |

| PIC16C55A      | 2.5-5.5                                                            | User    | See Note 1 | 0.7               | _              | Yes |  |  |  |  |  |  |

| PIC16C56       | 2.5-6.25                                                           | Factory | See Note 1 | 1.7               | _              | No  |  |  |  |  |  |  |

| PIC16C56A      | 2.5-5.5                                                            | User    | See Note 1 | 0.7               | PIC16CR56A     | Yes |  |  |  |  |  |  |

| PIC16C57       | 2.5-6.25                                                           | Factory | See Note 1 | 1.2               | _              | No  |  |  |  |  |  |  |

| PIC16C57C      | 2.5-5.5                                                            | User    | See Note 1 | 0.7               | PIC16CR57C     | Yes |  |  |  |  |  |  |

| PIC16C58B      | 2.5-5.5                                                            | User    | See Note 1 | 0.7               | PIC16CR58B     | Yes |  |  |  |  |  |  |

| PIC16CR54A     | 2.5-6.25                                                           | Factory | See Note 1 | 1.2               | N/A            | Yes |  |  |  |  |  |  |

| PIC16CR54C     | 2.5-5.5                                                            | Factory | See Note 1 | 0.7               | N/A            | Yes |  |  |  |  |  |  |

| PIC16CR56A     | 2.5-5.5                                                            | Factory | See Note 1 | 0.7               | N/A            | Yes |  |  |  |  |  |  |

| PIC16CR57C     | 2.5-5.5                                                            | Factory | See Note 1 | 0.7               | N/A            | Yes |  |  |  |  |  |  |

| PIC16CR58B     | 2.5-5.5                                                            | Factory | See Note 1 | 0.7               | N/A            | Yes |  |  |  |  |  |  |

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

Note: The table shown above shows the generic names of the PIC16C5X devices. For device varieties, please refer to Section 2.0.

NOTES:

TABLE 3-2: PINOUT DESCRIPTION - PIC16C55, PIC16C57, PIC16CR57

| Din Name    | Pi  | n Numb | er   | Pin  | Buffer | Description                                                                                                                                                                                              |

|-------------|-----|--------|------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name    | DIP | SOIC   | SSOP | Туре | Type   | Description                                                                                                                                                                                              |

| RA0         | 6   | 6      | 5    | I/O  | TTL    | Bi-directional I/O port                                                                                                                                                                                  |

| RA1         | 7   | 7      | 6    | I/O  | TTL    | ·                                                                                                                                                                                                        |

| RA2         | 8   | 8      | 7    | I/O  | TTL    |                                                                                                                                                                                                          |

| RA3         | 9   | 9      | 8    | I/O  | TTL    |                                                                                                                                                                                                          |

| RB0         | 10  | 10     | 9    | I/O  | TTL    | Bi-directional I/O port                                                                                                                                                                                  |

| RB1         | 11  | 11     | 10   | I/O  | TTL    | ·                                                                                                                                                                                                        |

| RB2         | 12  | 12     | 11   | I/O  | TTL    |                                                                                                                                                                                                          |

| RB3         | 13  | 13     | 12   | I/O  | TTL    |                                                                                                                                                                                                          |

| RB4         | 14  | 14     | 13   | I/O  | TTL    |                                                                                                                                                                                                          |

| RB5         | 15  | 15     | 15   | I/O  | TTL    |                                                                                                                                                                                                          |

| RB6         | 16  | 16     | 16   | I/O  | TTL    |                                                                                                                                                                                                          |

| RB7         | 17  | 17     | 17   | I/O  | TTL    |                                                                                                                                                                                                          |

| RC0         | 18  | 18     | 18   | I/O  | TTL    | Bi-directional I/O port                                                                                                                                                                                  |

| RC1         | 19  | 19     | 19   | I/O  | TTL    |                                                                                                                                                                                                          |

| RC2         | 20  | 20     | 20   | I/O  | TTL    |                                                                                                                                                                                                          |

| RC3         | 21  | 21     | 21   | I/O  | TTL    |                                                                                                                                                                                                          |

| RC4         | 22  | 22     | 22   | I/O  | TTL    |                                                                                                                                                                                                          |

| RC5         | 23  | 23     | 23   | I/O  | TTL    |                                                                                                                                                                                                          |

| RC6         | 24  | 24     | 24   | I/O  | TTL    |                                                                                                                                                                                                          |

| RC7         | 25  | 25     | 25   | I/O  | TTL    |                                                                                                                                                                                                          |

| TOCKI       | 1   | 1      | 2    | I    | ST     | Clock input to Timer0. Must be tied to Vss or VDD, if not in use, to reduce current consumption.                                                                                                         |

| MCLR        | 28  | 28     | 28   | I    | ST     | Master clear (RESET) input. This pin is an active low RESET to the device.                                                                                                                               |

| OSC1/CLKIN  | 27  | 27     | 27   | I    | ST     | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT | 26  | 26     | 26   | 0    | —      | Oscillator crystal output. Connects to crystal or resonator in crystal Oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| VDD         | 2   | 2      | 3,4  | Р    |        | Positive supply for logic and I/O pins.                                                                                                                                                                  |

| Vss         | 4   | 4      | 1,14 | Р    | _      | Ground reference for logic and I/O pins.                                                                                                                                                                 |

| N/C         | 3,5 | 3,5    |      | _    | _      | Unused, do not connect.                                                                                                                                                                                  |

Legend: I = input, O = output, I/O = input/output, P = power, — = Not Used, TTL = TTL input, ST = Schmitt Trigger input

NOTES:

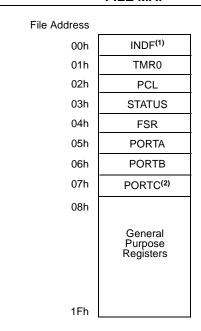

## 6.2 Data Memory Organization

Data memory is composed of registers, or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: Special Function Registers and General Purpose Registers.

The Special Function Registers include the TMR0 register, the Program Counter (PC), the Status Register, the I/O registers (ports) and the File Select Register (FSR). In addition, Special Purpose Registers are used to control the I/O port configuration and prescaler options.

The General Purpose Registers are used for data and control information under command of the instructions.

For the PIC16C54, PIC16CR54, PIC16C56 and PIC16CR56, the register file is composed of 7 Special Function Registers and 25 General Purpose Registers (Figure 6-4).

For the PIC16C55, the register file is composed of 8 Special Function Registers and 24 General Purpose Registers.

For the PIC16C57 and PIC16CR57, the register file is composed of 8 Special Function Registers, 24 General Purpose Registers and up to 48 additional General Purpose Registers that may be addressed using a banking scheme (Figure 6-5).

For the PIC16C58 and PIC16CR58, the register file is composed of 7 Special Function Registers, 25 General Purpose Registers and up to 48 additional General Purpose Registers that may be addressed using a banking scheme (Figure 6-6).

# 6.2.1 GENERAL PURPOSE REGISTER FILE

The register file is accessed either directly or indirectly through the File Select Register (FSR). The FSR Register is described in Section 6.7.

FIGURE 6-4: PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56 REGISTER FILE MAP

- **Note 1:** Not a physical register. See Section 6.7.

- **2:** PIC16C55 only, in all other devices this is implemented as a general purpose register.

## 6.3 STATUS Register

This register contains the arithmetic status of the ALU, the RESET status and the page preselect bits for program memories larger than 512 words.

The STATUS Register can be the destination for any instruction, as with any other register. If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not

writable. Therefore, the result of an instruction with the STATUS Register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS Register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS Register because these instructions do not affect the Z, DC or C bits from the STATUS Register. For other instructions which do affect STATUS Bits, see Section 10.0, Instruction Set Summary.

## REGISTER 6-1: STATUS REGISTER (ADDRESS: 03h)

| R/W-0 | R/W-0 | R/W-0 | R-1 | R-1 | R/W-x | R/W-x | R/W-x |  |

|-------|-------|-------|-----|-----|-------|-------|-------|--|

| PA2   | PA1   | PA0   | TO  | PD  | Z     | DC    | С     |  |

| bit 7 |       |       |     |     |       |       | bit 0 |  |

bit 7: **PA2**: This bit unused at this time.

Use of the PA2 bit as a general purpose read/write bit is not recommended, since this may affect upward compatibility with future products.

bit 6-5: PA<1:0>: Program page preselect bits (PIC16C56/CR56)(PIC16C57/CR57)(PIC16C58/CR58)

00 = Page 0 (000h - 1FFh) - PIC16C56/CR56, PIC16C57/CR57, PIC16C58/CR58

01 = Page 1 (200h - 3FFh) - PIC16C56/CR56, PIC16C57/CR57, PIC16C58/CR58

10 = Page 2 (400h - 5FFh) - PIC16C57/CR57, PIC16C58/CR58

11 = Page 3 (600h - 7FFh) - PIC16C57/CR57, PIC16C58/CR58

Each page is 512 words.

Using the PA<1:0> bits as general purpose read/write bits in devices which do not use them for program page preselect is not recommended since this may affect upward compatibility with future products.

bit 4: **TO**: Time-out bit

1 = After power-up, CLRWDT instruction, or SLEEP instruction

0 = A WDT time-out occurred

bit 3: **PD**: Power-down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

bit 2: Z: Zero bit

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

bit 1: **DC**: Digit carry/borrow bit (for ADDWF and SUBWF instructions)

## ADDWF

1 = A carry from the 4th low order bit of the result occurred

0 = A carry from the 4th low order bit of the result did not occur

### **SUBWF**

1 = A borrow from the 4th low order bit of the result did not occur

0 = A borrow from the 4th low order bit of the result occurred

bit 0: C: Carry/borrow bit (for ADDWF, SUBWF and RRF, RLF instructions)

ADDWF SUBWF RRF or RLF

1 = A carry occurred 1 = A borrow did not occur

0 = A carry did not occur 0 = A borrow occurred

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR 1 = bit is set 0 = bit is cleared x = bit is unknown

Loaded with LSb or MSb, respectively

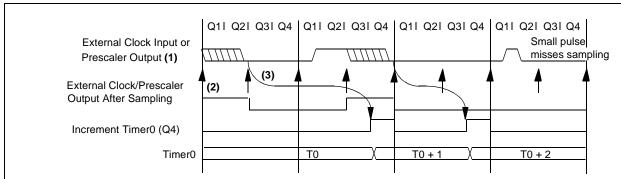

# 8.1 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

## 8.1.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 8-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for T0CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T0CKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 8.1.2 TIMERO INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 8-5 shows the delay from the external clock edge to the timer incrementing.

FIGURE 8-5: TIMERO TIMING WITH EXTERNAL CLOCK

- Note 1: External clock if no prescaler selected, prescaler output otherwise.

- 2: The arrows indicate the points in time where sampling occurs.

- 3: Delay from clock input change to Timer0 increment is 3Tosc to 7Tosc (duration of Q = Tosc). Therefore, the error in measuring the interval between two edges on Timer0 input =  $\pm$  4Tosc max.

#### 8.2 **Prescaler**

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer (WDT), respectively (Section 9.2.1). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT, but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the WDT, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1,x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a RESET, the prescaler contains all '0's.

#### 8.2.1 SWITCHING PRESCALER **ASSIGNMENT**

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 8-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

#### **EXAMPLE 8-1: CHANGING PRESCALER** (TIMER0→WDT)

CLRWDT ;Clear WDT ;Clear TMR0 & Prescaler CLRF TMR0 MOVIW B'00xx1111' ;Last 3 instructions in this example OPTION ; are required only if ;desired CLRWDT ;PS<2:0> are 000 or ;001 MOVLW B'00xx1xxx' ;Set Prescaler to OPTION ;desired WDT rate

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 8-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

#### **EXAMPLE 8-2: CHANGING PRESCALER** (WDT→TIMER0)

CLRWDT ;Clear WDT and ;prescaler ;Select TMR0, new MOVLW B'xxxx0xxx' ;prescale value and ; clock source

OPTION

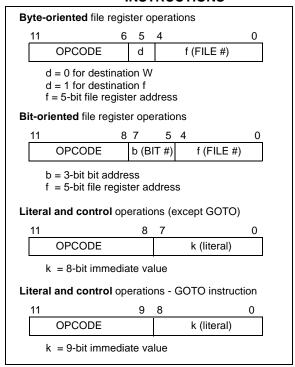

## 10.0 INSTRUCTION SET SUMMARY

Each PIC16C5X instruction is a 12-bit word divided into an OPCODE, which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16C5X instruction set summary in Table 10-2 groups the instructions into byte-oriented, bit-oriented, and literal and control operations. Table 10-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator is used to specify which one of the 32 file registers in that bank is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8 or 9-bit constant or literal value.

TABLE 10-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                     |

|---------------|-------------------------------------------------|

| f             | Register file address (0x00 to 0x1F)            |

| W             | Working register (accumulator)                  |

| b             | Bit address within an 8-bit file register       |

| k             | Literal field, constant data or label           |

| х             | Don't care location (= 0 or 1)                  |

|               | The assembler will generate code with $x = 0$ . |

|               | It is the recommended form of use for com-      |

|               | patibility with all Microchip software tools.   |

| d             | Destination select;                             |

|               | d = 0 (store result in W)                       |

|               | d = 1 (store result in file register 'f')       |

|               | Default is d = 1                                |

| label         | Label name                                      |

| TOS           | Top of Stack                                    |

| PC            | Program Counter                                 |

| WDT           | Watchdog Timer Counter                          |

| TO            | Time-out bit                                    |

| PD            | Power-down bit                                  |

| dest          | Destination, either the W register or the       |

|               | specified register file location                |

| [ ]           | Options                                         |

| ( )           | Contents                                        |

| $\rightarrow$ | Assigned to                                     |

| < >           | Register bit field                              |

| €             | In the set of                                   |

| italics       | User defined term (font is courier)             |

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time would be 1  $\mu s.$  If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time would be 2  $\mu s.$

Figure 10-1 shows the three general formats that the instructions can have. All examples in the figure use the following format to represent a hexadecimal number:

0xhhh

where 'h' signifies a hexadecimal digit.

# FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

## 11.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC MCUs and can be used to develop for this and other PIC microcontrollers. The MPLAB ICD utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming™ protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

## 11.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in Stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In Stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC devices. It can also set code protection in this mode.

# 11.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

# 11.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

# 11.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the I<sup>2</sup>C<sup>TM</sup> bus and separate headers for connection to an LCD module and a keypad.

NOTES:

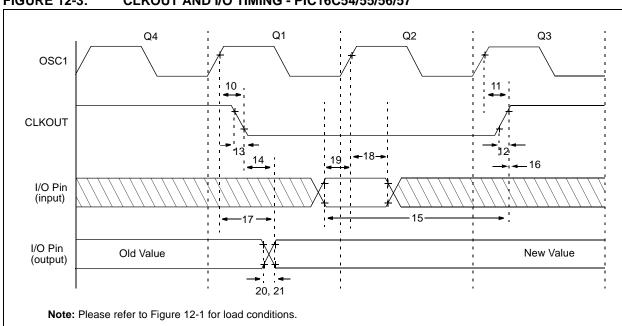

FIGURE 12-3: CLKOUT AND I/O TIMING - PIC16C54/55/56/57

TABLE 12-2: CLKOUT AND I/O TIMING REQUIREMENTS - PIC16C54/55/56/57

| AC Chara     | acteristics | Standard Operating Conditions (unless otherwise specified)  Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |              |      |      |       |  |  |  |

|--------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|-------|--|--|--|

| Param<br>No. | Symbol      | Characteristic                                                                                                                                                                                                                                   | Min          | Typ† | Max  | Units |  |  |  |

| 10           | TosH2ckL    | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                                                                                                                                                                                                                  | _            | 15   | 30** | ns    |  |  |  |

| 11           | TosH2ckH    | OSC1↑ to CLKOUT↑ <sup>(1)</sup>                                                                                                                                                                                                                  | _            | 15   | 30** | ns    |  |  |  |

| 12           | TckR        | CLKOUT rise time <sup>(1)</sup>                                                                                                                                                                                                                  | _            | 5.0  | 15** | ns    |  |  |  |

| 13           | TckF        | CLKOUT fall time <sup>(1)</sup>                                                                                                                                                                                                                  | _            | 5.0  | 15** | ns    |  |  |  |

| 14           | TckL2ioV    | CLKOUT↓ to Port out valid <sup>(1)</sup>                                                                                                                                                                                                         | _            | _    | 40** | ns    |  |  |  |

| 15           | TioV2ckH    | Port in valid before CLKOUT <sup>(1)</sup>                                                                                                                                                                                                       | 0.25 TCY+30* | _    | _    | ns    |  |  |  |

| 16           | TckH2ioI    | Port in hold after CLKOUT <sup>↑(1)</sup>                                                                                                                                                                                                        | 0*           | _    | _    | ns    |  |  |  |

| 17           | TosH2ioV    | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(2)</sup>                                                                                                                                                                                    | _            | _    | 100* | ns    |  |  |  |

| 18           | TosH2ioI    | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid (I/O in hold time)                                                                                                                                                                            | TBD          | _    | _    | ns    |  |  |  |

| 19           | TioV2osH    | Port input valid to OSC1↑ (I/O in setup time)                                                                                                                                                                                                    | TBD          | _    | _    | ns    |  |  |  |

| 20           | TioR        | Port output rise time <sup>(2)</sup>                                                                                                                                                                                                             | _            | 10   | 25** | ns    |  |  |  |

| 21           | TioF        | Port output fall time <sup>(2)</sup>                                                                                                                                                                                                             | _            | 10   | 25** | ns    |  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

**Note 1:** Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

2: Please refer to Figure 12-1 for load conditions.

<sup>\*\*</sup> These parameters are design targets and are not tested. No characterization data available at this time.

<sup>†</sup> Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

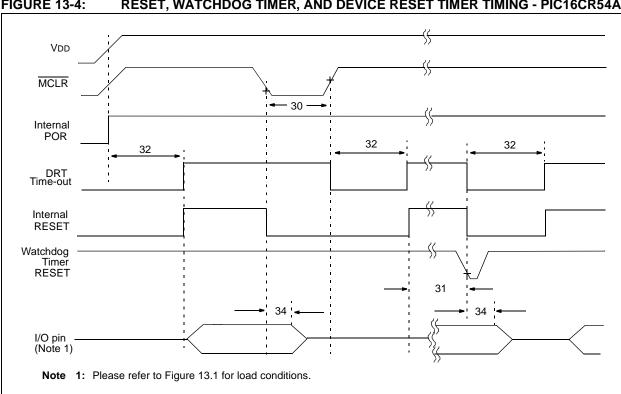

**FIGURE 13-4:** RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16CR54A

**TABLE 13-3:** RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16CR54A

| AC Characteristics  |      | Standard Operating Conditions (unless otherwise specified)  Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |      |      |       |                   |  |  |

|---------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|-------------------|--|--|

| Param<br>No. Symbol |      | Characteristic                                                                                                                                                                                                                                   | Min  | Тур† | Max  | Units | Conditions        |  |  |

| 30                  | TmcL | MCLR Pulse Width (low)                                                                                                                                                                                                                           | 1.0* | _    |      | μS    | VDD = 5.0V        |  |  |

| 31                  | Twdt | Watchdog Timer Time-out Period (No Prescaler)                                                                                                                                                                                                    | 7.0* | 18*  | 40*  | ms    | VDD = 5.0V (Comm) |  |  |

| 32                  | TDRT | Device Reset Timer Period                                                                                                                                                                                                                        | 7.0* | 18*  | 30*  | ms    | VDD = 5.0V (Comm) |  |  |

| 34                  | Tioz | I/O Hi-impedance from MCLR Low                                                                                                                                                                                                                   | _    | _    | 1.0* | μS    |                   |  |  |

These parameters are characterized but not tested.

Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

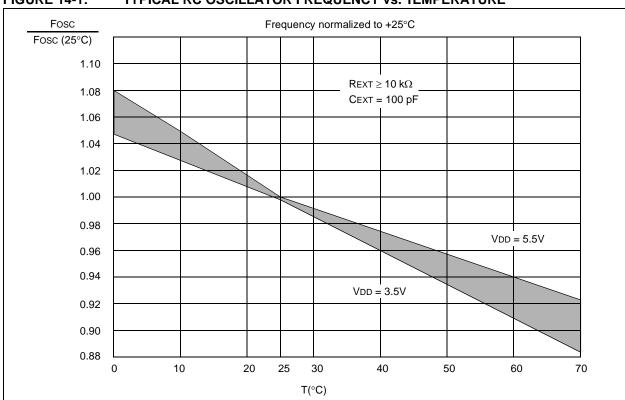

## 14.0 DEVICE CHARACTERIZATION - PIC16C54A

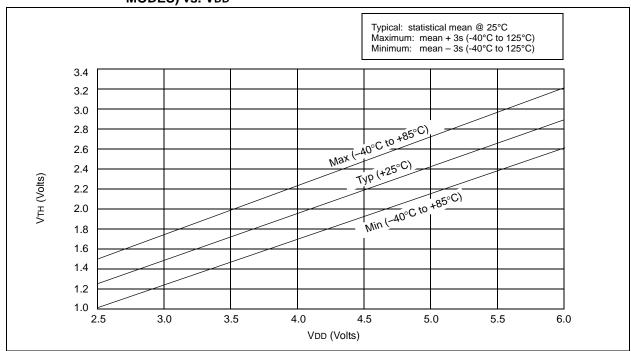

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

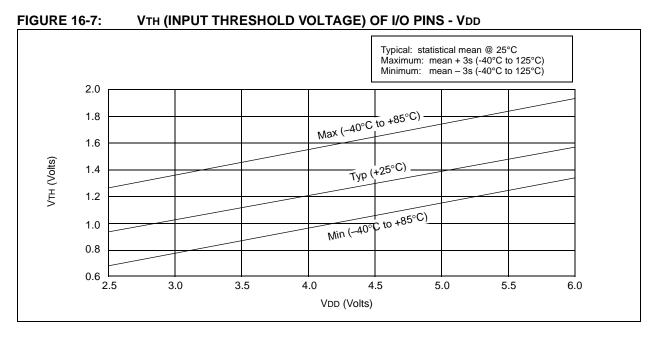

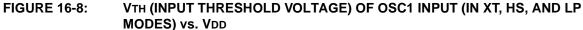

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean –  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

FIGURE 14-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

TABLE 14-1: RC OSCILLATOR FREQUENCIES

| Сехт   | REXT | Aver<br>Fosc @ 5 | •     |

|--------|------|------------------|-------|

| 20 pF  | 3.3K | 5 MHz            | ± 27% |

|        | 5K   | 3.8 MHz          | ± 21% |

|        | 10K  | 2.2 MHz          | ± 21% |

|        | 100K | 262 kHz          | ± 31% |

| 100 pF | 3.3K | 1.6 MHz          | ± 13% |

|        | 5K   | 1.2 MHz          | ± 13% |

|        | 10K  | 684 kHz          | ± 18% |

|        | 100K | 71 kHz           | ± 25% |

| 300 pF | 3.3K | 660 kHz          | ± 10% |

|        | 5.0K | 484 kHz          | ± 14% |

|        | 10K  | 267 kHz          | ± 15% |

|        | 100K | 29 kHz           | ± 19% |

The frequencies are measured on DIP packages.

The percentage variation indicated here is part-to-part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviations from the average value for VDD = 5V.

# 15.3 DC Characteristics: PIC16LV54A-02 (Commercial) PIC16LV54A-02I (Industrial)

| PIC16L       | .V54A-02<br>.V54A-02I<br>mercial, Ir | Standard Operating Conditions (unless otherwise specified) Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-20^{\circ}C \le TA \le +85^{\circ}C$ for industrial |       |                    |                 |                |                                                                                                                |

|--------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|-----------------|----------------|----------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol                               | Characteristic                                                                                                                                                                             | Min   | Тур†               | Max             | Units          | Conditions                                                                                                     |

| D001         | VDD                                  | Supply Voltage<br>RC and XT modes                                                                                                                                                          | 2.0   | _                  | 3.8             | V              |                                                                                                                |

| D002         | VDR                                  | RAM Data Retention<br>Voltage <sup>(1)</sup>                                                                                                                                               | _     | 1.5*               | _               | V              | Device in SLEEP mode                                                                                           |

| D003         | VPOR                                 | VDD Start Voltage to ensure Power-on Reset                                                                                                                                                 | _     | Vss                | _               | V              | See Section 5.1 for details on Power-on Reset                                                                  |

| D004         | SVDD                                 | VDD Rise Rate to ensure<br>Power-on Reset                                                                                                                                                  | 0.05* | _                  | _               | V/ms           | See Section 5.1 for details on<br>Power-on Reset                                                               |

| D010         | IDD                                  | Supply Current <sup>(2)</sup> RC <sup>(3)</sup> and XT modes LP mode, Commercial LP mode, Industrial                                                                                       |       | 0.5<br>11<br>14    | <br>27<br>35    | mA<br>μA<br>μA | Fosc = 2.0 MHz, VDD = 3.0V<br>Fosc = 32 kHz, VDD = 2.5V WDT disabled<br>Fosc = 32 kHz, VDD = 2.5V WDT disabled |

| D020         | IPD                                  | Power-down Current <sup>(2,4)</sup> Commercial Commercial Industrial                                                                                                                       |       | 2.5<br>0.25<br>3.5 | 12<br>4.0<br>14 | μΑ<br>μΑ<br>μΑ | VDD = 2.5V, WDT enabled<br>VDD = 2.5V, WDT disabled<br>VDD = 2.5V, WDT enabled                                 |

|              |                                      | Industrial                                                                                                                                                                                 | _     | 0.3                | 5.0             | μ <b>A</b>     | VDD = 2.5V, WDT disabled                                                                                       |

<sup>\*</sup> These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode <u>are: OSC1 = external square</u> wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in  $k\Omega$ .

- **4:** The oscillator start-up time can be as much as 8 seconds for XT and LP oscillator selection on wake-up from SLEEP mode or during initial power-up.

Typical: statistical mean @ 25°C Maximum: mean + 3s (-40°C to 125°C) Minimum: mean - 3s (-40°C to 125°C) 10000 1000 IDD (μA) 100 5.5V 5.0V 4.5V 3.0V <u>—</u> 2.5V — 10 0.01 0.1 Freq (MHz)

TYPICAL IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 300 PF, 25°C) FIGURE 16-14:

FIGURE 16-15: MAXIMUM IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 300 PF, -40°C to +85°C)

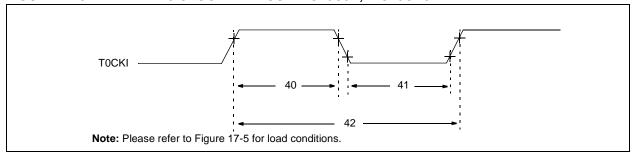

## FIGURE 17-9: TIMERO CLOCK TIMINGS - PIC16C5X, PIC16CR5X

TABLE 17-4: TIMERO CLOCK REQUIREMENTS - PIC16C5X, PIC16CR5X

|              | Standard Operating Conditions (unless otherwise specified) |                                       |                                                                                                                                                                     |      |     |       |                                                                |  |  |  |

|--------------|------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|----------------------------------------------------------------|--|--|--|

| A            | AC Chara                                                   | cteristics Operating Tempera          | ture $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |     |       |                                                                |  |  |  |

| Param<br>No. | Symbol                                                     | Characteristic                        | Min                                                                                                                                                                 | Тур† | Max | Units | Conditions                                                     |  |  |  |

| 40           | Tt0H                                                       | T0CKI High Pulse Width - No Prescaler | 0.5 Tcy + 20*                                                                                                                                                       | _    | _   | ns    |                                                                |  |  |  |

|              |                                                            | - With Prescaler                      | 10*                                                                                                                                                                 | _    | _   | ns    |                                                                |  |  |  |

| 41           | TtOL                                                       | T0CKI Low Pulse Width - No Prescaler  | 0.5 Tcy + 20*                                                                                                                                                       | _    | _   | ns    |                                                                |  |  |  |

|              |                                                            | - With Prescaler                      | 10*                                                                                                                                                                 | _    | _   | ns    |                                                                |  |  |  |

| 42           | Tt0P                                                       | T0CKI Period                          | 20 or <u>Tcy + 40</u> *<br>N                                                                                                                                        | _    | _   | ns    | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |  |  |  |

These parameters are characterized but not tested.

<sup>†</sup> Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

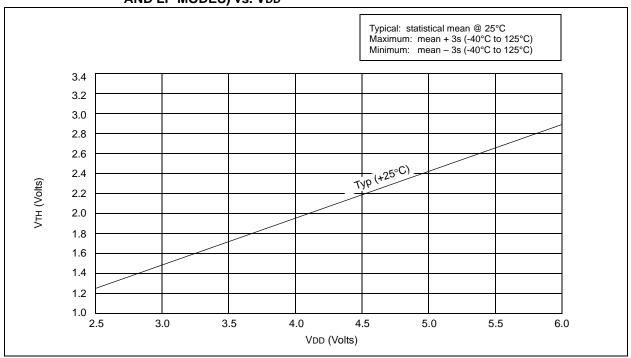

FIGURE 18-10: VTH (INPUT THRESHOLD TRIP POINT VOLTAGE) OF OSC1 INPUT (IN XT, HS AND LP MODES) vs. VDD

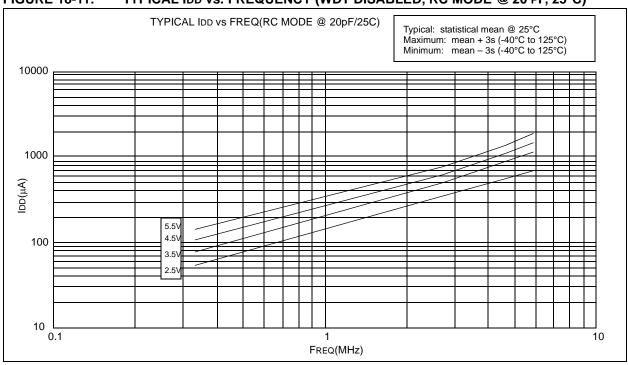

FIGURE 18-11: TYPICAL IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 20 pF, 25°C)

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 1997-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769355

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.