Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 1.5KB (1K x 12)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 25 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c56a-20-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C5X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C5X uses a Harvard architecture in which program and data are accessed on separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched on the same bus. Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 12 bits wide making it possible to have all single word instructions. A 12-bit wide program memory access bus fetches a 12-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (33) execute in a single cycle except for program branches.

The PIC16C54/CR54 and PIC16C55 address 512 x 12 of program memory, the PIC16C56/CR56 address 1K x 12 of program memory, and the PIC16C57/CR57 and PIC16C58/CR58 address 2K x 12 of program memory. All program memory is internal.

The PIC16C5X can directly or indirectly address its register files and data memory. All special function registers including the program counter are mapped in the data memory. The PIC16C5X has a highly orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C5X simple yet efficient. In addition, the learning curve is reduced significantly. The PIC16C5X device contains an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8 bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the W (working) register. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBWF and ADDWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with the corresponding device pins described in Table 3-1 (for PIC16C54/56/58) and Table 3-2 (for PIC16C55/57).

# 4.0 OSCILLATOR CONFIGURATIONS

## 4.1 Oscillator Types

PIC16C5Xs can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

- 1. LP: Low Power Crystal

- 2. XT: Crystal/Resonator

- 3. HS: High Speed Crystal/Resonator

- 4. RC: Resistor/Capacitor

**Note:** Not all oscillator selections available for all parts. See Section 9.1.

## 4.2 Crystal Oscillator/Ceramic Resonators

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 4-1). The PIC16C5X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source drive the OSC1/CLKIN pin (Figure 4-2).

### FIGURE 4-1: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

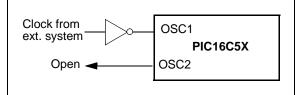

FIGURE 4-2:

### EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

### TABLE 4-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS -PIC16C5X, PIC16CR5X

| Osc<br>Type | Resonator<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |

|-------------|-------------------|------------------|------------------|

| XT          | 455 kHz           | 68-100 pF        | 68-100 pF        |

|             | 2.0 MHz           | 15-33 pF         | 15-33 pF         |

|             | 4.0 MHz           | 10-22 pF         | 10-22 pF         |

| HS          | 8.0 MHz           | 10-22 pF         | 10-22 pF         |

|             | 16.0 MHz          | 10 pF            | 10 pF            |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

### TABLE 4-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR -PIC16C5X. PIC16CR5X

| Osc<br>Type | Crystal<br>Freq       | Cap.Range<br>C1 | Cap. Range<br>C2 |  |  |  |

|-------------|-----------------------|-----------------|------------------|--|--|--|

| LP          | 32 kHz <sup>(1)</sup> | 15 pF           | 15 pF            |  |  |  |

| XT          | 100 kHz               | 15-30 pF        | 200-300 pF       |  |  |  |

|             | 200 kHz               | 15-30 pF        | 100-200 pF       |  |  |  |

|             | 455 kHz               | 15-30 pF        | 15-100 pF        |  |  |  |

|             | 1 MHz                 | 15-30 pF        | 15-30 pF         |  |  |  |

|             | 2 MHz                 | 15 pF           | 15 pF            |  |  |  |

|             | 4 MHz                 | 15 pF           | 15 pF            |  |  |  |

| HS          | 4 MHz                 | 15 pF           | 15 pF            |  |  |  |

|             | 8 MHz                 | 15 pF           | 15 pF            |  |  |  |

|             | 20 MHz                | 15 pF           | 15 pF            |  |  |  |

# Note 1: For VDD > 4.5V, C1 = C2 $\approx$ 30 pF is recommended.

These values are for design guidance only. Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

**Note:** If you change from this device to another device, please verify oscillator characteristics in your application.

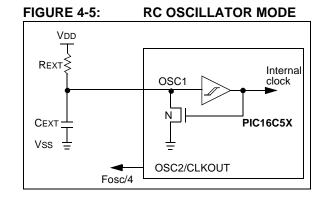

## 4.4 RC Oscillator

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 4-5 shows how the R/C combination is connected to the PIC16C5X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ) the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

The Electrical Specifications sections show RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

Also, see the Electrical Specifications sections for variation of oscillator frequency due to VDD for given REXT/ CEXT values as well as frequency variation due to operating temperature for given R, C, and VDD values.

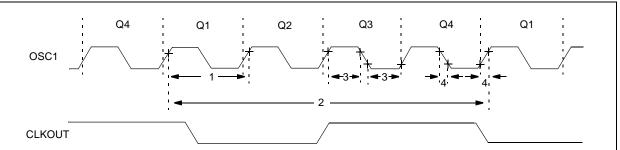

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic.

**Note:** If you change from this device to another device, please verify oscillator characteristics in your application.

### 6.5.1 PAGING CONSIDERATIONS – PIC16C56/CR56, PIC16C57/CR57 AND PIC16C58/CR58

If the Program Counter is pointing to the last address of a selected memory page, when it increments it will cause the program to continue in the next higher page. However, the page preselect bits in the STATUS Register will not be updated. Therefore, the next GOTO, CALL or modify PCL instruction will send the program to the page specified by the page preselect bits (PA0 or PA<1:0>).

For example, a NOP at location 1FFh (page 0) increments the PC to 200h (page 1). A GOTO xxx at 200h will return the program to address xxh on page 0 (assuming that PA<1:0> are clear).

To prevent this, the page preselect bits must be updated under program control.

### 6.5.2 EFFECTS OF RESET

The Program Counter is set upon a RESET, which means that the PC addresses the last location in the last page (i.e., the RESET vector).

The STATUS Register page preselect bits are cleared upon a RESET, which means that page 0 is pre-selected.

Therefore, upon a RESET, a GOTO instruction at the RESET vector location will automatically cause the program to jump to page 0.

### 6.6 Stack

PIC16C5X devices have a 10-bit or 11-bit wide, two-level hardware push/pop stack.

A CALL instruction will push the current value of stack 1 into stack 2 and then push the current program counter value, incremented by one, into stack level 1. If more than two sequential CALL's are executed, only the most recent two return addresses are stored.

A RETLW instruction will pop the contents of stack level 1 into the program counter and then copy stack level 2 contents into level 1. If more than two sequential RETLW's are executed, the stack will be filled with the address previously stored in level 2. Note that the W Register will be loaded with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

For the RETLW instruction, the PC is loaded with the Top of Stack (TOS) contents. All of the devices covered in this data sheet have a two-level stack. The stack has the same bit width as the device PC, therefore, paging is not an issue when returning from a subroutine.

## 7.6 I/O Programming Considerations

### 7.6.1 BI-DIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU, bit5 to be set and the PORTB value to be written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (say bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit0 is switched into Output mode later on, the content of the data latch may now be unknown.

Example 7-1 shows the effect of two sequential read-modify-write instructions (e.g., BCF, BSF, etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

### EXAMPLE 7-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT Settings

; PORTB<7:4> Inputs

; PORTB<3:0> Outputs

;PORTB<7:6> have external pull-ups and are

;not connected to other circuitry

;

| ; |       |        |   | PORT  | latch | PORT | pins |

|---|-------|--------|---|-------|-------|------|------|

| ; |       |        |   |       |       |      |      |

|   | BCF   | PORTB, | 7 | ;01pp | pppp  | 11pp | pppp |

|   | BCF   | PORTB, | 6 | ;10pp | pppp  | 11pp | pppp |

|   | MOVLW | H'3F'  |   | ;     |       |      |      |

|   | TRIS  | PORTB  |   | ;10pp | pppp  | 10pp | pppp |

| ; |       |        |   |       |       |      |      |

;Note that the user may have expected the pin ;values to be 00pp pppp. The 2nd BCF caused ;RB7 to be latched as the pin value (High).

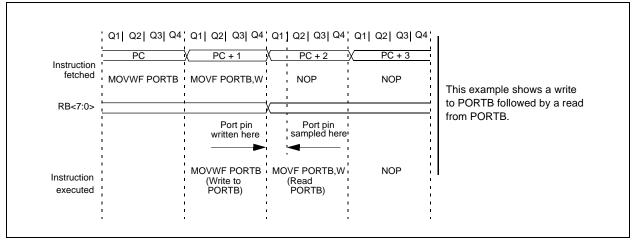

### 7.6.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 7-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

### FIGURE 7-2: SUCCESSIVE I/O OPERATION

### 8.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer (WDT), respectively (Section 9.2.1). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT, but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the WDT, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a RESET, the prescaler contains all '0's.

### 8.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 8-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

### EXAMPLE 8-1: CHANGING PRESCALER (TIMER0→WDT)

| CLRWDT            | ;Clear WDT              |

|-------------------|-------------------------|

| CLRF TMR0         | Clear TMR0 & Prescaler  |

| MOVLW B'00xx1111' | ;Last 3 instructions in |

|                   | this example            |

| OPTION            | ;are required only if   |

|                   | ;desired                |

| CLRWDT            | ;PS<2:0> are 000 or     |

|                   | ;001                    |

| MOVLW B'00xx1xxx' | ;Set Prescaler to       |

| OPTION            | ;desired WDT rate       |

|                   |                         |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 8-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

# EXAMPLE 8-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| MOVLW  | B'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

|        |             | ;clock source       |

OPTION

#### CONFIGURATION WORD FOR PIC16C54/C55/C56/C57 **REGISTER 9-2:**

|           |            |             |              |            |                     |             | İ         | СР      | WDTE        | FOSC1      | FOSC0   |

|-----------|------------|-------------|--------------|------------|---------------------|-------------|-----------|---------|-------------|------------|---------|

|           |            | _           | _            | _          |                     |             |           | CP      | WDIE        | FUSCI      |         |

| bit 11    |            |             |              |            |                     |             |           |         |             |            | bit 0   |

|           |            |             |              |            |                     |             |           |         |             |            |         |

| bit 11-4: | Unimple    | mented      | Read as '    | 0'         |                     |             |           |         |             |            |         |

| bit 3:    | CP: Cod    | e protecti  | on bit.      |            |                     |             |           |         |             |            |         |

|           |            | e protecti  |              |            |                     |             |           |         |             |            |         |

|           | 0 = Code   | e protectio | on on        |            |                     |             |           |         |             |            |         |

| bit 2:    | WDTE: \    | Vatchdog    | timer ena    | ble bit    |                     |             |           |         |             |            |         |

|           | 1 = WDT    | enabled     |              |            |                     |             |           |         |             |            |         |

|           | 0 = WDT    | disabled    |              |            |                     |             |           |         |             |            |         |

| bit 1-0:  | FOSC1:I    | FOSC0: (    | Oscillator s | election b | oits <sup>(2)</sup> |             |           |         |             |            |         |

|           | 00 = LF    | oscillato   | or           |            |                     |             |           |         |             |            |         |

|           | 01 = X     | T oscillato | or           |            |                     |             |           |         |             |            |         |

|           |            | S oscillato |              |            |                     |             |           |         |             |            |         |

|           | 11 = R     | C oscillate | or           |            |                     |             |           |         |             |            |         |

| Note 1.   | Refer to t | ha PIC16    | C5X Prog     | rammina    | Specificat          | ions (Liter | atura Num | her DS3 | 190) to d   | otormino l | now to  |

|           |            |             | iration wor  | 0          | opeemear            |             |           |         | , 100) to u |            | 1011 10 |

| 2:        |            | •           | orts XT, R   |            | oscillator          | onlv.       |           |         |             |            |         |

|           |            |             |              |            |                     | - 1         |           |         |             |            |         |

| Legend:   |            |             |              |            |                     |             |           |         |             |            |         |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared        | x = bit is unknown |

NOTES:

# PIC16C5X

| COMF                                                 | Complement f                                                                                                                                                          |  |  |  |  |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                              | [label] COMF f,d                                                                                                                                                      |  |  |  |  |

| Operands:                                            | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                            |  |  |  |  |

| Operation:                                           | $(\overline{f}) \rightarrow (dest)$                                                                                                                                   |  |  |  |  |

| Status Affected:                                     | Z                                                                                                                                                                     |  |  |  |  |

| Encoding:                                            | 0010 01df ffff                                                                                                                                                        |  |  |  |  |

| Description:                                         | The contents of register 'f' are<br>complemented. If 'd' is 0 the result<br>is stored in the W register. If 'd' is 1<br>the result is stored back in<br>register 'f'. |  |  |  |  |

| Words:                                               | 1                                                                                                                                                                     |  |  |  |  |

| Cycles:                                              | 1                                                                                                                                                                     |  |  |  |  |

| Example:                                             | COMF REG1,0                                                                                                                                                           |  |  |  |  |

| Before Instru<br>REG1<br>After Instruct<br>REG1<br>W | = 0x13                                                                                                                                                                |  |  |  |  |

| DECF                                                    | Decrement f                                                    |                         |      |            |  |  |

|---------------------------------------------------------|----------------------------------------------------------------|-------------------------|------|------------|--|--|

| Syntax:                                                 | [ label ]                                                      | DECF f,                 | d    |            |  |  |

| Operands:                                               | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$ |                         |      |            |  |  |

| Operation:                                              | $(f) - 1 \rightarrow$                                          | (dest)                  |      |            |  |  |

| Status Affected:                                        | Z                                                              |                         |      |            |  |  |

| Encoding:                                               | 0000                                                           | 11df                    | ffff |            |  |  |

| Description:                                            | Decreme<br>result is s<br>'d' is 1 th<br>register 'f           | stored in the result is |      | jister. If |  |  |

| Words:                                                  | 1                                                              |                         |      |            |  |  |

| Cycles:                                                 | 1                                                              |                         |      |            |  |  |

| Example:                                                | DECF                                                           | CNT,                    | 1    |            |  |  |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0<br>= 0<br>ion                                              | <01                     |      |            |  |  |

| DECFSZ                                                | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                               | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                        |

| Operands:                                             | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                                |

| Operation:                                            | (f) $-1 \rightarrow d$ ; skip if result = 0                                                                                                                                                                                                                                                                                               |

| Status Affected:                                      | None                                                                                                                                                                                                                                                                                                                                      |

| Encoding:                                             | 0010 11df ffff                                                                                                                                                                                                                                                                                                                            |

| Description:                                          | The contents of register 'f' are dec-<br>remented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded and a NOP is executed<br>instead making it a two-cycle<br>instruction. |

| Words:                                                | 1                                                                                                                                                                                                                                                                                                                                         |

| Cycles:                                               | 1(2)                                                                                                                                                                                                                                                                                                                                      |

| Example:                                              | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                        |

| Before Instru<br>PC                                   | = address (HERE)                                                                                                                                                                                                                                                                                                                          |

| After Instruct<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC | tion<br>= CNT - 1;<br>= 0,<br>= address (CONTINUE);<br>≠ 0,<br>= address (HERE+1)                                                                                                                                                                                                                                                         |

| GOTO                   | Unconditional Branch                                                                                                                                                                        |         |          |  |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|--|--|--|

| Syntax:                | [ label ]                                                                                                                                                                                   | GOTO    | k        |  |  |  |

| Operands:              | $0 \le k \le 5^{-1}$                                                                                                                                                                        | 11      |          |  |  |  |

| Operation:             | $k \rightarrow PC < STATUS$                                                                                                                                                                 | ,       | PC<10:9> |  |  |  |

| Status Affected:       | None                                                                                                                                                                                        |         |          |  |  |  |

| Encoding:              | 101k                                                                                                                                                                                        | kkkk    | kkkk     |  |  |  |

| Description:           | GOTO is an unconditional branch.<br>The 9-bit immediate value is<br>loaded into PC bits <8:0>. The<br>upper bits of PC are loaded from<br>STATUS<6:5>. GOTO is a two-<br>cycle instruction. |         |          |  |  |  |

| Words:                 | 1                                                                                                                                                                                           |         |          |  |  |  |

| Cycles:                | 2                                                                                                                                                                                           |         |          |  |  |  |

| Example:               | GOTO TH                                                                                                                                                                                     | IERE    |          |  |  |  |

| After Instruct<br>PC = | ion<br>address                                                                                                                                                                              | G (THER | E)       |  |  |  |

| INCF                                                    | Increment f                                                                                                                                                          |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                 | [label] INCF f,d                                                                                                                                                     |

| Operands:                                               | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                                     |

| Operation:                                              | (f) + 1 $\rightarrow$ (dest)                                                                                                                                         |

| Status Affected:                                        | Z                                                                                                                                                                    |

| Encoding:                                               | 0010 10df ffff                                                                                                                                                       |

| Description:                                            | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |

| Words:                                                  | 1                                                                                                                                                                    |

| Cycles:                                                 | 1                                                                                                                                                                    |

| Example:                                                | INCF CNT, 1                                                                                                                                                          |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0xFF<br>= 0                                                                                                                                                        |

| INCFSZ                                | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                               | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                          |

| Operands:                             | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                                  |

| Operation:                            | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                                            |

| Status Affected:                      | None                                                                                                                                                                                                                                                                                                                                        |

| Encoding:                             | 0011 11df ffff                                                                                                                                                                                                                                                                                                                              |

| Description:                          | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'.<br>If the result is 0, then the next<br>instruction, which is already<br>fetched, is discarded and a NOP is<br>executed instead making it a two-<br>cycle instruction. |

| Words:                                | 1                                                                                                                                                                                                                                                                                                                                           |

| Cycles:                               | 1(2)                                                                                                                                                                                                                                                                                                                                        |

| Example:                              | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•<br>•                                                                                                                                                                                                                                                                                     |

| Before Instru<br>PC<br>After Instruct | = address (HERE)                                                                                                                                                                                                                                                                                                                            |

| CNT<br>if CNT<br>PC<br>if CNT<br>PC   | <pre>= CNT + 1;<br/>= 0,<br/>= address (CONTINUE);<br/>≠ 0,<br/>= address (HERE +1)</pre>                                                                                                                                                                                                                                                   |

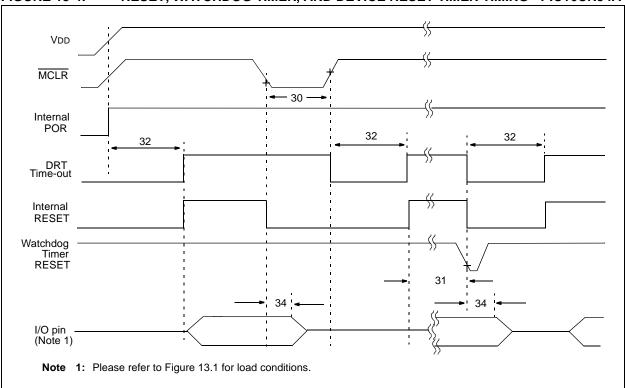

### FIGURE 13-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16CR54A

### TABLE 13-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16CR54A

| $\begin{tabular}{ c c c c c } \hline AC \ Characteristics \end{tabular} $$ $ $ $ $ $ $ $ $ $ $ $ $ $ $ $ $ $ $ |        |                                                  |      |      |      |       |                   |

|----------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------|------|------|------|-------|-------------------|

| Param<br>No.                                                                                                   | Symbol | Characteristic                                   | Min  | Тур† | Max  | Units | Conditions        |

| 30                                                                                                             | TmcL   | MCLR Pulse Width (low)                           | 1.0* |      |      | μS    | VDD = 5.0V        |

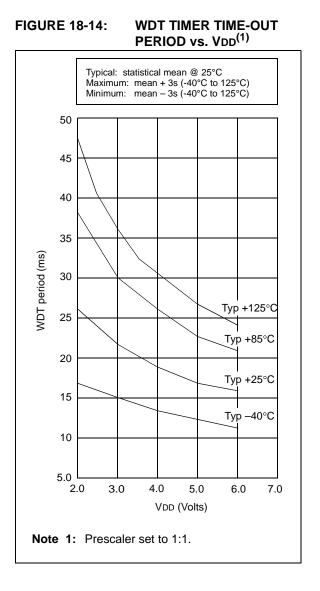

| 31                                                                                                             | Twdt   | Watchdog Timer Time-out Period<br>(No Prescaler) | 7.0* | 18*  | 40*  | ms    | VDD = 5.0V (Comm) |

| 32                                                                                                             | Tdrt   | Device Reset Timer Period                        | 7.0* | 18*  | 30*  | ms    | VDD = 5.0V (Comm) |

| 34                                                                                                             | Tioz   | I/O Hi-impedance from MCLR Low                   |      |      | 1.0* | μS    |                   |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C5X

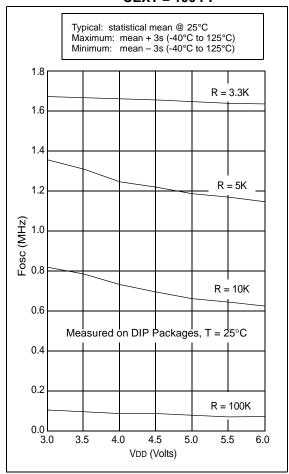

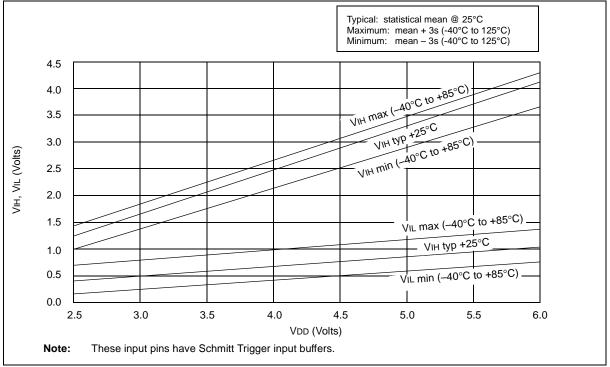

# **FIGURE 14-2: TYPICAL RC OSC** FREQUENCY vs. VDD, CEXT = 20 PF Typical: statistical mean @ 25°C Maximum: mean + 3s (-40°C to 125°C) Minimum: mean – 3s (-40°C to 125°C) 5.5 R = 3.3K5.0 4.5 R = 5K 4.0 3.5 Fosc (MHz) 3.0 R = 10K 2.5 2.0 Measured on DIP Packages, $T = 25^{\circ}C$ 1.5 1.0 R = 100K 0.5 0.0 3.0 3.5 4.0 4.5 5.0 5.5 6.0 VDD (Volts)

### FIGURE 14-3:

### TYPICAL RC OSC FREQUENCY vs. VDD, CEXT = 100 PF

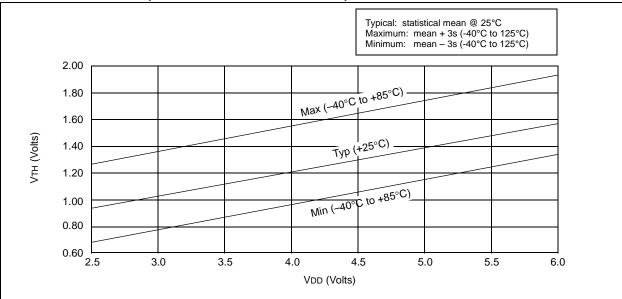

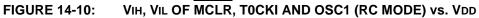

### FIGURE 14-9: VTH (INPUT THRESHOLD VOLTAGE) OF I/O PINS vs. VDD

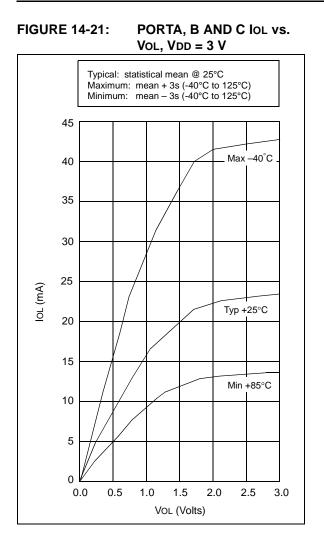

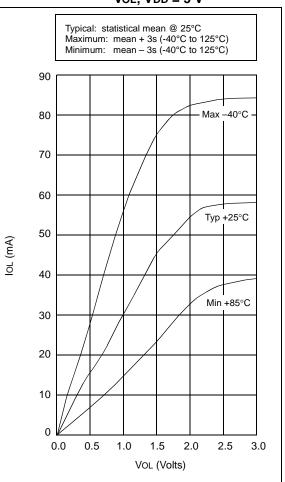

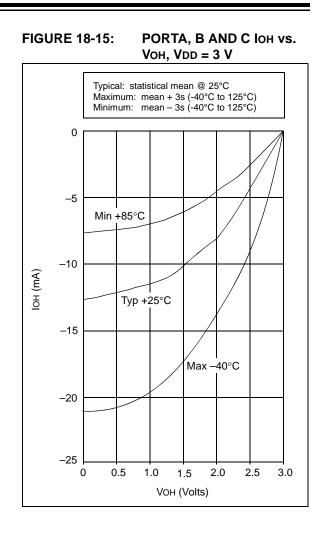

### FIGURE 14-22: PORTA, B AND C IOL vs. VoL, VDD = 5 V

### TABLE 14-2: INPUT CAPACITANCE FOR PIC16C54/56

| Pin         | Typical Capacitance (pF) |          |  |  |

|-------------|--------------------------|----------|--|--|

| F111        | 18L PDIP                 | 18L SOIC |  |  |

| RA port     | 5.0                      | 4.3      |  |  |

| RB port     | 5.0                      | 4.3      |  |  |

| MCLR        | 17.0                     | 17.0     |  |  |

| OSC1        | 4.0                      | 3.5      |  |  |

| OSC2/CLKOUT | 4.3                      | 3.5      |  |  |

| T0CKI       | 3.2                      | 2.8      |  |  |

All capacitance values are typical at  $25^{\circ}$ C. A part-to-part variation of ±25% (three standard deviations) should be taken into account.

| TABLE 14-3: | INPUT CAPACITANCE FOR |

|-------------|-----------------------|

|             | PIC16C55/57           |

|             | Typical Capacitance (pF) |          |  |  |

|-------------|--------------------------|----------|--|--|

| Pin         | 28L PDIP<br>(600 mil)    | 28L SOIC |  |  |

| RA port     | 5.2                      | 4.8      |  |  |

| RB port     | 5.6                      | 4.7      |  |  |

| RC port     | 5.0                      | 4.1      |  |  |

| MCLR        | 17.0                     | 17.0     |  |  |

| OSC1        | 6.6                      | 3.5      |  |  |

| OSC2/CLKOUT | 4.6                      | 3.5      |  |  |

| T0CKI       | 4.5                      | 3.5      |  |  |

All capacitance values are typical at  $25^{\circ}$ C. A part-to-part variation of ±25% (three standard deviations) should be taken into account.

### 17.5 Timing Diagrams and Specifications

#### FIGURE 17-6: EXTERNAL CLOCK TIMING - PIC16C5X, PIC16CR5X

### TABLE 17-1: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16C5X, PIC16CR5X

| AC Characteristics |        | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |      |      |       |       |                  |

|--------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------|------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                                                                                                                                                                                                                   | Min  | Тур† | Max   | Units | Conditions       |

|                    | Fosc   | External CLKIN Frequency <sup>(1)</sup>                                                                                                                                                                                                                                                                                          | DC   | _    | 4.0   | MHz   | XT osc mode      |

|                    |        |                                                                                                                                                                                                                                                                                                                                  | DC   | —    | 4.0   | MHz   | HS osc mode (04) |

|                    |        |                                                                                                                                                                                                                                                                                                                                  | DC   | —    | 20    | MHz   | HS osc mode (20) |

|                    |        |                                                                                                                                                                                                                                                                                                                                  | DC   | —    | 200   | kHz   | LP OSC mode      |

|                    |        | Oscillator Frequency <sup>(1)</sup>                                                                                                                                                                                                                                                                                              | DC   | —    | 4.0   | MHz   | RC osc mode      |

|                    |        |                                                                                                                                                                                                                                                                                                                                  | 0.45 | —    | 4.0   | MHz   | XT osc mode      |

|                    |        |                                                                                                                                                                                                                                                                                                                                  | 4.0  | —    | 4.0   | MHz   | HS osc mode (04) |

|                    |        |                                                                                                                                                                                                                                                                                                                                  | 4.0  | —    | 20    | MHz   | HS osc mode (20) |

|                    |        |                                                                                                                                                                                                                                                                                                                                  | 5.0  |      | 200   | kHz   | LP OSC mode      |

| 1                  | Tosc   | External CLKIN Period <sup>(1)</sup>                                                                                                                                                                                                                                                                                             | 250  | —    | —     | ns    | XT osc mode      |

|                    |        |                                                                                                                                                                                                                                                                                                                                  | 250  | —    | —     | ns    | HS osc mode (04) |

|                    |        |                                                                                                                                                                                                                                                                                                                                  | 50   | —    | —     | ns    | HS osc mode (20) |

|                    |        |                                                                                                                                                                                                                                                                                                                                  | 5.0  |      | —     | μS    | LP OSC mode      |

|                    |        | Oscillator Period <sup>(1)</sup>                                                                                                                                                                                                                                                                                                 | 250  | —    | —     | ns    | RC osc mode      |

|                    |        |                                                                                                                                                                                                                                                                                                                                  | 250  | —    | 2,200 | ns    | XT osc mode      |

|                    |        |                                                                                                                                                                                                                                                                                                                                  | 250  | —    | 250   | ns    | HS osc mode (04) |

|                    |        |                                                                                                                                                                                                                                                                                                                                  | 50   | —    | 250   | ns    | HS osc mode (20) |

|                    |        |                                                                                                                                                                                                                                                                                                                                  | 5.0  | —    | 200   | μS    | LP osc mode      |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption.

When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

**2:** Instruction cycle period (TCY) equals four times the input oscillator time base period.

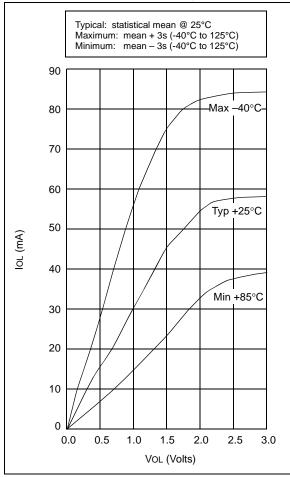

### FIGURE 20-9: IOL vs. VOL, VDD = 5 V

# Package Marking Information (Cont'd)

18-Lead CERDIP Windowed

|  | XXXXXXXX<br>XXXXXXXX<br>YYWWNNN |

|--|---------------------------------|

|--|---------------------------------|

### 28-Lead CERDIP Windowed

Example

### Example

| Lege | end: XX?<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | <ul> <li>Customer-specific information<br/>Year code (last digit of calendar year)<br/>Year code (last 2 digits of calendar year)<br/>Week code (week of January 1 is week '01')<br/>Alphanumeric traceability code<br/>Pb-free JEDEC designator for Matte Tin (Sn)<br/>This package is Pb-free. The Pb-free JEDEC designator (e3)<br/>can be found on the outer packaging for this package.</li> </ul> |

|------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note | be carr                                     | vent the full Microchip part number cannot be marked on one line, it will ied over to the next line, thus limiting the number of available ers for customer-specific information.                                                                                                                                                                                                                       |

# w

| W Register                 |        |

|----------------------------|--------|

| Value on reset             | 20     |

| Wake-up from SLEEP         | 19, 47 |

| Watchdog Timer (WDT)       | 43, 46 |

| Period                     |        |

| Programming Considerations |        |

| Register values on reset   |        |

| WWW, On-Line Support       |        |

| X                          |        |

| XORLW                      | 60     |

| XORWF                      |        |

| Z                          |        |

| Zero (Z) bit               | 9, 29  |