Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 1.5KB (1K x 12)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 25 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c56t-hsi-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

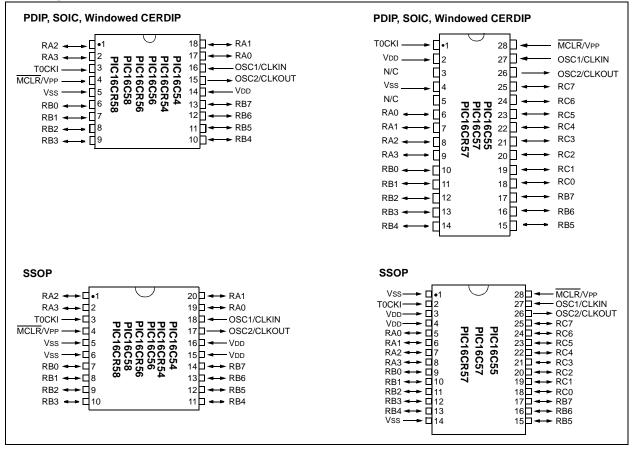

#### **Pin Diagrams**

## **Device Differences**

| Device     | Voltage<br>Range | Oscillator<br>Selection<br>(Program) | Oscillator | Process<br>Technology<br>(Microns) | ROM<br>Equivalent | MCLR<br>Filter |

|------------|------------------|--------------------------------------|------------|------------------------------------|-------------------|----------------|

| PIC16C54   | 2.5-6.25         | Factory                              | See Note 1 | 1.2                                | PIC16CR54A        | No             |

| PIC16C54A  | 2.0-6.25         | User                                 | See Note 1 | 0.9                                | —                 | No             |

| PIC16C54C  | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | PIC16CR54C        | Yes            |

| PIC16C55   | 2.5-6.25         | Factory                              | See Note 1 | 1.7                                | —                 | No             |

| PIC16C55A  | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | —                 | Yes            |

| PIC16C56   | 2.5-6.25         | Factory                              | See Note 1 | 1.7                                | —                 | No             |

| PIC16C56A  | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | PIC16CR56A        | Yes            |

| PIC16C57   | 2.5-6.25         | Factory                              | See Note 1 | 1.2                                | —                 | No             |

| PIC16C57C  | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | PIC16CR57C        | Yes            |

| PIC16C58B  | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | PIC16CR58B        | Yes            |

| PIC16CR54A | 2.5-6.25         | Factory                              | See Note 1 | 1.2                                | N/A               | Yes            |

| PIC16CR54C | 2.5-5.5          | Factory                              | See Note 1 | 0.7                                | N/A               | Yes            |

| PIC16CR56A | 2.5-5.5          | Factory                              | See Note 1 | 0.7                                | N/A               | Yes            |

| PIC16CR57C | 2.5-5.5          | Factory                              | See Note 1 | 0.7                                | N/A               | Yes            |

| PIC16CR58B | 2.5-5.5          | Factory                              | See Note 1 | 0.7                                | N/A               | Yes            |

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

**Note:** The table shown above shows the generic names of the PIC16C5X devices. For device varieties, please refer to Section 2.0.

# TABLE 1-1: PIC16C5X FAMILY OF DEVICES

| Features                         | PIC16C54                            | PIC16CR54                           | PIC16C55                            | PIC16C56                            | PIC16CR56                           |

|----------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Maximum Operation Frequency      | 40 MHz                              | 20 MHz                              | 40 MHz                              | 40 MHz                              | 20 MHz                              |

| EPROM Program Memory (x12 words) | 512                                 | _                                   | 512                                 | 1K                                  |                                     |

| ROM Program Memory (x12 words)   |                                     | 512                                 | _                                   | _                                   | 1K                                  |

| RAM Data Memory (bytes)          | 25                                  | 25                                  | 24                                  | 25                                  | 25                                  |

| Timer Module(s)                  | TMR0                                | TMR0                                | TMR0                                | TMR0                                | TMR0                                |

| I/O Pins                         | 12                                  | 12                                  | 20                                  | 12                                  | 12                                  |

| Number of Instructions           | 33                                  | 33                                  | 33                                  | 33                                  | 33                                  |

| Packages                         | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin DIP,<br>SOIC;<br>28-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP |

PIC16C58 Features **PIC16C57** PIC16CR57 PIC16CR58 Maximum Operation Frequency 20 MHz 40 MHz 40 MHz 20 MHz EPROM Program Memory (x12 words) 2K 2K \_\_\_\_ \_ ROM Program Memory (x12 words) 2K 2K \_ \_ RAM Data Memory (bytes) 72 72 73 73 Timer Module(s) TMR0 TMR0 TMR0 TMR0 I/O Pins 20 20 12 12 Number of Instructions 33 33 33 33 28-pin DIP, SOIC; 28-pin DIP, SOIC; 18-pin DIP, SOIC; 18-pin DIP, SOIC; Packages 28-pin SSOP 28-pin SSOP 20-pin SSOP 20-pin SSOP All PIC® Family devices have Power-on Reset, selectable Watchdog Timer, selectable Code Protect and high I/O current capability.

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C5X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C5X uses a Harvard architecture in which program and data are accessed on separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched on the same bus. Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 12 bits wide making it possible to have all single word instructions. A 12-bit wide program memory access bus fetches a 12-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (33) execute in a single cycle except for program branches.

The PIC16C54/CR54 and PIC16C55 address 512 x 12 of program memory, the PIC16C56/CR56 address 1K x 12 of program memory, and the PIC16C57/CR57 and PIC16C58/CR58 address 2K x 12 of program memory. All program memory is internal.

The PIC16C5X can directly or indirectly address its register files and data memory. All special function registers including the program counter are mapped in the data memory. The PIC16C5X has a highly orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C5X simple yet efficient. In addition, the learning curve is reduced significantly. The PIC16C5X device contains an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8 bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the W (working) register. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBWF and ADDWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with the corresponding device pins described in Table 3-1 (for PIC16C54/56/58) and Table 3-2 (for PIC16C55/57).

## 6.3 STATUS Register

This register contains the arithmetic status of the ALU, the RESET status and the page preselect bits for program memories larger than 512 words.

The STATUS Register can be the destination for any instruction, as with any other register. If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not

writable. Therefore, the result of an instruction with the STATUS Register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS Register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS Register because these instructions do not affect the Z, DC or C bits from the STATUS Register. For other instructions which do affect STATUS Bits, see Section 10.0, Instruction Set Summary.

## REGISTER 6-1: STATUS REGISTER (ADDRESS: 03h)

|          | R/W-0                                                                                                                               | R/W-0                              | R/W-0        | R-1          | R-1                        | R/W-x         | R/W-x          | R/W-x          |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------|--------------|----------------------------|---------------|----------------|----------------|--|--|

|          | PA2                                                                                                                                 | PA1                                | PA0          | TO           | PD                         | Z             | DC             | С              |  |  |

|          | bit 7                                                                                                                               |                                    |              |              |                            |               |                | bit 0          |  |  |

| bit 7:   | PA2: This bit                                                                                                                       | unused at th                       | is time.     |              |                            |               |                |                |  |  |

|          |                                                                                                                                     | A2 bit as a ge<br>with future pr   |              | e read/write | bit is not recor           | mmended, sir  | nce this may a | affect upward  |  |  |

| bit 6-5: |                                                                                                                                     |                                    |              | -            | CR56)(PIC16                |               |                | 58)            |  |  |

|          |                                                                                                                                     |                                    |              |              | 16C57/CR57,<br>16C57/CR57, |               |                |                |  |  |

|          |                                                                                                                                     | (400h - 5FFh                       |              |              |                            | FIC 10C30/C   | N00            |                |  |  |

|          | 11 = Page 3                                                                                                                         | (600h - 7FFh                       | •            |              |                            |               |                |                |  |  |

|          | Each page is                                                                                                                        |                                    | deperal pur  | ose read/wr  | ite bits in devi           | ices which do | not use them   | for program    |  |  |

|          |                                                                                                                                     |                                    |              |              | affect upward              |               |                |                |  |  |

| bit 4:   | TO: Time-ou                                                                                                                         |                                    |              | ,            | •                          |               |                |                |  |  |

|          |                                                                                                                                     | ver-up, CLRWI<br>ime-out occur     |              | , or sleep i | nstruction                 |               |                |                |  |  |

| bit 3:   | PD: Power-d                                                                                                                         | lown bit                           |              |              |                            |               |                |                |  |  |

|          | •                                                                                                                                   | ver-up or by tl<br>ution of the SI |              |              |                            |               |                |                |  |  |

| bit 2:   | Z: Zero bit                                                                                                                         |                                    |              |              |                            |               |                |                |  |  |

|          |                                                                                                                                     | lt of an arithm<br>It of an arithm |              |              |                            |               |                |                |  |  |

| bit 1:   | DC: Digit car                                                                                                                       | ry/borrow bit                      | (for ADDWF a | nd SUBWF in  | structions)                |               |                |                |  |  |

|          | ADDWF                                                                                                                               |                                    |              |              |                            |               |                |                |  |  |

|          | 1 = A carry from the 4th low order bit of the result occurred<br>0 = A carry from the 4th low order bit of the result did not occur |                                    |              |              |                            |               |                |                |  |  |

|          | SUBWF                                                                                                                               |                                    |              |              |                            |               |                |                |  |  |

|          |                                                                                                                                     |                                    |              |              | did not occur              |               |                |                |  |  |

|          |                                                                                                                                     | from the 4th                       |              |              |                            |               |                |                |  |  |

| bit 0:   | •                                                                                                                                   | row bit (for AI                    |              |              | F instructions             |               | _              |                |  |  |

|          | <b>ADDWF</b><br>1 = A carry o                                                                                                       | ocurred                            |              | orrow did n  | ot occur                   | RRF or RLI    |                | , respectively |  |  |

|          | $\pm = \pi \operatorname{carry} 0$                                                                                                  | locurrou                           | / · ·        |              |                            |               |                |                |  |  |

| Legena:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared        | x = bit is unknown |

| SUBWF            | Subt              | ract W               | from f                                                             |

|------------------|-------------------|----------------------|--------------------------------------------------------------------|

| Syntax:          | [label            | JSL                  | JBWF f,d                                                           |

| Operands:        | $0 \le f$         | ≤ 31                 |                                                                    |

| •                | d ∈ [0            | D,1]                 |                                                                    |

| Operation:       | (f) – (           | W) $\rightarrow$     | (dest)                                                             |

| Status Affected: | C, DO             | C, Z                 |                                                                    |

| Encoding:        | 000               | - 1                  | Odf ffff                                                           |

| Description:     |                   |                      | s complement method)<br>ter from register 'f'. If 'd'              |

|                  | is 0 tł<br>regist | ne resu<br>er. If 'o | It is stored in the W<br>I' is 1 the result is<br>in register 'f'. |

| Words:           | 1                 |                      |                                                                    |

| Cycles:          | 1                 |                      |                                                                    |

| Example 1:       | SUBW              | FF                   | REG1, 1                                                            |

| Before Instru    | ction             |                      |                                                                    |

| REG1             | =                 | 3                    |                                                                    |

| W                | =                 | 2                    |                                                                    |

| С                | =                 | ?                    |                                                                    |

| After Instruct   | ion               |                      |                                                                    |

| REG1             | =                 | 1                    |                                                                    |

| W<br>C           | =                 | 2<br>1               | , recult is positive                                               |

| Example 2:       | =                 | I                    | ; result is positive                                               |

| Before Instru    | ction             |                      |                                                                    |

| REG1             | =                 | 2                    |                                                                    |

| W                | =                 | 2                    |                                                                    |

| C                | =                 | ?                    |                                                                    |

| After Instruct   | ion               |                      |                                                                    |

| REG1             | =                 | 0                    |                                                                    |

| W                | =                 | 2                    |                                                                    |

| С                | =                 | 1                    | ; result is zero                                                   |

| Example 3:       |                   |                      |                                                                    |

| Before Ins       | tructio           |                      |                                                                    |

| REG1             | =                 | 1                    |                                                                    |

| W                | =                 | 2                    |                                                                    |

| C                | =                 | ?                    |                                                                    |

| After Instruct   |                   | 0.VEE                |                                                                    |

| REG1<br>W        | =                 | 0xFF<br>2            |                                                                    |

| C                | _                 | 2                    | ; result is negative                                               |

| Ũ                | -                 | U                    | , isourio nogativo                                                 |

| SWAPF                                          | Swap Nibbles in f                                                                                                                                                        |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                        | [label] SWAPF f,d                                                                                                                                                        |

| Operands:                                      | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                                         |

| Operation:                                     | $(f<3:0>) \rightarrow (dest<7:4>);$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                                |

| Status Affected:                               | None                                                                                                                                                                     |

| Encoding:                                      | 0011 10df ffff                                                                                                                                                           |

| Description:                                   | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is 0<br>the result is placed in W register. If<br>'d' is 1 the result is placed in<br>register 'f'. |

| Words:                                         | 1                                                                                                                                                                        |

| Cycles:                                        | 1                                                                                                                                                                        |

| Example                                        | SWAPF REG1, 0                                                                                                                                                            |

| REG1<br>After Instruct<br>REG1<br>W            | = 0xA5<br>ion<br>= 0xA5<br>= 0x5A                                                                                                                                        |

| TRIS                                           | Load TRIS Register                                                                                                                                                       |

| Syntax:                                        | [ <i>label</i> ] TRIS f                                                                                                                                                  |

| Operands:                                      | f = 5, 6 or 7                                                                                                                                                            |

| Operation:                                     | (W) $\rightarrow$ TRIS register f                                                                                                                                        |

| Status Affected:                               | None                                                                                                                                                                     |

| Encoding:                                      | 0000 0000 0fff                                                                                                                                                           |

| Description:                                   | TRIS register 'f' ( $f = 5, 6, or 7$ ) is<br>loaded with the contents of the W<br>register.                                                                              |

| Words:                                         | 1                                                                                                                                                                        |

| Cycles:                                        | 1                                                                                                                                                                        |

| Example                                        | TRIS PORTB                                                                                                                                                               |

| Before Instru<br>W<br>After Instructi<br>TRISB | = 0xA5<br>on                                                                                                                                                             |

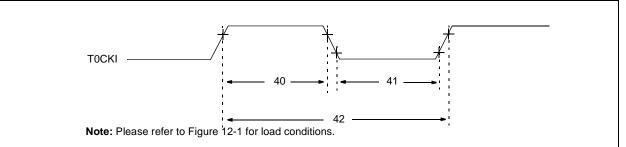

#### FIGURE 12-5: TIMER0 CLOCK TIMINGS - PIC16C54/55/56/57

#### TABLE 12-4: TIMER0 CLOCK REQUIREMENTS - PIC16C54/55/56/57

| $\label{eq:AC Characteristics} \begin{array}{c} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ Operating Temperature & 0°C \leq TA \leq +70°C \mbox{ for commercial} \\ -40°C \leq TA \leq +85°C \mbox{ for industrial} \\ -40°C \leq TA \leq +125°C \mbox{ for extended} \end{array}$ |        |                                                              |                                              |  |   |          | )                                                              |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------|----------------------------------------------|--|---|----------|----------------------------------------------------------------|--|

| Param<br>No.                                                                                                                                                                                                                                                                                                 | Symbol | Characteristic                                               | Characteristic Min Typ† Max Units Conditions |  |   |          |                                                                |  |

| 40                                                                                                                                                                                                                                                                                                           | Tt0H   | T0CKI High Pulse Width<br>- No Prescaler<br>- With Prescaler | 0.5 Tcy + 20*<br>10*                         |  | _ | ns<br>ns |                                                                |  |

| 41                                                                                                                                                                                                                                                                                                           | Tt0L   | T0CKI Low Pulse Width<br>- No Prescaler<br>- With Prescaler  | 0.5 Tcy + 20*<br>10*                         |  | _ | ns<br>ns |                                                                |  |

| 42                                                                                                                                                                                                                                                                                                           | Tt0P   | T0CKI Period                                                 | 20 or <u>Tcy + 40</u> *<br>N                 |  |   | ns       | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |  |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### 13.3 DC Characteristics: PIC16CR54A-04, 10, 20, PIC16LCR54A-04 (Commercial) PIC16CR54A-04I, 10I, 20I, PIC16LCR54A-04I (Industrial)

| DC CH        | ARACTEI | RISTICS                                                                                                                             | Standard O<br>Operating Te                                     |                        | ure 0°C                                                             | $\leq$ TA $\leq$ +7   | otherwise specified)<br>'0°C for commercial<br>35°C for industrial                                                                                                            |

|--------------|---------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------|---------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol  | Characteristic                                                                                                                      | Min                                                            | Тур†                   | Max                                                                 | Units                 | Conditions                                                                                                                                                                    |

| D030         | VIL     | Input Low Voltage<br>I/O ports<br>MCLR (Schmitt Trigger)<br>T0CKI (Schmitt Trigger)<br>OSC1 (Schmitt Trigger)<br>OSC1               | Vss<br>Vss<br>Vss<br>Vss<br>Vss                                |                        | 0.2 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD | V<br>V<br>V<br>V      | Pin at hi-impedance<br>RC mode only <sup>(3)</sup><br>XT, HS and LP modes                                                                                                     |

| D040         | VIн     | Input High Voltage<br>I/O ports<br>I/O ports<br>MCLR (Schmitt Trigger)<br>T0CKI (Schmitt Trigger)<br>OSC1 (Schmitt Trigger)<br>OSC1 | 2.0<br>0.6 VDD<br>0.85 VDD<br>0.85 VDD<br>0.85 VDD<br>0.85 VDD |                        | VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD                       | V<br>V<br>V<br>V<br>V | VDD = 3.0V to 5.5V <sup>(4)</sup><br>Full VDD range <sup>(4)</sup><br>RC mode only <sup>(3)</sup><br>XT, HS and LP modes                                                      |

| D050         | VHYS    | Hysteresis of Schmitt<br>Trigger inputs                                                                                             | 0.15 VDD*                                                      | —                      | —                                                                   | V                     |                                                                                                                                                                               |

| D060         | lι∟     | Input Leakage Current <sup>(1,2)</sup><br>I/O ports                                                                                 | -1.0                                                           | _                      | +1.0                                                                | μA                    | For VDD $\leq$ 5.5V:<br>VSS $\leq$ VPIN $\leq$ VDD,<br>pin at hi-impedance                                                                                                    |

|              |         | MCLR<br>MCLR<br>TOCKI<br>OSC1                                                                                                       | -5.0<br><br>-3.0<br>-3.0                                       | —<br>0.5<br>0.5<br>0.5 | <br>+5.0<br>+3.0<br>+3.0                                            | μΑ<br>μΑ<br>μΑ        | $\label{eq:VPIN} \begin{array}{l} VPIN = VSS + 0.25V \\ VPIN = VDD \\ VSS \leq VPIN \leq VDD \\ VSS \leq VPIN \leq VDD, \\ XT,  HS  \text{and}  LP  \text{modes} \end{array}$ |

| D080         | Vol     | Output Low Voltage<br>I/O ports<br>OSC2/CLKOUT                                                                                      |                                                                | _                      | 0.5<br>0.5                                                          | V<br>V                | IOL = 10  mA,  VDD = 6.0  V<br>IOL = 1.9  mA,  VDD = 6.0  V,<br>RC mode only                                                                                                  |

| D090         | Vон     | Output High Voltage <sup>(2)</sup><br>I/O ports<br>OSC2/CLKOUT                                                                      | Vdd - 0.5<br>Vdd - 0.5                                         | _                      |                                                                     | V<br>V                | IOH = -4.0  mA,  VDD = 6.0  V<br>IOH = -0.8  mA,  VDD = 6.0  V,<br>RC mode only                                                                                               |

\* These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

- 2: Negative current is defined as coming out of the pin.

- **3:** For the RC mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C5X be driven with external clock in RC mode.

- 4: The user may use the better of the two specifications.

| AC Characteristics |            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |        |        |       |                  |  |

|--------------------|------------|------------------------------------------------------|------|--------|--------|-------|------------------|--|

| Param<br>No.       | Symbol     | Characteristic                                       | Min  | Тур†   | Max    | Units | Conditions       |  |

| 1                  | Tosc       | External CLKIN Period <sup>(1)</sup>                 | 250  |        | —      | ns    | XT osc mode      |  |

|                    |            |                                                      | 250  | —      | —      | ns    | HS osc mode (04) |  |

|                    |            |                                                      | 100  | —      | —      | ns    | HS osc mode (10) |  |

|                    |            |                                                      | 50   | —      | —      | ns    | HS osc mode (20) |  |

|                    |            |                                                      | 5.0  | —      | —      | μS    | LP OSC mode      |  |

|                    |            | Oscillator Period <sup>(1)</sup>                     | 250  | _      | —      | ns    | RC osc mode      |  |

|                    |            |                                                      | 250  | —      | 10,000 | ns    | XT OSC mode      |  |

|                    |            |                                                      | 250  | —      | 250    | ns    | HS osc mode (04) |  |

|                    |            |                                                      | 100  | —      | 250    | ns    | HS osc mode (10) |  |

|                    |            |                                                      | 50   | —      | 250    | ns    | HS osc mode (20) |  |

|                    |            |                                                      | 5.0  | —      | 200    | μS    | LP OSC mode      |  |

| 2                  | Тсу        | Instruction Cycle Time <sup>(2)</sup>                | —    | 4/Fosc | —      | _     |                  |  |

| 3                  | TosL, TosH | Clock in (OSC1) Low or High                          | 50*  | _      | —      | ns    | XT oscillator    |  |

|                    |            | Time                                                 | 20*  | —      | —      | ns    | HS oscillator    |  |

|                    |            |                                                      | 2.0* | —      | —      | μS    | LP oscillator    |  |

| 4                  | TosR, TosF | Clock in (OSC1) Rise or Fall                         | —    |        | 25*    | ns    | XT oscillator    |  |

|                    |            | Time                                                 | —    | —      | 25*    | ns    | HS oscillator    |  |

|                    |            |                                                      | _    | —      | 50*    | ns    | LP oscillator    |  |

| TABLE 13-1: | EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16CR54A |

|-------------|-------------------------------------------------|

|-------------|-------------------------------------------------|

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

2: Instruction cycle period (TCY) equals four times the input oscillator time base period.

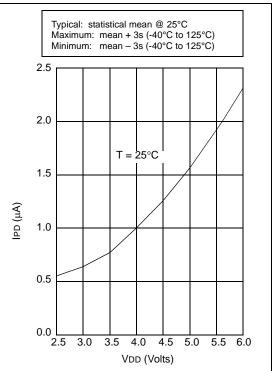

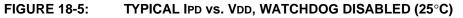

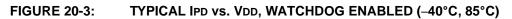

#### FIGURE 14-5: TYPICAL IPD vs. VDD, WATCHDOG DISABLED

# 17.0 ELECTRICAL CHARACTERISTICS - PIC16LC54A

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                                   | –55°C to +125°C       |

|----------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Storage temperature                                                                                                              |                       |

| Voltage on VDD with respect to Vss                                                                                               | 0 to +7.5V            |

| Voltage on MCLR with respect to Vss                                                                                              | 0 to +14V             |

| Voltage on all other pins with respect to Vss0.0                                                                                 | 6V to (VDD + 0.6V)    |

| Total power dissipation <sup>(1)</sup>                                                                                           | 800 mW                |

| Max. current out of Vss pin                                                                                                      | 150 mA                |

| Max. current into Vod pin                                                                                                        |                       |

| Max. current into an input pin (T0CKI only)                                                                                      | ±500 μA               |

| Input clamp current, liк (Vi < 0 or Vi > VDD)                                                                                    | ±20 mA                |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                                                   | ±20 mA                |

| Max. output current sunk by any I/O pin                                                                                          | 25 mA                 |

| Max. output current sourced by any I/O pin                                                                                       | 20 mA                 |

| Max. output current sourced by a single I/O (Port A, B or C)                                                                     | 50 mA                 |

| Max. output current sunk by a single I/O (Port A, B or C)                                                                        | 50 mA                 |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) x let $x \in X$ } | OH} + $∑$ (VOL x IOL) |

**†** NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

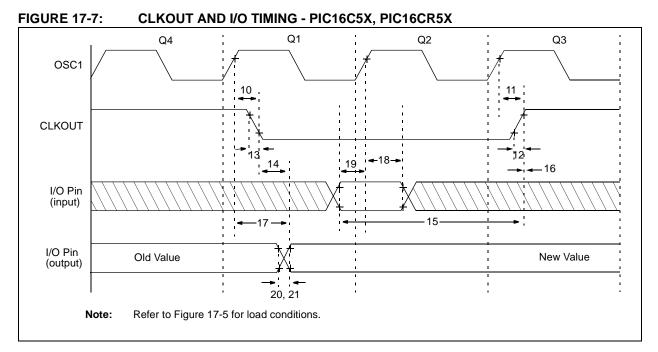

|             | ALVAUT AND VA TIMINA DEALUDENENTA DIALAASY DIALAADSY     |

|-------------|----------------------------------------------------------|

| IABLE 17-2: | CLKOUT AND I/O TIMING REQUIREMENTS - PIC16C5X, PIC16CR5X |

| AC Characteristics |          | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array} $ |              |      |      |       |  |

|--------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|-------|--|

| Param<br>No.       | Symbol   | Characteristic                                                                                                                                                                                                                                                                                                                     | Min          | Тур† | Max  | Units |  |

| 10                 | TosH2ckL | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                                                                                                                                                                                                                                                                                                    | _            | 15   | 30** | ns    |  |

| 11                 | TosH2ckH | OSC1↑ to CLKOUT↑ <sup>(1)</sup>                                                                                                                                                                                                                                                                                                    | _            | 15   | 30** | ns    |  |

| 12                 | TckR     | CLKOUT rise time <sup>(1)</sup>                                                                                                                                                                                                                                                                                                    | —            | 5.0  | 15** | ns    |  |

| 13                 | TckF     | CLKOUT fall time <sup>(1)</sup>                                                                                                                                                                                                                                                                                                    | —            | 5.0  | 15** | ns    |  |

| 14                 | TckL2ioV | CLKOUT↓ to Port out valid <sup>(1)</sup>                                                                                                                                                                                                                                                                                           | —            | —    | 40** | ns    |  |

| 15                 | TioV2ckH | Port in valid before CLKOUT <sup>(1)</sup>                                                                                                                                                                                                                                                                                         | 0.25 TCY+30* | —    | _    | ns    |  |

| 16                 | TckH2iol | Port in hold after CLKOUT <sup>(1)</sup>                                                                                                                                                                                                                                                                                           | 0*           | —    | _    | ns    |  |

| 17                 | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(2)</sup>                                                                                                                                                                                                                                                                      | —            | —    | 100* | ns    |  |

| 18                 | TosH2iol | OSC1↑ (Q2 cycle) to Port input invalid<br>(I/O in hold time)                                                                                                                                                                                                                                                                       | TBD          | —    | _    | ns    |  |

| 19                 | TioV2osH | Port input valid to OSC1↑<br>(I/O in setup time)                                                                                                                                                                                                                                                                                   | TBD          | —    | —    | ns    |  |

| 20                 | TioR     | Port output rise time <sup>(2)</sup>                                                                                                                                                                                                                                                                                               | _            | 10   | 25** | ns    |  |

| 21                 | TioF     | Port output fall time <sup>(2)</sup>                                                                                                                                                                                                                                                                                               | —            | 10   | 25** | ns    |  |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested. No characterization data available at this time.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

**2:** Refer to Figure 17-5 for load conditions.

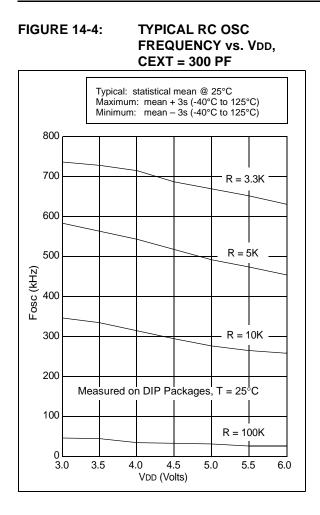

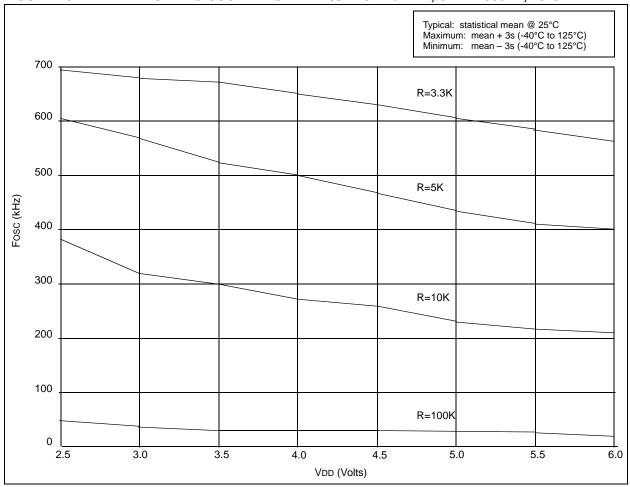

FIGURE 18-4: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD, CEXT = 300 PF, 25°C

© 1997-2013 Microchip Technology Inc.

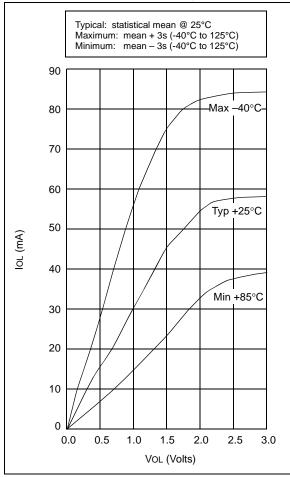

#### FIGURE 20-9: IOL vs. VOL, VDD = 5 V