#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Cana Decasara              |                                                                          |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 20                                                                       |

| Program Memory Size        | 3KB (2K x 12)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 72 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c57-hs-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name    | Pin Number |      |      | Pin  | Buffer | Description                                                                                                                                                                                                       |

|-------------|------------|------|------|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name    | DIP        | SOIC | SSOP | Туре | Туре   | Description                                                                                                                                                                                                       |

| RA0         | 6          | 6    | 5    | I/O  | TTL    | Bi-directional I/O port                                                                                                                                                                                           |

| RA1         | 7          | 7    | 6    | I/O  | TTL    |                                                                                                                                                                                                                   |

| RA2         | 8          | 8    | 7    | I/O  | TTL    |                                                                                                                                                                                                                   |

| RA3         | 9          | 9    | 8    | I/O  | TTL    |                                                                                                                                                                                                                   |

| RB0         | 10         | 10   | 9    | I/O  | TTL    | Bi-directional I/O port                                                                                                                                                                                           |

| RB1         | 11         | 11   | 10   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RB2         | 12         | 12   | 11   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RB3         | 13         | 13   | 12   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RB4         | 14         | 14   | 13   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RB5         | 15         | 15   | 15   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RB6         | 16         | 16   | 16   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RB7         | 17         | 17   | 17   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RC0         | 18         | 18   | 18   | I/O  | TTL    | Bi-directional I/O port                                                                                                                                                                                           |

| RC1         | 19         | 19   | 19   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RC2         | 20         | 20   | 20   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RC3         | 21         | 21   | 21   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RC4         | 22         | 22   | 22   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RC5         | 23         | 23   | 23   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RC6         | 24         | 24   | 24   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RC7         | 25         | 25   | 25   | I/O  | TTL    |                                                                                                                                                                                                                   |

| TOCKI       | 1          | 1    | 2    | Ι    | ST     | Clock input to Timer0. Must be tied to Vss or VDD, if not in use, to reduce current consumption.                                                                                                                  |

| MCLR        | 28         | 28   | 28   | I    | ST     | Master clear (RESET) input. This pin is an active low RESET to the device.                                                                                                                                        |

| OSC1/CLKIN  | 27         | 27   | 27   | I    | ST     | Oscillator crystal input/external clock source input.                                                                                                                                                             |

| OSC2/CLKOUT | 26         | 26   | 26   | 0    | _      | Oscillator crystal output. Connects to crystal or resonator<br>in crystal Oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| Vdd         | 2          | 2    | 3,4  | Р    | _      | Positive supply for logic and I/O pins.                                                                                                                                                                           |

| Vss         | 4          | 4    | 1,14 | Р    |        | Ground reference for logic and I/O pins.                                                                                                                                                                          |

| N/C         | 3,5        | 3,5  |      | _    |        | Unused, do not connect.                                                                                                                                                                                           |

## TABLE 3-2: PINOUT DESCRIPTION - PIC16C55, PIC16C57, PIC16CR57

Legend: I = input, O = output, I/O = input/output, P = power, — = Not Used, TTL = TTL input, ST = Schmitt Trigger input

#### 3.1 **Clocking Scheme/Instruction** Cycle

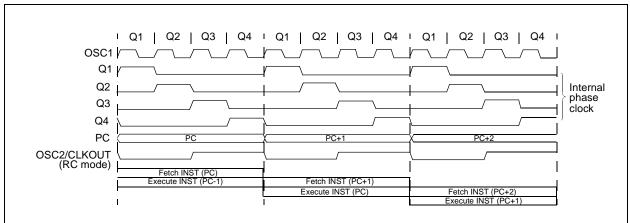

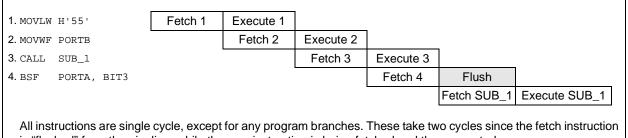

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter is incremented every Q1 and the instruction is fetched from program memory and latched into the instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-2 and Example 3-1.

#### 3.2 Instruction Flow/Pipelining

An Instruction Cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: **CLOCK/INSTRUCTION CYCLE**

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

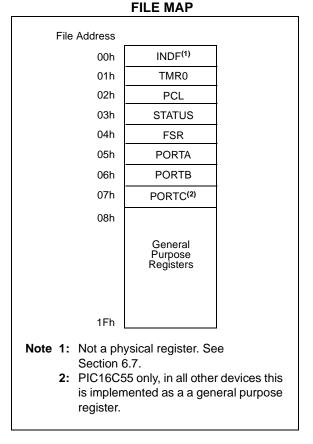

# 6.2 Data Memory Organization

Data memory is composed of registers, or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: Special Function Registers and General Purpose Registers.

The Special Function Registers include the TMR0 register, the Program Counter (PC), the Status Register, the I/O registers (ports) and the File Select Register (FSR). In addition, Special Purpose Registers are used to control the I/O port configuration and prescaler options.

The General Purpose Registers are used for data and control information under command of the instructions.

For the PIC16C54, PIC16CR54, PIC16C56 and PIC16CR56, the register file is composed of 7 Special Function Registers and 25 General Purpose Registers (Figure 6-4).

For the PIC16C55, the register file is composed of 8 Special Function Registers and 24 General Purpose Registers.

For the PIC16C57 and PIC16CR57, the register file is composed of 8 Special Function Registers, 24 General Purpose Registers and up to 48 additional General Purpose Registers that may be addressed using a banking scheme (Figure 6-5).

For the PIC16C58 and PIC16CR58, the register file is composed of 7 Special Function Registers, 25 General Purpose Registers and up to 48 additional General Purpose Registers that may be addressed using a banking scheme (Figure 6-6).

## 6.2.1 GENERAL PURPOSE REGISTER FILE

The register file is accessed either directly or indirectly through the File Select Register (FSR). The FSR Register is described in Section 6.7.

# FIGURE 6-4: PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56 REGISTER

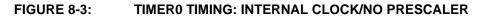

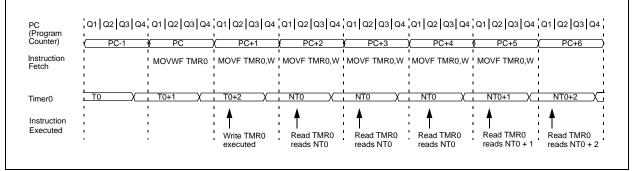

# FIGURE 8-4: TIMER0 TIMING: INTERNAL CLOCK/PRESCALER 1:2

## TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7                                  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | <u>Value</u> on<br>MCLR and<br>WDT Reset |

|---------|--------|----------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|------------------------------------------|

| 01h     | TMR0   | Timer0 - 8-bit real-time clock/counter |       |       |       |       |       |       |       | xxxx xxxx                     | uuuu uuuu                                |

| N/A     | OPTION | _                                      |       | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 11 1111                       | 11 1111                                  |

Legend: x = unknown, u = unchanged, - = unimplemented. Shaded cells not used by Timer0.

# PIC16C5X

| RLF                                          | Rotate Left f through Carry                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:                                      | [ <i>label</i> ] RLF f,d                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Operands:                                    | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                                                                                              |  |  |  |  |  |  |  |  |

| Operation:                                   | See description below                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| Status Affected:                             | С                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| Encoding:                                    | 0011 01df ffff                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| Description:                                 | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag (STATUS<0>). If 'd'<br>is 0 the result is placed in the W<br>register. If 'd' is 1 the result is<br>stored back in<br>register 'f'. |  |  |  |  |  |  |  |  |

| Words:                                       | 1                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| Cycles:                                      | 1                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| Example:                                     | RLF REG1,0                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Before Instru<br>REG1<br>C<br>After Instruct | = 1110 0110<br>= 0<br>tion                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| REG1<br>W<br>C                               | = 1110 0110<br>= 1100 1100<br>= 1                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| RRF                                          | Rotate Right f through Carry                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:                                      | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Operands:                                    | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                                                                                               |  |  |  |  |  |  |  |

| Operation:                                   | See description below                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Status Affected:                             | С                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Encoding:                                    | 0011 00df ffff                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Description:                                 | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag (STATUS<0>). If 'd'<br>is 0 the result is placed in the W<br>register. If 'd' is 1 the result is<br>placed back in<br>register 'f'. |  |  |  |  |  |  |  |

| Words:                                       | 1                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Cycles:                                      | 1                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Example:                                     | RRF REG1,0                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Before Instru<br>REG1<br>C<br>After Instruct | $= 1110 0110 \\ = 0$                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| REG1<br>W<br>C                               | = 1110 0110<br>= 0111 0011<br>= 0                                                                                                                                                                                              |  |  |  |  |  |  |  |

| SLEEP            | Enter SLEEP Mode                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SLEEP                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT; \\ 0 \rightarrow WDT \ prescaler; \ if \ assigned \\ 1 \rightarrow \overline{TO}; \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                                         |  |  |  |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Encoding:        | 0000 0000 0011                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Description:     | Time-out status bit $(\overline{TO})$ is set. The<br>power-down status bit $(\overline{PD})$ is<br>cleared. The WDT and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See section on SLEEP for more<br>details. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| SUBWF            | Subt              | ract W               | from f                                                             |

|------------------|-------------------|----------------------|--------------------------------------------------------------------|

| Syntax:          | [label            | JSL                  | JBWF f,d                                                           |

| Operands:        | $0 \le f$         | ≤ 31                 |                                                                    |

| •                | d ∈ [0            | D,1]                 |                                                                    |

| Operation:       | (f) – (           | W) $\rightarrow$     | (dest)                                                             |

| Status Affected: | C, DC             | C, Z                 |                                                                    |

| Encoding:        | 000               | - 1                  | Odf ffff                                                           |

| Description:     |                   |                      | s complement method)<br>ter from register 'f'. If 'd'              |

|                  | is 0 tł<br>regist | ne resu<br>er. If 'o | It is stored in the W<br>I' is 1 the result is<br>in register 'f'. |

| Words:           | 1                 |                      |                                                                    |

| Cycles:          | 1                 |                      |                                                                    |

| Example 1:       | SUBW              | FF                   | REG1, 1                                                            |

| Before Instru    | ction             |                      |                                                                    |

| REG1             | =                 | 3                    |                                                                    |

| W                | =                 | 2                    |                                                                    |

| С                | =                 | ?                    |                                                                    |

| After Instruct   | ion               |                      |                                                                    |

| REG1             | =                 | 1                    |                                                                    |

| W<br>C           | =                 | 2<br>1               | , recult is positive                                               |

| Example 2:       | =                 | I                    | ; result is positive                                               |

| Before Instru    | ction             |                      |                                                                    |

| REG1             | =                 | 2                    |                                                                    |

| W                | =                 | 2                    |                                                                    |

| C                | =                 | ?                    |                                                                    |

| After Instruct   | ion               |                      |                                                                    |

| REG1             | =                 | 0                    |                                                                    |

| W                | =                 | 2                    |                                                                    |

| С                | =                 | 1                    | ; result is zero                                                   |

| Example 3:       |                   |                      |                                                                    |

| Before Ins       | tructio           |                      |                                                                    |

| REG1             | =                 | 1                    |                                                                    |

| W                | =                 | 2                    |                                                                    |

| C                | =                 | ?                    |                                                                    |

| After Instruct   |                   | 0.VEE                |                                                                    |

| REG1<br>W        | =                 | 0xFF<br>2            |                                                                    |

| C                | _                 | 2                    | ; result is negative                                               |

| Ũ                | -                 | U                    | , isourio nogativo                                                 |

| SWAPF                                          | Swap Nibbles in f                                                                                                                                                        |  |  |  |  |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                        | [label] SWAPF f,d                                                                                                                                                        |  |  |  |  |  |  |

| Operands:                                      | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                                         |  |  |  |  |  |  |

| Operation:                                     | $(f<3:0>) \rightarrow (dest<7:4>);$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                                |  |  |  |  |  |  |

| Status Affected:                               | None                                                                                                                                                                     |  |  |  |  |  |  |

| Encoding:                                      | 0011 10df ffff                                                                                                                                                           |  |  |  |  |  |  |

| Description:                                   | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is 0<br>the result is placed in W register. If<br>'d' is 1 the result is placed in<br>register 'f'. |  |  |  |  |  |  |

| Words:                                         | 1                                                                                                                                                                        |  |  |  |  |  |  |

| Cycles:                                        | 1                                                                                                                                                                        |  |  |  |  |  |  |

| Example                                        | SWAPF REG1, 0                                                                                                                                                            |  |  |  |  |  |  |

| REG1<br>After Instruct<br>REG1<br>W            | = 0xA5<br>ion<br>= 0xA5<br>= 0x5A                                                                                                                                        |  |  |  |  |  |  |

| TRIS                                           | Load TRIS Register                                                                                                                                                       |  |  |  |  |  |  |

| Syntax:                                        | [ <i>label</i> ] TRIS f                                                                                                                                                  |  |  |  |  |  |  |

| Operands:                                      | f = 5, 6 or 7                                                                                                                                                            |  |  |  |  |  |  |

| Operation:                                     | (W) $\rightarrow$ TRIS register f                                                                                                                                        |  |  |  |  |  |  |

| Status Affected:                               | None                                                                                                                                                                     |  |  |  |  |  |  |

| Encoding:                                      | 0000 0000 0fff                                                                                                                                                           |  |  |  |  |  |  |

| Description:                                   | TRIS register 'f' ( $f = 5, 6, or 7$ ) is<br>loaded with the contents of the W<br>register.                                                                              |  |  |  |  |  |  |

| Words:                                         | 1                                                                                                                                                                        |  |  |  |  |  |  |

| Cycles:                                        | 1                                                                                                                                                                        |  |  |  |  |  |  |

| Example                                        | TRIS PORTB                                                                                                                                                               |  |  |  |  |  |  |

| Before Instru<br>W<br>After Instructi<br>TRISB | = 0xA5<br>on                                                                                                                                                             |  |  |  |  |  |  |

# 11.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC MCUs and can be used to develop for this and other PIC microcontrollers. The MPLAB ICD utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>TM</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

# 11.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in Stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In Stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC devices. It can also set code protection in this mode.

# 11.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

# 11.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

# 11.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the  $I^2C^{TM}$  bus and separate headers for connection to an LCD module and a keypad.

# 12.0 ELECTRICAL CHARACTERISTICS - PIC16C54A

# Absolute Maximum Ratings<sup>(†)</sup>

| Ambient Temperature under bias                                   | –55°C to +125°C      |

|------------------------------------------------------------------|----------------------|

| Storage Temperature                                              | 65°C to +150°C       |

| Voltage on VDD with respect to VSS                               | 0V to +7.5V          |

| Voltage on MCLR with respect to Vss <sup>(1)</sup>               | 0V to +14V           |

| Voltage on all other pins with respect to Vss                    | 0.6V to (VDD + 0.6V) |

| Total power dissipation <sup>(2)</sup>                           | 800 mW               |

| Max. current out of Vss pin                                      | 150 mA               |

| Max. current into Vod pin                                        | 100 mA               |

| Max. current into an input pin (T0CKI only)                      | ±500 μA              |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                     | ±20 mA               |

| Output clamp current, IOK (VO < 0 or VO > VDD)                   | ±20 mA               |

| Max. output current sunk by any I/O pin                          | 25 mA                |

| Max. output current sourced by any I/O pin                       | 20 mA                |

| Max. output current sourced by a single I/O port (PORTA, B or C) | 40 mA                |

| Max. output current sunk by a single I/O port (PORTA, B or C)    | 50 mA                |

|                                                                  |                      |

- **Note 1:** Voltage spikes below Vss at the  $\overline{\text{MCLR}}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50 to 100  $\Omega$  should be used when applying a "low" level to the  $\overline{\text{MCLR}}$  pin rather than pulling this pin directly to Vss.

- 2: Power Dissipation is calculated as follows: Pdis = VDD x {IDD  $\Sigma$  IOH} +  $\Sigma$  {(VDD VOH) x IOH} +  $\Sigma$ (VOL x IOL)

† NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

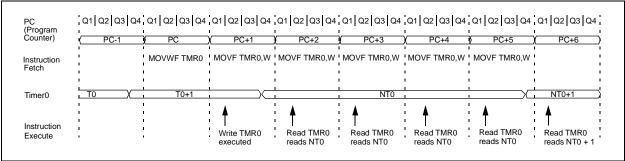

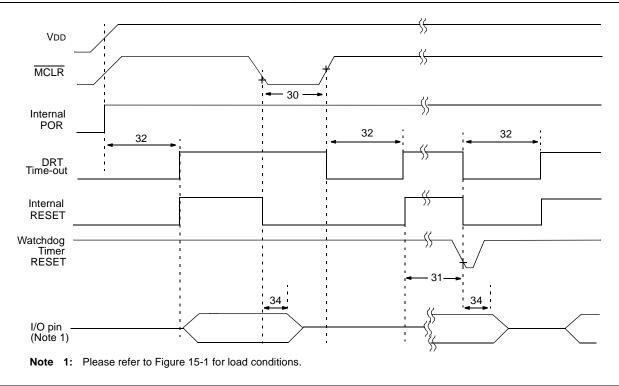

## FIGURE 12-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING -PIC16C54/55/56/57

## TABLE 12-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16C54/55/56/57

| $\label{eq:AC Characteristics} \begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                       |                                                  |      |      |      |       |                   |

|-------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------|------|------|------|-------|-------------------|

| Param<br>No.                                                                        | Symbol Characteristic |                                                  |      | Тур† | Max  | Units | Conditions        |

| 30                                                                                  | TmcL                  | MCLR Pulse Width (low)                           | 100* | —    | —    | ns    | VDD = 5.0V        |

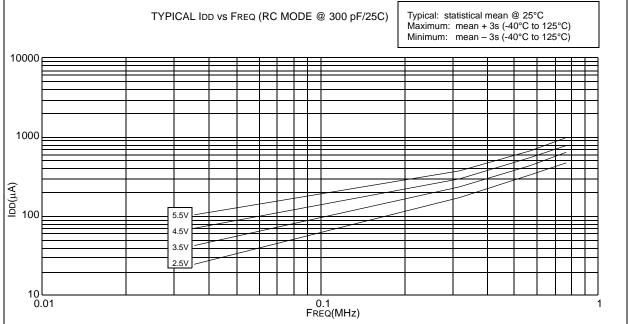

| 31                                                                                  | Twdt                  | Watchdog Timer Time-out Period<br>(No Prescaler) | 9.0* | 18*  | 30*  | ms    | VDD = 5.0V (Comm) |

| 32                                                                                  | Tdrt                  | Device Reset Timer Period                        | 9.0* | 18*  | 30*  | ms    | VDD = 5.0V (Comm) |

| 34                                                                                  | Tioz                  | I/O Hi-impedance from MCLR Low                   | _    | _    | 100* | ns    |                   |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

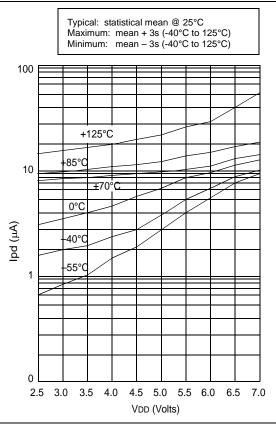

## FIGURE 14-6: MAXIMUM IPD vs. VDD, WATCHDOG DISABLED

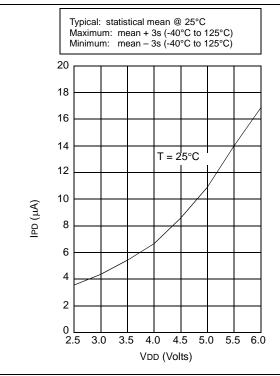

# FIGURE 14-7: T

#### TYPICAL IPD vs. VDD, WATCHDOG ENABLED

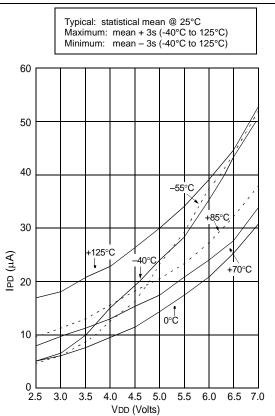

#### FIGURE 14-8: MAXIMUM IPD vs. VDD, WATCHDOG ENABLED

IPD, with WDT enabled, has two components: The leakage current, which increases with higher temperature, and the operating current of the WDT logic, which increases with lower temperature. At  $-40^{\circ}$ C, the latter dominates explaining the apparently anomalous behavior.

# 15.0 ELECTRICAL CHARACTERISTICS - PIC16C54A

| Absolute Maximum Ratings <sup>(†)</sup>                                                                  |                                      |

|----------------------------------------------------------------------------------------------------------|--------------------------------------|

| Ambient temperature under bias                                                                           | –55°C to +125°C                      |

| Storage temperature                                                                                      | –65°C to +150°C                      |

| Voltage on VDD with respect to Vss                                                                       | 0 to +7.5V                           |

| Voltage on MCLR with respect to Vss                                                                      | 0 to +14V                            |

| Voltage on all other pins with respect to Vss                                                            | –0.6V to (VDD + 0.6V)                |

| Total power dissipation <sup>(1)</sup>                                                                   | 800 mW                               |

| Max. current out of Vss pin                                                                              | 150 mA                               |

| Max. current into Vod pin                                                                                | 100 mA                               |

| Max. current into an input pin (T0CKI only)                                                              | ±500 μA                              |

| Input clamp current, Iik (VI < 0 or VI > VDD)                                                            | ±20 mA                               |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                           |                                      |

| Max. output current sunk by any I/O pin                                                                  | 25 mA                                |

| Max. output current sourced by any I/O pin                                                               | 20 mA                                |

| Max. output current sourced by a single I/O port (PORTA or B)                                            | 50 mA                                |

| Max. output current sunk by a single I/O port (PORTA or B)                                               | 50 mA                                |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VD | D-VOH) X IOH} + $\Sigma$ (VOL X IOL) |

† NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## FIGURE 15-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16C54A

## TABLE 15-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16C54A

|          |            | Standard Operating Condition                                              | ns (unle                                              | ess othe         | erwise    | specifie   | ed)                          |  |  |  |  |

|----------|------------|---------------------------------------------------------------------------|-------------------------------------------------------|------------------|-----------|------------|------------------------------|--|--|--|--|

|          |            | Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |                                                       |                  |           |            |                              |  |  |  |  |

| AC Chara | cteristics | -40                                                                       | $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                  |           |            |                              |  |  |  |  |

|          |            | -20                                                                       | $0^{\circ}C \leq TA$                                  | ∖ ≤ <b>+</b> 85° | C for ind | dustrial - | - PIC16LV54A-02I             |  |  |  |  |

|          |            | -40                                                                       | $0^{\circ}C \leq TA$                                  | ∖ ≤ <b>+</b> 125 | °C for e  | xtended    | ł                            |  |  |  |  |

| Param    |            |                                                                           |                                                       |                  |           |            |                              |  |  |  |  |

| No.      | Symbol     | Characteristic                                                            | Min                                                   | Тур†             | Мах       | Units      | Conditions                   |  |  |  |  |

| 30       | TmcL       | MCLR Pulse Width (low)                                                    | 100*                                                  | _                | _         | ns         | VDD = 5.0V                   |  |  |  |  |

|          |            |                                                                           | 1                                                     | —                | —         | μS         | VDD = 5.0V (PIC16LV54A only) |  |  |  |  |

| 31       | Twdt       | Watchdog Timer Time-out                                                   | 9.0*                                                  | 18*              | 30*       | ms         | VDD = 5.0V (Comm)            |  |  |  |  |

|          |            | Period (No Prescaler)                                                     |                                                       |                  |           |            |                              |  |  |  |  |

| 32       | Tdrt       | Device Reset Timer Period                                                 | 9.0*                                                  | 18*              | 30*       | ms         | VDD = 5.0V (Comm)            |  |  |  |  |

| 34       | Tioz       | I/O Hi-impedance from MCLR                                                | _                                                     | _                | 100*      | ns         |                              |  |  |  |  |

|          |            | Low                                                                       | —                                                     |                  | 1μs       | —          | (PIC16LV54A only)            |  |  |  |  |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

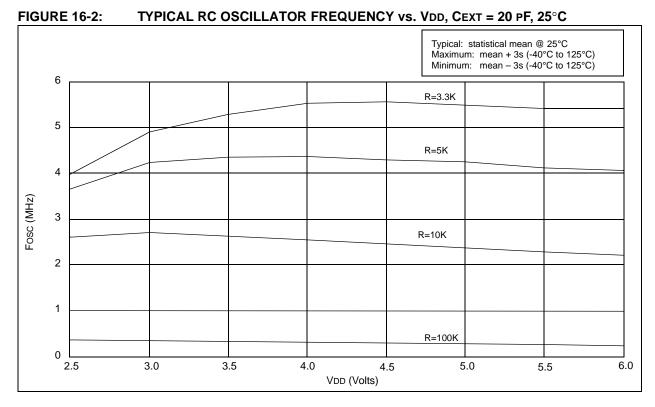

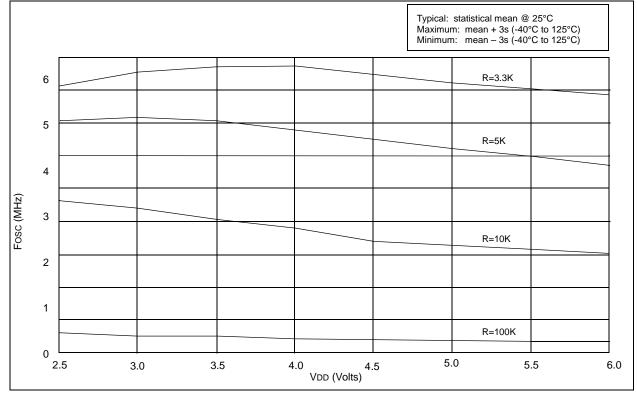

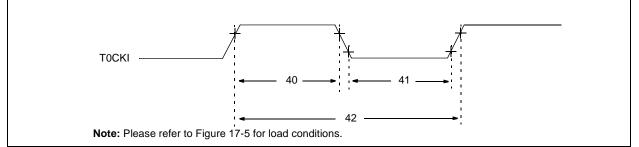

#### **FIGURE 17-9:** TIMER0 CLOCK TIMINGS - PIC16C5X, PIC16CR5X

#### **TABLE 17-4:** TIMER0 CLOCK REQUIREMENTS - PIC16C5X, PIC16CR5X

| ļ            | AC Chara | cteristics Standard Operatin<br>Operating Temperat | $\begin{array}{ll} \mbox{g Conditions (unless otherwise specified)} \\ \mbox{ture} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |      |     |       |                                                                |

|--------------|----------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|----------------------------------------------------------------|

| Param<br>No. | Symbol   | Characteristic                                     | Min                                                                                                                                                                                                                                                                                            | Тур† | Max | Units | Conditions                                                     |

| 40           | Tt0H     | T0CKI High Pulse Width<br>- No Prescaler           | 0.5 Tcy + 20*                                                                                                                                                                                                                                                                                  |      | _   | ns    |                                                                |

|              |          | - With Prescaler                                   | 10*                                                                                                                                                                                                                                                                                            | _    | —   | ns    |                                                                |

| 41           | TtOL     | T0CKI Low Pulse Width<br>- No Prescaler            | 0.5 Tcy + 20*                                                                                                                                                                                                                                                                                  | _    | _   | ns    |                                                                |

|              |          | - With Prescaler                                   | 10*                                                                                                                                                                                                                                                                                            | _    | _   | ns    |                                                                |

| 42           | Tt0P     | T0CKI Period                                       | 20 or <u>Tcy + 40</u> *<br>N                                                                                                                                                                                                                                                                   | _    | _   | ns    | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

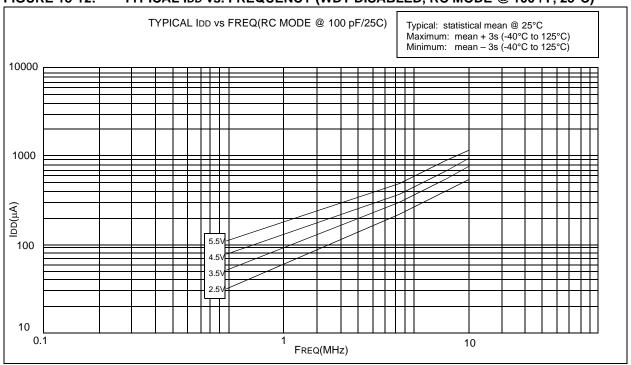

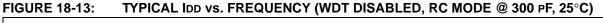

# FIGURE 18-12: TYPICAL IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 100 PF, 25°C)

# TABLE 20-1: INPUT CAPACITANCE

| Pin         | Typical Capacitance (pF) |          |  |  |

|-------------|--------------------------|----------|--|--|

| FIII        | 18L PDIP                 | 18L SOIC |  |  |

| RA port     | 5.0                      | 4.3      |  |  |

| RB port     | 5.0                      | 4.3      |  |  |

| MCLR        | 17.0                     | 17.0     |  |  |

| OSC1        | 4.0                      | 3.5      |  |  |

| OSC2/CLKOUT | 4.3                      | 3.5      |  |  |

| тоскі       | 3.2                      | 2.8      |  |  |

All capacitance values are typical at  $25^{\circ}$ C. A part-to-part variation of ±25% (three standard deviations) should be taken into account.