Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 20                                                                        |

| Program Memory Size        | 3KB (2K x 12)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 72 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c57-lpe-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

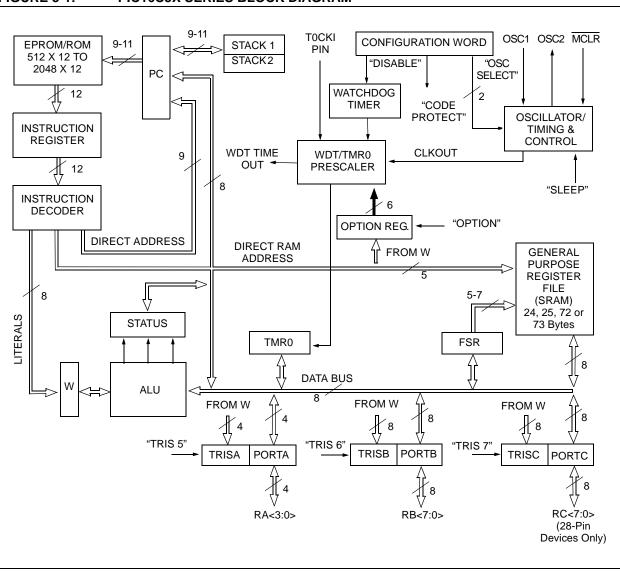

### FIGURE 3-1: PIC16C5X SERIES BLOCK DIAGRAM

### 7.6 I/O Programming Considerations

### 7.6.1 BI-DIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU, bit5 to be set and the PORTB value to be written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (say bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit0 is switched into Output mode later on, the content of the data latch may now be unknown.

Example 7-1 shows the effect of two sequential read-modify-write instructions (e.g., BCF, BSF, etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

### EXAMPLE 7-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT Settings

; PORTB<7:4> Inputs

; PORTB<3:0> Outputs

;PORTB<7:6> have external pull-ups and are

;not connected to other circuitry

;

| ; |       |        |   | PORT  | latch | PORT | pins |

|---|-------|--------|---|-------|-------|------|------|

| ; |       |        |   |       |       |      |      |

|   | BCF   | PORTB, | 7 | ;01pp | pppp  | 11pp | pppp |

|   | BCF   | PORTB, | 6 | ;10pp | pppp  | 11pp | pppp |

|   | MOVLW | H'3F'  |   | ;     |       |      |      |

|   | TRIS  | PORTB  |   | ;10pp | pppp  | 10pp | pppp |

| ; |       |        |   |       |       |      |      |

;Note that the user may have expected the pin ;values to be 00pp pppp. The 2nd BCF caused ;RB7 to be latched as the pin value (High).

### 7.6.2 SUCCESSIVE OPERATIONS ON I/O PORTS

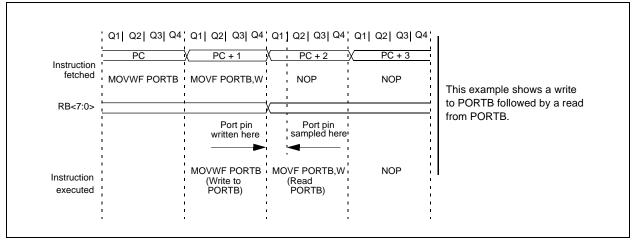

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 7-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

### FIGURE 7-2: SUCCESSIVE I/O OPERATION

# PIC16C5X

| COMF                                                                                                                                                                          | Complement f                                                   |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                                                                                                                                                       | [ <i>label</i> ] COMF f,d                                      |  |  |  |  |  |  |

| Operands:                                                                                                                                                                     | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$ |  |  |  |  |  |  |

| Operation:                                                                                                                                                                    | $(\overline{f}) \rightarrow (dest)$                            |  |  |  |  |  |  |

| Status Affected:                                                                                                                                                              | Z                                                              |  |  |  |  |  |  |

| Encoding:                                                                                                                                                                     | 0010 01df ffff                                                 |  |  |  |  |  |  |

| Description: The contents of register 'f' are<br>complemented. If 'd' is 0 the res<br>is stored in the W register. If 'd' is<br>the result is stored back in<br>register 'f'. |                                                                |  |  |  |  |  |  |

| Words:                                                                                                                                                                        | 1                                                              |  |  |  |  |  |  |

| Cycles:                                                                                                                                                                       | 1                                                              |  |  |  |  |  |  |

| Example:                                                                                                                                                                      | COMF REG1,0                                                    |  |  |  |  |  |  |

| Before Instru<br>REG1<br>After Instruct<br>REG1<br>W                                                                                                                          | = 0x13                                                         |  |  |  |  |  |  |

| DECF                                                    | ECF Decrement f                                                                                                                             |         |      |  |  |  |  |  |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------|------|--|--|--|--|--|

| Syntax:                                                 | [ label ]                                                                                                                                   | DECF f, | d    |  |  |  |  |  |

| Operands:                                               | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                              |         |      |  |  |  |  |  |

| Operation:                                              | $(f) - 1 \rightarrow$                                                                                                                       | (dest)  |      |  |  |  |  |  |

| Status Affected:                                        | Z                                                                                                                                           |         |      |  |  |  |  |  |

| Encoding:                                               | 0000                                                                                                                                        | 11df    | ffff |  |  |  |  |  |

| Description:                                            | Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If<br>'d' is 1 the result is stored back in<br>register 'f'. |         |      |  |  |  |  |  |

| Words:                                                  | 1                                                                                                                                           |         |      |  |  |  |  |  |

| Cycles:                                                 | 1                                                                                                                                           |         |      |  |  |  |  |  |

| Example:                                                | DECF                                                                                                                                        | CNT,    | 1    |  |  |  |  |  |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0<br>= 0<br>ion                                                                                                                           | <01     |      |  |  |  |  |  |

| DECFSZ                                                | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                               | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Operands:                                             | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                                |  |  |  |  |

| Operation:                                            | (f) $-1 \rightarrow d$ ; skip if result = 0                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Status Affected:                                      | None                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Encoding:                                             | 0010 11df ffff                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Description:                                          | The contents of register 'f' are dec-<br>remented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded and a NOP is executed<br>instead making it a two-cycle<br>instruction. |  |  |  |  |

| Words:                                                | 1                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Cycles:                                               | 1(2)                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Example:                                              | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Before Instru<br>PC                                   | = address (HERE)                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| After Instruct<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC | tion<br>= CNT - 1;<br>= 0,<br>= address (CONTINUE);<br>≠ 0,<br>= address (HERE+1)                                                                                                                                                                                                                                                         |  |  |  |  |

| GOTO                                      | Unconditional Branch                                                                                                                                                                        |      |          |  |  |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|--|--|

| Syntax:                                   | [ label ]                                                                                                                                                                                   | GOTO | k        |  |  |

| Operands:                                 | $0 \le k \le 5^{-1}$                                                                                                                                                                        | 11   |          |  |  |

| Operation:                                | $k \rightarrow PC < STATUS$                                                                                                                                                                 | ,    | PC<10:9> |  |  |

| Status Affected:                          | None                                                                                                                                                                                        |      |          |  |  |

| Encoding:                                 | 101k                                                                                                                                                                                        | kkkk | kkkk     |  |  |

| Description:                              | GOTO is an unconditional branch.<br>The 9-bit immediate value is<br>loaded into PC bits <8:0>. The<br>upper bits of PC are loaded from<br>STATUS<6:5>. GOTO is a two-<br>cycle instruction. |      |          |  |  |

| Words:                                    | 1                                                                                                                                                                                           |      |          |  |  |

| Cycles:                                   | 2                                                                                                                                                                                           |      |          |  |  |

| Example: GOTO THERE                       |                                                                                                                                                                                             |      |          |  |  |

| After Instruction<br>PC = address (THERE) |                                                                                                                                                                                             |      |          |  |  |

| INCF                                                    | Increment f                                                                                                                                                          |  |  |  |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                 | [ <i>label</i> ] INCF f,d                                                                                                                                            |  |  |  |  |  |

| Operands:                                               | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                       |  |  |  |  |  |

| Operation:                                              | (f) + 1 $\rightarrow$ (dest)                                                                                                                                         |  |  |  |  |  |

| Status Affected:                                        | Z                                                                                                                                                                    |  |  |  |  |  |

| Encoding:                                               | 0010 10df ffff                                                                                                                                                       |  |  |  |  |  |

| Description:                                            | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |  |  |  |  |  |

| Words:                                                  | 1                                                                                                                                                                    |  |  |  |  |  |

| Cycles:                                                 | 1                                                                                                                                                                    |  |  |  |  |  |

| Example:                                                | INCF CNT, 1                                                                                                                                                          |  |  |  |  |  |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0xFF<br>= 0                                                                                                                                                        |  |  |  |  |  |

| INCFSZ                               | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                              | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Operands:                            | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Operation:                           | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Status Affected:                     | None                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Encoding:                            | 0011 11df ffff                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Description:                         | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'.<br>If the result is 0, then the next<br>instruction, which is already<br>fetched, is discarded and a NOP is<br>executed instead making it a two-<br>cycle instruction. |  |  |  |  |

| Words:                               | 1                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Cycles:                              | 1(2)                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Example:                             | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•<br>•                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Before Instru<br>PC<br>After Instruc | = address (HERE)                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| CNT<br>if CNT<br>PC<br>if CNT<br>PC  | <pre>= CNT + 1;<br/>= 0,<br/>= address (CONTINUE);<br/>≠ 0,<br/>= address (HERE +1)</pre>                                                                                                                                                                                                                                                   |  |  |  |  |

## PIC16C5X

| RLF                                          | Rotate Left f through Carry                                                                                                                                                                                                   |  |  |  |  |  |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                      | [ <i>label</i> ] RLF f,d                                                                                                                                                                                                      |  |  |  |  |  |

| Operands:                                    | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                                                                |  |  |  |  |  |

| Operation:                                   | See description below                                                                                                                                                                                                         |  |  |  |  |  |

| Status Affected:                             | С                                                                                                                                                                                                                             |  |  |  |  |  |

| Encoding:                                    | 0011 01df ffff                                                                                                                                                                                                                |  |  |  |  |  |

| Description:                                 | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag (STATUS<0>). If 'd'<br>is 0 the result is placed in the W<br>register. If 'd' is 1 the result is<br>stored back in<br>register 'f'. |  |  |  |  |  |

| Words:                                       | 1                                                                                                                                                                                                                             |  |  |  |  |  |

| Cycles:                                      | 1                                                                                                                                                                                                                             |  |  |  |  |  |

| Example:                                     | RLF REG1,0                                                                                                                                                                                                                    |  |  |  |  |  |

| Before Instru<br>REG1<br>C<br>After Instruct | = 1110 0110<br>= 0<br>tion                                                                                                                                                                                                    |  |  |  |  |  |

| REG1<br>W<br>C                               | = 1110 0110<br>= 1100 1100<br>= 1                                                                                                                                                                                             |  |  |  |  |  |

| RRF                                          | Rotate Right f through Carry                                                                                                                                                                                                   |  |  |  |  |  |  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                      | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                       |  |  |  |  |  |  |

| Operands:                                    | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                     |  |  |  |  |  |  |

| Operation:                                   | See description below                                                                                                                                                                                                          |  |  |  |  |  |  |

| Status Affected:                             | С                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Encoding:                                    | 0011 00df ffff                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Description:                                 | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag (STATUS<0>). If 'd'<br>is 0 the result is placed in the W<br>register. If 'd' is 1 the result is<br>placed back in<br>register 'f'. |  |  |  |  |  |  |

| Words:                                       | 1                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Cycles:                                      | 1                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Example:                                     | RRF REG1,0                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Before Instru<br>REG1<br>C<br>After Instruct | $= 1110 0110 \\ = 0$                                                                                                                                                                                                           |  |  |  |  |  |  |

| REG1<br>W<br>C                               | = 1110 0110<br>= 0111 0011<br>= 0                                                                                                                                                                                              |  |  |  |  |  |  |

| SLEEP            | Enter SLEEP Mode                                                                                                                                                                                                                                                             |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SLEEP                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT; \\ 0 \rightarrow WDT \ prescaler; \ if \ assigned \\ 1 \rightarrow \overline{TO}; \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                                         |  |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Encoding:        | 0000 0000 0011                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Description:     | Time-out status bit $(\overline{TO})$ is set. The<br>power-down status bit $(\overline{PD})$ is<br>cleared. The WDT and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See section on SLEEP for more<br>details. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                                                                        |  |  |  |  |  |

### 11.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can also link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian is a librarian for precompiled code to be used with the MPLINK object linker. When a routine from a library is called from another source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. The MPLIB object librarian manages the creation and modification of library files.

The MPLINK object linker features include:

- Integration with MPASM assembler and MPLAB C17 and MPLAB C18 C compilers.

- Allows all memory areas to be defined as sections to provide link-time flexibility.

The MPLIB object librarian features include:

- Easier linking because single libraries can be included instead of many smaller files.

- Helps keep code maintainable by grouping related modules together.

- Allows libraries to be created and modules to be added, listed, replaced, deleted or extracted.

### 11.5 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC-hosted environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user-defined key press, to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and the MPLAB C18 C compilers and the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent multiproject software development tool.

### 11.6 MPLAB ICE High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB ICE universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers (MCUs). Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE in-circuit emulator system has been designed as a real-time emulation system, with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows environment were chosen to best make these features available to you, the end user.

### 11.7 ICEPIC In-Circuit Emulator

The ICEPIC low cost, in-circuit emulator is a solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X and PIC16CXXX families of 8-bit One-Time-Programmable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules, or daughter boards. The emulator is capable of emulating without target application circuitry being present.

#### 13.4 DC Characteristics: PIC16CR54A-04E, 10E, 20E (Extended)

| DC CHARACTERISTICS |        | Standard Operating Conditions (unless otherwise specified)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |           |      |          |       |                                               |

|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|-----------|------|----------|-------|-----------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                       | Min       | Тур† | Мах      | Units | Conditions                                    |

| D030               | VIL    | Input Low Voltage                                                                                                                    |           |      |          |       |                                               |

|                    |        | I/O ports                                                                                                                            | Vss       |      | 0.15 Vdd | V     | Pin at hi-impedance                           |

|                    |        | MCLR (Schmitt Trigger)                                                                                                               | Vss       |      | 0.15 VDD | V     |                                               |

|                    |        | T0CKI (Schmitt Trigger)                                                                                                              | Vss       |      | 0.15 VDD | V     |                                               |

|                    |        | OSC1 (Schmitt Trigger)                                                                                                               | Vss       |      | 0.15 VDD | V     | RC mode only <sup>(3)</sup>                   |

|                    |        | OSC1                                                                                                                                 | Vss       | —    | 0.3 Vdd  | V     | XT, HS and LP modes                           |

| D040               | Vін    | Input High Voltage                                                                                                                   |           |      |          |       |                                               |

|                    |        | I/O ports                                                                                                                            | 0.45 Vdd  |      | Vdd      | V     | For all VDD <sup>(4)</sup>                    |

|                    |        | I/O ports                                                                                                                            | 2.0       |      | Vdd      | V     | $4.0V < VDD \le 5.5V^{(4)}$                   |

|                    |        | I/O ports                                                                                                                            | 0.36 Vdd  |      | Vdd      | V     | VDD > 5.5V                                    |

|                    |        | MCLR (Schmitt Trigger)                                                                                                               | 0.85 VDD  |      | Vdd      | V     |                                               |

|                    |        | T0CKI (Schmitt Trigger)                                                                                                              | 0.85 VDD  |      | Vdd      | V     |                                               |

|                    |        | OSC1 (Schmitt Trigger)                                                                                                               | 0.85 VDD  |      | Vdd      | V     | RC mode only <sup>(3)</sup>                   |

|                    |        | OSC1                                                                                                                                 | 0.7 Vdd   | —    | Vdd      | V     | XT, HS and LP modes                           |

| D050               | VHYS   | Hysteresis of Schmitt<br>Trigger inputs                                                                                              | 0.15 Vdd* | —    | _        | V     |                                               |

| D060               | lı∟    | Input Leakage Current <sup>(1,2)</sup>                                                                                               |           |      |          |       | <b>For</b> VDD ≤ <b>5.5</b> V:                |

|                    |        | I/O ports                                                                                                                            | -1.0      | 0.5  | +1.0     | μA    | $VSS \leq VPIN \leq VDD$ ,                    |

|                    |        |                                                                                                                                      |           |      |          |       | pin at hi-impedance                           |

|                    |        | MCLR                                                                                                                                 | -5.0      |      | _        | μA    | VPIN = VSS + 0.25V                            |

|                    |        | MCLR                                                                                                                                 | _         | 0.5  | +5.0     | μΑ    | VPIN = VDD                                    |

|                    |        | TOCKI                                                                                                                                | -3.0      | 0.5  | +3.0     | μΑ    | $VSS \leq VPIN \leq VDD$                      |

|                    |        | OSC1                                                                                                                                 | -3.0      | 0.5  | +3.0     | μA    | $VSS \leq VPIN \leq VDD$ ,                    |

|                    |        |                                                                                                                                      |           |      |          |       | XT, HS and LP modes                           |

| D080               | Vol    | Output Low Voltage                                                                                                                   |           |      |          |       |                                               |

|                    |        | I/O ports                                                                                                                            | I —       | —    | 0.6      | V     | IOL = 8.7 mA, VDD = 4.5V                      |

|                    |        | OSC2/CLKOUT                                                                                                                          |           |      | 0.6      | V     | IOL = 1.6  mA, VDD = 4.5 V,                   |

|                    |        |                                                                                                                                      |           |      |          |       | RC mode only                                  |

| D090               | Voh    | Output High Voltage <sup>(2)</sup>                                                                                                   |           |      |          |       |                                               |

|                    |        | I/O ports                                                                                                                            | Vdd - 0.7 | —    | —        | V     | IOH = −5.4 mA, VDD = 4.5\                     |

|                    |        | OSC2/CLKOUT                                                                                                                          | Vdd - 0.7 | —    | -        | V     | IOH = -1.0  mA,  VDD = 4.5  V<br>RC mode only |

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

**2:** Negative current is defined as coming out of the pin.

3: For the RC mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C5X be driven with external clock in RC mode.

4: The user may use the better of the two specifications.

| AC Characteristics |            | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |        |        |       |                  |  |  |  |

|--------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|--------|-------|------------------|--|--|--|

| Param<br>No.       | Symbol     | Characteristic                                                                                                                                                                                                                                 | Min  | Тур†   | Max    | Units | Conditions       |  |  |  |

| 1                  | Tosc       | External CLKIN Period <sup>(1)</sup>                                                                                                                                                                                                           | 250  | _      | _      | ns    | XT osc mode      |  |  |  |

|                    |            |                                                                                                                                                                                                                                                | 250  | —      | —      | ns    | HS osc mode (04) |  |  |  |

|                    |            |                                                                                                                                                                                                                                                | 100  | —      |        | ns    | HS osc mode (10) |  |  |  |

|                    |            |                                                                                                                                                                                                                                                | 50   | —      |        | ns    | HS osc mode (20) |  |  |  |

|                    |            |                                                                                                                                                                                                                                                | 5.0  | _      | _      | μS    | LP OSC mode      |  |  |  |

|                    |            | Oscillator Period <sup>(1)</sup>                                                                                                                                                                                                               | 250  |        | _      | ns    | RC OSC mode      |  |  |  |

|                    |            |                                                                                                                                                                                                                                                | 250  | —      | 10,000 | ns    | XT OSC mode      |  |  |  |

|                    |            |                                                                                                                                                                                                                                                | 250  | —      | 250    | ns    | HS OSC mode (04) |  |  |  |

|                    |            |                                                                                                                                                                                                                                                | 100  | —      | 250    | ns    | HS osc mode (10) |  |  |  |

|                    |            |                                                                                                                                                                                                                                                | 50   | —      | 250    | ns    | HS osc mode (20) |  |  |  |

|                    |            |                                                                                                                                                                                                                                                | 5.0  | _      | 200    | μS    | LP OSC mode      |  |  |  |

| 2                  | Тсу        | Instruction Cycle Time <sup>(2)</sup>                                                                                                                                                                                                          | —    | 4/Fosc |        | _     |                  |  |  |  |

| 3                  | TosL, TosH | Clock in (OSC1) Low or High                                                                                                                                                                                                                    | 50*  |        | _      | ns    | XT oscillator    |  |  |  |

|                    |            | Time                                                                                                                                                                                                                                           | 20*  | —      | —      | ns    | HS oscillator    |  |  |  |

|                    |            |                                                                                                                                                                                                                                                | 2.0* | _      | —      | μS    | LP oscillator    |  |  |  |

| 4                  | TosR, TosF | Clock in (OSC1) Rise or Fall                                                                                                                                                                                                                   | _    | —      | 25*    | ns    | XT oscillator    |  |  |  |

|                    |            | Time                                                                                                                                                                                                                                           | —    | —      | 25*    | ns    | HS oscillator    |  |  |  |

|                    |            |                                                                                                                                                                                                                                                | —    | —      | 50*    | ns    | LP oscillator    |  |  |  |

| TABLE 13-1: | EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16CR54A |

|-------------|-------------------------------------------------|

|-------------|-------------------------------------------------|

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

when an external clock input is used, the "max" cycle time limit is "Du" (no clock) for all device

2: Instruction cycle period (TcY) equals four times the input oscillator time base period.

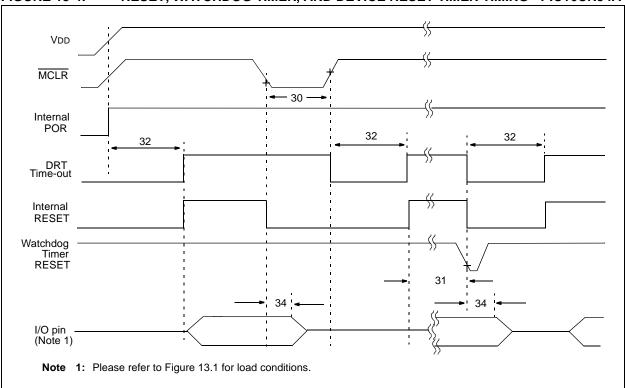

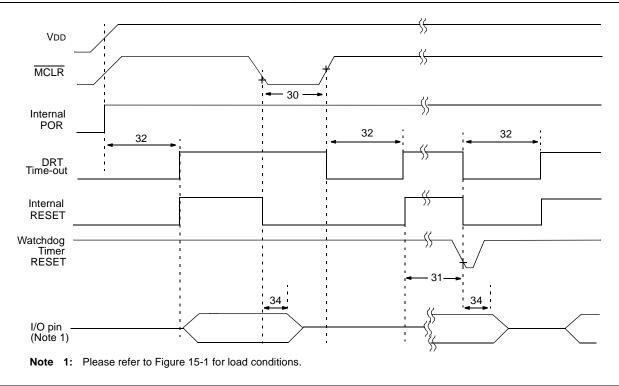

### FIGURE 13-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16CR54A

### TABLE 13-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16CR54A

| AC Chara     | cteristics | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^\circ C \leq TA \leq +70^\circ C \mbox{ for commercial} \\ -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array}$ |      |      |      |       |                   |  |  |

|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|-------------------|--|--|

| Param<br>No. | Symbol     | Characteristic                                                                                                                                                                                                                                                                                                             | Min  | Тур† | Max  | Units | Conditions        |  |  |

| 30           | TmcL       | MCLR Pulse Width (low)                                                                                                                                                                                                                                                                                                     | 1.0* |      |      | μS    | VDD = 5.0V        |  |  |

| 31           | Twdt       | Watchdog Timer Time-out Period<br>(No Prescaler)                                                                                                                                                                                                                                                                           | 7.0* | 18*  | 40*  | ms    | VDD = 5.0V (Comm) |  |  |

| 32           | Tdrt       | Device Reset Timer Period                                                                                                                                                                                                                                                                                                  | 7.0* | 18*  | 30*  | ms    | VDD = 5.0V (Comm) |  |  |

| 34           | Tioz       | I/O Hi-impedance from MCLR Low                                                                                                                                                                                                                                                                                             | _    | _    | 1.0* | μS    |                   |  |  |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### FIGURE 15-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16C54A

### TABLE 15-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16C54A

|                    |        | Standard Operating Condition                                              | ns (unle                                              | ess othe         | erwise    | specifie   | ed)                          |  |  |  |  |  |

|--------------------|--------|---------------------------------------------------------------------------|-------------------------------------------------------|------------------|-----------|------------|------------------------------|--|--|--|--|--|

|                    |        | Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |                                                       |                  |           |            |                              |  |  |  |  |  |

| AC Characteristics |        | -40                                                                       | $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                  |           |            |                              |  |  |  |  |  |

|                    |        | -20                                                                       | $0^{\circ}C \leq TA$                                  | ∖ ≤ <b>+</b> 85° | C for ind | dustrial - | - PIC16LV54A-02I             |  |  |  |  |  |

|                    |        | -40                                                                       | $0^{\circ}C \leq TA$                                  | ∖ ≤ <b>+</b> 125 | °C for e  | xtended    | ł                            |  |  |  |  |  |

| Param              |        |                                                                           |                                                       |                  |           |            |                              |  |  |  |  |  |

| No.                | Symbol | Characteristic                                                            | Min                                                   | Тур†             | Мах       | Units      | Conditions                   |  |  |  |  |  |

| 30                 | TmcL   | MCLR Pulse Width (low)                                                    | 100*                                                  | _                | _         | ns         | VDD = 5.0V                   |  |  |  |  |  |

|                    |        |                                                                           | 1                                                     | —                | —         | μS         | VDD = 5.0V (PIC16LV54A only) |  |  |  |  |  |

| 31                 | Twdt   | Watchdog Timer Time-out                                                   | 9.0*                                                  | 18*              | 30*       | ms         | VDD = 5.0V (Comm)            |  |  |  |  |  |

|                    |        | Period (No Prescaler)                                                     |                                                       |                  |           |            |                              |  |  |  |  |  |

| 32                 | Tdrt   | Device Reset Timer Period                                                 | 9.0*                                                  | 18*              | 30*       | ms         | VDD = 5.0V (Comm)            |  |  |  |  |  |

| 34                 | Tioz   | I/O Hi-impedance from MCLR                                                | _                                                     | _                | 100*      | ns         |                              |  |  |  |  |  |

|                    |        | Low                                                                       | —                                                     |                  | 1μs       | —          | (PIC16LV54A only)            |  |  |  |  |  |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## PIC16C5X

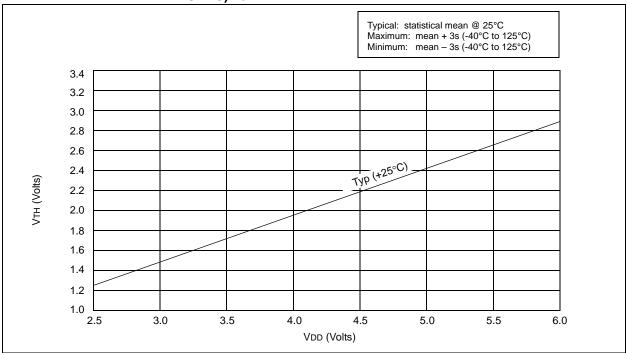

## FIGURE 18-10: VTH (INPUT THRESHOLD TRIP POINT VOLTAGE) OF OSC1 INPUT (IN XT, HS AND LP MODES) vs. VDD

## 19.0 ELECTRICAL CHARACTERISTICS - PIC16LC54C 40MHz

### Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                 | –55°C to +125°C               |

|----------------------------------------------------------------------------------------------------------------|-------------------------------|

| Storage temperature                                                                                            | –65°C to +150°C               |

| Voltage on VDD with respect to VSS                                                                             | 0 to +7.5V                    |

| Voltage on MCLR with respect to Vss                                                                            | 0 to +14V                     |

| Voltage on all other pins with respect to Vss                                                                  | –0.6V to (VDD + 0.6V)         |

| Total power dissipation <sup>(1)</sup>                                                                         | 800 mW                        |

| Max. current out of Vss pin                                                                                    | 150 mA                        |

| Max. current into Vod pin                                                                                      |                               |

| Max. current into an input pin (T0CKI only)                                                                    | ±500 μA                       |

| Input clamp current, liк (Vi <0 or Vi > VDD)                                                                   | ±20 mA                        |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                                 | ±20 mA                        |

| Max. output current sunk by any I/O pin                                                                        | 25 mA                         |

| Max. output current sourced by any I/O pin                                                                     | 20 mA                         |

| Max. output current sourced by a single I/O (Port A, B or C)                                                   | 50 mA                         |

| Max. output current sunk by a single I/O (Port A, B or C)                                                      | 50 mA                         |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) | x IOH} + $\Sigma$ (Vol x Iol) |

**†** NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

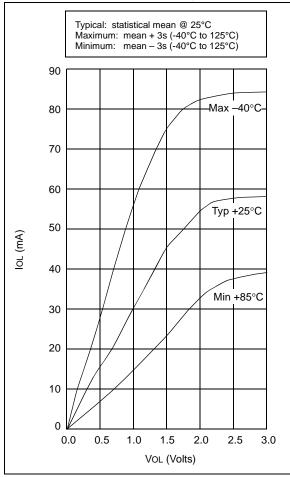

### FIGURE 20-9: IOL vs. VOL, VDD = 5 V

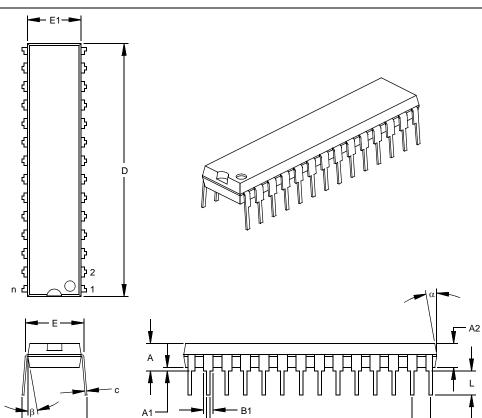

### 28-Lead Skinny Plastic Dual In-line (SP) - 300 mil (PDIP)

в

|                            | Units     | INCHES* |       |       | MILLIMETERS |       |       |

|----------------------------|-----------|---------|-------|-------|-------------|-------|-------|

| Dimensi                    | on Limits | MIN     | NOM   | MAX   | MIN         | NOM   | MAX   |

| Number of Pins             | n         |         | 28    |       |             | 28    |       |

| Pitch                      | р         |         | .100  |       |             | 2.54  |       |

| Top to Seating Plane       | А         | .140    | .150  | .160  | 3.56        | 3.81  | 4.06  |

| Molded Package Thickness   | A2        | .125    | .130  | .135  | 3.18        | 3.30  | 3.43  |

| Base to Seating Plane      | A1        | .015    |       |       | 0.38        |       |       |

| Shoulder to Shoulder Width | Е         | .300    | .310  | .325  | 7.62        | 7.87  | 8.26  |

| Molded Package Width       | E1        | .275    | .285  | .295  | 6.99        | 7.24  | 7.49  |

| Overall Length             | D         | 1.345   | 1.365 | 1.385 | 34.16       | 34.67 | 35.18 |

| Tip to Seating Plane       | L         | .125    | .130  | .135  | 3.18        | 3.30  | 3.43  |

| Lead Thickness             | С         | .008    | .012  | .015  | 0.20        | 0.29  | 0.38  |

| Upper Lead Width           | B1        | .040    | .053  | .065  | 1.02        | 1.33  | 1.65  |

| Lower Lead Width           | В         | .016    | .019  | .022  | 0.41        | 0.48  | 0.56  |

| Overall Row Spacing        | § eB      | .320    | .350  | .430  | 8.13        | 8.89  | 10.92 |

| Mold Draft Angle Top       | α         | 5       | 10    | 15    | 5           | 10    | 15    |

| Mold Draft Angle Bottom    | β         | 5       | 10    | 15    | 5           | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

eВ

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MO-095

Drawing No. C04-070

- p -

Notes:

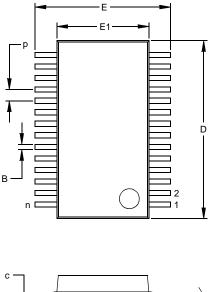

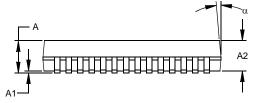

### 28-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |      | INCHES |      |       | MILLIMETERS* |        |  |

|--------------------------|----------|------|--------|------|-------|--------------|--------|--|

| Dimensio                 | n Limits | MIN  | NOM    | MAX  | MIN   | NOM          | MAX    |  |

| Number of Pins           | n        |      | 28     |      |       | 28           |        |  |

| Pitch                    | р        |      | .026   |      |       | 0.65         |        |  |

| Overall Height           | А        | .068 | .073   | .078 | 1.73  | 1.85         | 1.98   |  |

| Molded Package Thickness | A2       | .064 | .068   | .072 | 1.63  | 1.73         | 1.83   |  |

| Standoff §               | A1       | .002 | .006   | .010 | 0.05  | 0.15         | 0.25   |  |

| Overall Width            | Е        | .299 | .309   | .319 | 7.59  | 7.85         | 8.10   |  |

| Molded Package Width     | E1       | .201 | .207   | .212 | 5.11  | 5.25         | 5.38   |  |

| Overall Length           | D        | .396 | .402   | .407 | 10.06 | 10.20        | 10.34  |  |

| Foot Length              | L        | .022 | .030   | .037 | 0.56  | 0.75         | 0.94   |  |

| Lead Thickness           | С        | .004 | .007   | .010 | 0.10  | 0.18         | 0.25   |  |

| Foot Angle               | ф        | 0    | 4      | 8    | 0.00  | 101.60       | 203.20 |  |

| Lead Width               | В        | .010 | .013   | .015 | 0.25  | 0.32         | 0.38   |  |

| Mold Draft Angle Top     | α        | 0    | 5      | 10   | 0     | 5            | 10     |  |

| Mold Draft Angle Bottom  | β        | 0    | 5      | 10   | 0     | 5            | 10     |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-150 Drawing No. C04-073

## APPENDIX A: COMPATIBILITY

To convert code written for PIC16CXX to PIC16C5X, the user should take the following steps:

- 1. Check any CALL, GOTO or instructions that modify the PC to determine if any program memory page select operations (PA2, PA1, PA0 bits) need to be made.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any special function register page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change RESET vector to proper value for processor used.

- 6. Remove any use of the ADDLW, RETURN and SUBLW instructions.

- 7. Rewrite any code segments that use interrupts.

### APPENDIX B: REVISION HISTORY

Revision KE (January 2013)

Added a note to each package outline drawing.

### Μ

| MCLR Reset                                             |    |

|--------------------------------------------------------|----|

| Register values on2                                    | 20 |

| Memory Map                                             |    |

| PIC16C54/CR54/C55                                      | 25 |

| PIC16C56/CR56                                          | 25 |

| PIC16C57/CR57/C58/CR582                                | 25 |

| Memory Organization                                    |    |

| MOVF                                                   | 56 |

| MOVLW                                                  | 56 |

| MOVWF                                                  | 57 |

| MPLAB C17 and MPLAB C18 C Compilers                    | 31 |

| MPLAB ICD In-Circuit Debugger                          | 33 |

| MPLAB ICE High Performance Universal In-Circuit Emulat | or |

| with MPLAB IDE                                         | 32 |

| MPLAB Integrated Development Environment Software      | 31 |

| MPLINK Object Linker/MPLIB Object Librarian            | 32 |

## Ν

| NOP |

|-----|

|-----|

### 0

| One-Time-Programmable (OTP) Devices | 7 |

|-------------------------------------|---|

| -                                   |   |

| OPTION                              | - |

| OPTION Register                     |   |

| Value on reset                      |   |

| Oscillator Configurations           |   |

| Oscillator Types                    |   |

| HS                                  |   |

| LP                                  |   |

| RC                                  |   |

| XT                                  |   |

|                                     |   |

### Ρ

| PA0 bit                                            | .29  |

|----------------------------------------------------|------|

| PA1 bit                                            | .29  |

| Paging                                             | . 31 |

| PC                                                 | . 31 |

| Value on reset                                     | .20  |

| PD bit                                             | , 29 |