# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               |                                                                          |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 20                                                                       |

| Program Memory Size        | 3KB (2K x 12)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                |                                                                          |

| RAM Size                   | 72 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3.25V ~ 6V                                                               |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 28-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c57-xte-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16C5X

## 8-Bit EPROM/ROM-Based CMOS Microcontrollers

#### 1.0 GENERAL DESCRIPTION

The PIC16C5X from Microchip Technology is a family of low cost, high performance, 8-bit fully static, EPROM/ROM-based CMOS microcontrollers. It employs a RISC architecture with only 33 single word/ single cycle instructions. All instructions are single cycle except for program branches which take two cycles. The PIC16C5X delivers performance in an order of magnitude higher than its competitors in the same price category. The 12-bit wide instructions are highly symmetrical resulting in 2:1 code compression over other 8-bit microcontrollers in its class. The easy to use and easy to remember instruction set reduces development time significantly.

The PIC16C5X products are equipped with special features that reduce system cost and power requirements. The Power-on Reset (POR) and Device Reset Timer (DRT) eliminate the need for external RESET circuitry. There are four oscillator configurations to choose from, including the power saving LP (Low Power) oscillator and cost saving RC oscillator. Power saving SLEEP mode, Watchdog Timer and Code Protection features improve system cost, power and reliability.

The UV erasable CERDIP packaged versions are ideal for code development, while the cost effective One Time Programmable (OTP) versions are suitable for production in any volume. The customer can take full advantage of Microchip's price leadership in OTP microcontrollers, while benefiting from the OTP's flexibility.

The PIC16C5X products are supported by a full featured macro assembler, a software simulator, an in-circuit emulator, a low cost development programmer and a full featured programmer. All the tools are supported on IBM<sup>®</sup> PC and compatible machines.

#### 1.1 Applications

The PIC16C5X series fits perfectly in applications ranging from high speed automotive and appliance motor control to low power remote transmitters/receivers, pointing devices and telecom processors. The EPROM technology makes customizing application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages, for through hole or surface mounting, make this microcontroller series perfect for applications with space limitations. Low cost, low power, high performance ease of use and I/O flexibility make the PIC16C5X series very versatile even in areas where no microcontroller use has been considered before (e.g., timer functions, replacement of "glue" logic in larger systems, co-processor applications).

#### 6.3 STATUS Register

This register contains the arithmetic status of the ALU, the RESET status and the page preselect bits for program memories larger than 512 words.

The STATUS Register can be the destination for any instruction, as with any other register. If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not

writable. Therefore, the result of an instruction with the STATUS Register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS Register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS Register because these instructions do not affect the Z, DC or C bits from the STATUS Register. For other instructions which do affect STATUS Bits, see Section 10.0, Instruction Set Summary.

#### REGISTER 6-1: STATUS REGISTER (ADDRESS: 03h)

|          | R/W-0                                                                                                                                                         | R/W-0                              | R/W-0        | R-1          | R-1                        | R/W-x         | R/W-x          | R/W-x          |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------|--------------|----------------------------|---------------|----------------|----------------|--|--|

|          | PA2                                                                                                                                                           | PA1                                | PA0          | TO           | PD                         | Z             | DC             | С              |  |  |

|          | bit 7                                                                                                                                                         |                                    |              |              |                            |               |                | bit 0          |  |  |

| bit 7:   | PA2: This bit                                                                                                                                                 | unused at th                       | is time.     |              |                            |               |                |                |  |  |

|          |                                                                                                                                                               | A2 bit as a ge<br>with future pr   |              | e read/write | bit is not recor           | mmended, sir  | nce this may a | affect upward  |  |  |

| bit 6-5: |                                                                                                                                                               |                                    |              | -            | CR56)(PIC16                |               |                | 58)            |  |  |

|          |                                                                                                                                                               |                                    |              |              | 16C57/CR57,<br>16C57/CR57, |               |                |                |  |  |

|          |                                                                                                                                                               | (400h - 5FFh                       |              |              |                            | FIC 10C30/C   | N00            |                |  |  |

|          | 11 = Page 3                                                                                                                                                   | (600h - 7FFh                       | •            |              |                            |               |                |                |  |  |

|          | Each page is                                                                                                                                                  |                                    | deperal pur  | ose read/wr  | ite bits in devi           | ices which do | not use them   | for program    |  |  |

|          |                                                                                                                                                               |                                    |              |              | affect upward              |               |                |                |  |  |

| bit 4:   | TO: Time-ou                                                                                                                                                   |                                    |              | ,            | •                          |               |                |                |  |  |

|          |                                                                                                                                                               | ver-up, CLRWI<br>ime-out occur     |              | , or sleep i | nstruction                 |               |                |                |  |  |

| bit 3:   | PD: Power-d                                                                                                                                                   | lown bit                           |              |              |                            |               |                |                |  |  |

|          | •                                                                                                                                                             | ver-up or by tl<br>ution of the SI |              |              |                            |               |                |                |  |  |

| bit 2:   | Z: Zero bit                                                                                                                                                   |                                    |              |              |                            |               |                |                |  |  |

|          |                                                                                                                                                               | lt of an arithm<br>It of an arithm |              |              |                            |               |                |                |  |  |

| bit 1:   | DC: Digit car                                                                                                                                                 | ry/borrow bit                      | (for ADDWF a | nd SUBWF in  | structions)                |               |                |                |  |  |

|          | ADDWF                                                                                                                                                         |                                    |              |              |                            |               |                |                |  |  |

|          | <ul> <li>1 = A carry from the 4th low order bit of the result occurred</li> <li>0 = A carry from the 4th low order bit of the result did not occur</li> </ul> |                                    |              |              |                            |               |                |                |  |  |

|          | SUBWF                                                                                                                                                         |                                    |              |              |                            |               |                |                |  |  |

|          | 1 = A borrow from the 4th low order bit of the result did not occur                                                                                           |                                    |              |              |                            |               |                |                |  |  |

|          |                                                                                                                                                               | from the 4th                       |              |              |                            |               |                |                |  |  |

| bit 0:   | -                                                                                                                                                             | row bit (for AI                    |              |              | F instructions             |               | _              |                |  |  |

|          | <b>ADDWF</b><br>1 = A carry o                                                                                                                                 | ocurred                            |              | orrow did n  | ot occur                   | RRF or RLI    |                | , respectively |  |  |

|          | $\pm = \pi \operatorname{carry} 0$                                                                                                                            | locurrou                           | / · ·        |              |                            |               |                |                |  |  |

| Legena:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared        | x = bit is unknown |

#### 8.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer (WDT), respectively (Section 9.2.1). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT, but not both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the WDT, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a RESET, the prescaler contains all '0's.

#### 8.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 8-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

#### EXAMPLE 8-1: CHANGING PRESCALER (TIMER0→WDT)

| CLRWDT            | ;Clear WDT              |

|-------------------|-------------------------|

| CLRF TMR0         | Clear TMR0 & Prescaler  |

| MOVLW B'00xx1111' | ;Last 3 instructions in |

|                   | this example            |

| OPTION            | ;are required only if   |

|                   | ;desired                |

| CLRWDT            | ;PS<2:0> are 000 or     |

|                   | ;001                    |

| MOVLW B'00xx1xxx' | ;Set Prescaler to       |

| OPTION            | ;desired WDT rate       |

|                   |                         |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 8-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

## EXAMPLE 8-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| MOVLW  | B'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

|        |             | ;clock source       |

OPTION

| Mnemo            | Mnemonic, Description Cycles |                              | Cualaa           | 12-1 | Bit Opc | ode  | Status   |       |

|------------------|------------------------------|------------------------------|------------------|------|---------|------|----------|-------|

| Opera            | nds                          | Description                  | Cycles           | MSb  |         | LSb  | Affected | Notes |

| ADDWF            | f,d                          | Add W and f                  | 1                | 0001 | 11df    | ffff | C,DC,Z   | 1,2,4 |

| ANDWF            | f,d                          | AND W with f                 | 1                | 0001 | 01df    | ffff | Z        | 2,4   |

| CLRF             | f                            | Clear f                      | 1                | 0000 | 011f    | ffff | Z        | 4     |

| CLRW             | -                            | Clear W                      | 1                | 0000 | 0100    | 0000 | Z        |       |

| COMF             | f, d                         | Complement f                 | 1                | 0010 | 01df    | ffff | Z        |       |

| DECF             | f, d                         | Decrement f                  | 1                | 0000 | 11df    | ffff | Z        | 2,4   |

| DECFSZ           | f, d                         | Decrement f, Skip if 0       | 1 <sup>(2)</sup> | 0010 | 11df    | ffff | None     | 2,4   |

| INCF             | f, d                         | Increment f                  | 1                | 0010 | 10df    | ffff | Z        | 2,4   |

| INCFSZ           | f, d                         | Increment f, Skip if 0       | 1 <sup>(2)</sup> | 0011 | 11df    | ffff | None     | 2,4   |

| IORWF            | f, d                         | Inclusive OR W with f        | 1                | 0001 | 00df    | ffff | Z        | 2,4   |

| MOVF             | f, d                         | Move f                       | 1                | 0010 | 00df    | ffff | Z        | 2,4   |

| MOVWF            | f                            | Move W to f                  | 1                | 0000 | 001f    | ffff | None     | 1,4   |

| NOP              | -                            | No Operation                 | 1                | 0000 | 0000    | 0000 | None     |       |

| RLF              | f, d                         | Rotate left f through Carry  | 1                | 0011 | 01df    | ffff | С        | 2,4   |

| RRF              | f, d                         | Rotate right f through Carry | 1                | 0011 | 00df    | ffff | С        | 2,4   |

| SUBWF            | f, d                         | Subtract W from f            | 1                | 0000 | 10df    | ffff | C,DC,Z   | 1,2,4 |

| SWAPF            | f, d                         | Swap f                       | 1                | 0011 | 10df    | ffff | None     | 2,4   |

| XORWF            | f, d                         | Exclusive OR W with f        | 1                | 0001 | 10df    | ffff | Z        | 2,4   |

| <b>BIT-ORIEN</b> | TED FIL                      | E REGISTER OPERATIONS        | •                |      |         |      |          |       |

| BCF              | f, b                         | Bit Clear f                  | 1                | 0100 | bbbf    | ffff | None     | 2,4   |

| BSF              | f, b                         | Bit Set f                    | 1                | 0101 | bbbf    | ffff | None     | 2,4   |

| BTFSC            | f, b                         | Bit Test f, Skip if Clear    | 1 (2)            | 0110 | bbbf    | ffff | None     |       |

| BTFSS            | f, b                         | Bit Test f, Skip if Set      | 1 (2)            | 0111 | bbbf    | ffff | None     |       |

| LITERAL A        | ND CON                       | ITROL OPERATIONS             | •                |      |         |      |          |       |

| ANDLW            | k                            | AND literal with W           | 1                | 1110 | kkkk    | kkkk | Z        |       |

| CALL             | k                            | Call subroutine              | 2                | 1001 | kkkk    | kkkk | None     | 1     |

| CLRWDT           | k                            | Clear Watchdog Timer         | 1                | 0000 | 0000    | 0100 | TO, PD   |       |

| GOTO             | k                            | Unconditional branch         | 2                | 101k | kkkk    | kkkk | None     |       |

| IORLW            | k                            | Inclusive OR Literal with W  | 1                | 1101 | kkkk    | kkkk | Z        |       |

| MOVLW            | k                            | Move Literal to W            | 1                | 1100 | kkkk    | kkkk | None     |       |

| OPTION           | k                            | Load OPTION register         | 1                | 0000 | 0000    | 0010 | None     |       |

| RETLW            | k                            | Return, place Literal in W   | 2                | 1000 | kkkk    | kkkk | None     |       |

| SLEEP            | _                            | Go into standby mode         | 1                | 0000 | 0000    | 0011 | TO, PD   |       |

| TRIS             | f                            | Load TRIS register           | 1                | 0000 | 0000    | Offf | None     | 3     |

| XORLW            | k                            | Exclusive OR Literal to W    | 1                | 1111 | kkkk    | kkkk | Z        |       |

#### TABLE 10-2: INSTRUCTION SET SUMMARY

**Note 1:** The 9th bit of the program counter will be forced to a '0' by any instruction that writes to the PC except for GOTO (see Section 6.5 for more on program counter).

2: When an I/O register is modified as a function of itself (e.g. MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**3:** The instruction TRIS f, where f = 5, 6 or 7 causes the contents of the W register to be written to the tristate latches of PORTA, B or C respectively. A '1' forces the pin to a hi-impedance state and disables the output buffers.

**4:** If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared (if assigned to TMR0).

| ADDWF                                                       | Add W and f                                                                                                                                                                   |                              |      |  |  |  |  |  |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|--|--|--|--|--|

| Syntax:                                                     | [ label ] A                                                                                                                                                                   | [ label ] ADDWF f,d          |      |  |  |  |  |  |

| Operands:                                                   | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                |                              |      |  |  |  |  |  |

| Operation:                                                  | (W) + (f)                                                                                                                                                                     | $\rightarrow$ (dest)         |      |  |  |  |  |  |

| Status Affected:                                            | C, DC, Z                                                                                                                                                                      |                              |      |  |  |  |  |  |

| Encoding:                                                   | 0001                                                                                                                                                                          | 11df                         | ffff |  |  |  |  |  |

| Description:                                                | Add the contents of the W register<br>and register 'f'. If 'd' is 0 the result<br>is stored in the W register. If 'd' is<br>'1' the result is stored back in<br>register 'f'. |                              |      |  |  |  |  |  |

| Words:                                                      | 1                                                                                                                                                                             |                              |      |  |  |  |  |  |

| Cycles:                                                     | 1                                                                                                                                                                             |                              |      |  |  |  |  |  |

| Example:                                                    | ADDWF                                                                                                                                                                         | TEMP_RE                      | G, 0 |  |  |  |  |  |

| Before Instr<br>W<br>TEMP_I<br>After Instruc<br>W<br>TEMP_F | =<br>REG =<br>ction<br>=                                                                                                                                                      | 0x17<br>0xC2<br>0xD9<br>0xC2 |      |  |  |  |  |  |

| ANDWF                                                      | AND W with f                                                                                                                                                                            |  |  |  |  |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                                    | [label] ANDWF f,d                                                                                                                                                                       |  |  |  |  |

| Operands:                                                  | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                          |  |  |  |  |

| Operation:                                                 | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                      |  |  |  |  |

| Status Affected:                                           | Z                                                                                                                                                                                       |  |  |  |  |

| Encoding:                                                  | 0001 01df ffff                                                                                                                                                                          |  |  |  |  |

| Description:                                               | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is 0<br>the result is stored in the W regis-<br>ter. If 'd' is '1' the result is stored<br>back in register 'f'. |  |  |  |  |

| Words:                                                     | 1                                                                                                                                                                                       |  |  |  |  |

| Cycles:                                                    | 1                                                                                                                                                                                       |  |  |  |  |

| Example:                                                   | ANDWF TEMP_REG, 1                                                                                                                                                                       |  |  |  |  |

| Before Instru<br>W<br>TEMP_<br>After Instruc<br>W<br>TEMP_ | = 0x17<br>REG = 0xC2<br>tion<br>= 0x17                                                                                                                                                  |  |  |  |  |

| ANDLW                                        | AND literal with W                                                                                                           |  |  |  |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                      | [ <i>label</i> ] ANDLW k                                                                                                     |  |  |  |  |  |

| Operands:                                    | $0 \le k \le 255$                                                                                                            |  |  |  |  |  |

| Operation:                                   | (W).AND. (k) $\rightarrow$ (W)                                                                                               |  |  |  |  |  |

| Status Affected:                             | Z                                                                                                                            |  |  |  |  |  |

| Encoding:                                    | 1110 kkkk kkkk                                                                                                               |  |  |  |  |  |

| Description:                                 | The contents of the W register are<br>AND'ed with the eight-bit literal 'k'.<br>The result is placed in the W regis-<br>ter. |  |  |  |  |  |

| Words:                                       | 1                                                                                                                            |  |  |  |  |  |

| Cycles:                                      | 1                                                                                                                            |  |  |  |  |  |

| Example:                                     | ANDLW H'5F'                                                                                                                  |  |  |  |  |  |

| Before Instru<br>W =<br>After Instruc<br>W = | 0xA3                                                                                                                         |  |  |  |  |  |

| BCF                                                        | Bit Clear f                                                        |              |             |  |  |  |  |  |

|------------------------------------------------------------|--------------------------------------------------------------------|--------------|-------------|--|--|--|--|--|

| Syntax:                                                    | [label] BCF f,b                                                    |              |             |  |  |  |  |  |

| Operands:                                                  | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |              |             |  |  |  |  |  |

| Operation:                                                 | $0 \rightarrow (f < b$                                             | >)           |             |  |  |  |  |  |

| Status Affected:                                           | None                                                               |              |             |  |  |  |  |  |

| Encoding:                                                  | 0100                                                               | bbbf         | ffff        |  |  |  |  |  |

| Description:                                               | Bit 'b' in                                                         | register 'f' | is cleared. |  |  |  |  |  |

| Words:                                                     | 1                                                                  |              |             |  |  |  |  |  |

| Cycles:                                                    | 1                                                                  |              |             |  |  |  |  |  |

| Example:                                                   | BCF                                                                | FLAG_RE      | IG, 7       |  |  |  |  |  |

| Before Instruction<br>FLAG_REG = 0xC7<br>After Instruction |                                                                    |              |             |  |  |  |  |  |

| FLAG_F                                                     | REG =                                                              | 0x47         |             |  |  |  |  |  |

#### 11.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC MCUs and can be used to develop for this and other PIC microcontrollers. The MPLAB ICD utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>TM</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

#### 11.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in Stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In Stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC devices. It can also set code protection in this mode.

#### 11.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

#### 11.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

#### 11.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the  $I^2C^{TM}$  bus and separate headers for connection to an LCD module and a keypad.

NOTES:

#### 13.2 DC Characteristics: PIC16CR54A-04E, 10E, 20E (Extended)

| PIC16CR54A-04E, 10E, 20E<br>(Extended) |        |                                                                                       | Standard Operating Conditions (unless otherwise specified<br>Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                   |                 |                |                                                                                      |  |

|----------------------------------------|--------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|----------------|--------------------------------------------------------------------------------------|--|

| Param<br>No.                           | Symbol | Characteristic                                                                        | Min                                                                                                                                     | Тур†              | Max             | Units          | Conditions                                                                           |  |

| D001                                   | Vdd    | Supply Voltage<br>RC, XT and LP modes<br>HS mode                                      | 3.25<br>4.5                                                                                                                             |                   | 6.0<br>5.5      | V<br>V         |                                                                                      |  |

| D002                                   | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>                                             | —                                                                                                                                       | 1.5*              | —               | V              | Device in SLEEP mode                                                                 |  |

| D003                                   | VPOR   | VDD Start Voltage to ensure<br>Power-on Reset                                         | —                                                                                                                                       | Vss               | —               | V              | See Section 5.1 for details on<br>Power-on Reset                                     |  |

| D004                                   | Svdd   | VDD Rise Rate to ensure Power-<br>on Reset                                            | 0.05*                                                                                                                                   | _                 |                 | V/ms           | See Section 5.1 for details on<br>Power-on Reset                                     |  |

| D010                                   | IDD    | Supply Current <sup>(2)</sup><br>RC <sup>(3)</sup> and XT modes<br>HS mode<br>HS mode |                                                                                                                                         | 1.8<br>4.8<br>9.0 | 3.3<br>10<br>20 | mA<br>mA<br>mA | Fosc = 4.0 MHz, Vdd = 5.5V<br>Fosc = 10 MHz, Vdd = 5.5V<br>Fosc = 16 MHz, Vdd = 5.5V |  |

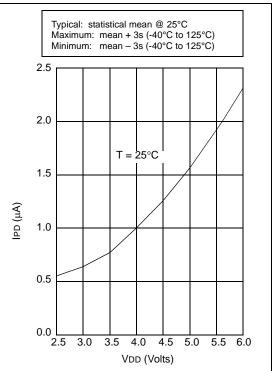

| D020                                   | IPD    | Power-down Current <sup>(2)</sup>                                                     |                                                                                                                                         | 5.0<br>0.8        | 22<br>18        | μΑ<br>μΑ       | VDD = 3.25V, WDT enabled<br>VDD = 3.25V, WDT disabled                                |  |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

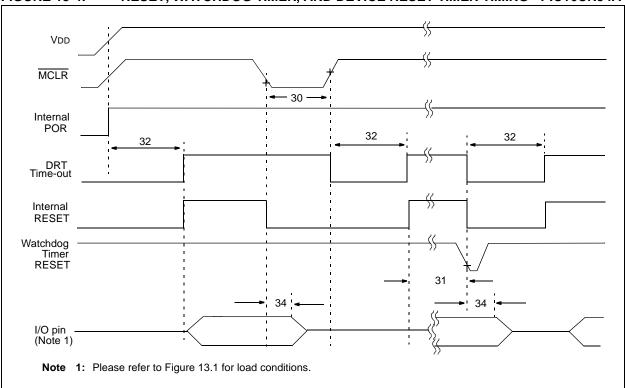

#### FIGURE 13-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16CR54A

#### TABLE 13-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16CR54A

| AC Chara     | haracteristics Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                                  |      |     |      |    |                   |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------|-----|------|----|-------------------|

| Param<br>No. | Symbol                                                                                                                                                                                                                                                                  | Characteristic Min Typ† Max Units Conditions     |      |     |      |    | Conditions        |

| 30           | TmcL                                                                                                                                                                                                                                                                    | MCLR Pulse Width (low)                           | 1.0* |     |      | μS | VDD = 5.0V        |

| 31           | Twdt                                                                                                                                                                                                                                                                    | Watchdog Timer Time-out Period<br>(No Prescaler) | 7.0* | 18* | 40*  | ms | VDD = 5.0V (Comm) |

| 32           | Tdrt                                                                                                                                                                                                                                                                    | Device Reset Timer Period                        | 7.0* | 18* | 30*  | ms | VDD = 5.0V (Comm) |

| 34           | Tioz                                                                                                                                                                                                                                                                    | I/O Hi-impedance from MCLR Low                   | _    | _   | 1.0* | μS |                   |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### FIGURE 14-5: TYPICAL IPD vs. VDD, WATCHDOG DISABLED

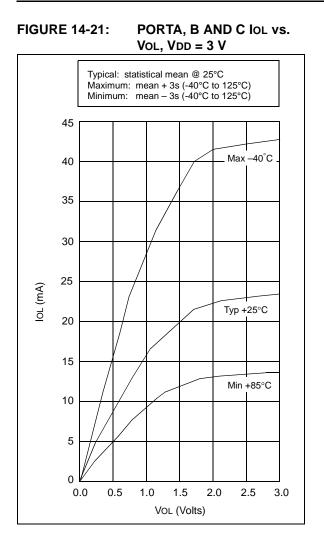

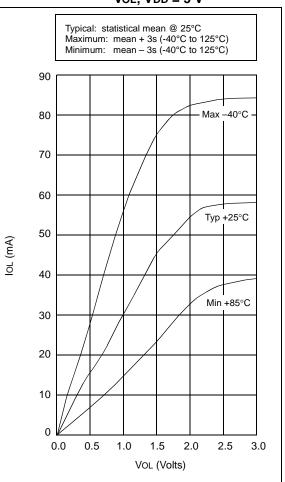

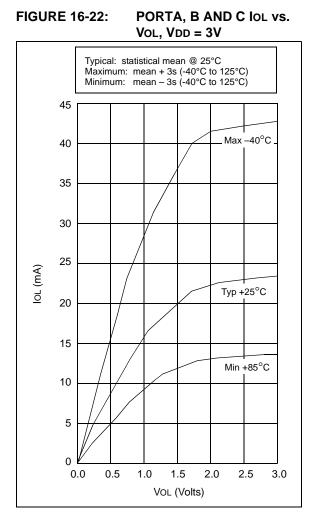

#### FIGURE 14-22: PORTA, B AND C IOL vs. VoL, VDD = 5 V

#### 15.3 DC Characteristics: PIC16LV54A-02 (Commercial) PIC16LV54A-02I (Industrial)

| PIC16LV54A-02<br>PIC16LV54A-02I<br>(Commercial, Industrial) |                       |                                                                                                                     | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -20^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \end{array}$ |                           |                        |                      |                                                                                                                |  |

|-------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------|----------------------|----------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.                                                | Symbol Characteristic |                                                                                                                     | Min                                                                                                                                                                                                                                                              | Тур†                      | Max                    | Units                | Conditions                                                                                                     |  |

| D001                                                        | Vdd                   | Supply Voltage<br>RC and XT modes                                                                                   | 2.0                                                                                                                                                                                                                                                              | _                         | 3.8                    | V                    |                                                                                                                |  |

| D002                                                        | Vdr                   | RAM Data Retention<br>Voltage <sup>(1)</sup>                                                                        | —                                                                                                                                                                                                                                                                | 1.5*                      | —                      | V                    | Device in SLEEP mode                                                                                           |  |

| D003                                                        | VPOR                  | VDD Start Voltage to ensure<br>Power-on Reset                                                                       | —                                                                                                                                                                                                                                                                | Vss                       | —                      | V                    | See Section 5.1 for details on<br>Power-on Reset                                                               |  |

| D004                                                        | SVDD                  | VDD Rise Rate to ensure<br>Power-on Reset                                                                           | 0.05*                                                                                                                                                                                                                                                            |                           | —                      | V/ms                 | See Section 5.1 for details on<br>Power-on Reset                                                               |  |

| D010                                                        | IDD                   | <b>Supply Current<sup>(2)</sup></b><br>RC <sup>(3)</sup> and XT modes<br>LP mode, Commercial<br>LP mode, Industrial |                                                                                                                                                                                                                                                                  | 0.5<br>11<br>14           | —<br>27<br>35          | μA                   | Fosc = 2.0 MHz, VDD = 3.0V<br>Fosc = 32 kHz, VDD = 2.5V WDT disabled<br>Fosc = 32 kHz, VDD = 2.5V WDT disabled |  |

| D020                                                        | IPD                   | <b>Power-down Current<sup>(2,4)</sup></b><br>Commercial<br>Commercial<br>Industrial<br>Industrial                   |                                                                                                                                                                                                                                                                  | 2.5<br>0.25<br>3.5<br>0.3 | 12<br>4.0<br>14<br>5.0 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 2.5V, WDT enabled<br>VDD = 2.5V, WDT disabled<br>VDD = 2.5V, WDT enabled<br>VDD = 2.5V, WDT disabled     |  |

These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to VSS, T0CKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- **3:** Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

- 4: The oscillator start-up time can be as much as 8 seconds for XT and LP oscillator selection on wake-up from SLEEP mode or during initial power-up.

#### 15.5 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| S                                     |                                                                                                                                                                               |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                       |                                                                                                                                                                               |

|                                       |                                                                                                                                                                               |

| Frequency                             | T Time                                                                                                                                                                        |

| case letters (pp) and their meanings: |                                                                                                                                                                               |

|                                       |                                                                                                                                                                               |

| to                                    | mc MCLR                                                                                                                                                                       |

| CLKOUT                                | osc oscillator                                                                                                                                                                |

| cycle time                            | os OSC1                                                                                                                                                                       |

| device reset timer                    | t0 T0CKI                                                                                                                                                                      |

| I/O port                              | wdt watchdog timer                                                                                                                                                            |

| case letters and their meanings:      |                                                                                                                                                                               |

|                                       |                                                                                                                                                                               |

| Fall                                  | P Period                                                                                                                                                                      |

| High                                  | R Rise                                                                                                                                                                        |

| Invalid (Hi-impedance)                | V Valid                                                                                                                                                                       |

| Low                                   | Z Hi-impedance                                                                                                                                                                |

|                                       | case letters (pp) and their meanings:<br>CLKOUT<br>cycle time<br>device reset timer<br>I/O port<br>case letters and their meanings:<br>Fall<br>High<br>Invalid (Hi-impedance) |

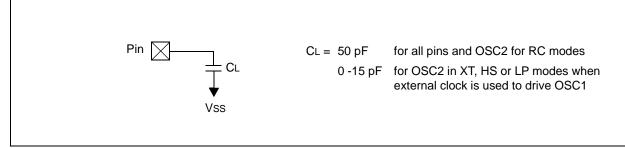

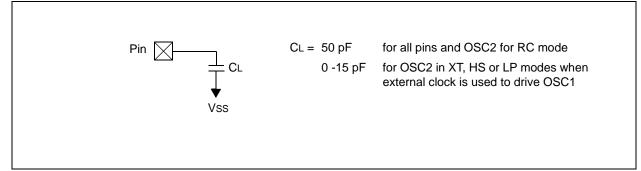

#### FIGURE 15-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS - PIC16C54A

#### 16.0 DEVICE CHARACTERIZATION - PIC16C54A

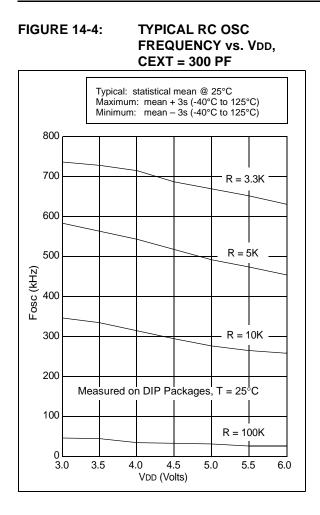

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

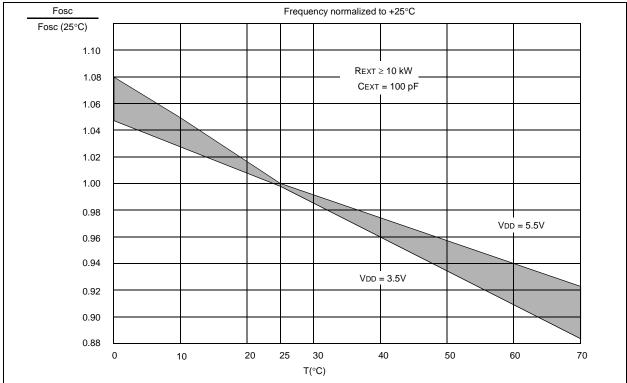

FIGURE 16-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

| TABLE 16-1: | RC OSCILLATOR FREQUENCIES |

|-------------|---------------------------|

|-------------|---------------------------|

| Сехт   | Rext |         | rage<br>5 V, 25°C |

|--------|------|---------|-------------------|

| 20 pF  | 3.3K | 5 MHz   | ± 27%             |

|        | 5K   | 3.8 MHz | ± 21%             |

|        | 10K  | 2.2 MHz | ± 21%             |

|        | 100K | 262 kHz | ± 31%             |

| 100 pF | 3.3K | 1.6 MHz | ± 13%             |

|        | 5K   | 1.2 MHz | ± 13%             |

|        | 10K  | 684 kHz | ± 18%             |

|        | 100K | 71 kHz  | ± 25%             |

| 300 pF | 3.3K | 660 kHz | ± 10%             |

|        | 5.0K | 484 kHz | ± 14%             |

|        | 10K  | 267 kHz | ± 15%             |

|        | 100K | 29 kHz  | ± 19%             |

The frequencies are measured on DIP packages.

The percentage variation indicated here is part-to-part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviation from average value for VDD = 5V.

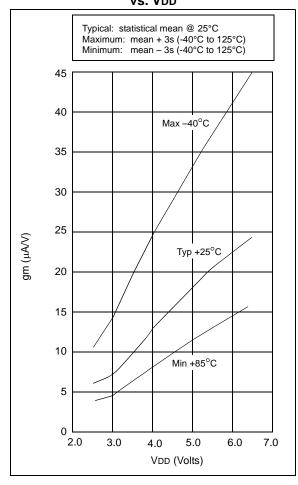

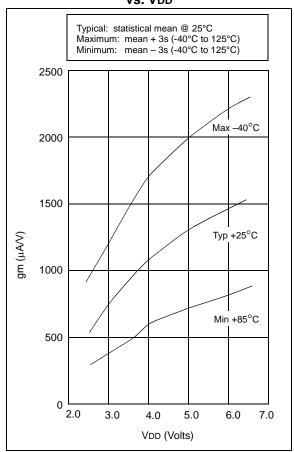

#### FIGURE 16-18: TRANSCONDUCTANCE (gm) OF LP OSCILLATOR vs. VDD

#### FIGURE 16-19:

#### TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

TABLE 16-2:INPUT CAPACITANCE FOR<br/>PIC16C54A/C58A

| Pin         | Typical Capacitance (pF) |          |  |  |  |

|-------------|--------------------------|----------|--|--|--|

| FIII        | 18L PDIP                 | 18L SOIC |  |  |  |

| RA port     | 5.0                      | 4.3      |  |  |  |

| RB port     | 5.0                      | 4.3      |  |  |  |

| MCLR        | 17.0                     | 17.0     |  |  |  |

| OSC1        | 4.0                      | 3.5      |  |  |  |

| OSC2/CLKOUT | 4.3                      | 3.5      |  |  |  |

| TOCKI       | 3.2                      | 2.8      |  |  |  |

All capacitance values are typical at 25°C. A part-to-part variation of  $\pm 25\%$  (three standard deviations) should be taken into account.

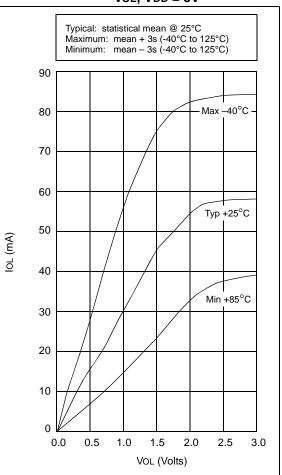

#### FIGURE 16-23: PORTA, B AND C IOL vs. VOL, VDD = 5V

#### 17.1 DC Characteristics:PIC16C54C/C55A/C56A/C57C/C58B-04, 20 (Commercial, Industrial) PIC16LC54C/LC55A/LC56A/LC57C/LC58B-04 (Commercial, Industrial) PIC16CR54C/CR56A/CR57C/CR58B-04, 20 (Commercial, Industrial) PIC16LCR54C/LCR56A/LCR57C/LCR58B-04 (Commercial, Industrial)

| PIC16LC5X<br>PIC16LCR5X<br>(Commercial, Industrial) |        |                                 | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                                                                                                                                                                                                                                                                  |            |                    |                                                   |  |  |

|-----------------------------------------------------|--------|---------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------|---------------------------------------------------|--|--|

| PIC16C5X<br>PIC16CR5X<br>(Commercial, Industrial)   |        |                                 |                                                       | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \end{array}$ |            |                    |                                                   |  |  |

| Param<br>No.                                        | Symbol | Characteristic/Device           | Min                                                   | Тур†                                                                                                                                                                                                                                                             | Max        | x Units Conditions |                                                   |  |  |

|                                                     | IDD    | Supply Current <sup>(2,3)</sup> |                                                       |                                                                                                                                                                                                                                                                  |            |                    |                                                   |  |  |

| D010                                                |        | PIC16LC5X                       |                                                       | 0.5                                                                                                                                                                                                                                                              | 2.4        | mA                 | Fosc = 4.0 MHz, VDD = 5.5V, XT and                |  |  |

|                                                     |        |                                 | —                                                     | 11                                                                                                                                                                                                                                                               | 27         | μA                 | RC modes                                          |  |  |

|                                                     |        |                                 |                                                       |                                                                                                                                                                                                                                                                  |            |                    | FOSC = $32 \text{ kHz}$ , VDD = 2.5V, LP mode,    |  |  |

|                                                     |        |                                 | _                                                     | 14                                                                                                                                                                                                                                                               | 35         | μA                 | Commercial<br>Fosc = 32 kHz, VDD = 2.5V, LP mode, |  |  |

| <b>BA</b> 4 <b>A</b> 4                              |        | DIOLOGEY                        |                                                       |                                                                                                                                                                                                                                                                  |            |                    |                                                   |  |  |

| D010A                                               |        | PIC16C5X                        |                                                       | 1.8                                                                                                                                                                                                                                                              | 2.4        | mA                 | FOSC = 4 MHz, $VDD = 5.5V$ , $XT$ and $RC$        |  |  |

|                                                     |        |                                 | _                                                     | 2.6<br>4.5                                                                                                                                                                                                                                                       | 3.6*<br>16 | mA<br>mA           | modes<br>Fosc = 10 MHz, VDD = 3.0V, HS mode       |  |  |

|                                                     |        |                                 |                                                       | 14                                                                                                                                                                                                                                                               | 32         | μA                 | FOSC = 20  MHz,  VDD = 5.5V,  HS mode             |  |  |

|                                                     |        |                                 |                                                       |                                                                                                                                                                                                                                                                  | 02         | μη                 | FOSC = 32  kHz,  VDD = 3.0 V,  LP mode,           |  |  |

|                                                     |        |                                 | _                                                     | 17                                                                                                                                                                                                                                                               | 40         | μA                 | Commercial                                        |  |  |

|                                                     |        |                                 |                                                       |                                                                                                                                                                                                                                                                  |            |                    | Fosc = 32 kHz, VDD = 3.0V, LP mode,<br>Industrial |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

\* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to VSS, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

#### 17.4 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. Tp | 2. TppS                                 |                    |  |  |  |  |  |

|-------|-----------------------------------------|--------------------|--|--|--|--|--|

| Т     |                                         |                    |  |  |  |  |  |

| F     | Frequency                               | T Time             |  |  |  |  |  |

| Lowe  | ercase letters (pp) and their meanings: |                    |  |  |  |  |  |

| рр    |                                         |                    |  |  |  |  |  |

| 2     | to                                      | mc MCLR            |  |  |  |  |  |

| ck    | CLKOUT                                  | osc oscillator     |  |  |  |  |  |

| су    | cycle time                              | os OSC1            |  |  |  |  |  |

| drt   | device reset timer                      | t0 T0CKI           |  |  |  |  |  |

| io    | I/O port                                | wdt watchdog timer |  |  |  |  |  |

| Uppe  | Uppercase letters and their meanings:   |                    |  |  |  |  |  |

| S     |                                         |                    |  |  |  |  |  |

| F     | Fall                                    | P Period           |  |  |  |  |  |

| н     | High                                    | R Rise             |  |  |  |  |  |

| T     | Invalid (Hi-impedance)                  | V Valid            |  |  |  |  |  |

| L     | Low                                     | Z Hi-impedance     |  |  |  |  |  |

#### FIGURE 17-5: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS -PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/C58B/CR58B-04, 20

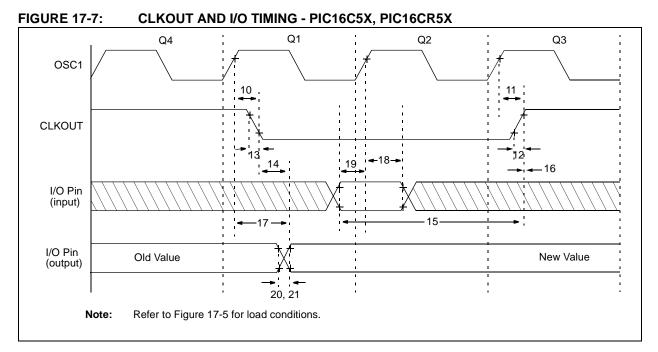

|             | ALVAUT AND VA TIMINA DEALUDENENTA DIALAASY DIALAADSY     |

|-------------|----------------------------------------------------------|

| IABLE 17-2: | CLKOUT AND I/O TIMING REQUIREMENTS - PIC16C5X, PIC16CR5X |

| AC Characteristics |          |                                                               |              |      |      |       |  |

|--------------------|----------|---------------------------------------------------------------|--------------|------|------|-------|--|

| Param<br>No.       | Symbol   | Characteristic                                                | Min          | Тур† | Max  | Units |  |

| 10                 | TosH2ckL | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                               | _            | 15   | 30** | ns    |  |

| 11                 | TosH2ckH | OSC1↑ to CLKOUT↑ <sup>(1)</sup>                               | _            | 15   | 30** | ns    |  |

| 12                 | TckR     | CLKOUT rise time <sup>(1)</sup>                               | —            | 5.0  | 15** | ns    |  |

| 13                 | TckF     | CLKOUT fall time <sup>(1)</sup>                               | —            | 5.0  | 15** | ns    |  |

| 14                 | TckL2ioV | CLKOUT↓ to Port out valid <sup>(1)</sup>                      | —            | —    | 40** | ns    |  |

| 15                 | TioV2ckH | Port in valid before CLKOUT <sup>(1)</sup>                    | 0.25 TCY+30* | —    | _    | ns    |  |

| 16                 | TckH2iol | Port in hold after CLKOUT <sup>(1)</sup>                      | 0*           | —    | _    | ns    |  |

| 17                 | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(2)</sup> | —            | —    | 100* | ns    |  |

| 18                 | TosH2iol | OSC1↑ (Q2 cycle) to Port input invalid<br>(I/O in hold time)  | TBD          | —    | _    | ns    |  |

| 19                 | TioV2osH | Port input valid to OSC1↑<br>(I/O in setup time)              | TBD          | —    | —    | ns    |  |

| 20                 | TioR     | Port output rise time <sup>(2)</sup>                          | _            | 10   | 25** | ns    |  |

| 21                 | TioF     | Port output fall time <sup>(2)</sup>                          | —            | 10   | 25** | ns    |  |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested. No characterization data available at this time.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

**2:** Refer to Figure 17-5 for load conditions.

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755 China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889