#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

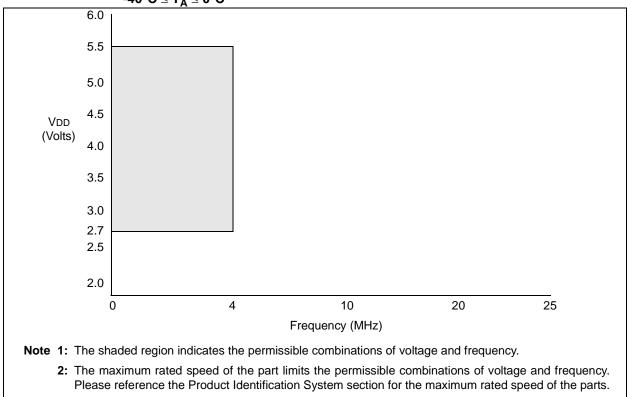

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 20                                                                        |

| Program Memory Size        | 3KB (2K x 12)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 72 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6.25V                                                                |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c57-xti-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

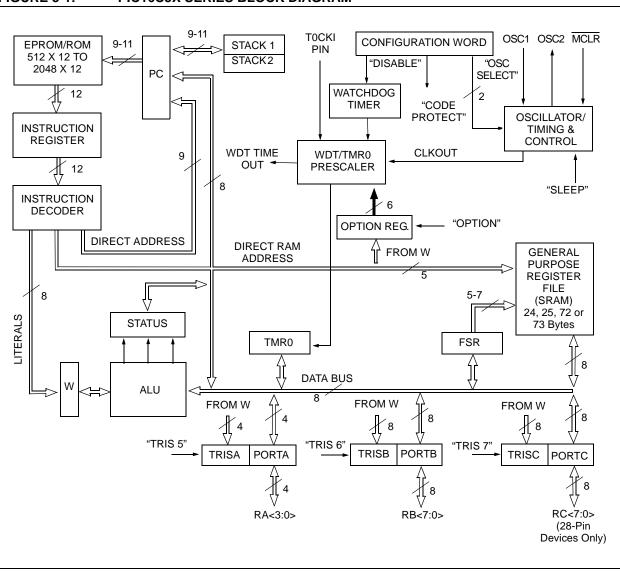

#### FIGURE 3-1: PIC16C5X SERIES BLOCK DIAGRAM

| Pin Name    | Pin Numbe |      | er   | er Pin |      | Description                                                                                                                                                                                                       |

|-------------|-----------|------|------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name    | DIP       | SOIC | SSOP | Туре   | Туре | Description                                                                                                                                                                                                       |

| RA0         | 6         | 6    | 5    | I/O    | TTL  | Bi-directional I/O port                                                                                                                                                                                           |

| RA1         | 7         | 7    | 6    | I/O    | TTL  |                                                                                                                                                                                                                   |

| RA2         | 8         | 8    | 7    | I/O    | TTL  |                                                                                                                                                                                                                   |

| RA3         | 9         | 9    | 8    | I/O    | TTL  |                                                                                                                                                                                                                   |

| RB0         | 10        | 10   | 9    | I/O    | TTL  | Bi-directional I/O port                                                                                                                                                                                           |

| RB1         | 11        | 11   | 10   | I/O    | TTL  |                                                                                                                                                                                                                   |

| RB2         | 12        | 12   | 11   | I/O    | TTL  |                                                                                                                                                                                                                   |

| RB3         | 13        | 13   | 12   | I/O    | TTL  |                                                                                                                                                                                                                   |

| RB4         | 14        | 14   | 13   | I/O    | TTL  |                                                                                                                                                                                                                   |

| RB5         | 15        | 15   | 15   | I/O    | TTL  |                                                                                                                                                                                                                   |

| RB6         | 16        | 16   | 16   | I/O    | TTL  |                                                                                                                                                                                                                   |

| RB7         | 17        | 17   | 17   | I/O    | TTL  |                                                                                                                                                                                                                   |

| RC0         | 18        | 18   | 18   | I/O    | TTL  | Bi-directional I/O port                                                                                                                                                                                           |

| RC1         | 19        | 19   | 19   | I/O    | TTL  |                                                                                                                                                                                                                   |

| RC2         | 20        | 20   | 20   | I/O    | TTL  |                                                                                                                                                                                                                   |

| RC3         | 21        | 21   | 21   | I/O    | TTL  |                                                                                                                                                                                                                   |

| RC4         | 22        | 22   | 22   | I/O    | TTL  |                                                                                                                                                                                                                   |

| RC5         | 23        | 23   | 23   | I/O    | TTL  |                                                                                                                                                                                                                   |

| RC6         | 24        | 24   | 24   | I/O    | TTL  |                                                                                                                                                                                                                   |

| RC7         | 25        | 25   | 25   | I/O    | TTL  |                                                                                                                                                                                                                   |

| TOCKI       | 1         | 1    | 2    | Ι      | ST   | Clock input to Timer0. Must be tied to Vss or VDD, if not in use, to reduce current consumption.                                                                                                                  |

| MCLR        | 28        | 28   | 28   | I      | ST   | Master clear (RESET) input. This pin is an active low RESET to the device.                                                                                                                                        |

| OSC1/CLKIN  | 27        | 27   | 27   | I      | ST   | Oscillator crystal input/external clock source input.                                                                                                                                                             |

| OSC2/CLKOUT | 26        | 26   | 26   | 0      | _    | Oscillator crystal output. Connects to crystal or resonator<br>in crystal Oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| Vdd         | 2         | 2    | 3,4  | Р      | _    | Positive supply for logic and I/O pins.                                                                                                                                                                           |

| Vss         | 4         | 4    | 1,14 | Р      |      | Ground reference for logic and I/O pins.                                                                                                                                                                          |

| N/C         | 3,5       | 3,5  |      | _      |      | Unused, do not connect.                                                                                                                                                                                           |

#### TABLE 3-2: PINOUT DESCRIPTION - PIC16C55, PIC16C57, PIC16CR57

Legend: I = input, O = output, I/O = input/output, P = power, — = Not Used, TTL = TTL input, ST = Schmitt Trigger input

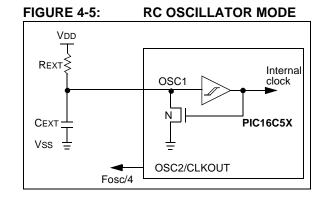

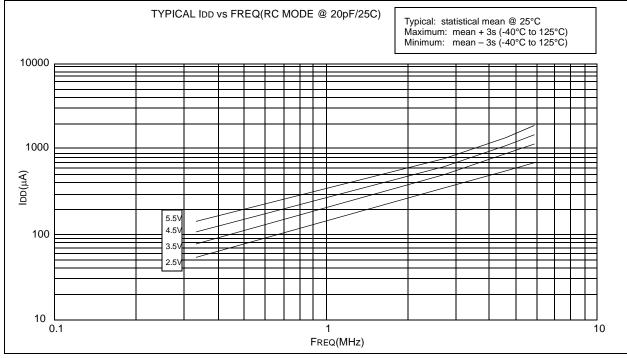

#### 4.4 RC Oscillator

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 4-5 shows how the R/C combination is connected to the PIC16C5X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ) the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

The Electrical Specifications sections show RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

Also, see the Electrical Specifications sections for variation of oscillator frequency due to VDD for given REXT/ CEXT values as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic.

**Note:** If you change from this device to another device, please verify oscillator characteristics in your application.

#### TABLE 5-3: RESET CONDITIONS FOR ALL REGISTERS

| Register                       | Address | Power-On Reset | MCLR or WDT Reset |

|--------------------------------|---------|----------------|-------------------|

| W                              | N/A     | XXXX XXXX      | uuuu uuuu         |

| TRIS                           | N/A     | 1111 1111      | 1111 1111         |

| OPTION                         | N/A     | 11 1111        | 11 1111           |

| INDF                           | 00h     | XXXX XXXX      | uuuu uuuu         |

| TMR0                           | 01h     | XXXX XXXX      | uuuu uuuu         |

| PCL                            | 02h     | 1111 1111      | 1111 1111         |

| STATUS                         | 03h     | 0001 1xxx      | 000q quuu         |

| FSR <sup>(1)</sup>             | 04h     | 1xxx xxxx      | luuu uuuu         |

| PORTA                          | 05h     | xxxx           | uuuu              |

| PORTB                          | 06h     | XXXX XXXX      | uuuu uuuu         |

| PORTC <sup>(2)</sup>           | 07h     | XXXX XXXX      | uuuu uuuu         |

| General Purpose Register Files | 07-7Fh  | XXXX XXXX      | սսսս սսսս         |

Legend: x = unknown u = unchanged - = unimplemented, read as '0'<math>q = see tables in Table 5-1 for possible values.

- Note 1: These values are valid for PIC16C57/CR57/CR58/CR58. For the PIC16C54/CR54/C55/C56/CR56, the value on RESET is 111x xxxx and for MCLR and WDT Reset, the value is 111u uuuu.

- **2:** General purpose register file on PIC16C54/CR54/C56/CR56/C58/CR58.

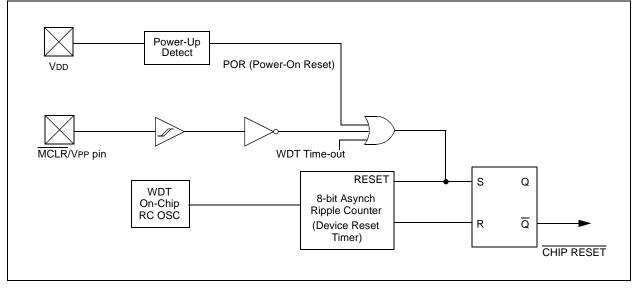

#### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 7.0 I/O PORTS

As with any other register, the I/O Registers can be written and read under program control. However, read instructions (e.g., MOVF PORTB, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers (TRISA, TRISB, TRISC) are all set.

#### 7.1 PORTA

PORTA is a 4-bit I/O Register. Only the low order 4 bits are used (RA<3:0>). Bits 7-4 are unimplemented and read as '0's.

#### 7.2 PORTB

PORTB is an 8-bit I/O Register (PORTB<7:0>).

#### 7.3 PORTC

PORTC is an 8-bit I/O Register for PIC16C55, PIC16C57 and PIC16CR57.

PORTC is a General Purpose Register for PIC16C54, PIC16CR54, PIC16CR56, PIC16CR56, PIC16CS8 and PIC16CR58.

#### 7.4 TRIS Registers

The Output Driver Control Registers are loaded with the contents of the W Register by executing the TRIS f instruction. A '1' from a TRIS Register bit puts the corresponding output driver in a hi-impedance (input) mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer.

| Note: | A read of the ports reads the pins, not the    |

|-------|------------------------------------------------|

|       | output data latches. That is, if an output     |

|       | driver on a pin is enabled and driven high,    |

|       | but the external system is holding it low, a   |

|       | read of the port will indicate that the pin is |

|       | low.                                           |

The TRIS Registers are "write-only" and are set (output drivers disabled) upon RESET.

| TABLE 7-1: | SUMMARY OF PORT REGISTERS |

|------------|---------------------------|

|            |                           |

#### Value on Value on Bit 4 Bit 3 Bit 1 Bit 0 MCLR and Address Name Bit 7 Bit 6 Bit 5 Bit 2 Power-On Reset WDT Reset TRIS N/A I/O Control Registers (TRISA, TRISB, TRISC) 1111 1111 1111 1111 05h PORTA RA3 RA2 RA1 RA0 \_ \_ \_ \_ xxxx \_ \_ \_ \_ uuuu PORTB 06h RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0 XXXX XXXX uuuu uuuu 07h PORTC RC7 RC6 RC5 RC4 RC3 RC2 RC1 RC0 XXXX XXXX uuuu uuuu

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0', Shaded cells = unimplemented, read as '0'

#### 7.5 I/O Interfacing

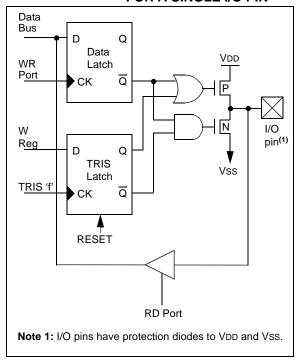

The equivalent circuit for an I/O port pin is shown in Figure 7-1. All ports may be used for both input and output operation. For input operations these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF PORTB, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit (in TRISA, TRISB, TRISC) must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin can be programmed individually as input or output.

#### FIGURE 7-1: EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

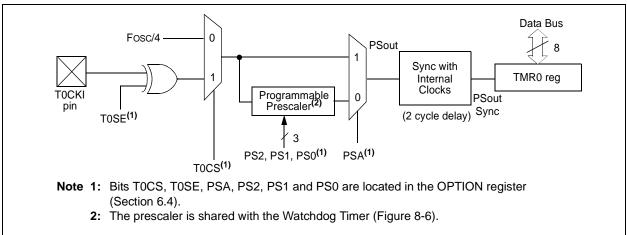

#### 8.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Edge select for external clock

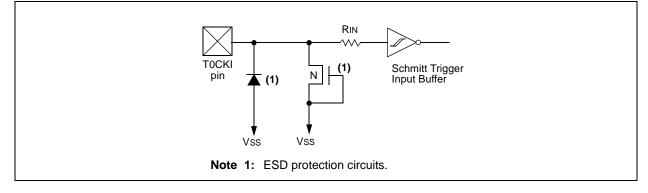

Figure 8-1 is a simplified block diagram of the Timer0 module, while Figure 8-2 shows the electrical structure of the Timer0 input.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 8-3 and Figure 8-4). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The incrementing edge is determined by the source edge select bit T0SE (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 8.1.

Note: The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both.

The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. Section 8.2 details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 8-1.

#### FIGURE 8-2: ELECTRICAL STRUCTURE OF TOCKI PIN

NOTES:

| Mnemonic, Description |         | Description                  | Cycles           | 12-Bit Opcode |      |      | Status   |       |

|-----------------------|---------|------------------------------|------------------|---------------|------|------|----------|-------|

|                       |         | Description                  |                  | MSb           |      | LSb  | Affected | Notes |

| ADDWF                 | f,d     | Add W and f                  | 1                | 0001          | 11df | ffff | C,DC,Z   | 1,2,4 |

| ANDWF                 | f,d     | AND W with f                 | 1                | 0001          | 01df | ffff | Z        | 2,4   |

| CLRF                  | f       | Clear f                      | 1                | 0000          | 011f | ffff | Z        | 4     |

| CLRW                  | -       | Clear W                      | 1                | 0000          | 0100 | 0000 | Z        |       |

| COMF                  | f, d    | Complement f                 | 1                | 0010          | 01df | ffff | Z        |       |

| DECF                  | f, d    | Decrement f                  | 1                | 0000          | 11df | ffff | Z        | 2,4   |

| DECFSZ                | f, d    | Decrement f, Skip if 0       | 1 <sup>(2)</sup> | 0010          | 11df | ffff | None     | 2,4   |

| INCF                  | f, d    | Increment f                  | 1                | 0010          | 10df | ffff | Z        | 2,4   |

| INCFSZ                | f, d    | Increment f, Skip if 0       | 1 <sup>(2)</sup> | 0011          | 11df | ffff | None     | 2,4   |

| IORWF                 | f, d    | Inclusive OR W with f        | 1                | 0001          | 00df | ffff | Z        | 2,4   |

| MOVF                  | f, d    | Move f                       | 1                | 0010          | 00df | ffff | Z        | 2,4   |

| MOVWF                 | f       | Move W to f                  | 1                | 0000          | 001f | ffff | None     | 1,4   |

| NOP                   | -       | No Operation                 | 1                | 0000          | 0000 | 0000 | None     |       |

| RLF                   | f, d    | Rotate left f through Carry  | 1                | 0011          | 01df | ffff | С        | 2,4   |

| RRF                   | f, d    | Rotate right f through Carry | 1                | 0011          | 00df | ffff | С        | 2,4   |

| SUBWF                 | f, d    | Subtract W from f            | 1                | 0000          | 10df | ffff | C,DC,Z   | 1,2,4 |

| SWAPF                 | f, d    | Swap f                       | 1                | 0011          | 10df | ffff | None     | 2,4   |

| XORWF                 | f, d    | Exclusive OR W with f        | 1                | 0001          | 10df | ffff | Z        | 2,4   |

| <b>BIT-ORIEN</b>      | TED FIL | E REGISTER OPERATIONS        | •                |               |      |      |          |       |

| BCF                   | f, b    | Bit Clear f                  | 1                | 0100          | bbbf | ffff | None     | 2,4   |

| BSF                   | f, b    | Bit Set f                    | 1                | 0101          | bbbf | ffff | None     | 2,4   |

| BTFSC                 | f, b    | Bit Test f, Skip if Clear    | 1 (2)            | 0110          | bbbf | ffff | None     |       |

| BTFSS                 | f, b    | Bit Test f, Skip if Set      | 1 (2)            | 0111          | bbbf | ffff | None     |       |

| LITERAL A             | ND CON  | ITROL OPERATIONS             | •                |               |      |      |          |       |

| ANDLW                 | k       | AND literal with W           | 1                | 1110          | kkkk | kkkk | Z        |       |

| CALL                  | k       | Call subroutine              | 2                | 1001          | kkkk | kkkk | None     | 1     |

| CLRWDT                | k       | Clear Watchdog Timer         | 1                | 0000          | 0000 | 0100 | TO, PD   |       |

| GOTO                  | k       | Unconditional branch         | 2                | 101k          | kkkk | kkkk | None     |       |

| IORLW                 | k       | Inclusive OR Literal with W  | 1                | 1101          | kkkk | kkkk | Z        |       |

| MOVLW                 | k       | Move Literal to W            | 1                | 1100          | kkkk | kkkk | None     |       |

| OPTION                | k       | Load OPTION register         | 1                | 0000          | 0000 | 0010 | None     |       |

| RETLW                 | k       | Return, place Literal in W   | 2                | 1000          | kkkk | kkkk | None     |       |

| SLEEP                 | _       | Go into standby mode         | 1                | 0000          | 0000 | 0011 | TO, PD   |       |

| TRIS                  | f       | Load TRIS register           | 1                | 0000          | 0000 | Offf | None     | 3     |

| XORLW                 | k       | Exclusive OR Literal to W    | 1                | 1111          | kkkk | kkkk | Z        |       |

#### TABLE 10-2: INSTRUCTION SET SUMMARY

**Note 1:** The 9th bit of the program counter will be forced to a '0' by any instruction that writes to the PC except for GOTO (see Section 6.5 for more on program counter).

2: When an I/O register is modified as a function of itself (e.g. MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**3:** The instruction TRIS f, where f = 5, 6 or 7 causes the contents of the W register to be written to the tristate latches of PORTA, B or C respectively. A '1' forces the pin to a hi-impedance state and disables the output buffers.

**4:** If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared (if assigned to TMR0).

| GOTO                   | Uncondi                                                                                                                                                                                     | tional B | anch |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|--|--|

| Syntax:                | [ label ]                                                                                                                                                                                   | GOTO     | k    |  |  |

| Operands:              | $0 \le k \le 5^{-1}$                                                                                                                                                                        | 11       |      |  |  |

| Operation:             | k → PC<8:0>;<br>STATUS<6:5> → PC<10:9>                                                                                                                                                      |          |      |  |  |

| Status Affected:       | None                                                                                                                                                                                        |          |      |  |  |

| Encoding:              | 101k                                                                                                                                                                                        | kkkk     | kkkk |  |  |

| Description:           | GOTO is an unconditional branch.<br>The 9-bit immediate value is<br>loaded into PC bits <8:0>. The<br>upper bits of PC are loaded from<br>STATUS<6:5>. GOTO is a two-<br>cycle instruction. |          |      |  |  |

| Words:                 | 1                                                                                                                                                                                           |          |      |  |  |

| Cycles:                | 2                                                                                                                                                                                           |          |      |  |  |

| Example:               | GOTO TH                                                                                                                                                                                     | IERE     |      |  |  |

| After Instruct<br>PC = | ion<br>address                                                                                                                                                                              | G (THER  | E)   |  |  |

| INCF                                                    | Increment f                                                                                                                                                          |  |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                                 | [label] INCF f,d                                                                                                                                                     |  |  |  |

| Operands:                                               | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                       |  |  |  |

| Operation:                                              | (f) + 1 $\rightarrow$ (dest)                                                                                                                                         |  |  |  |

| Status Affected:                                        | Z                                                                                                                                                                    |  |  |  |

| Encoding:                                               | 0010 10df ffff                                                                                                                                                       |  |  |  |

| Description:                                            | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |  |  |  |

| Words:                                                  | 1                                                                                                                                                                    |  |  |  |

| Cycles:                                                 | 1                                                                                                                                                                    |  |  |  |

| Example:                                                | INCF CNT, 1                                                                                                                                                          |  |  |  |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0xFF<br>= 0                                                                                                                                                        |  |  |  |

| INCFSZ                               | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                      |  |  |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                              | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Operands:                            | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                                  |  |  |  |

| Operation:                           | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                                            |  |  |  |

| Status Affected:                     | None                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Encoding:                            | 0011 11df ffff                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Description:                         | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'.<br>If the result is 0, then the next<br>instruction, which is already<br>fetched, is discarded and a NOP is<br>executed instead making it a two-<br>cycle instruction. |  |  |  |

| Words:                               | 1                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Cycles:                              | 1(2)                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Example:                             | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•<br>•                                                                                                                                                                                                                                                                                     |  |  |  |

| Before Instru<br>PC<br>After Instruc | = address (HERE)                                                                                                                                                                                                                                                                                                                            |  |  |  |

| CNT<br>if CNT<br>PC<br>if CNT<br>PC  | <pre>= CNT + 1;<br/>= 0,<br/>= address (CONTINUE);<br/>≠ 0,<br/>= address (HERE +1)</pre>                                                                                                                                                                                                                                                   |  |  |  |

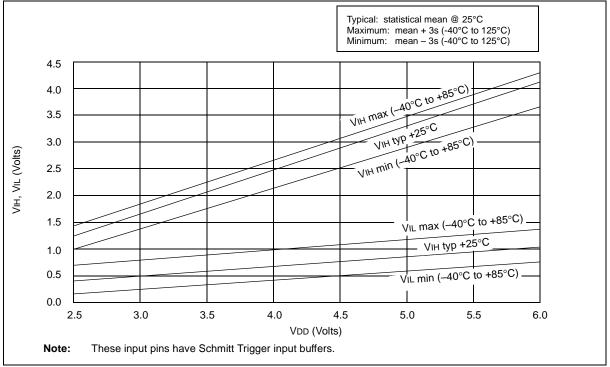

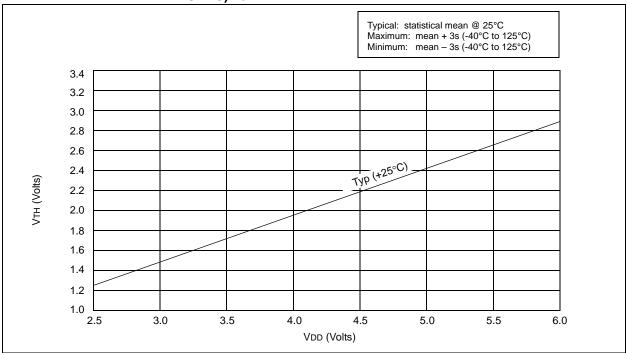

#### FIGURE 14-9: VTH (INPUT THRESHOLD VOLTAGE) OF I/O PINS vs. VDD

#### 15.2 DC Characteristics: PIC16C54A-04E, 10E, 20E (Extended) PIC16LC54A-04E (Extended)

|                                       |        | FICTULCJ                                      | -7 0-      |                                                                                                                                      | cnac         | ч)     |                                                                                         |

|---------------------------------------|--------|-----------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------|--------|-----------------------------------------------------------------------------------------|

|                                       |        |                                               |            | <b>ard Ope</b><br>ting Terr                                                                                                          |              |        | tions (unless otherwise specified) $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |

| PIC16C54A-04E, 10E, 20E<br>(Extended) |        |                                               |            | Standard Operating Conditions (unless otherwise specified)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |              |        |                                                                                         |

| Param<br>No.                          | Symbol | Characteristic                                | Min        | Тур†                                                                                                                                 | Max          | Units  | Conditions                                                                              |

|                                       | Vdd    | Supply Voltage                                |            |                                                                                                                                      | •            |        |                                                                                         |

| D001                                  |        | PIC16LC54A                                    | 3.0<br>2.5 | _                                                                                                                                    | 6.25<br>6.25 | V<br>V | XT and RC modes<br>LP mode                                                              |

| D001A                                 |        | PIC16C54A                                     | 3.5<br>4.5 |                                                                                                                                      | 5.5<br>5.5   | V<br>V | RC and XT modes<br>HS mode                                                              |

| D002                                  | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>     | —          | 1.5*                                                                                                                                 |              | V      | Device in SLEEP mode                                                                    |

| D003                                  | VPOR   | VDD Start Voltage to ensure<br>Power-on Reset | —          | Vss                                                                                                                                  | -            | V      | See Section 5.1 for details on<br>Power-on Reset                                        |

| D004                                  | Svdd   | VDD Rise Rate to ensure<br>Power-on Reset     | 0.05*      | _                                                                                                                                    | _            | V/ms   | See Section 5.1 for details on<br>Power-on Reset                                        |

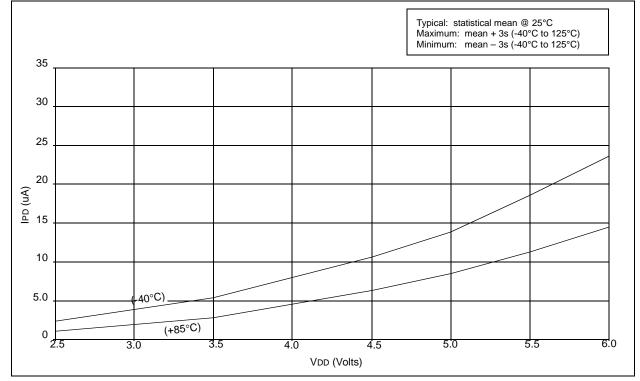

|                                       | IDD    | Supply Current <sup>(2)</sup>                 |            |                                                                                                                                      |              |        |                                                                                         |

| D010                                  |        | PIC16LC54A                                    | —          | 0.5                                                                                                                                  | 25           | mA     | Fosc = 4.0 MHz, VDD = 5.5V,<br>RC <sup>(3)</sup> and XT modes                           |

|                                       |        |                                               | —          | 11                                                                                                                                   | 27           | μA     | Fosc = 32 kHz, VDD = 2.5V,<br>LP mode, Commercial                                       |

|                                       |        |                                               | —          | 11                                                                                                                                   | 35           | μA     | Fosc = 32 kHz, VDD = 2.5V,<br>LP mode, Industrial                                       |

|                                       |        |                                               | _          | 11                                                                                                                                   | 37           | μA     | Fosc = 32 kHz, VDD = 2.5V,<br>LP mode, Extended                                         |

| D010A                                 |        | PIC16C54A                                     | —          | 1.8                                                                                                                                  | 3.3          | mA     | Fosc = 4.0 MHz, VDD = 5.5V,<br>RC <sup>(3)</sup> and XT modes                           |

|                                       |        |                                               | —          | 4.8                                                                                                                                  | 10           | mA     | Fosc = 10 MHz, VDD = 5.5V,<br>HS mode                                                   |

|                                       |        |                                               | —          | 9.0                                                                                                                                  | 20           | mA     | Fosc = 20 MHz, VDD = 5.5V,<br>HS mode                                                   |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- \* These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- **3:** Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

## PIC16C5X

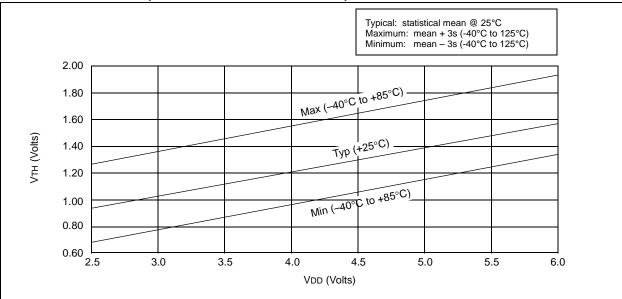

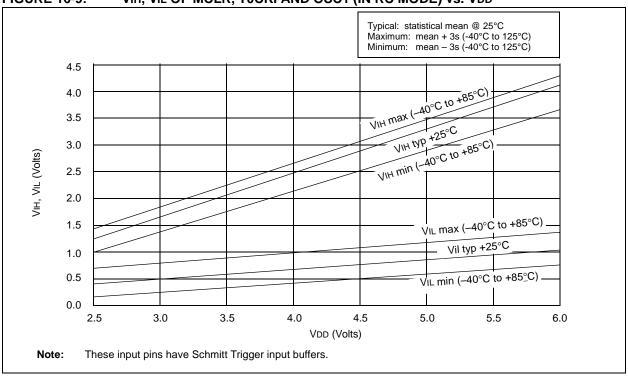

FIGURE 16-9: VIH, VIL OF MCLR, TOCKI AND OSC1 (IN RC MODE) vs. VDD

# PIC16C5X

### FIGURE 18-10: VTH (INPUT THRESHOLD TRIP POINT VOLTAGE) OF OSC1 INPUT (IN XT, HS AND LP MODES) vs. VDD

### 19.0 ELECTRICAL CHARACTERISTICS - PIC16LC54C 40MHz

#### Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                 | –55°C to +125°C               |

|----------------------------------------------------------------------------------------------------------------|-------------------------------|

| Storage temperature                                                                                            | –65°C to +150°C               |

| Voltage on VDD with respect to VSS                                                                             | 0 to +7.5V                    |

| Voltage on MCLR with respect to Vss                                                                            | 0 to +14V                     |

| Voltage on all other pins with respect to Vss                                                                  | –0.6V to (VDD + 0.6V)         |

| Total power dissipation <sup>(1)</sup>                                                                         | 800 mW                        |

| Max. current out of Vss pin                                                                                    | 150 mA                        |

| Max. current into Vod pin                                                                                      |                               |

| Max. current into an input pin (T0CKI only)                                                                    | ±500 μA                       |

| Input clamp current, liк (Vi <0 or Vi > VDD)                                                                   | ±20 mA                        |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                                 | ±20 mA                        |

| Max. output current sunk by any I/O pin                                                                        | 25 mA                         |

| Max. output current sourced by any I/O pin                                                                     | 20 mA                         |

| Max. output current sourced by a single I/O (Port A, B or C)                                                   | 50 mA                         |

| Max. output current sunk by a single I/O (Port A, B or C)                                                      | 50 mA                         |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) | x IOH} + $\Sigma$ (Vol x Iol) |

**†** NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### **19.3 Timing Parameter Symbology and Load Conditions**

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. Tp | pS                                      |                    |

|-------|-----------------------------------------|--------------------|

| Т     |                                         |                    |

| F     | Frequency                               | T Time             |

| Lowe  | ercase letters (pp) and their meanings: |                    |

| рр    |                                         |                    |

| 2     | to                                      | mc MCLR            |

| ck    | CLKOUT                                  | osc oscillator     |

| су    | cycle time                              | os OSC1            |

| drt   | device reset timer                      | t0 T0CKI           |

| io    | I/O port                                | wdt watchdog timer |

| Uppe  | ercase letters and their meanings:      |                    |

| S     |                                         |                    |

| F     | Fall                                    | P Period           |

| н     | High                                    | R Rise             |

| Ι     | Invalid (Hi-impedance)                  | V Valid            |

| L     | Low                                     | Z Hi-impedance     |

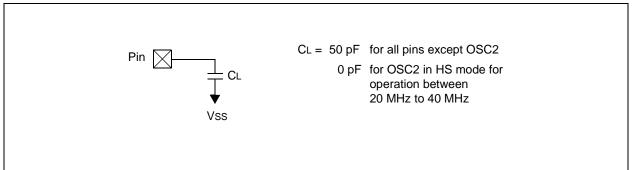

#### FIGURE 19-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS -PIC16C54C/C55A/C56A/C57C/C58B-40

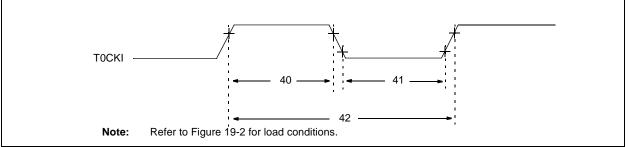

#### FIGURE 19-6: TIMER0 CLOCK TIMINGS - PIC16C5X-40

#### TABLE 19-4: TIMER0 CLOCK REQUIREMENTS PIC16C5X-40

| A            | AC Charac | toristics              | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |      |     |       |                                                                |  |  |

|--------------|-----------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|----------------------------------------------------------------|--|--|

| Param<br>No. | Symbol    | Characteristic         | Min                                                                                                                                 | Тур† | Max | Units | Conditions                                                     |  |  |

| 40           | Tt0H      | T0CKI High Pulse Width |                                                                                                                                     |      |     |       |                                                                |  |  |

|              |           | - No Prescaler         | 0.5 Tcy + 20*                                                                                                                       | —    |     | ns    |                                                                |  |  |

|              |           | - With Prescaler       | 10*                                                                                                                                 |      | —   | ns    |                                                                |  |  |

| 41           | Tt0L      | T0CKI Low Pulse Width  |                                                                                                                                     |      |     |       |                                                                |  |  |

|              |           | - No Prescaler         | 0.5 TCY + 20*                                                                                                                       | —    |     | ns    |                                                                |  |  |

|              |           | - With Prescaler       | 10*                                                                                                                                 | _    | —   | ns    |                                                                |  |  |

| 42           | Tt0P      | T0CKI Period           | 20 or <u>Tcy + 40</u> *<br>N                                                                                                        | _    | _   | ns    | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |  |  |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

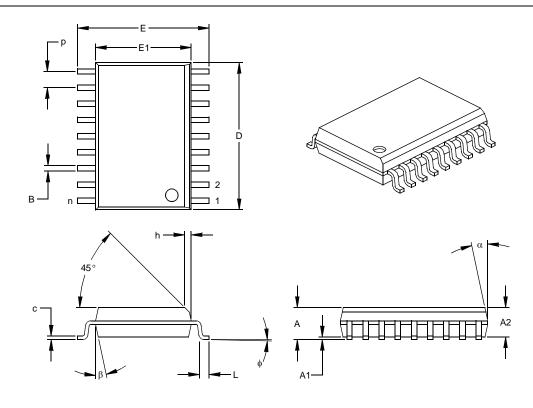

#### 18-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                          | Units     | INCHES* |      |      | MILLIMETERS |       |       |  |

|--------------------------|-----------|---------|------|------|-------------|-------|-------|--|

| Dimensi                  | on Limits | MIN     | NOM  | MAX  | MIN         | NOM   | MAX   |  |

| Number of Pins           | n         |         | 18   |      |             | 18    |       |  |

| Pitch                    | р         |         | .050 |      |             | 1.27  |       |  |

| Overall Height           | А         | .093    | .099 | .104 | 2.36        | 2.50  | 2.64  |  |

| Molded Package Thickness | A2        | .088    | .091 | .094 | 2.24        | 2.31  | 2.39  |  |

| Standoff §               | A1        | .004    | .008 | .012 | 0.10        | 0.20  | 0.30  |  |

| Overall Width            | E         | .394    | .407 | .420 | 10.01       | 10.34 | 10.67 |  |

| Molded Package Width     | E1        | .291    | .295 | .299 | 7.39        | 7.49  | 7.59  |  |

| Overall Length           | D         | .446    | .454 | .462 | 11.33       | 11.53 | 11.73 |  |

| Chamfer Distance         | h         | .010    | .020 | .029 | 0.25        | 0.50  | 0.74  |  |

| Foot Length              | L         | .016    | .033 | .050 | 0.41        | 0.84  | 1.27  |  |

| Foot Angle               | φ         | 0       | 4    | 8    | 0           | 4     | 8     |  |

| Lead Thickness           | С         | .009    | .011 | .012 | 0.23        | 0.27  | 0.30  |  |

| Lead Width               | В         | .014    | .017 | .020 | 0.36        | 0.42  | 0.51  |  |

| Mold Draft Angle Top     | α         | 0       | 12   | 15   | 0           | 12    | 15    |  |

| Mold Draft Angle Bottom  | β         | 0       | 12   | 15   | 0           | 12    | 15    |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013 Drawing No. C04-051

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 1997-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769355

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.