#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 20                                                                        |

| Program Memory Size        | 3KB (2K x 12)                                                             |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 72 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6.25V                                                                |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c57-xti-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

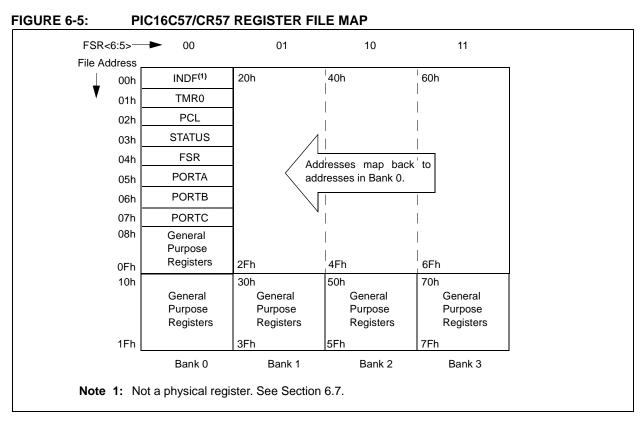

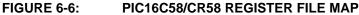

# 6.0 MEMORY ORGANIZATION

PIC16C5X memory is organized into program memory and data memory. For devices with more than 512 bytes of program memory, a paging scheme is used. Program memory pages are accessed using one or two STATUS Register bits. For devices with a data memory register file of more than 32 registers, a banking scheme is used. Data memory banks are accessed using the File Selection Register (FSR).

# 6.1 Program Memory Organization

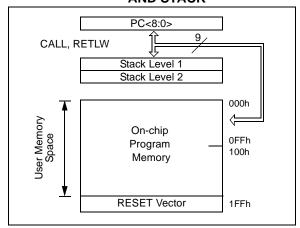

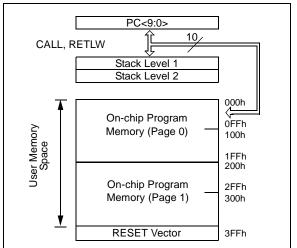

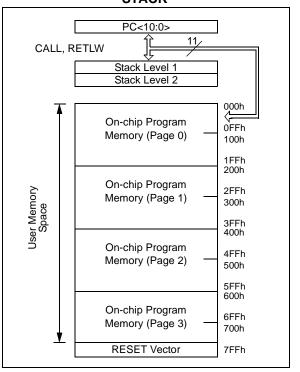

The PIC16C54, PIC16CR54 and PIC16C55 have a 9bit Program Counter (PC) capable of addressing a 512 x 12 program memory space (Figure 6-1). The PIC16C56 and PIC16CR56 have a 10-bit Program Counter (PC) capable of addressing a 1K x 12 program memory space (Figure 6-2). The PIC16CR57, PIC16C58 and PIC16CR58 have an 11-bit Program Counter capable of addressing a 2K x 12 program memory space (Figure 6-3). Accessing a location above the physically implemented address will cause a wraparound.

A NOP at the RESET vector location will cause a restart at location 000h. The RESET vector for the PIC16C54, PIC16CR54 and PIC16C55 is at 1FFh. The RESET vector for the PIC16C56 and PIC16CR56 is at 3FFh. The RESET vector for the PIC16C57, PIC16CR57, PIC16C58, and PIC16CR58 is at 7FFh. See Section 6.5 for additional information using CALL and GOTO instructions.

#### FIGURE 6-1: PIC16C54/CR54/C55 PROGRAM MEMORY MAP AND STACK

### FIGURE 6-2:

#### PIC16C56/CR56 PROGRAM MEMORY MAP AND STACK

FIGURE 6-3:

PIC16C57/CR57/C58/ CR58 PROGRAM MEMORY MAP AND STACK

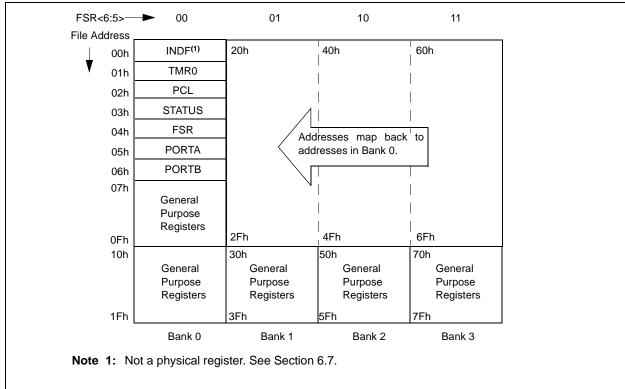

# 7.0 I/O PORTS

As with any other register, the I/O Registers can be written and read under program control. However, read instructions (e.g., MOVF PORTB, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers (TRISA, TRISB, TRISC) are all set.

# 7.1 PORTA

PORTA is a 4-bit I/O Register. Only the low order 4 bits are used (RA<3:0>). Bits 7-4 are unimplemented and read as '0's.

# 7.2 PORTB

PORTB is an 8-bit I/O Register (PORTB<7:0>).

# 7.3 PORTC

PORTC is an 8-bit I/O Register for PIC16C55, PIC16C57 and PIC16CR57.

PORTC is a General Purpose Register for PIC16C54, PIC16CR54, PIC16CR56, PIC16CR56, PIC16CS8 and PIC16CR58.

# 7.4 TRIS Registers

The Output Driver Control Registers are loaded with the contents of the W Register by executing the TRIS f instruction. A '1' from a TRIS Register bit puts the corresponding output driver in a hi-impedance (input) mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer.

| Note: | A read of the ports reads the pins, not the    |

|-------|------------------------------------------------|

|       | output data latches. That is, if an output     |

|       | driver on a pin is enabled and driven high,    |

|       | but the external system is holding it low, a   |

|       | read of the port will indicate that the pin is |

|       | low.                                           |

The TRIS Registers are "write-only" and are set (output drivers disabled) upon RESET.

| TABLE 7-1: | SUMMARY OF PORT REGISTERS |

|------------|---------------------------|

|            |                           |

#### Value on Value on Bit 4 Bit 3 Bit 1 Bit 0 MCLR and Address Name Bit 7 Bit 6 Bit 5 Bit 2 Power-On Reset WDT Reset TRIS N/A I/O Control Registers (TRISA, TRISB, TRISC) 1111 1111 1111 1111 05h PORTA RA3 RA2 RA1 RA0 \_ \_ \_ \_ xxxx \_ \_ \_ \_ uuuu PORTB 06h RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0 XXXX XXXX uuuu uuuu 07h PORTC RC7 RC6 RC5 RC4 RC3 RC2 RC1 RC0 XXXX XXXX uuuu uuuu

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0', Shaded cells = unimplemented, read as '0'

# 7.5 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 7-1. All ports may be used for both input and output operation. For input operations these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF PORTB, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit (in TRISA, TRISB, TRISC) must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin can be programmed individually as input or output.

#### FIGURE 7-1: EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

| COMF                                                 | Complement f                                                                                                                                                          |  |  |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                                              | [label] COMF f,d                                                                                                                                                      |  |  |

| Operands:                                            | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                        |  |  |

| Operation:                                           | $(\overline{f}) \rightarrow (dest)$                                                                                                                                   |  |  |

| Status Affected:                                     | Z                                                                                                                                                                     |  |  |

| Encoding:                                            | 0010 01df ffff                                                                                                                                                        |  |  |

| Description:                                         | The contents of register 'f' are<br>complemented. If 'd' is 0 the result<br>is stored in the W register. If 'd' is 1<br>the result is stored back in<br>register 'f'. |  |  |

| Words:                                               | 1                                                                                                                                                                     |  |  |

| Cycles:                                              | 1                                                                                                                                                                     |  |  |

| Example:                                             | COMF REG1,0                                                                                                                                                           |  |  |

| Before Instru<br>REG1<br>After Instruct<br>REG1<br>W | = 0x13                                                                                                                                                                |  |  |

| DECF                                                    | Decrement f                                                    |                                                                |      |            |

|---------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|------|------------|

| Syntax:                                                 | [ label ]                                                      | [label] DECF f,d                                               |      |            |

| Operands:                                               | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$ | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$ |      |            |

| Operation:                                              | $(f) - 1 \rightarrow$                                          | (dest)                                                         |      |            |

| Status Affected:                                        | Z                                                              |                                                                |      |            |

| Encoding:                                               | 0000                                                           | 11df                                                           | ffff |            |

| Description:                                            | Decreme<br>result is s<br>'d' is 1 th<br>register 'f           | stored in the result is                                        |      | jister. If |

| Words:                                                  | 1                                                              |                                                                |      |            |

| Cycles:                                                 | 1                                                              |                                                                |      |            |

| Example:                                                | DECF                                                           | CNT,                                                           | 1    |            |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0<br>= 0<br>ion                                              | <01                                                            |      |            |

| DECFSZ                                                | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                               | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                        |

| Operands:                                             | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                                |

| Operation:                                            | (f) $-1 \rightarrow d$ ; skip if result = 0                                                                                                                                                                                                                                                                                               |

| Status Affected:                                      | None                                                                                                                                                                                                                                                                                                                                      |

| Encoding:                                             | 0010 11df ffff                                                                                                                                                                                                                                                                                                                            |

| Description:                                          | The contents of register 'f' are dec-<br>remented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded and a NOP is executed<br>instead making it a two-cycle<br>instruction. |

| Words:                                                | 1                                                                                                                                                                                                                                                                                                                                         |

| Cycles:                                               | 1(2)                                                                                                                                                                                                                                                                                                                                      |

| Example:                                              | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                        |

| Before Instru<br>PC                                   | = address (HERE)                                                                                                                                                                                                                                                                                                                          |

| After Instruct<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC | tion<br>= CNT - 1;<br>= 0,<br>= address (CONTINUE);<br>≠ 0,<br>= address (HERE+1)                                                                                                                                                                                                                                                         |

| GOTO                   | Unconditional Branch                |                                                |                                                                                    |

|------------------------|-------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------|

| Syntax:                | [ label ]                           | GOTO                                           | k                                                                                  |

| Operands:              | $0 \le k \le 5^{-1}$                | 11                                             |                                                                                    |

| Operation:             | $k \rightarrow PC < STATUS$         | ,                                              | PC<10:9>                                                                           |

| Status Affected:       | None                                |                                                |                                                                                    |

| Encoding:              | 101k                                | kkkk                                           | kkkk                                                                               |

| Description:           | The 9-bit<br>loaded in<br>upper bit | immedia<br>to PC bit<br>s of PC a<br><6:5>. GC | ditional branch.<br>te value is<br>s <8:0>. The<br>re loaded from<br>pTO is a two- |

| Words:                 | 1                                   |                                                |                                                                                    |

| Cycles:                | 2                                   |                                                |                                                                                    |

| Example:               | GOTO TH                             | IERE                                           |                                                                                    |

| After Instruct<br>PC = | ion<br>address                      | G (THER                                        | E)                                                                                 |

| INCF                                                    | Increment f                                                                                                                                                          |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                                                 | [label] INCF f,d                                                                                                                                                     |  |  |

| Operands:                                               | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                                     |  |  |

| Operation:                                              | (f) + 1 $\rightarrow$ (dest)                                                                                                                                         |  |  |

| Status Affected:                                        | Z                                                                                                                                                                    |  |  |

| Encoding:                                               | 0010 10df ffff                                                                                                                                                       |  |  |

| Description:                                            | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |  |  |

| Words:                                                  | 1                                                                                                                                                                    |  |  |

| Cycles:                                                 | 1                                                                                                                                                                    |  |  |

| Example:                                                | INCF CNT, 1                                                                                                                                                          |  |  |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0xFF<br>= 0                                                                                                                                                        |  |  |

| INCFSZ                               | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                              | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                          |

| Operands:                            | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                                  |

| Operation:                           | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                                            |

| Status Affected:                     | None                                                                                                                                                                                                                                                                                                                                        |

| Encoding:                            | 0011 11df ffff                                                                                                                                                                                                                                                                                                                              |

| Description:                         | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'.<br>If the result is 0, then the next<br>instruction, which is already<br>fetched, is discarded and a NOP is<br>executed instead making it a two-<br>cycle instruction. |

| Words:                               | 1                                                                                                                                                                                                                                                                                                                                           |

| Cycles:                              | 1(2)                                                                                                                                                                                                                                                                                                                                        |

| Example:                             | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•<br>•                                                                                                                                                                                                                                                                                     |

| Before Instru<br>PC<br>After Instruc | = address (HERE)                                                                                                                                                                                                                                                                                                                            |

| CNT<br>if CNT<br>PC<br>if CNT<br>PC  | <pre>= CNT + 1;<br/>= 0,<br/>= address (CONTINUE);<br/>≠ 0,<br/>= address (HERE +1)</pre>                                                                                                                                                                                                                                                   |

| IORLW                                               | Inclusive OR literal with W                                                                                                 |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                             | [ <i>label</i> ] IORLW k                                                                                                    |

| Operands:                                           | $0 \leq k \leq 255$                                                                                                         |

| Operation:                                          | (W) .OR. (k) $\rightarrow$ (W)                                                                                              |

| Status Affected:                                    | Z                                                                                                                           |

| Encoding:                                           | 1101 kkkk kkkk                                                                                                              |

| Description:                                        | The contents of the W register are<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W regis-<br>ter. |

| Words:                                              | 1                                                                                                                           |

| Cycles:                                             | 1                                                                                                                           |

| Example:                                            | IORLW 0x35                                                                                                                  |

| Before Instru<br>W =<br>After Instruc<br>W =<br>Z = | 0x9A<br>tion                                                                                                                |

| IORWF                                                            | Inclusive OR W with f                                                                                                                                                 |  |  |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                                                          | [ <i>label</i> ] IORWF f,d                                                                                                                                            |  |  |

| Operands:                                                        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                            |  |  |

| Operation:                                                       | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                                      |  |  |

| Status Affected:                                                 | Z                                                                                                                                                                     |  |  |

| Encoding:                                                        | 0001 00df ffff                                                                                                                                                        |  |  |

| Description:                                                     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |  |  |

| Words:                                                           | 1                                                                                                                                                                     |  |  |

| Cycles:                                                          | 1                                                                                                                                                                     |  |  |

| Example:                                                         | IORWF RESULT, 0                                                                                                                                                       |  |  |

| Before Instru<br>RESUL<br>W<br>After Instruct<br>RESUL<br>W<br>Z | Γ = 0x13<br>= 0x91<br>tion                                                                                                                                            |  |  |

| MOVF                  | Move f                                                                                                                                                                                                                                                 |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:               | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                              |

| Operands:             | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                                                                                         |

| Operation:            | $(f) \rightarrow (dest)$                                                                                                                                                                                                                               |

| Status Affected:      | Z                                                                                                                                                                                                                                                      |

| Encoding:             | 0010 00df ffff                                                                                                                                                                                                                                         |

| Description:          | The contents of register 'f' is<br>moved to destination 'd'. If 'd' is 0,<br>destination is the W register. If 'd'<br>is 1, the destination is file<br>register 'f'. 'd' is 1 is useful to test a<br>file register since status flag Z is<br>affected. |

| Words:                | 1                                                                                                                                                                                                                                                      |

| Cycles:               | 1                                                                                                                                                                                                                                                      |

| Example:              | MOVF FSR, 0                                                                                                                                                                                                                                            |

| After Instruct<br>W = | tion<br>- value in FSR register                                                                                                                                                                                                                        |

| MOVLW                         | Move Lit             | teral to W | I             |        |  |

|-------------------------------|----------------------|------------|---------------|--------|--|

| Syntax:                       | [ label ]            | MOVLW      | k             |        |  |

| Operands:                     | $0 \leq k \leq 2$    | 55         |               |        |  |

| Operation:                    | $k \rightarrow (W)$  |            |               |        |  |

| Status Affected:              | None                 |            |               |        |  |

| Encoding:                     | 1100                 | kkkk       | kkkk          |        |  |

| Description:                  | The eigh<br>the W re |            | 'k' is loaded | d into |  |

| Words:                        | 1                    |            |               |        |  |

| Cycles:                       | 1                    |            |               |        |  |

| Example:                      | MOVLW                | 0x5A       |               |        |  |

| After Instruction<br>W = 0x5A |                      |            |               |        |  |

| RLF                                          | Rotate Left f through Carry                                                                                                                                                                                                   |  |  |  |  |  |  |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                      | [ <i>label</i> ] RLF f,d                                                                                                                                                                                                      |  |  |  |  |  |  |

| Operands:                                    | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                    |  |  |  |  |  |  |

| Operation:                                   | See description below                                                                                                                                                                                                         |  |  |  |  |  |  |

| Status Affected:                             | С                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Encoding:                                    | 0011 01df ffff                                                                                                                                                                                                                |  |  |  |  |  |  |

| Description:                                 | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag (STATUS<0>). If 'd'<br>is 0 the result is placed in the W<br>register. If 'd' is 1 the result is<br>stored back in<br>register 'f'. |  |  |  |  |  |  |

| Words:                                       | 1                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Cycles:                                      | 1                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Example:                                     | RLF REG1,0                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Before Instru<br>REG1<br>C<br>After Instruct | = 1110 0110<br>= 0<br>tion                                                                                                                                                                                                    |  |  |  |  |  |  |

| REG1<br>W<br>C                               | = 1110 0110<br>= 1100 1100<br>= 1                                                                                                                                                                                             |  |  |  |  |  |  |

| RRF                                          | Rotate Right f through Carry                                                                                                                                                                                                   |  |  |  |  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                      | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                       |  |  |  |  |

| Operands:                                    | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                     |  |  |  |  |

| Operation:                                   | See description below                                                                                                                                                                                                          |  |  |  |  |

| Status Affected:                             | С                                                                                                                                                                                                                              |  |  |  |  |

| Encoding:                                    | 0011 00df ffff                                                                                                                                                                                                                 |  |  |  |  |

| Description:                                 | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag (STATUS<0>). If 'd'<br>is 0 the result is placed in the W<br>register. If 'd' is 1 the result is<br>placed back in<br>register 'f'. |  |  |  |  |

| Words:                                       | 1                                                                                                                                                                                                                              |  |  |  |  |

| Cycles:                                      | 1                                                                                                                                                                                                                              |  |  |  |  |

| Example:                                     | RRF REG1,0                                                                                                                                                                                                                     |  |  |  |  |

| Before Instru<br>REG1<br>C<br>After Instruct | $= 1110 0110 \\ = 0$                                                                                                                                                                                                           |  |  |  |  |

| REG1<br>W<br>C                               | = 1110 0110<br>= 0111 0011<br>= 0                                                                                                                                                                                              |  |  |  |  |

| SLEEP            | Enter SLEEP Mode                                                                                                                                                                                                                                                             |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SLEEP                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Operation:       | 00h $\rightarrow$ WDT;<br>0 $\rightarrow$ WDT prescaler; if assigned<br>1 $\rightarrow$ TO;<br>0 $\rightarrow$ PD                                                                                                                                                            |  |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Encoding:        | 0000 0000 0011                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Description:     | Time-out status bit $(\overline{TO})$ is set. The<br>power-down status bit $(\overline{PD})$ is<br>cleared. The WDT and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See section on SLEEP for more<br>details. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                                                                        |  |  |  |  |  |

# 11.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK™ Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC<sup>™</sup> In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup>1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

# 11.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup>-based application that contains:

- An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- A project manager

- Customizable toolbar and key mapping

- A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the cost-effective simulator to a full-featured emulator with minimal retraining.

# 11.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCUs.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

# 11.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

### 12.4 DC Characteristics: PIC16C54/55/56/57-RC, XT, 10, HS, LP (Commercial) PIC16C54/55/56/57-RCI, XTI, 10I, HSI, LPI (Industrial)

|              |        |                                                                                                                                                                    | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \end{array}$ |                               |                                                        |                                         |                                                                                                                                                                                                        |

|--------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic/Device                                                                                                                                              | Min                                                                                                                                                                                                                                                              | Тур†                          | Max                                                    | Units                                   | Conditions                                                                                                                                                                                             |

| D030         | VIL    | Input Low Voltage<br>I/O ports<br>MCLR (Schmitt Trigger)<br>TOCKI (Schmitt Trigger)<br>OSC1 (Schmitt Trigger)<br>OSC1 (Schmitt Trigger)                            | Vss<br>Vss<br>Vss<br>Vss<br>Vss                                                                                                                                                                                                                                  |                               | 0.2 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.3 VDD | >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>> | Pin at hi-impedance<br>PIC16C5X-RC only <sup>(3)</sup><br>PIC16C5X-XT, 10, HS, LP                                                                                                                      |

| D040         | Vih    | Input High Voltage<br>I/O ports<br>I/O ports<br>I/O ports<br>MCLR (Schmitt Trigger)<br>TOCKI (Schmitt Trigger)<br>OSC1 (Schmitt Trigger)<br>OSC1 (Schmitt Trigger) | 0.45 VDD<br>2.0<br>0.36 VDD<br>0.85 VDD<br>0.85 VDD<br>0.85 VDD<br>0.7 VDD                                                                                                                                                                                       |                               | VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD   | > > > > > > > > > > > > > > > > > > > > | For all VDD <sup>(4)</sup><br>4.0V < VDD ≤ 5.5V <sup>(4)</sup><br>VDD > 5.5V<br>PIC16C5X-RC only <sup>(3)</sup><br>PIC16C5X-XT, 10, HS, LP                                                             |

| D050         | VHYS   | Hysteresis of Schmitt<br>Trigger inputs                                                                                                                            | 0.15 VDD*                                                                                                                                                                                                                                                        | —                             | —                                                      | V                                       |                                                                                                                                                                                                        |

| D060         | Ιι∟    | Input Leakage Current <sup>(1,2)</sup><br>I/O ports<br>MCLR<br>MCLR<br>T0CKI<br>OSC1                                                                               | -1<br>-5<br><br>-3<br>-3                                                                                                                                                                                                                                         | 0.5<br>—<br>0.5<br>0.5<br>0.5 | +1<br><br>+5<br>+3<br>+3                               | μΑ<br>μΑ<br>μΑ<br>μΑ                    | For VDD $\leq$ 5.5V:<br>VSS $\leq$ VPIN $\leq$ VDD,<br>pin at hi-impedance<br>VPIN = VSS + 0.25V<br>VPIN = VDD<br>VSS $\leq$ VPIN $\leq$ VDD<br>VSS $\leq$ VPIN $\leq$ VDD,<br>PIC16C5X-XT, 10, HS, LP |

| D080         | Vol    | Output Low Voltage<br>I/O ports<br>OSC2/CLKOUT                                                                                                                     |                                                                                                                                                                                                                                                                  | —                             | 0.6<br>0.6                                             | V<br>V                                  | IOL = 8.7 mA, VDD = 4.5V<br>IOL = 1.6 mA, VDD = 4.5V,<br>PIC16C5X-RC                                                                                                                                   |

| D090         | Vон    | Output High Voltage <sup>(2)</sup><br>I/O ports<br>OSC2/CLKOUT                                                                                                     | Vdd – 0.7<br>Vdd – 0.7                                                                                                                                                                                                                                           | _                             |                                                        | V<br>V                                  | IOH = -5.4 mA, VDD = 4.5V<br>IOH = -1.0 mA, VDD = 4.5V,<br>PIC16C5X-RC                                                                                                                                 |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

- 2: Negative current is defined as coming out of the pin.

- **3:** For PIC16C5X-RC devices, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C5X be driven with external clock in RC mode.

- 4: The user may use the better of the two specifications.

### 13.3 DC Characteristics: PIC16CR54A-04, 10, 20, PIC16LCR54A-04 (Commercial) PIC16CR54A-04I, 10I, 20I, PIC16LCR54A-04I (Industrial)

| DC CHARACTERISTICS |        |                                                                                                                                     | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \end{array} $ |                        |                                                                     |                       |                                                                                                                                                                               |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                      | Min                                                                                                                                                                                                                                                                | Тур†                   | Max                                                                 | Units                 | Conditions                                                                                                                                                                    |

| D030               | VIL    | Input Low Voltage<br>I/O ports<br>MCLR (Schmitt Trigger)<br>T0CKI (Schmitt Trigger)<br>OSC1 (Schmitt Trigger)<br>OSC1               | Vss<br>Vss<br>Vss<br>Vss<br>Vss                                                                                                                                                                                                                                    |                        | 0.2 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD | V<br>V<br>V<br>V      | Pin at hi-impedance<br>RC mode only <sup>(3)</sup><br>XT, HS and LP modes                                                                                                     |

| D040               | VIн    | Input High Voltage<br>I/O ports<br>I/O ports<br>MCLR (Schmitt Trigger)<br>T0CKI (Schmitt Trigger)<br>OSC1 (Schmitt Trigger)<br>OSC1 | 2.0<br>0.6 VDD<br>0.85 VDD<br>0.85 VDD<br>0.85 VDD<br>0.85 VDD                                                                                                                                                                                                     |                        | VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD                       | V<br>V<br>V<br>V<br>V | VDD = 3.0V to 5.5V <sup>(4)</sup><br>Full VDD range <sup>(4)</sup><br>RC mode only <sup>(3)</sup><br>XT, HS and LP modes                                                      |

| D050               | VHYS   | Hysteresis of Schmitt<br>Trigger inputs                                                                                             | 0.15 VDD*                                                                                                                                                                                                                                                          | —                      | —                                                                   | V                     |                                                                                                                                                                               |

| D060               | lι∟    | Input Leakage Current <sup>(1,2)</sup><br>I/O ports                                                                                 | -1.0                                                                                                                                                                                                                                                               | _                      | +1.0                                                                | μA                    | For VDD $\leq$ 5.5V:<br>VSS $\leq$ VPIN $\leq$ VDD,<br>pin at hi-impedance                                                                                                    |

|                    |        | MCLR<br>MCLR<br>TOCKI<br>OSC1                                                                                                       | -5.0<br><br>-3.0<br>-3.0                                                                                                                                                                                                                                           | —<br>0.5<br>0.5<br>0.5 | <br>+5.0<br>+3.0<br>+3.0                                            | μΑ<br>μΑ<br>μΑ        | $\label{eq:VPIN} \begin{array}{l} VPIN = VSS + 0.25V \\ VPIN = VDD \\ VSS \leq VPIN \leq VDD \\ VSS \leq VPIN \leq VDD, \\ XT,  HS  \text{and}  LP  \text{modes} \end{array}$ |

| D080               | Vol    | Output Low Voltage<br>I/O ports<br>OSC2/CLKOUT                                                                                      |                                                                                                                                                                                                                                                                    | _                      | 0.5<br>0.5                                                          | V<br>V                | IOL = 10  mA,  VDD = 6.0  V<br>IOL = 1.9  mA,  VDD = 6.0  V,<br>RC mode only                                                                                                  |

| D090               | Vон    | Output High Voltage <sup>(2)</sup><br>I/O ports<br>OSC2/CLKOUT                                                                      | Vdd - 0.5<br>Vdd - 0.5                                                                                                                                                                                                                                             | _                      |                                                                     | V<br>V                | IOH = -4.0  mA,  VDD = 6.0  V<br>IOH = -0.8  mA,  VDD = 6.0  V,<br>RC mode only                                                                                               |

\* These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

- 2: Negative current is defined as coming out of the pin.

- **3:** For the RC mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C5X be driven with external clock in RC mode.

- 4: The user may use the better of the two specifications.

| AC Characteristics |            | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |        |        |       |                  |

|--------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|--------|-------|------------------|

| Param<br>No.       | Symbol     | Characteristic                                                                                                                                                                                                                                 | Min  | Тур†   | Max    | Units | Conditions       |

| 1                  | Tosc       | External CLKIN Period <sup>(1)</sup>                                                                                                                                                                                                           | 250  | _      | _      | ns    | XT osc mode      |

|                    |            |                                                                                                                                                                                                                                                | 250  | —      | —      | ns    | HS osc mode (04) |

|                    |            |                                                                                                                                                                                                                                                | 100  | —      |        | ns    | HS osc mode (10) |

|                    |            |                                                                                                                                                                                                                                                | 50   | —      |        | ns    | HS osc mode (20) |

|                    |            |                                                                                                                                                                                                                                                | 5.0  | _      | —      | μS    | LP OSC mode      |

|                    |            | Oscillator Period <sup>(1)</sup>                                                                                                                                                                                                               | 250  |        | _      | ns    | RC OSC mode      |

|                    |            |                                                                                                                                                                                                                                                | 250  | —      | 10,000 | ns    | XT OSC mode      |

|                    |            |                                                                                                                                                                                                                                                | 250  | —      | 250    | ns    | HS OSC mode (04) |

|                    |            |                                                                                                                                                                                                                                                | 100  | —      | 250    | ns    | HS osc mode (10) |

|                    |            |                                                                                                                                                                                                                                                | 50   | —      | 250    | ns    | HS osc mode (20) |

|                    |            |                                                                                                                                                                                                                                                | 5.0  | _      | 200    | μS    | LP OSC mode      |

| 2                  | Тсу        | Instruction Cycle Time <sup>(2)</sup>                                                                                                                                                                                                          | —    | 4/Fosc |        | _     |                  |

| 3                  | TosL, TosH | Clock in (OSC1) Low or High                                                                                                                                                                                                                    | 50*  |        | _      | ns    | XT oscillator    |

|                    |            | Time                                                                                                                                                                                                                                           | 20*  | —      | —      | ns    | HS oscillator    |

|                    |            |                                                                                                                                                                                                                                                | 2.0* | _      | —      | μS    | LP oscillator    |

| 4                  | TosR, TosF | Clock in (OSC1) Rise or Fall                                                                                                                                                                                                                   | _    | —      | 25*    | ns    | XT oscillator    |

|                    |            | Time                                                                                                                                                                                                                                           | —    | —      | 25*    | ns    | HS oscillator    |

|                    |            |                                                                                                                                                                                                                                                | —    | —      | 50*    | ns    | LP oscillator    |

| TABLE 13-1: | EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16CR54A |

|-------------|-------------------------------------------------|

|-------------|-------------------------------------------------|

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

when an external clock input is used, the "max" cycle time limit is "Du" (no clock) for all device

2: Instruction cycle period (TcY) equals four times the input oscillator time base period.

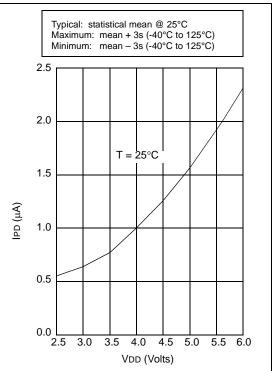

### FIGURE 14-5: TYPICAL IPD vs. VDD, WATCHDOG DISABLED

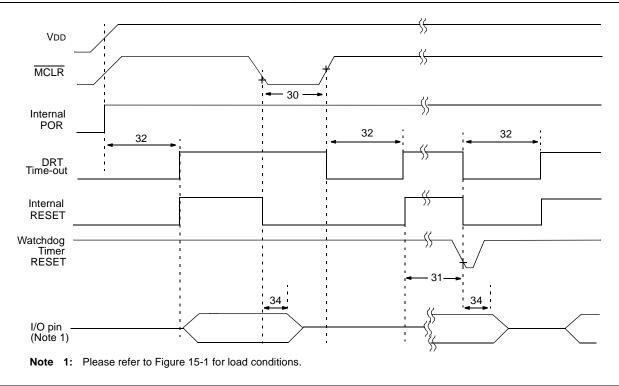

### FIGURE 15-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16C54A

### TABLE 15-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16C54A

|          | Standard Operating Conditions (unless otherwise specified) |                            |                      |                  |           |            |                              |

|----------|------------------------------------------------------------|----------------------------|----------------------|------------------|-----------|------------|------------------------------|

|          |                                                            | Operating Temperature 0    | $0^{\circ}C \leq TA$ | √≤ <b>+</b> 70°  | C for co  | mmercia    | al                           |

| AC Chara | cteristics                                                 | -40                        | $0^{\circ}C \leq TA$ | √≤ <b>+</b> 85°  | C for ind | dustrial   |                              |

|          |                                                            | -20                        | $0^{\circ}C \leq TA$ | ∖ ≤ <b>+</b> 85° | C for ind | dustrial - | - PIC16LV54A-02I             |

|          |                                                            | -40                        | $0^{\circ}C \leq TA$ | ∖ ≤ <b>+</b> 125 | °C for e  | xtended    | ł                            |

| Param    |                                                            |                            |                      |                  |           |            |                              |

| No.      | Symbol                                                     | Characteristic             | Min                  | Тур†             | Мах       | Units      | Conditions                   |

| 30       | TmcL                                                       | MCLR Pulse Width (low)     | 100*                 | _                | _         | ns         | VDD = 5.0V                   |

|          |                                                            |                            | 1                    | —                | —         | μS         | VDD = 5.0V (PIC16LV54A only) |

| 31       | Twdt                                                       | Watchdog Timer Time-out    | 9.0*                 | 18*              | 30*       | ms         | VDD = 5.0V (Comm)            |