# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 20                                                                       |

| Program Memory Size        | 3KB (2K x 12)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 72 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 28-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c57c-04-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-1: PIC16C5X FAMILY OF DEVICES

| Features                         | PIC16C54                            | PIC16CR54                           | PIC16C55                            | PIC16C56                            | PIC16CR56                           |

|----------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Maximum Operation Frequency      | 40 MHz                              | 20 MHz                              | 40 MHz                              | 40 MHz                              | 20 MHz                              |

| EPROM Program Memory (x12 words) | 512                                 | _                                   | 512                                 | 1K                                  |                                     |

| ROM Program Memory (x12 words)   |                                     | 512                                 | _                                   | _                                   | 1K                                  |

| RAM Data Memory (bytes)          | 25                                  | 25                                  | 24                                  | 25                                  | 25                                  |

| Timer Module(s)                  | TMR0                                | TMR0                                | TMR0                                | TMR0                                | TMR0                                |

| I/O Pins                         | 12                                  | 12                                  | 20                                  | 12                                  | 12                                  |

| Number of Instructions           | 33                                  | 33                                  | 33                                  | 33                                  | 33                                  |

| Packages                         | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin DIP,<br>SOIC;<br>28-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP |

PIC16C58 Features **PIC16C57** PIC16CR57 PIC16CR58 Maximum Operation Frequency 20 MHz 40 MHz 40 MHz 20 MHz EPROM Program Memory (x12 words) 2K 2K \_\_\_\_ \_ ROM Program Memory (x12 words) 2K 2K \_ \_ RAM Data Memory (bytes) 72 72 73 73 Timer Module(s) TMR0 TMR0 TMR0 TMR0 I/O Pins 20 20 12 12 Number of Instructions 33 33 33 33 28-pin DIP, SOIC; 28-pin DIP, SOIC; 18-pin DIP, SOIC; 18-pin DIP, SOIC; Packages 28-pin SSOP 28-pin SSOP 20-pin SSOP 20-pin SSOP All PIC® Family devices have Power-on Reset, selectable Watchdog Timer, selectable Code Protect and high I/O current capability.

#### 5.1 Power-On Reset (POR)

The PIC16C5X family incorporates on-chip Power-On Reset (POR) circuitry which provides an internal chip RESET for most power-up situations. To use this feature, the user merely ties the MCLR/VPP pin to VDD. A simplified block diagram of the on-chip Power-On Reset circuit is shown in Figure 5-1.

The Power-On Reset circuit and the Device Reset Timer (Section 5.2) circuit are closely related. On power-up, the RESET latch is set and the DRT is <u>RESET</u>. The DRT timer begins counting once it detects MCLR to be high. After the time-out period, which is typically 18 ms, it will RESET the reset latch and thus end the on-chip RESET signal.

A power-up example where MCLR is not tied to VDD is shown in Figure 5-3. VDD is allowed to rise and stabilize before bringing MCLR high. The chip will actually come out of reset TDRT msec after MCLR goes high.

In Figure 5-4, the on-chip Power-On Reset feature is being used (MCLR and VDD are tied together). The VDD is stable before the start-up timer times out and there is no problem in getting a proper RESET. However, Figure 5-5 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses a high on the MCLR/VPP pin, and when the MCLR/VPP pin (and VDD) actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip is, therefore, not guaranteed to function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 5-2).

Note: When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For more information on PIC16C5X POR, see *Power-Up Considerations* - AN522 in the <u>Embedded Control Handbook</u>.

The POR circuit does not produce an internal RESET when VDD declines.

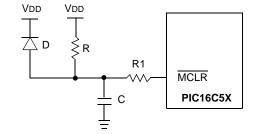

#### FIGURE 5-2:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- External Power-On Reset circuit is required only if VDD power-up is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device electrical specification.

- R1 =  $100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

#### 6.3 STATUS Register

This register contains the arithmetic status of the ALU, the RESET status and the page preselect bits for program memories larger than 512 words.

The STATUS Register can be the destination for any instruction, as with any other register. If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not

writable. Therefore, the result of an instruction with the STATUS Register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS Register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS Register because these instructions do not affect the Z, DC or C bits from the STATUS Register. For other instructions which do affect STATUS Bits, see Section 10.0, Instruction Set Summary.

#### REGISTER 6-1: STATUS REGISTER (ADDRESS: 03h)

|          | R/W-0                              | R/W-0                              | R/W-0        | R-1          | R-1                        | R/W-x         | R/W-x          | R/W-x          |

|----------|------------------------------------|------------------------------------|--------------|--------------|----------------------------|---------------|----------------|----------------|

|          | PA2                                | PA1                                | PA0          | TO           | PD                         | Z             | DC             | С              |

|          | bit 7                              |                                    |              |              |                            |               |                | bit 0          |

| bit 7:   | PA2: This bit                      | unused at th                       | is time.     |              |                            |               |                |                |

|          |                                    | A2 bit as a ge<br>with future pr   |              | e read/write | bit is not recor           | mmended, sir  | nce this may a | affect upward  |

| bit 6-5: |                                    |                                    |              | -            | CR56)(PIC16                |               |                | 58)            |

|          |                                    |                                    |              |              | 16C57/CR57,<br>16C57/CR57, |               |                |                |

|          |                                    | (400h - 5FFh                       |              |              |                            | FIC 10C30/C   | N00            |                |

|          | 11 = Page 3                        | (600h - 7FFh                       | •            |              |                            |               |                |                |

|          | Each page is                       |                                    | deperal pur  | ose read/wr  | ite bits in devi           | ices which do | not use them   | for program    |

|          |                                    |                                    |              |              | affect upward              |               |                |                |

| bit 4:   | TO: Time-ou                        |                                    |              | ,            | •                          |               |                |                |

|          |                                    | ver-up, CLRWI<br>ime-out occur     |              | , or sleep i | nstruction                 |               |                |                |

| bit 3:   | PD: Power-d                        | lown bit                           |              |              |                            |               |                |                |

|          | •                                  | ver-up or by tl<br>ution of the SI |              |              |                            |               |                |                |

| bit 2:   | Z: Zero bit                        |                                    |              |              |                            |               |                |                |

|          |                                    | lt of an arithm<br>It of an arithm |              |              |                            |               |                |                |

| bit 1:   | DC: Digit car                      | ry/borrow bit                      | (for ADDWF a | nd SUBWF in  | structions)                |               |                |                |

|          | ADDWF                              |                                    |              |              |                            |               |                |                |

|          |                                    | rom the 4th la<br>rom the 4th la   |              |              |                            |               |                |                |

|          | SUBWF                              |                                    |              |              |                            |               |                |                |

|          |                                    |                                    |              |              | did not occur              |               |                |                |

|          |                                    | from the 4th                       |              |              |                            |               |                |                |

| bit 0:   | •                                  | row bit (for AI                    |              |              | F instructions             |               | _              |                |

|          | <b>ADDWF</b><br>1 = A carry o      | ocurred                            |              | orrow did n  | ot occur                   | RRF or RLI    |                | , respectively |

|          | $\pm = \pi \operatorname{carry} 0$ | locurrou                           | / · ·        |              |                            |               |                |                |

| Legena:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared        | x = bit is unknown |

# 7.0 I/O PORTS

As with any other register, the I/O Registers can be written and read under program control. However, read instructions (e.g., MOVF PORTB, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers (TRISA, TRISB, TRISC) are all set.

#### 7.1 PORTA

PORTA is a 4-bit I/O Register. Only the low order 4 bits are used (RA<3:0>). Bits 7-4 are unimplemented and read as '0's.

# 7.2 PORTB

PORTB is an 8-bit I/O Register (PORTB<7:0>).

### 7.3 PORTC

PORTC is an 8-bit I/O Register for PIC16C55, PIC16C57 and PIC16CR57.

PORTC is a General Purpose Register for PIC16C54, PIC16CR54, PIC16CR56, PIC16CR56, PIC16CS8 and PIC16CR58.

### 7.4 TRIS Registers

The Output Driver Control Registers are loaded with the contents of the W Register by executing the TRIS f instruction. A '1' from a TRIS Register bit puts the corresponding output driver in a hi-impedance (input) mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer.

| Note: | A read of the ports reads the pins, not the    |

|-------|------------------------------------------------|

|       | output data latches. That is, if an output     |

|       | driver on a pin is enabled and driven high,    |

|       | but the external system is holding it low, a   |

|       | read of the port will indicate that the pin is |

|       | low.                                           |

The TRIS Registers are "write-only" and are set (output drivers disabled) upon RESET.

| TABLE 7-1: | SUMMARY OF PORT REGISTERS |

|------------|---------------------------|

|            |                           |

#### Value on Value on Bit 4 Bit 3 Bit 1 Bit 0 MCLR and Address Name Bit 7 Bit 6 Bit 5 Bit 2 Power-On Reset WDT Reset TRIS N/A I/O Control Registers (TRISA, TRISB, TRISC) 1111 1111 1111 1111 05h PORTA RA3 RA2 RA1 RA0 \_ \_ \_ \_ xxxx \_ \_ \_ \_ uuuu PORTB 06h RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0 XXXX XXXX uuuu uuuu 07h PORTC RC7 RC6 RC5 RC4 RC3 RC2 RC1 RC0 XXXX XXXX uuuu uuuu

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0', Shaded cells = unimplemented, read as '0'

#### 7.5 I/O Interfacing

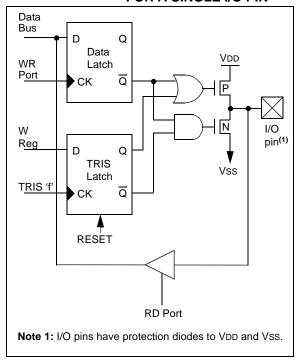

The equivalent circuit for an I/O port pin is shown in Figure 7-1. All ports may be used for both input and output operation. For input operations these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF PORTB, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit (in TRISA, TRISB, TRISC) must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin can be programmed individually as input or output.

#### FIGURE 7-1: EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

#### 7.6 I/O Programming Considerations

#### 7.6.1 BI-DIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU, bit5 to be set and the PORTB value to be written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (say bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit0 is switched into Output mode later on, the content of the data latch may now be unknown.

Example 7-1 shows the effect of two sequential read-modify-write instructions (e.g., BCF, BSF, etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### EXAMPLE 7-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT Settings

; PORTB<7:4> Inputs

; PORTB<3:0> Outputs

;PORTB<7:6> have external pull-ups and are

;not connected to other circuitry

;

| ; |       |        |   | PORT  | latch | PORT | pins |

|---|-------|--------|---|-------|-------|------|------|

| ; |       |        |   |       |       |      |      |

|   | BCF   | PORTB, | 7 | ;01pp | pppp  | 11pp | pppp |

|   | BCF   | PORTB, | 6 | ;10pp | pppp  | 11pp | pppp |

|   | MOVLW | H'3F'  |   | ;     |       |      |      |

|   | TRIS  | PORTB  |   | ;10pp | pppp  | 10pp | pppp |

| ; |       |        |   |       |       |      |      |

;Note that the user may have expected the pin ;values to be 00pp pppp. The 2nd BCF caused ;RB7 to be latched as the pin value (High).

#### 7.6.2 SUCCESSIVE OPERATIONS ON I/O PORTS

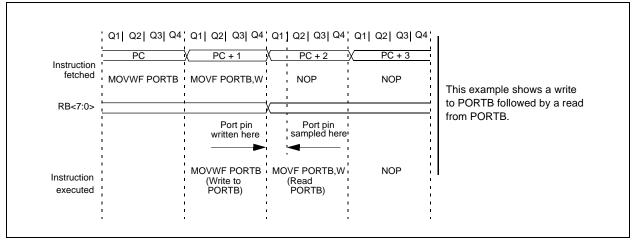

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 7-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### FIGURE 7-2: SUCCESSIVE I/O OPERATION

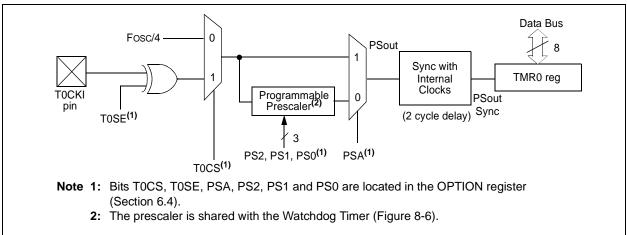

#### 8.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Edge select for external clock

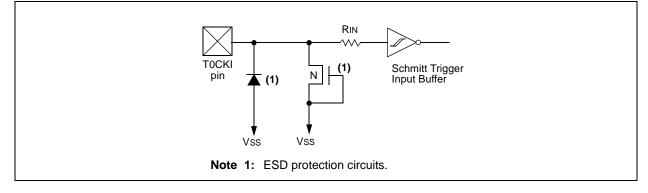

Figure 8-1 is a simplified block diagram of the Timer0 module, while Figure 8-2 shows the electrical structure of the Timer0 input.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 8-3 and Figure 8-4). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The incrementing edge is determined by the source edge select bit T0SE (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 8.1.

Note: The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both.

The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. Section 8.2 details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 8-1.

#### FIGURE 8-2: ELECTRICAL STRUCTURE OF TOCKI PIN

#### CONFIGURATION WORD FOR PIC16C54/C55/C56/C57 **REGISTER 9-2:**

|           |            |             |              |            |                     |             | İ         | СР      | WDTE        | FOSC1      | FOSC0   |

|-----------|------------|-------------|--------------|------------|---------------------|-------------|-----------|---------|-------------|------------|---------|

|           |            | _           | _            | _          |                     |             |           | CP      | WDIE        | FUSCI      |         |

| bit 11    |            |             |              |            |                     |             |           |         |             |            | bit 0   |

|           |            |             |              |            |                     |             |           |         |             |            |         |

| bit 11-4: | Unimple    | mented      | Read as '    | 0'         |                     |             |           |         |             |            |         |

| bit 3:    | CP: Cod    | e protecti  | on bit.      |            |                     |             |           |         |             |            |         |

|           |            | e protecti  |              |            |                     |             |           |         |             |            |         |

|           | 0 = Code   | e protectio | on on        |            |                     |             |           |         |             |            |         |

| bit 2:    | WDTE: \    | Vatchdog    | timer ena    | ble bit    |                     |             |           |         |             |            |         |

|           | 1 = WDT    | enabled     |              |            |                     |             |           |         |             |            |         |

|           | 0 = WDT    | disabled    |              |            |                     |             |           |         |             |            |         |

| bit 1-0:  | FOSC1:I    | FOSC0: (    | Oscillator s | election b | oits <sup>(2)</sup> |             |           |         |             |            |         |

|           | 00 = LF    | oscillato   | or           |            |                     |             |           |         |             |            |         |

|           | 01 = X     | T oscillato | or           |            |                     |             |           |         |             |            |         |

|           |            | S oscillato |              |            |                     |             |           |         |             |            |         |

|           | 11 = R     | C oscillate | or           |            |                     |             |           |         |             |            |         |

| Note 1.   | Refer to t | ha PIC16    | C5X Prog     | rammina    | Specificat          | ions (Liter | atura Num | her DS3 | 190) to d   | otormino l | now to  |

|           |            |             | iration wor  | 0          | opeemear            |             |           |         | , 100) to u |            | 1011 10 |

| 2:        |            | •           | orts XT, R   |            | oscillator          | onlv.       |           |         |             |            |         |

|           |            |             |              |            |                     | - 1         |           |         |             |            |         |

| Legend:   |            |             |              |            |                     |             |           |         |             |            |         |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared        | x = bit is unknown |

| MOVWF               | Move W to f                      |  |  |  |  |  |

|---------------------|----------------------------------|--|--|--|--|--|

| Syntax:             | [ <i>label</i> ] MOVWF f         |  |  |  |  |  |

| Operands:           | $0 \leq f \leq 31$               |  |  |  |  |  |

| Operation:          | $(W) \rightarrow (f)$            |  |  |  |  |  |

| Status Affected:    | None                             |  |  |  |  |  |

| Encoding:           | 0000 001f ffff                   |  |  |  |  |  |

| Description:        | Move data from the W register to |  |  |  |  |  |

|                     | register 'f'.                    |  |  |  |  |  |

| Words:              | 1                                |  |  |  |  |  |

| Cycles:             | 1                                |  |  |  |  |  |

| Example:            | MOVWF TEMP_REG                   |  |  |  |  |  |

| W<br>After Instruct | REG = 0xFF $= 0x4F$              |  |  |  |  |  |

| NOP              | No Operation |        |      |  |  |

|------------------|--------------|--------|------|--|--|

| Syntax:          | [ label ]    | NOP    |      |  |  |

| Operands:        | None         |        |      |  |  |

| Operation:       | No opera     | ation  |      |  |  |

| Status Affected: | None         |        |      |  |  |

| Encoding:        | 0000         | 0000   | 0000 |  |  |

| Description:     | No opera     | ation. |      |  |  |

| Words:           | 1            |        |      |  |  |

| Cycles:          | 1            |        |      |  |  |

| Example:         | NOP          |        |      |  |  |

| OPTION           | Load Ol             |             | egister |  |

|------------------|---------------------|-------------|---------|--|

| Syntax:          | [ label ]           | OPTIO       | N       |  |

| Operands:        | None                |             |         |  |

| Operation:       | $(W) \rightarrow C$ | PTION       |         |  |

| Status Affected: | None                |             |         |  |

| Encoding:        | 0000                | 0000        | 0010    |  |

| Description:     |                     | tent of the | 0       |  |

| Words:           | 1                   |             |         |  |

| Cycles:          | 1                   |             |         |  |

| Example          | OPTION              |             |         |  |

| Before Instru    | ction               |             |         |  |

| W                | •                   | 07          |         |  |

| After Instructi  | -                   |             |         |  |

| OPTION           | = 0x                | 07          |         |  |

| RETLW               | Return with Literal in W                                                                                                                                                            |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:             | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:           | $0 \leq k \leq 255$                                                                                                                                                                 |

| Operation:          | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |

| Status Affected:    | None                                                                                                                                                                                |

| Encoding:           | 1000 kkkk kkkk                                                                                                                                                                      |

| Description:        | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address). This<br>is a two-cycle instruction. |

| Words:              | 1                                                                                                                                                                                   |

| Cycles:             | 2                                                                                                                                                                                   |

| Example:            | CALL TABLE ;W contains<br>;table offset<br>;value.<br>• ;W now has table<br>• ;value.                                                                                               |

| TABLE               | <pre>ADDWF PC ;W = offset RETLW k1 ;Begin table RETLW k2 ;</pre>                                                                                                                    |

| Before Instru       |                                                                                                                                                                                     |

| W<br>After Instruct | = 0x07                                                                                                                                                                              |

| After Instruct<br>W | = value of k8                                                                                                                                                                       |

#### 13.4 DC Characteristics: PIC16CR54A-04E, 10E, 20E (Extended)

| DC CHARACTERISTICS |        | Standard Operating Conditions (unless otherwise specified)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |           |      |          |       |                                               |

|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|-----------|------|----------|-------|-----------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                       | Min       | Тур† | Мах      | Units | Conditions                                    |

| D030               | VIL    | Input Low Voltage                                                                                                                    |           |      |          |       |                                               |

|                    |        | I/O ports                                                                                                                            | Vss       | _    | 0.15 Vdd | V     | Pin at hi-impedance                           |

|                    |        | MCLR (Schmitt Trigger)                                                                                                               | Vss       | —    | 0.15 Vdd | V     |                                               |

|                    |        | T0CKI (Schmitt Trigger)                                                                                                              | Vss       | —    | 0.15 VDD | V     |                                               |

|                    |        | OSC1 (Schmitt Trigger)                                                                                                               | Vss       |      | 0.15 VDD | V     | RC mode only <sup>(3)</sup>                   |

|                    |        | OSC1                                                                                                                                 | Vss       |      | 0.3 Vdd  | V     | XT, HS and LP modes                           |

| D040               | Vін    | Input High Voltage                                                                                                                   |           |      |          |       |                                               |

|                    |        | I/O ports                                                                                                                            | 0.45 Vdd  | —    | Vdd      | V     | For all VDD <sup>(4)</sup>                    |

|                    |        | I/O ports                                                                                                                            | 2.0       | —    | Vdd      | V     | $4.0V < VDD \le 5.5V^{(4)}$                   |

|                    |        | I/O ports                                                                                                                            | 0.36 VDD  | —    | Vdd      | V     | VDD > 5.5V                                    |

|                    |        | MCLR (Schmitt Trigger)                                                                                                               | 0.85 VDD  | —    | Vdd      | V     |                                               |

|                    |        | T0CKI (Schmitt Trigger)                                                                                                              | 0.85 VDD  | —    | Vdd      | V     |                                               |

|                    |        | OSC1 (Schmitt Trigger)                                                                                                               | 0.85 VDD  | —    | Vdd      | V     | RC mode only <sup>(3)</sup>                   |

|                    |        | OSC1                                                                                                                                 | 0.7 Vdd   |      | Vdd      | V     | XT, HS and LP modes                           |

| D050               | VHYS   | Hysteresis of Schmitt<br>Trigger inputs                                                                                              | 0.15 Vdd* | —    |          | V     |                                               |

| D060               | lı∟    | Input Leakage Current <sup>(1,2)</sup>                                                                                               |           |      |          |       | <b>For V</b> DD ≤ <b>5.5V</b> :               |

|                    |        | I/O ports                                                                                                                            | -1.0      | 0.5  | +1.0     | μA    | $VSS \leq VPIN \leq VDD$ ,                    |

|                    |        |                                                                                                                                      |           |      |          |       | pin at hi-impedance                           |

|                    |        | MCLR                                                                                                                                 | -5.0      |      | _        | μA    | VPIN = VSS + 0.25V                            |

|                    |        | MCLR                                                                                                                                 |           | 0.5  | +5.0     | μΑ    | VPIN = VDD                                    |

|                    |        | TOCKI                                                                                                                                | -3.0      | 0.5  | +3.0     | μΑ    | $VSS \leq VPIN \leq VDD$                      |

|                    |        | OSC1                                                                                                                                 | -3.0      | 0.5  | +3.0     | μA    | $VSS \leq VPIN \leq VDD$ ,                    |

|                    |        |                                                                                                                                      |           |      |          | •     | XT, HS and LP modes                           |

| D080               | Vol    | Output Low Voltage                                                                                                                   |           |      |          |       |                                               |

|                    |        | I/O ports                                                                                                                            | _         | _    | 0.6      | V     | IOL = 8.7 mA, VDD = 4.5V                      |

|                    |        | OSC2/CLKOUT                                                                                                                          | _         | _    | 0.6      | V     | IOL = 1.6  mA,  VDD = 4.5 V,                  |

|                    |        |                                                                                                                                      |           |      |          |       | RC mode only                                  |

| D090               | Vон    | Output High Voltage <sup>(2)</sup>                                                                                                   |           |      |          |       |                                               |

|                    |        | I/O ports                                                                                                                            | Vdd - 0.7 | —    | —        | V     | IOH = −5.4 mA, VDD = 4.5\                     |

|                    |        | OSC2/CLKOUT                                                                                                                          | Vdd - 0.7 | —    | —        | V     | IOH = -1.0  mA,  VDD = 4.5  V<br>RC mode only |

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

**2:** Negative current is defined as coming out of the pin.

3: For the RC mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C5X be driven with external clock in RC mode.

4: The user may use the better of the two specifications.

#### **13.6** Timing Diagrams and Specifications

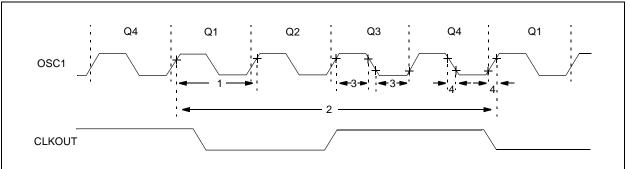

#### FIGURE 13-2: EXTERNAL CLOCK TIMING - PIC16CR54A

#### TABLE 13-1: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16CR54A

| AC Chara     | cteristics | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |      |     |       |                  |

|--------------|------------|------------------------------------------------------|-----|------|-----|-------|------------------|

| Param<br>No. | Symbol     | Characteristic                                       | Min | Тур† | Max | Units | Conditions       |

|              | Fosc       | External CLKIN Frequency <sup>(1)</sup>              | DC  | _    | 4.0 | MHz   | XT osc mode      |

|              |            |                                                      | DC  | —    | 4.0 | MHz   | HS osc mode (04) |

|              |            |                                                      | DC  | _    | 10  | MHz   | HS osc mode (10) |

|              |            |                                                      | DC  | —    | 20  | MHz   | HS osc mode (20) |

|              |            |                                                      | DC  | _    | 200 | kHz   | LP osc mode      |

|              |            | Oscillator Frequency <sup>(1)</sup>                  | DC  |      | 4.0 | MHz   | RC OSC mode      |

|              |            |                                                      | 0.1 | _    | 4.0 | MHz   | XT osc mode      |

|              |            |                                                      | 4.0 | _    | 4.0 | MHz   | HS osc mode (04) |

|              |            |                                                      | 4.0 | _    | 10  | MHz   | HS osc mode (10) |

|              |            |                                                      | 4.0 | _    | 20  | MHz   | HS osc mode (20) |

|              |            |                                                      | 5.0 | —    | 200 | kHz   | LP osc mode      |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

**2:** Instruction cycle period (TCY) equals four times the input oscillator time base period.

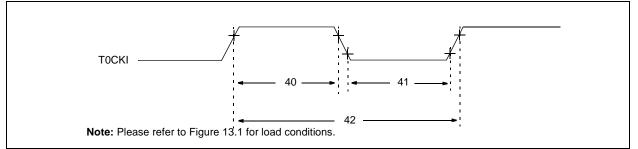

#### FIGURE 13-5: TIMER0 CLOCK TIMINGS - PIC16CR54A

#### TABLE 13-4: TIMER0 CLOCK REQUIREMENTS - PIC16CR54A

|              | AC Chara | acteristics | $\begin{array}{l} \mbox{Conditions (unless otherwise specified)} \\ \mbox{ture} & 0^\circ C \leq TA \leq +70^\circ C \mbox{ for commercial} \\ -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array}$ |                              |      |     |          |                                                                |

|--------------|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|-----|----------|----------------------------------------------------------------|

| Param<br>No. | Symbol   |             | Characteristic                                                                                                                                                                                                                                                                        | Min                          | Тур† | Max | Units    | Conditions                                                     |

| 40           | Tt0H     | T0CKI High  | Pulse Width<br>- No Prescaler<br>- With Prescaler                                                                                                                                                                                                                                     | 0.5 Tcy + 20*<br>10*         |      | _   | ns<br>ns | -                                                              |

| 41           | TtOL     | T0CKI Low   | Pulse Width<br>- No Prescaler<br>- With Prescaler                                                                                                                                                                                                                                     | 0.5 Tcy + 20*<br>10*         |      |     | ns<br>ns | -                                                              |

| 42           | Tt0P     | T0CKI Perio | od                                                                                                                                                                                                                                                                                    | 20 or <u>Tcy + 40</u> *<br>N |      | —   | ns       | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

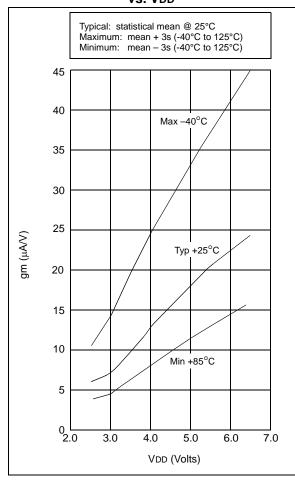

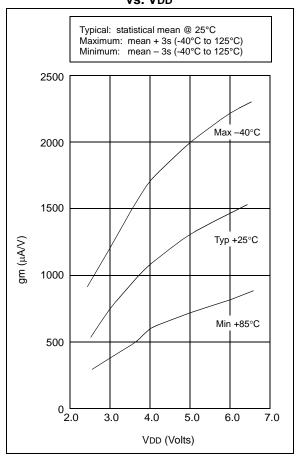

#### FIGURE 14-18:

#### TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

| TABLE 15-1: | EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16C54A |

|-------------|------------------------------------------------|

|-------------|------------------------------------------------|

| $ \begin{array}{c} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -20^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} -20^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \\ \end{array} $ |            |                                       |      |        |        |       |                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------|------|--------|--------|-------|--------------------------|

| Param<br>No.                                                                                                                                                                                                                                                                                                                                                                                       | Symbol     | Characteristic                        | Min  | Тур†   | Max    | Units | Conditions               |

| 1                                                                                                                                                                                                                                                                                                                                                                                                  | Tosc       | External CLKIN Period <sup>(1)</sup>  | 250  |        |        | ns    | XT OSC mode              |

|                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                       | 500  | —      |        | ns    | XT osc mode (PIC16LV54A) |

|                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                       | 250  | —      |        | ns    | HS osc mode (04)         |

|                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                       | 100  | —      |        | ns    | HS osc mode (10)         |

|                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                       | 50   | —      |        | ns    | HS osc mode (20)         |

|                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                       | 5.0  | _      |        | μs    | LP OSC mode              |

|                                                                                                                                                                                                                                                                                                                                                                                                    |            | Oscillator Period <sup>(1)</sup>      | 250  | _      |        | ns    | RC osc mode              |

|                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                       | 500  | —      |        | ns    | RC osc mode (PIC16LV54A) |

|                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                       | 250  | —      | 10,000 | ns    | XT OSC mode              |

|                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                       | 500  | —      |        | ns    | XT osc mode (PIC16LV54A) |

|                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                       | 250  | —      | 250    | ns    | HS osc mode (04)         |

|                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                       | 100  | —      | 250    | ns    | HS osc mode (10)         |

|                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                       | 50   | —      | 250    | ns    | HS osc mode (20)         |

|                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                       | 5.0  | _      | 200    | μs    | LP OSC mode              |

| 2                                                                                                                                                                                                                                                                                                                                                                                                  | Тсу        | Instruction Cycle Time <sup>(2)</sup> |      | 4/Fosc | —      | —     |                          |

| 3                                                                                                                                                                                                                                                                                                                                                                                                  | TosL, TosH | Clock in (OSC1) Low or                | 85*  | _      | -      | ns    | XT oscillator            |

|                                                                                                                                                                                                                                                                                                                                                                                                    |            | High Time                             | 20*  | —      | —      | ns    | HS oscillator            |

|                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                       | 2.0* | —      | —      | μS    | LP oscillator            |

| 4                                                                                                                                                                                                                                                                                                                                                                                                  | TosR, TosF | Clock in (OSC1) Rise or               | _    | —      | 25*    | ns    | XT oscillator            |

|                                                                                                                                                                                                                                                                                                                                                                                                    |            | Fall Time                             | —    | —      | 25*    | ns    | HS oscillator            |

|                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                       | _    | _      | 50*    | ns    | LP oscillator            |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

**2:** Instruction cycle period (TCY) equals four times the input oscillator time base period.

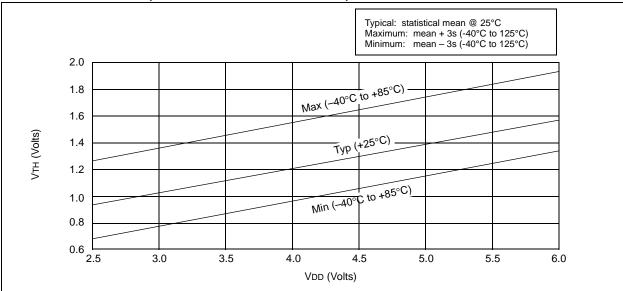

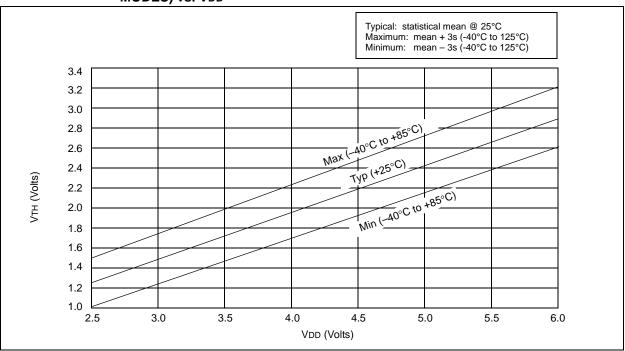

FIGURE 16-7: VTH (INPUT THRESHOLD VOLTAGE) OF I/O PINS - VDD

# PIC16C5X

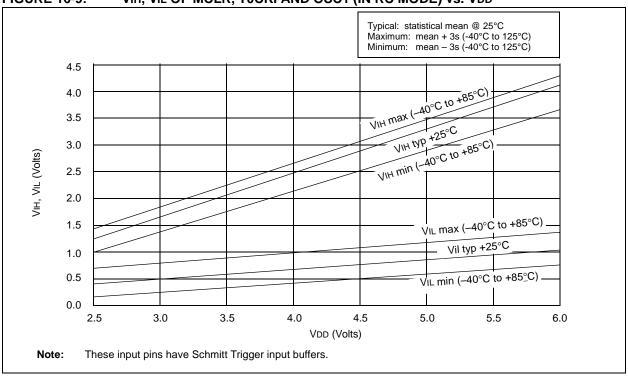

FIGURE 16-9: VIH, VIL OF MCLR, TOCKI AND OSC1 (IN RC MODE) vs. VDD

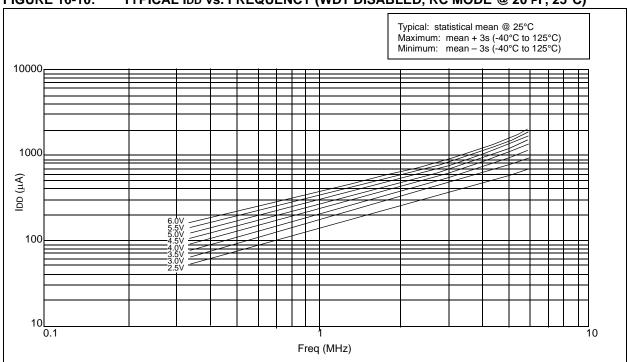

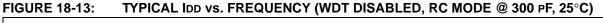

FIGURE 16-10: TYPICAL IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 20 PF, 25°C)

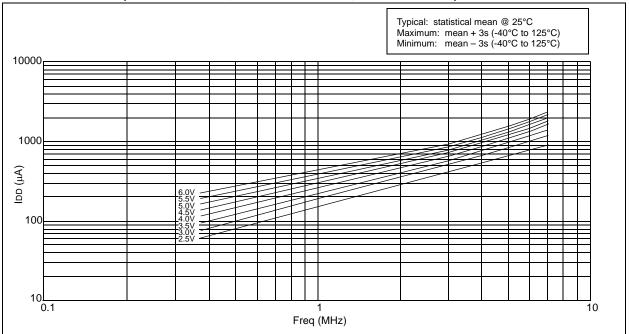

FIGURE 16-11: MAXIMUM IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 20 PF, -40°C to +85°C)

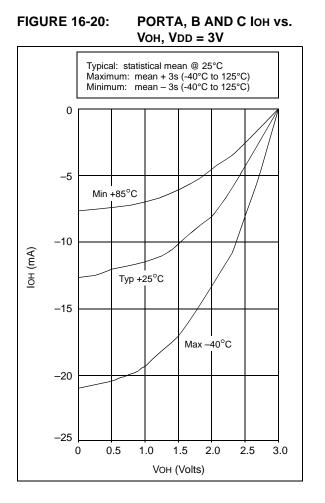

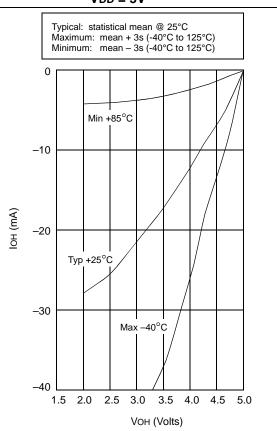

FIGURE 16-21: PORTA, B AND C IOH vs. VOH, VDD = 5V

TABLE 16-2:INPUT CAPACITANCE FOR<br/>PIC16C54A/C58A

| Pin         | Typical Capacitance (pF) |          |  |  |  |

|-------------|--------------------------|----------|--|--|--|

| FIII        | 18L PDIP                 | 18L SOIC |  |  |  |

| RA port     | 5.0                      | 4.3      |  |  |  |

| RB port     | 5.0                      | 4.3      |  |  |  |

| MCLR        | 17.0                     | 17.0     |  |  |  |

| OSC1        | 4.0                      | 3.5      |  |  |  |

| OSC2/CLKOUT | 4.3                      | 3.5      |  |  |  |

| TOCKI       | 3.2                      | 2.8      |  |  |  |

All capacitance values are typical at 25°C. A part-to-part variation of  $\pm 25\%$  (three standard deviations) should be taken into account.

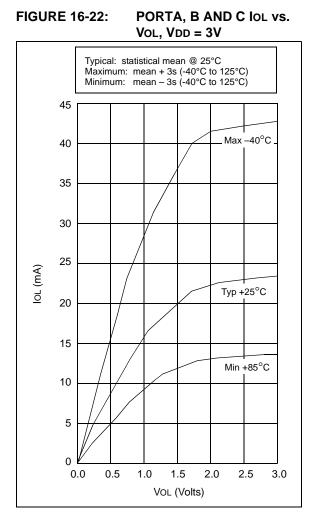

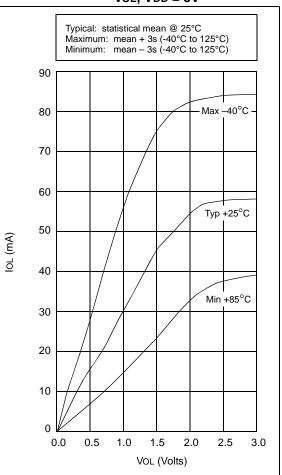

#### FIGURE 16-23: PORTA, B AND C IOL vs. VOL, VDD = 5V

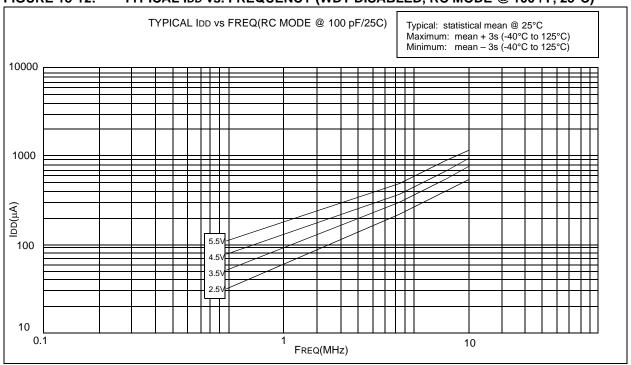

#### FIGURE 18-12: TYPICAL IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 100 PF, 25°C)

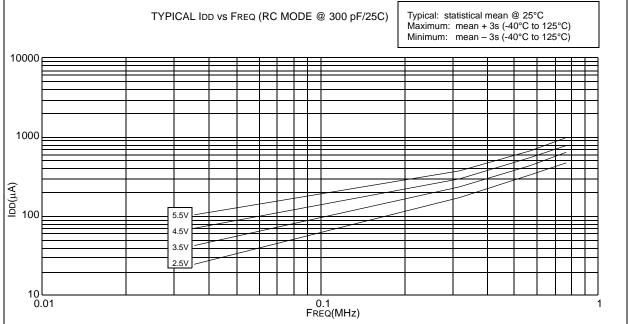

| TABLE 19-2: | CLKOUT AND I/O TIMING REQUIREMENTS - PIC16C5X-40 |

|-------------|--------------------------------------------------|

|             |                                                  |

| AC Characteristics Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |          |                                                                          |              |      |      |       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------|--------------|------|------|-------|

| Param<br>No.                                                                                                                                               | Symbol   | Characteristic                                                           | Min          | Тур† | Max  | Units |

| 10                                                                                                                                                         | TosH2ckL | OSC1↑ to CLKOUT↓ <sup>(1,2)</sup>                                        | —            | 15   | 30** | ns    |

| 11                                                                                                                                                         | TosH2ckH | OSC1↑ to CLKOUT↑ <sup>(1,2)</sup>                                        | —            | 15   | 30** | ns    |

| 12                                                                                                                                                         | TckR     | CLKOUT rise time <sup>(1,2)</sup>                                        | —            | 5.0  | 15** | ns    |

| 13                                                                                                                                                         | TckF     | CLKOUT fall time <sup>(1,2)</sup>                                        | —            | 5.0  | 15** | ns    |

| 14                                                                                                                                                         | TckL2ioV | CLKOUT↓ to Port out valid <sup>(1,2)</sup>                               | —            | —    | 40** | ns    |

| 15                                                                                                                                                         | TioV2ckH | Port in valid before CLKOUT <sup>(1,2)</sup>                             | 0.25 TCY+30* | —    | _    | ns    |

| 16                                                                                                                                                         | TckH2iol | Port in hold after CLKOUT <sup>(1,2)</sup>                               | 0*           | —    | _    | ns    |

| 17                                                                                                                                                         | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(2)</sup>            | —            | —    | 100  | ns    |

| 18                                                                                                                                                         | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid<br>(I/O in hold time) | TBD          | —    | —    | ns    |

| 19                                                                                                                                                         | TioV2osH | Port input valid to OSC1↑<br>(I/O in setup time)                         | TBD          | —    | —    | ns    |

| 20                                                                                                                                                         | TioR     | Port output rise time <sup>(2)</sup>                                     | —            | 10   | 25** | ns    |

| 21                                                                                                                                                         | TioF     | Port output fall time <sup>(2)</sup>                                     | —            | 10   | 25** | ns    |

\* These parameters are characterized but not tested.

- \*\* These parameters are design targets and are not tested. No characterization data available at this time.

- † Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

2: Refer to Figure 19-2 for load conditions.

© 1997-2013 Microchip Technology Inc.