#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 20                                                                        |

| Program Memory Size        | 3KB (2K x 12)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 72 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            |                                                                           |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 28-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c57c-04i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 4.0   |                                                                                        | -    |

|-------|----------------------------------------------------------------------------------------|------|

| 1.0   | General Description                                                                    |      |

| 2.0   | PIC16C5X Device Varieties                                                              |      |

| 3.0   | Architectural Overview                                                                 |      |

| 4.0   | Oscillator Configurations                                                              | . 15 |

| 5.0   | Reset                                                                                  | . 19 |

| 6.0   | Memory Organization                                                                    | . 25 |

| 7.0   | I/O Ports                                                                              | . 35 |

| 8.0   | Timer0 Module and TMR0 Register                                                        | . 37 |

| 9.0   | Special Features of the CPU                                                            | . 43 |

| 10.0  | Instruction Set Summary                                                                | . 49 |

| 11.0  | Development Support                                                                    | . 61 |

| 12.0  | Electrical Characteristics - PIC16C54/55/56/57                                         | . 67 |

| 13.0  | Electrical Characteristics - PIC16CR54A                                                |      |

| 14.0  | Device Characterization - PIC16C54/55/56/57/CR54A                                      | . 91 |

| 15.0  | Electrical Characteristics - PIC16C54A                                                 | 103  |

| 16.0  | Device Characterization - PIC16C54A                                                    | 117  |

| 17.0  | Electrical Characteristics - PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/C58B/CR58B     | 131  |

| 18.0  | Device Characterization - PIC16C54C/CR54C/C55A/C56A/CR56A/CR56A/CR57C/CR57C/C58B/CR58B | 145  |

| 19.0  | Electrical Characteristics - PIC16C54C/C55A/C56A/C57C/C58B 40MHz                       | 155  |

| 20.0  | Device Characterization - PIC16C54C/C55A/C56A/C57C/C58B 40MHz                          | 165  |

| 21.0  | Packaging Information                                                                  | 171  |

| Appe  | ndix A: Compatibility                                                                  | 182  |

| On-L  | ne Support                                                                             | 187  |

| Read  | er Response                                                                            | 188  |

| Produ | uct Identification System                                                              | 189  |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

NOTES:

NOTES:

# 5.2 Device Reset Timer (DRT)

The Device Reset Timer (DRT) provides an 18 ms nominal time-out on RESET regardless of Oscillator mode used. The DRT operates on an internal RC oscillator. The processor is kept in RESET as long as the DRT is active. The DRT delay allows VDD to rise above VDD min., and for the oscillator to stabilize.

Oscillator circuits based on crystals or ceramic resonators require a certain time after power-up to establish a stable oscillation. The on-chip DRT keeps the device in a RESET condition for approximately 18 ms after the voltage on the MCLR/VPP pin has reached a logic high (VIH) level. Thus, external RC networks connected to the MCLR input are not required in most cases, allowing for savings in cost-sensitive and/or space restricted applications.

The Device Reset time delay will vary from chip to chip due to VDD, temperature, and process variation. See AC parameters for details.

The DRT will also be triggered upon a Watchdog Timer time-out. This is particularly important for applications using the WDT to wake the PIC16C5X from SLEEP mode automatically.

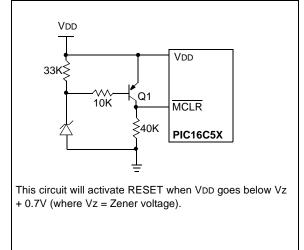

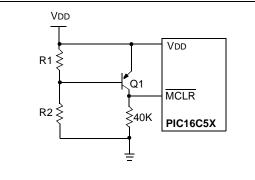

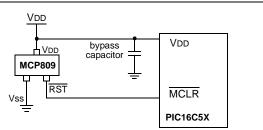

# 5.3 Reset on Brown-Out

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be RESET in the event of a brown-out.

To RESET PIC16C5X devices when a brown-out occurs, external brown-out protection circuits may be built, as shown in Figure 5-6, Figure 5-7 and Figure 5-8.

## FIGURE 5-7:

#### EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, although less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

#### FIGURE 5-8:

#### EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both "active high and active low" RESET pins. There are 7 different trip point selections to accommodate 5V and 3V systems.

# 6.3 STATUS Register

This register contains the arithmetic status of the ALU, the RESET status and the page preselect bits for program memories larger than 512 words.

The STATUS Register can be the destination for any instruction, as with any other register. If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not

writable. Therefore, the result of an instruction with the STATUS Register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS Register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS Register because these instructions do not affect the Z, DC or C bits from the STATUS Register. For other instructions which do affect STATUS Bits, see Section 10.0, Instruction Set Summary.

# REGISTER 6-1: STATUS REGISTER (ADDRESS: 03h)

|          | R/W-0                              | R/W-0                              | R/W-0        | R-1          | R-1                        | R/W-x         | R/W-x          | R/W-x          |

|----------|------------------------------------|------------------------------------|--------------|--------------|----------------------------|---------------|----------------|----------------|

|          | PA2                                | PA1                                | PA0          | TO           | PD                         | Z             | DC             | С              |

|          | bit 7                              |                                    |              |              |                            |               |                | bit 0          |

| bit 7:   | PA2: This bit                      | unused at th                       | is time.     |              |                            |               |                |                |

|          |                                    | A2 bit as a ge<br>with future pr   |              | e read/write | bit is not recor           | mmended, sir  | nce this may a | affect upward  |

| bit 6-5: |                                    |                                    |              | -            | CR56)(PIC16                |               |                | 58)            |

|          |                                    |                                    |              |              | 16C57/CR57,<br>16C57/CR57, |               |                |                |

|          |                                    | (400h - 5FFh                       |              |              |                            | FIC 10C30/C   | N00            |                |

|          | 11 = Page 3                        | (600h - 7FFh                       | •            |              |                            |               |                |                |

|          | Each page is                       |                                    | deperal pur  | ose read/wr  | ite bits in devi           | ices which do | not use them   | for program    |

|          |                                    |                                    |              |              | affect upward              |               |                |                |

| bit 4:   | TO: Time-ou                        |                                    |              | ,            | •                          |               |                |                |

|          |                                    | ver-up, CLRWI<br>ime-out occur     |              | , or sleep i | nstruction                 |               |                |                |

| bit 3:   | PD: Power-d                        | lown bit                           |              |              |                            |               |                |                |

|          | •                                  | ver-up or by tl<br>ution of the SI |              |              |                            |               |                |                |

| bit 2:   | Z: Zero bit                        |                                    |              |              |                            |               |                |                |

|          |                                    | lt of an arithm<br>It of an arithm |              |              |                            |               |                |                |

| bit 1:   | DC: Digit car                      | ry/borrow bit                      | (for ADDWF a | nd SUBWF in  | structions)                |               |                |                |

|          | ADDWF                              |                                    |              |              |                            |               |                |                |

|          |                                    | rom the 4th la<br>rom the 4th la   |              |              |                            |               |                |                |

|          | SUBWF                              |                                    |              |              |                            |               |                |                |

|          |                                    |                                    |              |              | did not occur              |               |                |                |

|          |                                    | from the 4th                       |              |              |                            |               |                |                |

| bit 0:   | •                                  | row bit (for AI                    |              |              | F instructions             |               | _              |                |

|          | <b>ADDWF</b><br>1 = A carry o      | ocurred                            |              | orrow did n  | ot occur                   | RRF or RLI    |                | , respectively |

|          | $\pm = \pi \operatorname{carry} 0$ | locurrou                           | / · ·        |              |                            |               |                |                |

| Legena:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared        | x = bit is unknown |

NOTES:

# PIC16C5X

| XORLW                                                           | Exclusive OR literal with W |               |                                           |           |  |

|-----------------------------------------------------------------|-----------------------------|---------------|-------------------------------------------|-----------|--|

| Syntax:                                                         | [label]                     | XORLW         | k                                         |           |  |

| Operands:                                                       | $0 \le k \le 2$             | 55            |                                           |           |  |

| Operation:                                                      | (W) .XOF                    | $R. k \to (W$ | /)                                        |           |  |

| Status Affected:                                                | Z                           |               |                                           |           |  |

| Encoding:                                                       | 1111                        | kkkk          | kkkk                                      |           |  |

| Description:                                                    | XOR'ed                      | with the e    | e W regis<br>eight bit lit<br>ed in the V | eral 'k'. |  |

| Words:                                                          | 1                           |               |                                           |           |  |

| Cycles:                                                         | 1                           |               |                                           |           |  |

| Example:                                                        | XORLW                       | 0xAF          |                                           |           |  |

| Before Instruction<br>W = 0xB5<br>After Instruction<br>W = 0x1A |                             |               |                                           |           |  |

| Exclusive OR W with f                                                                                                                                        |                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| [ label ] XORWF f,d                                                                                                                                          | -                                   |

| $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                             |                                     |

| (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                           |                                     |

| ted: Z                                                                                                                                                       |                                     |

| 0001 10df ffff                                                                                                                                               |                                     |

| W register with register 'f'. If 'd' is 0<br>the result is stored in the W regis-<br>ter. If 'd' is 1 the result is stored<br>back in register 'f'.          |                                     |

| 1                                                                                                                                                            |                                     |

| 1                                                                                                                                                            |                                     |

| XORWF REG,1                                                                                                                                                  |                                     |

| Instruction<br>G = 0xAF<br>= 0xB5<br>struction<br>G = 0x1A<br>= 0xB5                                                                                         |                                     |

| the result is stored in t<br>ter. If 'd' is 1 the result<br>back in register 'f'.<br>1<br>1<br>XORWF REG, 1<br>nstruction<br>G = 0xAF<br>= 0xB5<br>struction | er 'f'. If 'd' is 0<br>the W regis- |

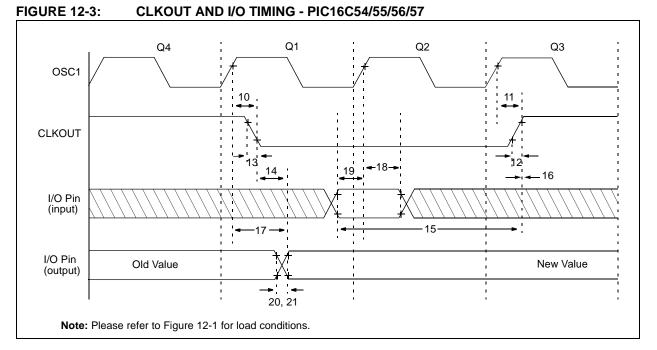

#### TABLE 12-2: CLKOUT AND I/O TIMING REQUIREMENTS - PIC16C54/55/56/57

| AC Char      | acteristics | $\begin{array}{llllllllllllllllllllllllllllllllllll$                     |              |      |      |       |  |

|--------------|-------------|--------------------------------------------------------------------------|--------------|------|------|-------|--|

| Param<br>No. | Symbol      | Characteristic                                                           | Min          | Тур† | Max  | Units |  |

| 10           | TosH2ckL    | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                                          | _            | 15   | 30** | ns    |  |

| 11           | TosH2ckH    | OSC1↑ to CLKOUT↑ <sup>(1)</sup>                                          | _            | 15   | 30** | ns    |  |

| 12           | TckR        | CLKOUT rise time <sup>(1)</sup>                                          |              | 5.0  | 15** | ns    |  |

| 13           | TckF        | CLKOUT fall time <sup>(1)</sup>                                          | —            | 5.0  | 15** | ns    |  |

| 14           | TckL2ioV    | CLKOUT↓ to Port out valid <sup>(1)</sup>                                 |              |      | 40** | ns    |  |

| 15           | TioV2ckH    | Port in valid before CLKOUT <sup>(1)</sup>                               | 0.25 TCY+30* | _    | _    | ns    |  |

| 16           | TckH2iol    | Port in hold after CLKOUT <sup>(1)</sup>                                 | 0*           | _    | _    | ns    |  |

| 17           | TosH2ioV    | OSC1↑ (Q1 cycle) to Port out valid <sup>(2)</sup>                        | _            |      | 100* | ns    |  |

| 18           | TosH2iol    | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid<br>(I/O in hold time) | TBD          | —    |      | ns    |  |

| 19           | TioV2osH    | Port input valid to OSC1↑<br>(I/O in setup time)                         | TBD          | —    | —    | ns    |  |

| 20           | TioR        | Port output rise time <sup>(2)</sup>                                     | —            | 10   | 25** | ns    |  |

| 21           | TioF        | Port output fall time <sup>(2)</sup>                                     | —            | 10   | 25** | ns    |  |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested. No characterization data available at this time.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

2: Please refer to Figure 12-1 for load conditions.

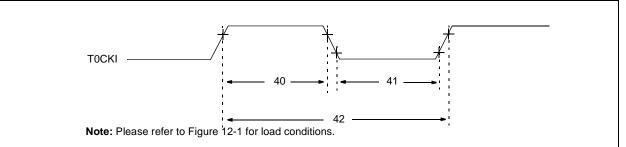

### FIGURE 12-5: TIMER0 CLOCK TIMINGS - PIC16C54/55/56/57

#### TABLE 12-4: TIMER0 CLOCK REQUIREMENTS - PIC16C54/55/56/57

| AC Characteristics Standard Operating C Operating Temperature |        |                                                              | •                            | +70°C f<br>+85°C f | or com<br>or indu | mercial<br>strial | )                                                              |

|---------------------------------------------------------------|--------|--------------------------------------------------------------|------------------------------|--------------------|-------------------|-------------------|----------------------------------------------------------------|

| Param<br>No.                                                  | Symbol | Characteristic                                               | Min                          | Тур†               | Max               | Units             | Conditions                                                     |

| 40                                                            | Tt0H   | T0CKI High Pulse Width<br>- No Prescaler<br>- With Prescaler | 0.5 Tcy + 20*<br>10*         |                    | _                 | ns<br>ns          |                                                                |

| 41                                                            | Tt0L   | T0CKI Low Pulse Width<br>- No Prescaler<br>- With Prescaler  | 0.5 Tcy + 20*<br>10*         |                    | _                 | ns<br>ns          |                                                                |

| 42                                                            | Tt0P   | T0CKI Period                                                 | 20 or <u>Tcy + 40</u> *<br>N |                    |                   | ns                | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

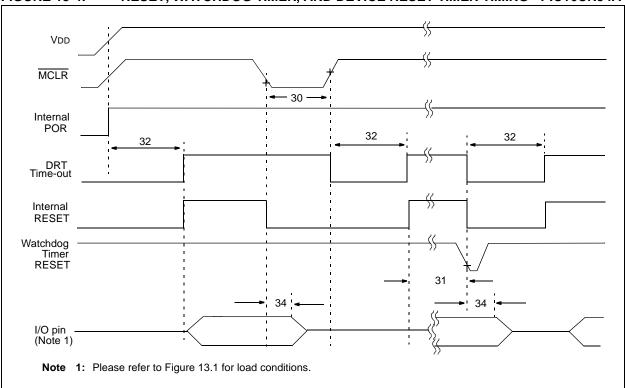

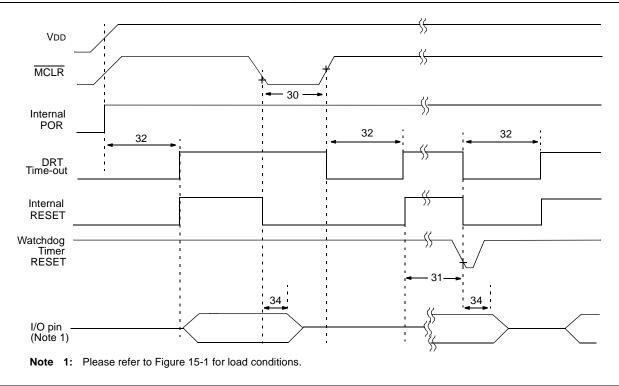

#### FIGURE 13-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16CR54A

### TABLE 13-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16CR54A

| AC Chara            | cteristics | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \\ \end{array} $ |      |      |      |       |                   |

|---------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|-------------------|

| Param<br>No. Symbol |            | Characteristic                                                                                                                                                                                                                                                                                                                        | Min  | Тур† | Max  | Units | Conditions        |

| 30                  | TmcL       | MCLR Pulse Width (low)                                                                                                                                                                                                                                                                                                                | 1.0* |      |      | μS    | VDD = 5.0V        |

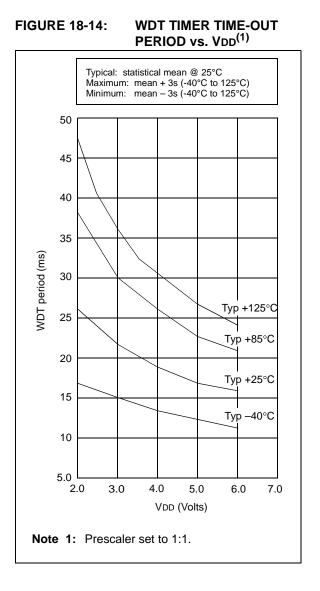

| 31                  | Twdt       | Watchdog Timer Time-out Period<br>(No Prescaler)                                                                                                                                                                                                                                                                                      | 7.0* | 18*  | 40*  | ms    | VDD = 5.0V (Comm) |

| 32                  | Tdrt       | Device Reset Timer Period                                                                                                                                                                                                                                                                                                             | 7.0* | 18*  | 30*  | ms    | VDD = 5.0V (Comm) |

| 34                  | Tioz       | I/O Hi-impedance from MCLR Low                                                                                                                                                                                                                                                                                                        | _    | _    | 1.0* | μS    |                   |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

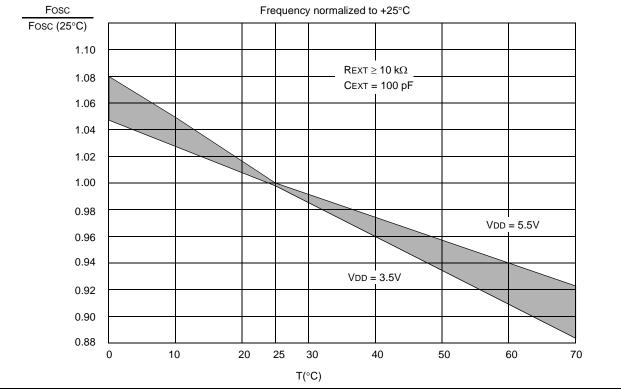

# 14.0 DEVICE CHARACTERIZATION - PIC16C54A

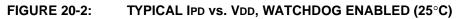

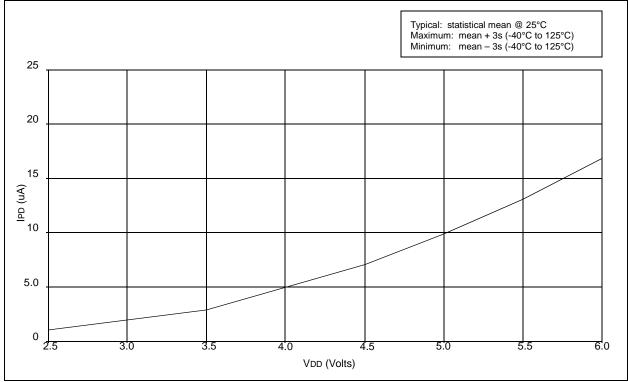

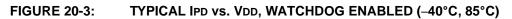

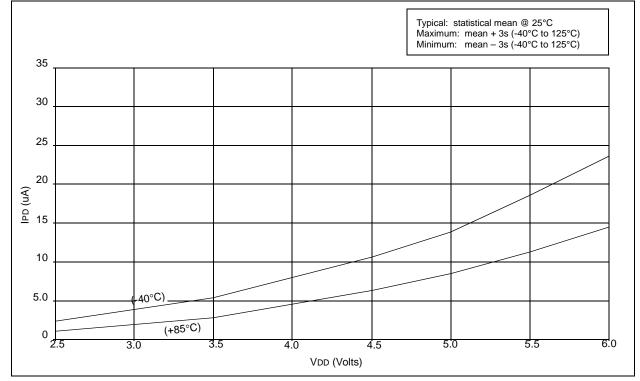

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

### TABLE 14-1: RC OSCILLATOR FREQUENCIES

| Сехт   | Rext | Average<br>Fosc @ 5 V, 25°C |       |  |  |  |

|--------|------|-----------------------------|-------|--|--|--|

| 20 pF  | 3.3K | 5 MHz                       | ± 27% |  |  |  |

|        | 5K   | 3.8 MHz                     | ± 21% |  |  |  |

|        | 10K  | 2.2 MHz                     | ± 21% |  |  |  |

|        | 100K | 262 kHz                     | ± 31% |  |  |  |

| 100 pF | 3.3K | 1.6 MHz                     | ± 13% |  |  |  |

|        | 5K   | 1.2 MHz                     | ± 13% |  |  |  |

|        | 10K  | 684 kHz                     | ± 18% |  |  |  |

|        | 100K | 71 kHz                      | ± 25% |  |  |  |

| 300 pF | 3.3K | 660 kHz                     | ± 10% |  |  |  |

|        | 5.0K | 484 kHz                     | ± 14% |  |  |  |

|        | 10K  | 267 kHz                     | ± 15% |  |  |  |

|        | 100K | 29 kHz                      | ± 19% |  |  |  |

The frequencies are measured on DIP packages.

The percentage variation indicated here is part-to-part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviations from the average value for VDD = 5V.

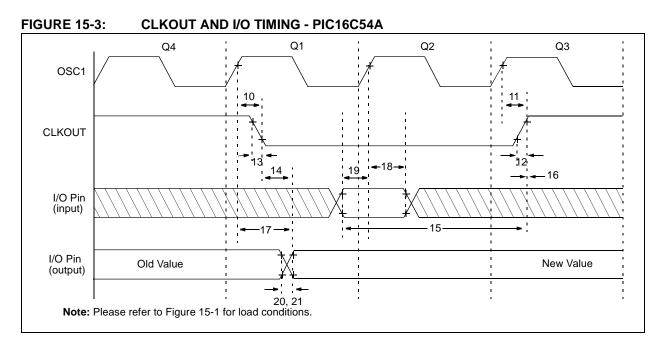

### TABLE 15-2: CLKOUT AND I/O TIMING REQUIREMENTS - PIC16C54A

| AC CharacteristicsStandard Operating Conditions (unless otherwise specified)<br>Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-20^{\circ}C \le TA \le +85^{\circ}C$ for industrial - PIC16LV54A-021<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |          |                                                                       |              |      |      |       |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------|--------------|------|------|-------|--|

| Param<br>No.                                                                                                                                                                                                                                                                                                                                         | Symbol   | Characteristic                                                        | Min          | Тур† | Мах  | Units |  |

| 10                                                                                                                                                                                                                                                                                                                                                   | TosH2ckL | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                                       | —            | 15   | 30** | ns    |  |

| 11                                                                                                                                                                                                                                                                                                                                                   | TosH2ckH | OSC1↑ to CLKOUT↑ <sup>(1)</sup>                                       | —            | 15   | 30** | ns    |  |

| 12                                                                                                                                                                                                                                                                                                                                                   | TckR     | CLKOUT rise time <sup>(1)</sup>                                       | —            | 5.0  | 15** | ns    |  |

| 13                                                                                                                                                                                                                                                                                                                                                   | TckF     | CLKOUT fall time <sup>(1)</sup>                                       | —            | 5.0  | 15** | ns    |  |

| 14                                                                                                                                                                                                                                                                                                                                                   | TckL2ioV | CLKOUT↓ to Port out valid <sup>(1)</sup>                              | —            | —    | 40** | ns    |  |

| 15                                                                                                                                                                                                                                                                                                                                                   | TioV2ckH | Port in valid before CLKOUT <sup>(1)</sup>                            | 0.25 TCY+30* | —    | —    | ns    |  |

| 16                                                                                                                                                                                                                                                                                                                                                   | TckH2iol | Port in hold after CLKOUT <sup>(1)</sup>                              | 0*           | —    | —    | ns    |  |

| 17                                                                                                                                                                                                                                                                                                                                                   | TosH2ioV | OSC1↑ (Q1 cycle) to Port out valid <sup>(2)</sup>                     | —            | —    | 100* | ns    |  |

| 18                                                                                                                                                                                                                                                                                                                                                   | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid (I/O in hold time) | TBD          | —    | —    | ns    |  |

| 19                                                                                                                                                                                                                                                                                                                                                   | TioV2osH | Port input valid to OSC1↑<br>(I/O in setup time)                      | TBD          | —    | —    | ns    |  |

| 20                                                                                                                                                                                                                                                                                                                                                   | TioR     | Port output rise time <sup>(2)</sup>                                  | —            | 10   | 25** | ns    |  |

| 21                                                                                                                                                                                                                                                                                                                                                   | TioF     | Port output fall time <sup>(2)</sup>                                  | —            | 10   | 25** | ns    |  |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested. No characterization data available at this time.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

**Note 1:** Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

2: Please refer to Figure 15-1 for load conditions.

#### FIGURE 15-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16C54A

#### TABLE 15-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16C54A

|          |            | Standard Operating Condition | ns (unle             | ess othe         | erwise    | specifie   | ed)                          |

|----------|------------|------------------------------|----------------------|------------------|-----------|------------|------------------------------|

|          |            | Operating Temperature 0      | $0^{\circ}C \leq TA$ | √≤ <b>+</b> 70°  | C for co  | mmercia    | al                           |

| AC Chara | cteristics | -40                          | $0^{\circ}C \leq TA$ | √≤ <b>+</b> 85°  | C for ind | dustrial   |                              |

|          |            | -20                          | $0^{\circ}C \leq TA$ | ∖ ≤ <b>+</b> 85° | C for ind | dustrial - | - PIC16LV54A-02I             |

|          |            | -40                          | $0^{\circ}C \leq TA$ | ∖ ≤ <b>+</b> 125 | °C for e  | xtended    | ł                            |

| Param    |            |                              |                      |                  |           |            |                              |

| No.      | Symbol     | Characteristic               | Min                  | Тур†             | Мах       | Units      | Conditions                   |

| 30       | TmcL       | MCLR Pulse Width (low)       | 100*                 | _                | _         | ns         | VDD = 5.0V                   |

|          |            |                              | 1                    | —                | —         | μS         | VDD = 5.0V (PIC16LV54A only) |

| 31       | Twdt       | Watchdog Timer Time-out      | 9.0*                 | 18*              | 30*       | ms         | VDD = 5.0V (Comm)            |

|          |            | Period (No Prescaler)        |                      |                  |           |            |                              |

| 32       | Tdrt       | Device Reset Timer Period    | 9.0*                 | 18*              | 30*       | ms         | VDD = 5.0V (Comm)            |

| 34       | Tioz       | I/O Hi-impedance from MCLR   | _                    | _                | 100*      | ns         |                              |

|          |            | Low                          | —                    |                  | 1μs       | —          | (PIC16LV54A only)            |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C5X

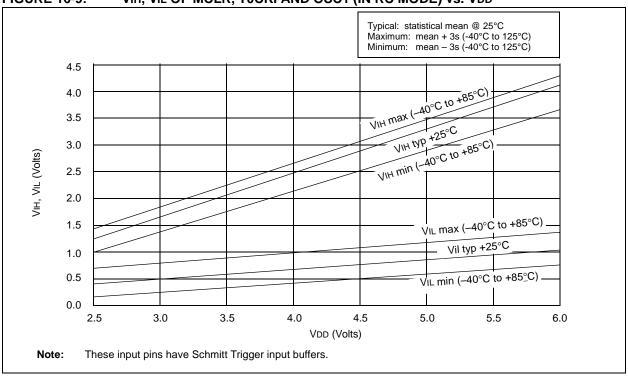

FIGURE 16-9: VIH, VIL OF MCLR, TOCKI AND OSC1 (IN RC MODE) vs. VDD

# 17.0 ELECTRICAL CHARACTERISTICS - PIC16LC54A

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                                   | –55°C to +125°C       |

|----------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Storage temperature                                                                                                              |                       |

| Voltage on VDD with respect to Vss                                                                                               | 0 to +7.5V            |

| Voltage on MCLR with respect to Vss                                                                                              | 0 to +14V             |

| Voltage on all other pins with respect to Vss0.0                                                                                 | 6V to (VDD + 0.6V)    |

| Total power dissipation <sup>(1)</sup>                                                                                           | 800 mW                |

| Max. current out of Vss pin                                                                                                      | 150 mA                |

| Max. current into Vod pin                                                                                                        |                       |

| Max. current into an input pin (T0CKI only)                                                                                      | ±500 μA               |

| Input clamp current, liк (Vi < 0 or Vi > VDD)                                                                                    | ±20 mA                |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                                                   | ±20 mA                |

| Max. output current sunk by any I/O pin                                                                                          | 25 mA                 |

| Max. output current sourced by any I/O pin                                                                                       | 20 mA                 |

| Max. output current sourced by a single I/O (Port A, B or C)                                                                     | 50 mA                 |

| Max. output current sunk by a single I/O (Port A, B or C)                                                                        | 50 mA                 |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) x let $x \in X$ } | OH} + $∑$ (VOL x IOL) |

**†** NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

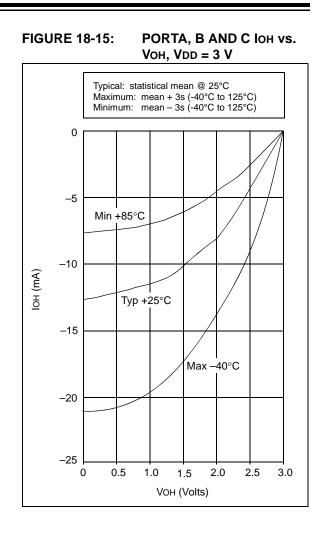

## 17.2 DC Characteristics: PIC16C54C/C55A/C56A/C57C/C58B-04E, 20E (Extended) PIC16CR54C/CR56A/CR57C/CR58B-04E, 20E (Extended)

| PIC16C54C/C55A/C56A/C57C/C58B-04E, 20E<br>PIC16CR54C/CR56A/CR57C/CR58B-04E, 20E<br>(Extended) |        |                                                                            |            |                                    |                                       |                                  |                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------|------------|------------------------------------|---------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                                                                                  | Symbol | Characteristic                                                             | Min        | Тур†                               | Max                                   | Units                            | Conditions                                                                                                                                                        |

| D001                                                                                          | Vdd    | Supply Voltage                                                             | 3.0<br>4.5 |                                    | 5.5<br>5.5                            |                                  | RC, XT, LP, and HS mode<br>from 0 - 10 MHz<br>from 10 - 20 MHz                                                                                                    |

| D002                                                                                          | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>                                  | —          | 1.5*                               | —                                     | V                                | Device in SLEEP mode                                                                                                                                              |

| D003                                                                                          | VPOR   | VDD start voltage to ensure<br>Power-on Reset                              | —          | Vss                                | —                                     | V                                | See Section 5.1 for details on<br>Power-on Reset                                                                                                                  |

| D004                                                                                          | SVDD   | VDD rise rate to ensure<br>Power-on Reset                                  | 0.05*      | —                                  | —                                     | V/ms                             | See Section 5.1 for details on<br>Power-on Reset                                                                                                                  |

| D010                                                                                          | IDD    | Supply Current <sup>(2)</sup><br>XT and RC <sup>(3)</sup> modes<br>HS mode | _          | 1.8<br>9.0                         | 3.3<br>20                             | mA<br>mA                         | Fosc = 4.0 MHz, Vdd = 5.5V<br>Fosc = 20 MHz, Vdd = 5.5V                                                                                                           |

| D020                                                                                          | IPD    | Power-down Current <sup>(2)</sup>                                          |            | 0.3<br>10<br>12<br>4.8<br>18<br>26 | 17<br>50*<br>60*<br>31*<br>68*<br>90* | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 3.0V, WDT disabled<br>VDD = 4.5V, WDT disabled<br>VDD = 5.5V, WDT disabled<br>VDD = 3.0V, WDT enabled<br>VDD = 4.5V, WDT enabled<br>VDD = 5.5V, WDT enabled |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- **3:** Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

# PIC16C5X

#### INDEX

#### Α

| Absolute Maximum Ratings                    |

|---------------------------------------------|

| PIC16C54/55/56/5767                         |

| PIC16C54A 103                               |

| PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/ |

| C58B/CR58B 131                              |

| PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/ |

| C58B/CR58B-40 155                           |

| PIC16CR54A79                                |

| ADDWF                                       |

| ALU                                         |

| ANDLW                                       |

| ANDWF51                                     |

| Applications5                               |

| Architectural Overview                      |

| Assembler                                   |

| MPASM Assembler 61                          |

# в

| Block Diagram                |    |

|------------------------------|----|

| On-Chip Reset Circuit        |    |

| PIC16C5X Series              |    |

| Timer0                       |    |

| TMR0/WDT Prescaler           | 41 |

| Watchdog Timer               |    |

| Brown-Out Protection Circuit |    |

| BSF                          |    |

| BTFSC                        |    |

| BTFSS                        |    |

|                              |    |

# С

| CALL               | 31, 53 |

|--------------------|--------|

| Carry (C) bit      |        |

| Clocking Scheme    |        |

| CLRF               | 53     |

| CLRW               | 53     |

| CLRWDT             | 53     |

| CMOS Technology    | 1      |

| Code Protection    | 43, 47 |

| COMF               | 54     |

| Compatibility      |        |

| Configuration Bits |        |

# D

| Data Memory Organization                    |

|---------------------------------------------|

| PIC16C54/55/56/57                           |

| Commercial                                  |

| Extended70, 72                              |

| Industrial69, 71                            |

| PIC16C54A                                   |

| Commercial104, 109                          |

| Extended106, 109                            |

| Industrial 104, 109                         |

| PIC16C54C/C55A/C56A/C57C/C58B-40            |

| Commercial157, 158                          |

| PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/ |

| C58B/CR58B                                  |

| Commercial134, 138                          |

| Extended137, 138                            |

| Industrial134, 138                          |

| PIC16CR54A                                  |

| Commercial                                  |

| Extended                         | 82, 84   |

|----------------------------------|----------|

| Industrial                       | 80, 83   |

| PIC16LV54A                       |          |

| Commercial                       | 108, 109 |

| Industrial                       | 108, 109 |

| DECF                             | 54       |

| DECFSZ                           | 54       |

| Development Support              | 61       |

| Device Characterization          |          |

| PIC16C54/55/56/57/CR54A          | 91       |

| PIC16C54A                        | 117      |

| PIC16C54C/C55A/C56A/C57C/C58B-40 | 165      |

| Device Reset Timer (DRT)         | 23       |

| Device Varieties                 | 7        |

| Digit Carry (DC) bit             |          |

| DRT                              | 23       |

# Ε

| Electrical Specifications                   |

|---------------------------------------------|

| PIC16C54/55/56/57 67                        |

| PIC16C54A103                                |

| PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/ |

| C58B/CR58B 131                              |

| PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/ |

| C58B/CR58B-40155                            |

| PIC16CR54A 79                               |

| Errata                                      |

| External Power-On Reset Circuit 21          |

## F

| Family of Devices |  |

|-------------------|--|

| PIC16C5X          |  |

| FSR Register      |  |

| Value on reset    |  |

|                   |  |

# G

| General Purpose Registers |       |

|---------------------------|-------|

| Value on reset            | 20    |

| GOTO 31                   | l, 55 |

# Н

| High-Performance RISC CPU | . 1 |

|---------------------------|-----|

|---------------------------|-----|

# ī

| •                              |        |

|--------------------------------|--------|

| I/O Interfacing                | 35     |

| I/O Ports                      | 35     |

| I/O Programming Considerations | 36     |

| ICEPIC In-Circuit Emulator     | 62     |

| ID Locations                   | 43, 47 |

| INCF                           | 55     |

| INCFSZ                         | 55     |

| INDF Register                  | 33     |

| Value on reset                 | 20     |

| Indirect Data Addressing       | 33     |

| Instruction Cycle              | 13     |

| Instruction Flow/Pipelining    | 13     |

| Instruction Set Summary        | 49     |

| IORLW                          | 56     |

| IORWF                          | 56     |

| к                              |        |

|                                |        |

# KeeLoq Evaluation and Programming Tools ...... 64

| 3 | 1 |

|---|---|

| 3 | 1 |

L

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 1997-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769355

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.