### Microchip Technology - PIC16C57T-HSI/SO Datasheet

Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 20                                                                         |

| Program Memory Size        | 3KB (2K x 12)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 72 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c57t-hsi-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 5.1 Power-On Reset (POR)

The PIC16C5X family incorporates on-chip Power-On Reset (POR) circuitry which provides an internal chip RESET for most power-up situations. To use this feature, the user merely ties the MCLR/VPP pin to VDD. A simplified block diagram of the on-chip Power-On Reset circuit is shown in Figure 5-1.

The Power-On Reset circuit and the Device Reset Timer (Section 5.2) circuit are closely related. On power-up, the RESET latch is set and the DRT is <u>RESET</u>. The DRT timer begins counting once it detects MCLR to be high. After the time-out period, which is typically 18 ms, it will RESET the reset latch and thus end the on-chip RESET signal.

A power-up example where MCLR is not tied to VDD is shown in Figure 5-3. VDD is allowed to rise and stabilize before bringing MCLR high. The chip will actually come out of reset TDRT msec after MCLR goes high.

In Figure 5-4, the on-chip Power-On Reset feature is being used (MCLR and VDD are tied together). The VDD is stable before the start-up timer times out and there is no problem in getting a proper RESET. However, Figure 5-5 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses a high on the MCLR/VPP pin, and when the MCLR/VPP pin (and VDD) actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip is, therefore, not guaranteed to function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 5-2).

Note: When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For more information on PIC16C5X POR, see *Power-Up Considerations* - AN522 in the <u>Embedded Control Handbook</u>.

The POR circuit does not produce an internal RESET when VDD declines.

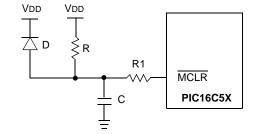

### FIGURE 5-2:

### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- External Power-On Reset circuit is required only if VDD power-up is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device electrical specification.

- R1 =  $100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

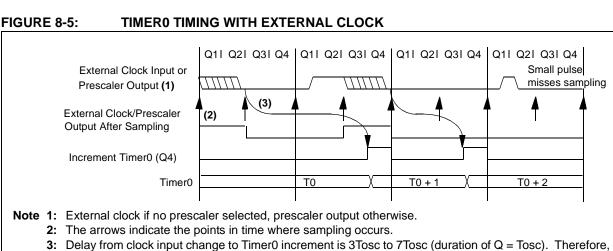

### 8.1 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 8.1.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 8-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 8.1.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 8-5 shows the delay from the external clock edge to the timer incrementing.

Belay from clock input change to Timer0 increment is 3 lose to 7 lose (duration of Q = lose). There the error in measuring the interval between two edges on Timer0 input = ± 4 Tose max.

# PIC16C5X

| COMF                                                                                                                                                                          | Complement f                                                   |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:                                                                                                                                                                       | [ <i>label</i> ] COMF f,d                                      |  |  |  |  |  |  |  |  |  |

| Operands:                                                                                                                                                                     | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$ |  |  |  |  |  |  |  |  |  |

| Operation:                                                                                                                                                                    | $(\overline{f}) \rightarrow (dest)$                            |  |  |  |  |  |  |  |  |  |

| Status Affected:                                                                                                                                                              | Z                                                              |  |  |  |  |  |  |  |  |  |

| Encoding:                                                                                                                                                                     | 0010 01df ffff                                                 |  |  |  |  |  |  |  |  |  |

| Description: The contents of register 'f' are<br>complemented. If 'd' is 0 the res<br>is stored in the W register. If 'd' is<br>the result is stored back in<br>register 'f'. |                                                                |  |  |  |  |  |  |  |  |  |

| Words:                                                                                                                                                                        | 1                                                              |  |  |  |  |  |  |  |  |  |

| Cycles:                                                                                                                                                                       | 1                                                              |  |  |  |  |  |  |  |  |  |

| Example:                                                                                                                                                                      | COMF REG1,0                                                    |  |  |  |  |  |  |  |  |  |

| Before Instru<br>REG1<br>After Instruct<br>REG1<br>W                                                                                                                          | = 0x13                                                         |  |  |  |  |  |  |  |  |  |

| DECF                                                    | Decrement f                                                                                                                                 |        |      |  |  |  |  |  |  |  |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------|------|--|--|--|--|--|--|--|

| Syntax:                                                 | [label] DECF f,d                                                                                                                            |        |      |  |  |  |  |  |  |  |

| Operands:                                               | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                              |        |      |  |  |  |  |  |  |  |

| Operation:                                              | $(f) - 1 \rightarrow$                                                                                                                       | (dest) |      |  |  |  |  |  |  |  |

| Status Affected:                                        | Z                                                                                                                                           |        |      |  |  |  |  |  |  |  |

| Encoding:                                               | 0000                                                                                                                                        | 11df   | ffff |  |  |  |  |  |  |  |

| Description:                                            | Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If<br>'d' is 1 the result is stored back in<br>register 'f'. |        |      |  |  |  |  |  |  |  |

| Words:                                                  | 1                                                                                                                                           |        |      |  |  |  |  |  |  |  |

| Cycles:                                                 | 1                                                                                                                                           |        |      |  |  |  |  |  |  |  |

| Example:                                                | DECF                                                                                                                                        | CNT,   | 1    |  |  |  |  |  |  |  |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0<br>= 0<br>ion                                                                                                                           | <01    |      |  |  |  |  |  |  |  |

| DECFSZ                                                | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                               | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Operands:                                             | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Operation:                                            | (f) $-1 \rightarrow d$ ; skip if result = 0                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Status Affected:                                      | None                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Encoding:                                             | 0010 11df ffff                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Description:                                          | The contents of register 'f' are dec-<br>remented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded and a NOP is executed<br>instead making it a two-cycle<br>instruction. |  |  |  |  |  |  |

| Words:                                                | 1                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Cycles:                                               | 1(2)                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Example:                                              | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Before Instru<br>PC                                   | = address (HERE)                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| After Instruct<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC | tion<br>= CNT - 1;<br>= 0,<br>= address (CONTINUE);<br>≠ 0,<br>= address (HERE+1)                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

# PIC16C5X

| IORLW                                               | Inclusive OR literal with W                                                                                                 |  |  |  |  |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:                                             | [label] IORLW k                                                                                                             |  |  |  |  |  |  |  |  |

| $Operands: \qquad 0 \le k \le 255$                  |                                                                                                                             |  |  |  |  |  |  |  |  |

| Operation:                                          | (W) .OR. (k) $\rightarrow$ (W)                                                                                              |  |  |  |  |  |  |  |  |

| Status Affected:                                    | Z                                                                                                                           |  |  |  |  |  |  |  |  |

| Encoding:                                           | 1101 kkkk kkkk                                                                                                              |  |  |  |  |  |  |  |  |

| Description:                                        | The contents of the W register are<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W regis-<br>ter. |  |  |  |  |  |  |  |  |

| Words:                                              | 1                                                                                                                           |  |  |  |  |  |  |  |  |

| Cycles:                                             | 1                                                                                                                           |  |  |  |  |  |  |  |  |

| Example:                                            | IORLW 0x35                                                                                                                  |  |  |  |  |  |  |  |  |

| Before Instru<br>W =<br>After Instruc<br>W =<br>Z = | 0x9A<br>tion                                                                                                                |  |  |  |  |  |  |  |  |

| IORWF                                                            | Inclusive OR W with f                                                                                                                                                 |  |  |  |  |  |  |  |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:                                                          | [ <i>label</i> ] IORWF f,d                                                                                                                                            |  |  |  |  |  |  |  |

| Operands:                                                        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                            |  |  |  |  |  |  |  |

| Operation:                                                       | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                                      |  |  |  |  |  |  |  |

| Status Affected:                                                 | Z                                                                                                                                                                     |  |  |  |  |  |  |  |

| Encoding:                                                        | 0001 00df ffff                                                                                                                                                        |  |  |  |  |  |  |  |

| Description:                                                     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |  |  |  |  |  |  |  |

| Words:                                                           | 1                                                                                                                                                                     |  |  |  |  |  |  |  |

| Cycles:                                                          | 1                                                                                                                                                                     |  |  |  |  |  |  |  |

| Example:                                                         | IORWF RESULT, 0                                                                                                                                                       |  |  |  |  |  |  |  |

| Before Instru<br>RESUL<br>W<br>After Instruct<br>RESUL<br>W<br>Z | Γ = 0x13<br>= 0x91<br>tion                                                                                                                                            |  |  |  |  |  |  |  |

| MOVF                  | Move f                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:               | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Operands:             | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Operation:            | $(f) \rightarrow (dest)$                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Status Affected:      | Z                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Encoding:             | 0010 00df ffff                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Description:          | The contents of register 'f' is<br>moved to destination 'd'. If 'd' is 0,<br>destination is the W register. If 'd'<br>is 1, the destination is file<br>register 'f'. 'd' is 1 is useful to test a<br>file register since status flag Z is<br>affected. |  |  |  |  |  |  |  |

| Words:                | 1                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Cycles:               | 1                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Example:              | MOVF FSR, 0                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| After Instruct<br>W = | tion<br>- value in FSR register                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| MOVLW                         | Move Literal to W    |       |               |        |  |  |  |  |  |  |

|-------------------------------|----------------------|-------|---------------|--------|--|--|--|--|--|--|

| Syntax:                       | [ label ]            | MOVLW | k             |        |  |  |  |  |  |  |

| Operands:                     | $0 \leq k \leq 2$    | 55    |               |        |  |  |  |  |  |  |

| Operation:                    | $k \rightarrow (W)$  |       |               |        |  |  |  |  |  |  |

| Status Affected:              | None                 |       |               |        |  |  |  |  |  |  |

| Encoding:                     | 1100                 | kkkk  | kkkk          |        |  |  |  |  |  |  |

| Description:                  | The eigh<br>the W re |       | 'k' is loaded | d into |  |  |  |  |  |  |

| Words:                        | 1                    |       |               |        |  |  |  |  |  |  |

| Cycles:                       | 1                    |       |               |        |  |  |  |  |  |  |

| Example:                      | MOVLW                | 0x5A  |               |        |  |  |  |  |  |  |

| After Instruction<br>W = 0x5A |                      |       |               |        |  |  |  |  |  |  |

### 13.3 DC Characteristics: PIC16CR54A-04, 10, 20, PIC16LCR54A-04 (Commercial) PIC16CR54A-04I, 10I, 20I, PIC16LCR54A-04I (Industrial)

| DC CHARACTERISTICS |        |                                                                                                                                     | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \end{array}$ |                        |                                                                     |                       |                                                                                                                                                                               |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                      | Min                                                                                                                                                                                                                                                             | Тур†                   | Max                                                                 | Units                 | Conditions                                                                                                                                                                    |

| D030               | VIL    | Input Low Voltage<br>I/O ports<br>MCLR (Schmitt Trigger)<br>T0CKI (Schmitt Trigger)<br>OSC1 (Schmitt Trigger)<br>OSC1               | Vss<br>Vss<br>Vss<br>Vss<br>Vss                                                                                                                                                                                                                                 |                        | 0.2 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD | V<br>V<br>V<br>V      | Pin at hi-impedance<br>RC mode only <sup>(3)</sup><br>XT, HS and LP modes                                                                                                     |

| D040               | VIн    | Input High Voltage<br>I/O ports<br>I/O ports<br>MCLR (Schmitt Trigger)<br>T0CKI (Schmitt Trigger)<br>OSC1 (Schmitt Trigger)<br>OSC1 | 2.0<br>0.6 VDD<br>0.85 VDD<br>0.85 VDD<br>0.85 VDD<br>0.85 VDD                                                                                                                                                                                                  |                        | VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD                       | V<br>V<br>V<br>V<br>V | VDD = 3.0V to 5.5V <sup>(4)</sup><br>Full VDD range <sup>(4)</sup><br>RC mode only <sup>(3)</sup><br>XT, HS and LP modes                                                      |

| D050               | VHYS   | Hysteresis of Schmitt<br>Trigger inputs                                                                                             | 0.15 VDD*                                                                                                                                                                                                                                                       | —                      | —                                                                   | V                     |                                                                                                                                                                               |

| D060               | lι∟    | Input Leakage Current <sup>(1,2)</sup><br>I/O ports                                                                                 | -1.0                                                                                                                                                                                                                                                            | _                      | +1.0                                                                | μA                    | For VDD $\leq$ 5.5V:<br>VSS $\leq$ VPIN $\leq$ VDD,<br>pin at hi-impedance                                                                                                    |

|                    |        | MCLR<br>MCLR<br>TOCKI<br>OSC1                                                                                                       | -5.0<br><br>-3.0<br>-3.0                                                                                                                                                                                                                                        | —<br>0.5<br>0.5<br>0.5 | <br>+5.0<br>+3.0<br>+3.0                                            | μΑ<br>μΑ<br>μΑ        | $\label{eq:VPIN} \begin{array}{l} VPIN = VSS + 0.25V \\ VPIN = VDD \\ VSS \leq VPIN \leq VDD \\ VSS \leq VPIN \leq VDD, \\ XT,  HS  \text{and}  LP  \text{modes} \end{array}$ |

| D080               | Vol    | Output Low Voltage<br>I/O ports<br>OSC2/CLKOUT                                                                                      |                                                                                                                                                                                                                                                                 | _                      | 0.5<br>0.5                                                          | V<br>V                | IOL = 10  mA,  VDD = 6.0  V<br>IOL = 1.9  mA,  VDD = 6.0  V,<br>RC mode only                                                                                                  |

| D090               | Vон    | Output High Voltage <sup>(2)</sup><br>I/O ports<br>OSC2/CLKOUT                                                                      | Vdd - 0.5<br>Vdd - 0.5                                                                                                                                                                                                                                          | _                      |                                                                     | V<br>V                | IOH = -4.0  mA,  VDD = 6.0  V<br>IOH = -0.8  mA,  VDD = 6.0  V,<br>RC mode only                                                                                               |

\* These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

- 2: Negative current is defined as coming out of the pin.

- **3:** For the RC mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C5X be driven with external clock in RC mode.

- 4: The user may use the better of the two specifications.

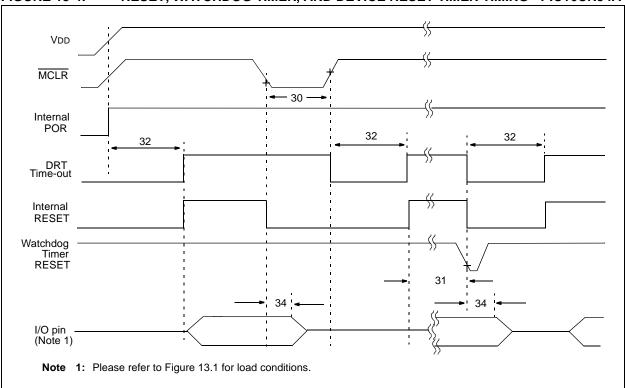

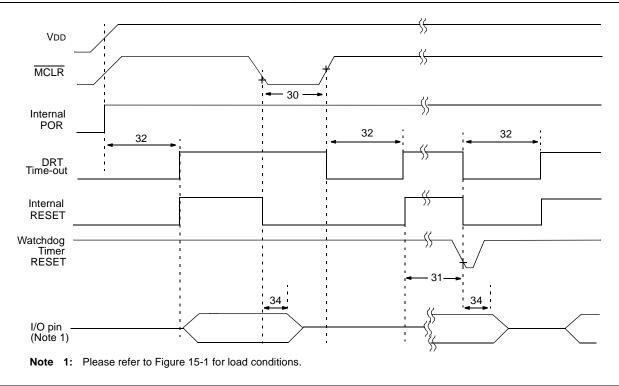

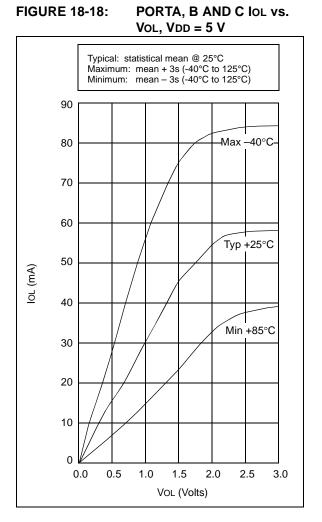

### FIGURE 13-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16CR54A

### TABLE 13-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16CR54A

| $\label{eq:AC Characteristics} \begin{array}{ c c c } \mbox{Standard Operating Conditions (unless otherwise specified)} \\ Operating Temperature & 0^\circ C \leq TA \leq +70^\circ C \mbox{ for commercial} \\ -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array}$ |        |                                                  |      |     |      |    |                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------|------|-----|------|----|-------------------|

| Param<br>No.                                                                                                                                                                                                                                                                                                                                           | Symbol | Characteristic Min Typ† Max Units Conditions     |      |     |      |    |                   |

| 30                                                                                                                                                                                                                                                                                                                                                     | TmcL   | MCLR Pulse Width (low)                           | 1.0* |     |      | μS | VDD = 5.0V        |

| 31                                                                                                                                                                                                                                                                                                                                                     | Twdt   | Watchdog Timer Time-out Period<br>(No Prescaler) | 7.0* | 18* | 40*  | ms | VDD = 5.0V (Comm) |

| 32                                                                                                                                                                                                                                                                                                                                                     | Tdrt   | Device Reset Timer Period                        | 7.0* | 18* | 30*  | ms | VDD = 5.0V (Comm) |

| 34                                                                                                                                                                                                                                                                                                                                                     | Tioz   | I/O Hi-impedance from MCLR Low                   | _    | _   | 1.0* | μS |                   |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

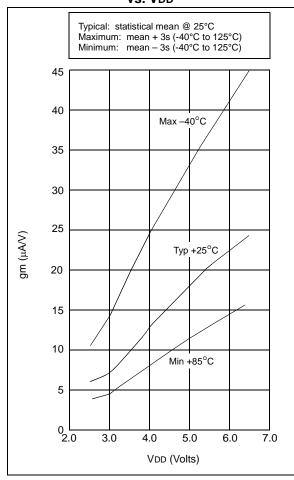

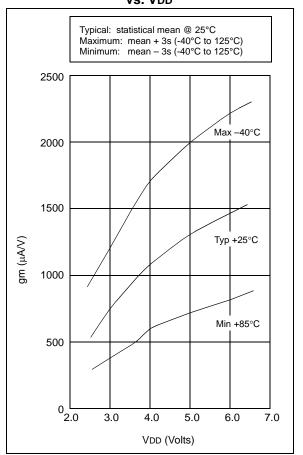

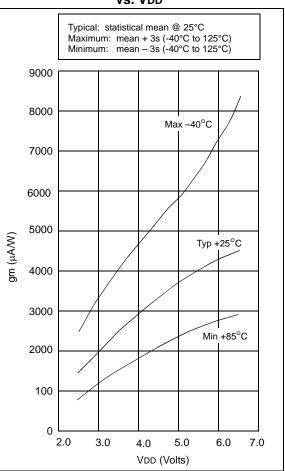

### FIGURE 14-18:

### TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

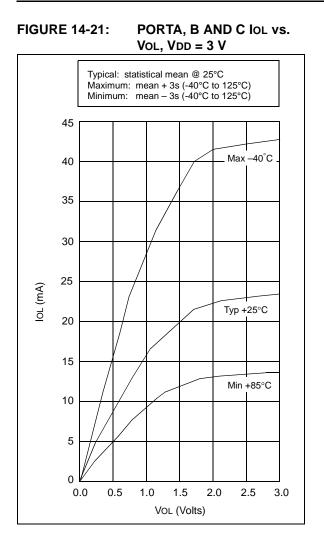

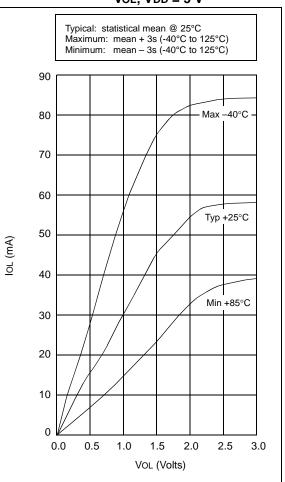

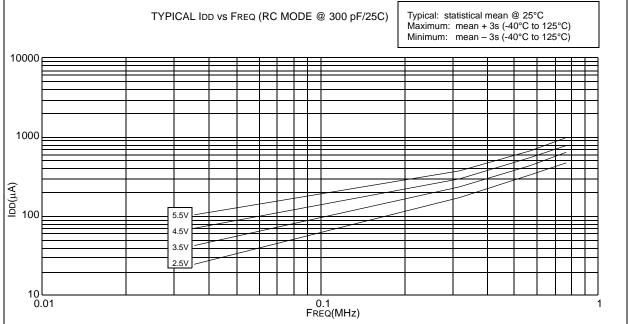

### FIGURE 14-22: PORTA, B AND C IOL vs. VoL, VDD = 5 V

### 15.2 DC Characteristics: PIC16C54A-04E, 10E, 20E (Extended) PIC16LC54A-04E (Extended)

|                                       |        | FICTULCJ                                      |                               |                             | cnac         | ч)     |                                                                                         |

|---------------------------------------|--------|-----------------------------------------------|-------------------------------|-----------------------------|--------------|--------|-----------------------------------------------------------------------------------------|

| PIC16LC54A-04E<br>(Extended)          |        |                                               |                               | <b>ard Ope</b><br>ting Terr |              |        | tions (unless otherwise specified) $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |

| PIC16C54A-04E, 10E, 20E<br>(Extended) |        |                                               |                               | ard Ope<br>ting Terr        |              |        | tions (unless otherwise specified) $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |

| Param<br>No.                          | Symbol | Characteristic                                | Min Typ† Max Units Conditions |                             |              |        |                                                                                         |

|                                       | Vdd    | Supply Voltage                                |                               |                             | •            |        |                                                                                         |

| D001                                  |        | PIC16LC54A                                    | 3.0<br>2.5                    | _                           | 6.25<br>6.25 | V<br>V | XT and RC modes<br>LP mode                                                              |

| D001A                                 |        | PIC16C54A                                     | 3.5<br>4.5                    |                             | 5.5<br>5.5   | V<br>V | RC and XT modes<br>HS mode                                                              |

| D002                                  | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>     | —                             | 1.5*                        |              | V      | Device in SLEEP mode                                                                    |

| D003                                  | VPOR   | VDD Start Voltage to ensure<br>Power-on Reset | —                             | Vss                         | -            | V      | See Section 5.1 for details on<br>Power-on Reset                                        |

| D004                                  | Svdd   | VDD Rise Rate to ensure<br>Power-on Reset     | 0.05*                         | _                           | _            | V/ms   | See Section 5.1 for details on<br>Power-on Reset                                        |

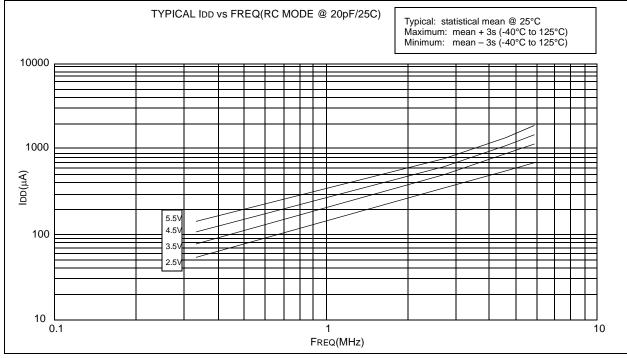

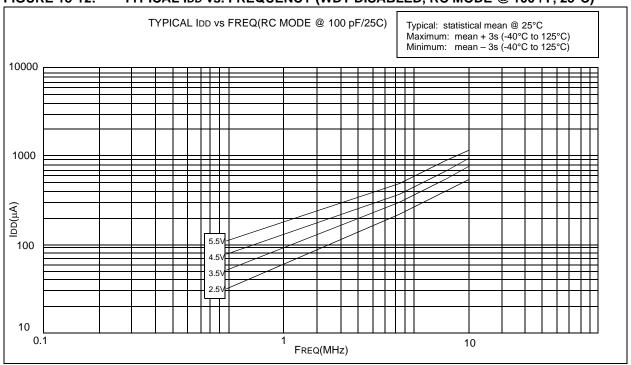

|                                       | IDD    | Supply Current <sup>(2)</sup>                 |                               |                             |              |        |                                                                                         |

| D010                                  |        | PIC16LC54A                                    | —                             | 0.5                         | 25           | mA     | Fosc = 4.0 MHz, VDD = 5.5V,<br>RC <sup>(3)</sup> and XT modes                           |

|                                       |        |                                               | —                             | 11                          | 27           | μA     | Fosc = 32 kHz, VDD = 2.5V,<br>LP mode, Commercial                                       |

|                                       |        |                                               | —                             | 11                          | 35           | μA     | Fosc = 32 kHz, VDD = 2.5V,<br>LP mode, Industrial                                       |

|                                       |        |                                               | _                             | 11                          | 37           | μA     | Fosc = 32 kHz, VDD = 2.5V,<br>LP mode, Extended                                         |

| D010A                                 |        | PIC16C54A                                     | —                             | 1.8                         | 3.3          | mA     | Fosc = 4.0 MHz, VDD = 5.5V, $RC^{(3)}$ and XT modes                                     |

|                                       |        |                                               | —                             | 4.8                         | 10           | mA     | Fosc = 10 MHz, VDD = 5.5V,<br>HS mode                                                   |

|                                       |        |                                               | —                             | 9.0                         | 20           | mA     | Fosc = 20 MHz, VDD = 5.5V,<br>HS mode                                                   |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- \* These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- **3:** Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

### FIGURE 15-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16C54A

### TABLE 15-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16C54A

| Standard Operating Conditions (unless otherwise specified) |            |                            |                      |                  |           |            |                              |

|------------------------------------------------------------|------------|----------------------------|----------------------|------------------|-----------|------------|------------------------------|

|                                                            |            | Operating Temperature 0    | $0^{\circ}C \leq TA$ | √≤ <b>+</b> 70°  | C for co  | mmercia    | al                           |

| AC Chara                                                   | cteristics | -40                        | $0^{\circ}C \leq TA$ | √≤ <b>+</b> 85°  | C for ind | dustrial   |                              |

|                                                            |            | -20                        | $0^{\circ}C \leq TA$ | ∖ ≤ <b>+</b> 85° | C for ind | dustrial - | - PIC16LV54A-02I             |

|                                                            |            | -40                        | $0^{\circ}C \leq TA$ | ∖ ≤ <b>+</b> 125 | °C for e  | xtended    | ł                            |

| Param                                                      |            |                            |                      |                  |           |            |                              |

| No.                                                        | Symbol     | Characteristic             | Min                  | Тур†             | Мах       | Units      | Conditions                   |

| 30                                                         | TmcL       | MCLR Pulse Width (low)     | 100*                 | _                | _         | ns         | VDD = 5.0V                   |

|                                                            |            |                            | 1                    | —                | —         | μS         | VDD = 5.0V (PIC16LV54A only) |

| 31                                                         | Twdt       | Watchdog Timer Time-out    | 9.0*                 | 18*              | 30*       | ms         | VDD = 5.0V (Comm)            |

|                                                            |            | Period (No Prescaler)      |                      |                  |           |            |                              |

| 32                                                         | Tdrt       | Device Reset Timer Period  | 9.0*                 | 18*              | 30*       | ms         | VDD = 5.0V (Comm)            |

| 34                                                         | Tioz       | I/O Hi-impedance from MCLR | _                    | _                | 100*      | ns         |                              |

|                                                            |            | Low                        | —                    |                  | 1μs       | —          | (PIC16LV54A only)            |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### 16.0 DEVICE CHARACTERIZATION - PIC16C54A

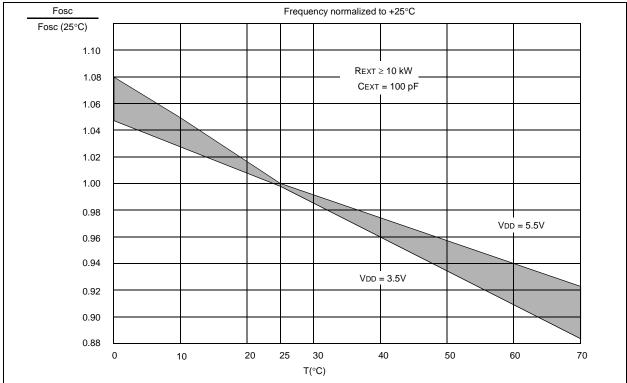

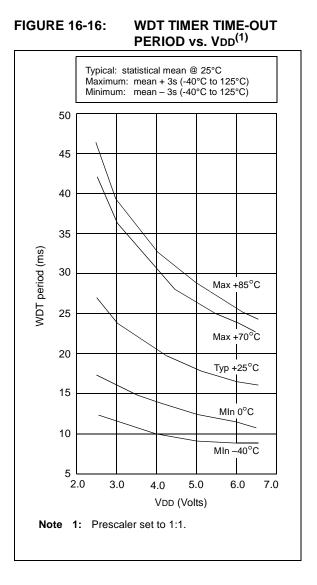

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

FIGURE 16-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

| TABLE 16-1: | RC OSCILLATOR FREQUENCIES |

|-------------|---------------------------|

|-------------|---------------------------|

| Сехт   | Rext | Average<br>Fosc @ 5 V, 25°C |       |  |

|--------|------|-----------------------------|-------|--|

| 20 pF  | 3.3K | 5 MHz ± 27%                 |       |  |

|        | 5K   | 3.8 MHz                     | ± 21% |  |

|        | 10K  | 2.2 MHz                     | ± 21% |  |

|        | 100K | 262 kHz                     | ± 31% |  |

| 100 pF | 3.3K | 1.6 MHz                     | ± 13% |  |

|        | 5K   | 1.2 MHz                     | ± 13% |  |

|        | 10K  | 684 kHz                     | ± 18% |  |

|        | 100K | 71 kHz                      | ± 25% |  |

| 300 pF | 3.3K | 660 kHz                     | ± 10% |  |

|        | 5.0K | 484 kHz                     | ± 14% |  |

|        | 10K  | 267 kHz                     | ± 15% |  |

|        | 100K | 29 kHz                      | ± 19% |  |

The frequencies are measured on DIP packages.

The percentage variation indicated here is part-to-part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviation from average value for VDD = 5V.

### FIGURE 16-17: TRANSCONDUCTANCE (gm) OF HS OSCILLATOR vs. VDD

### TABLE 17-1: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16C5X, PIC16CR5X

| AC Chara     | $ \begin{array}{l} \mbox{ Characteristics} \end{array} \begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                                              |            |        |            | -        |                                |

|--------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------|--------|------------|----------|--------------------------------|

| Param<br>No. | Symbol                                                                                                      | Characteristic Min Typ† Max Units Conditions |            |        |            |          |                                |

| 2            | Тсу                                                                                                         | Instruction Cycle Time <sup>(2)</sup>        | —          | 4/Fosc |            | —        |                                |

| 3            | TosL, TosH                                                                                                  | Clock in (OSC1) Low or High<br>Time          | 50*<br>20* |        |            | ns<br>ns | XT oscillator<br>HS oscillator |

| 4            | TosR, TosF                                                                                                  | Clock in (OSC1) Rise or Fall<br>Time         | 2.0*       | _      | <br>25*    | μS<br>ns | LP oscillator<br>XT oscillator |

|              |                                                                                                             |                                              | _          |        | 25*<br>50* | ns<br>ns | HS oscillator<br>LP oscillator |

- \* These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption.

When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

2: Instruction cycle period (TCY) equals four times the input oscillator time base period.

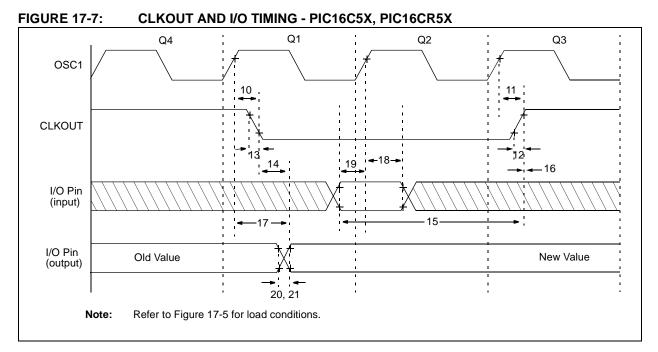

|             | ALVAUT AND VA TIMINA DEALUDENENTA DIALAASY DIALAADSY     |

|-------------|----------------------------------------------------------|

| IABLE 17-2: | CLKOUT AND I/O TIMING REQUIREMENTS - PIC16C5X, PIC16CR5X |

| AC Chara     | acteristics | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |              |      |      |       |

|--------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|-------|

| Param<br>No. | Symbol      | Characteristic                                                                                                                                                                                                                                                                                                                  | Min          | Тур† | Max  | Units |

| 10           | TosH2ckL    | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                                                                                                                                                                                                                                                                                                 | _            | 15   | 30** | ns    |

| 11           | TosH2ckH    | OSC1↑ to CLKOUT↑ <sup>(1)</sup>                                                                                                                                                                                                                                                                                                 | _            | 15   | 30** | ns    |

| 12           | TckR        | CLKOUT rise time <sup>(1)</sup>                                                                                                                                                                                                                                                                                                 | —            | 5.0  | 15** | ns    |

| 13           | TckF        | CLKOUT fall time <sup>(1)</sup>                                                                                                                                                                                                                                                                                                 | —            | 5.0  | 15** | ns    |

| 14           | TckL2ioV    | CLKOUT↓ to Port out valid <sup>(1)</sup>                                                                                                                                                                                                                                                                                        | —            | —    | 40** | ns    |

| 15           | TioV2ckH    | Port in valid before CLKOUT <sup>(1)</sup>                                                                                                                                                                                                                                                                                      | 0.25 TCY+30* | —    | _    | ns    |

| 16           | TckH2iol    | Port in hold after CLKOUT <sup>(1)</sup>                                                                                                                                                                                                                                                                                        | 0*           | —    | _    | ns    |

| 17           | TosH2ioV    | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(2)</sup>                                                                                                                                                                                                                                                                   | —            | —    | 100* | ns    |

| 18           | TosH2iol    | OSC1↑ (Q2 cycle) to Port input invalid<br>(I/O in hold time)                                                                                                                                                                                                                                                                    | TBD          | —    | _    | ns    |

| 19           | TioV2osH    | Port input valid to OSC1↑<br>(I/O in setup time)                                                                                                                                                                                                                                                                                | TBD          | —    | —    | ns    |

| 20           | TioR        | Port output rise time <sup>(2)</sup>                                                                                                                                                                                                                                                                                            | _            | 10   | 25** | ns    |

| 21           | TioF        | Port output fall time <sup>(2)</sup>                                                                                                                                                                                                                                                                                            | —            | 10   | 25** | ns    |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested. No characterization data available at this time.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

**2:** Refer to Figure 17-5 for load conditions.

# PIC16C5X

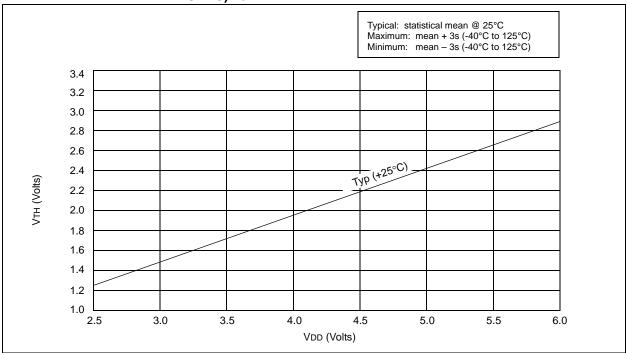

## FIGURE 18-10: VTH (INPUT THRESHOLD TRIP POINT VOLTAGE) OF OSC1 INPUT (IN XT, HS AND LP MODES) vs. VDD

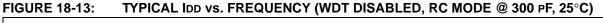

### FIGURE 18-12: TYPICAL IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 100 PF, 25°C)

### TABLE 18-2:INPUT CAPACITANCE

| Pin         | Typical Capacitance (pF) |          |  |  |  |

|-------------|--------------------------|----------|--|--|--|

| Pin         | 18L PDIP                 | 18L SOIC |  |  |  |

| RA port     | 5.0                      | 4.3      |  |  |  |

| RB port     | 5.0                      | 4.3      |  |  |  |

| MCLR        | 17.0                     | 17.0     |  |  |  |

| OSC1        | 4.0                      | 3.5      |  |  |  |

| OSC2/CLKOUT | 4.3                      | 3.5      |  |  |  |

| тоскі       | 3.2                      | 2.8      |  |  |  |

All capacitance values are typical at  $25^{\circ}$ C. A part-to-part variation of ±25% (three standard deviations) should be taken into account.

### FIGURE 19-5: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16C5X-40

### TABLE 19-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16C5X-40

| AC CharacteristicsStandard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercial)Operating Voltage VDD range is described in Section 19.1. |        |                                                  |       |      |       |    |                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------|-------|------|-------|----|-------------------|

| Param<br>No.                                                                                                                                                                                                 | Symbol | Characteristic Min Typ† Max Units Conditions     |       |      |       |    |                   |

| 30                                                                                                                                                                                                           | TmcL   | MCLR Pulse Width (low)                           | 1000* | _    | _     | ns | VDD = 5.0V        |

| 31                                                                                                                                                                                                           | Twdt   | Watchdog Timer Time-out Period<br>(No Prescaler) | 9.0*  | 18*  | 30*   | ms | VDD = 5.0V (Comm) |

| 32                                                                                                                                                                                                           | Tdrt   | Device Reset Timer Period                        | 9.0*  | 18*  | 30*   | ms | VDD = 5.0V (Comm) |

| 34                                                                                                                                                                                                           | Tioz   | I/O Hi-impedance from MCLR Low                   | 100*  | 300* | 1000* | ns |                   |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## PIC16C5X

### INDEX

### Α

| Absolute Maximum Ratings                    |

|---------------------------------------------|

| PIC16C54/55/56/5767                         |

| PIC16C54A 103                               |

| PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/ |

| C58B/CR58B 131                              |

| PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/ |

| C58B/CR58B-40 155                           |

| PIC16CR54A79                                |

| ADDWF                                       |

| ALU                                         |

| ANDLW                                       |

| ANDWF51                                     |

| Applications5                               |

| Architectural Overview                      |

| Assembler                                   |

| MPASM Assembler 61                          |

### в

| Block Diagram                |    |

|------------------------------|----|

| On-Chip Reset Circuit        |    |

| PIC16C5X Series              |    |

| Timer0                       |    |

| TMR0/WDT Prescaler           | 41 |

| Watchdog Timer               |    |

| Brown-Out Protection Circuit |    |

| BSF                          |    |

| BTFSC                        |    |

| BTFSS                        |    |

|                              |    |

## С

| CALL               | 31, 53 |

|--------------------|--------|

| Carry (C) bit      | 9, 29  |

| Clocking Scheme    |        |

| CLRF               | 53     |

| CLRW               | 53     |

| CLRWDT             | 53     |

| CMOS Technology    | 1      |

| Code Protection    | 43, 47 |

| COMF               | 54     |

| Compatibility      |        |

| Configuration Bits |        |

### D

| Data Memory Organization                    |

|---------------------------------------------|

| PIC16C54/55/56/57                           |

| Commercial                                  |

| Extended70, 72                              |

| Industrial69, 71                            |

| PIC16C54A                                   |

| Commercial104, 109                          |

| Extended106, 109                            |

| Industrial 104, 109                         |

| PIC16C54C/C55A/C56A/C57C/C58B-40            |

| Commercial157, 158                          |

| PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/ |

| C58B/CR58B                                  |

| Commercial134, 138                          |

| Extended137, 138                            |

| Industrial134, 138                          |

| PIC16CR54A                                  |

| Commercial                                  |

| Extended                         | 82, 84   |

|----------------------------------|----------|

| Industrial                       | 80, 83   |

| PIC16LV54A                       |          |

| Commercial                       | 108, 109 |

| Industrial                       | 108, 109 |

| DECF                             | 54       |

| DECFSZ                           | 54       |

| Development Support              | 61       |

| Device Characterization          |          |

| PIC16C54/55/56/57/CR54A          | 91       |

| PIC16C54A                        | 117      |

| PIC16C54C/C55A/C56A/C57C/C58B-40 | 165      |

| Device Reset Timer (DRT)         | 23       |

| Device Varieties                 | 7        |

| Digit Carry (DC) bit             |          |

| DRT                              | 23       |

### Ε

| Electrical Specifications                   |

|---------------------------------------------|

| PIC16C54/55/56/57 67                        |

| PIC16C54A103                                |

| PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/ |

| C58B/CR58B 131                              |

| PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/ |

| C58B/CR58B-40155                            |

| PIC16CR54A 79                               |

| Errata                                      |

| External Power-On Reset Circuit 21          |

### F

| Family of Devices |  |

|-------------------|--|

| PIC16C5X          |  |

| FSR Register      |  |

| Value on reset    |  |

|                   |  |

### G

| General Purpose Registers |      |

|---------------------------|------|

| Value on reset            | 20   |

| GOTO 31                   | , 55 |

### Н

| High-Performance RISC CPU |  |

|---------------------------|--|

|---------------------------|--|

### ī

| •                              |        |

|--------------------------------|--------|

| I/O Interfacing                | 35     |

| I/O Ports                      | 35     |

| I/O Programming Considerations | 36     |

| ICEPIC In-Circuit Emulator     | 62     |

| ID Locations                   | 43, 47 |

| INCF                           | 55     |

| INCFSZ                         | 55     |

| INDF Register                  | 33     |

| Value on reset                 | 20     |

| Indirect Data Addressing       | 33     |

| Instruction Cycle              |        |

| Instruction Flow/Pipelining    | 13     |

| Instruction Set Summary        | 49     |

| IORLW                          | 56     |

| IORWF                          | 56     |

| к                              |        |

|                                |        |

# KeeLoq Evaluation and Programming Tools ...... 64

| Loading of PC | 3 | , | 1 |  |

|---------------|---|---|---|--|

|---------------|---|---|---|--|

L

### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 1997-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769355

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.